Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15356-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **PIN ALLOCATION TABLES**

#### TABLE 3: 28-PIN ALLOCATION TABLE (PIC16(L)F15356)

| I/O( <sup>2)</sup> | 28-Pin PDIP/SOIC/SSOP | 28-Pin UQFN | ADC                          | Reference | Comparator       | NCO | DAC      | Timers             | ССР | MWd | CWG                   | ASSM                           | ZCD  | EUSART                    | CLC                   | СГКК | Interrupt                   | Pull-up | Basic          |

|--------------------|-----------------------|-------------|------------------------------|-----------|------------------|-----|----------|--------------------|-----|-----|-----------------------|--------------------------------|------|---------------------------|-----------------------|------|-----------------------------|---------|----------------|

| RA0                | 2                     | 27          | ANA0                         |           | C1IN0-<br>C2IN0- | _   | —        | _                  |     |     | _                     | _                              | _    |                           | CLCIN0 <sup>(1)</sup> |      | IOCA0                       | Y       | _              |

| RA1                | 3                     | 28          | ANA1                         |           | C1IN1-<br>C2IN1- | _   | _        | _                  | _   | -   | _                     | _                              |      | -                         | CLCIN1 <sup>(1)</sup> |      | IOCA1                       | Y       | _              |

| RA2                | 4                     | 1           | ANA2                         | _         | C1IN0+<br>C2IN0+ | _   | DAC1OUT1 | _                  | -   | _   | _                     | _                              | _    | _                         | -                     | _    | IOCA2                       | Y       | _              |

| RA3                | 5                     | 2           | ANA3                         | VREF+     | C1IN1+           |     | DAC1REF+ |                    |     |     | _                     |                                | _    |                           |                       | _    | IOCA3                       | Y       | _              |

| RA4                | 6                     | 3           | ANA4                         | _         | —                | _   | _        | T0CKI              |     | _   | _                     | _                              | _    | _                         | _                     | -    | IOCA4                       | Υ       | _              |

| RA5                | 7                     | 4           | ANA5                         | _         | —                | _   | _        | -                  | _   | _   | _                     | SS1 <sup>(1)</sup>             | _    | _                         | _                     | _    | IOCA5                       | Υ       | _              |

| RA6                | 10                    | 7           | ANA6                         | -         | —                | _   | -        | _                  |     |     | -                     | _                              | _    |                           |                       | I    | IOCA6                       | Y       | CLKOUT<br>OSC2 |

| RA7                | 9                     | 6           | ANA7                         | -         | —                | _   | —        | _                  | -   | -   | _                     | _                              | _    |                           | -                     | I    | IOCA7                       | Y       | CLKIN<br>OSC1  |

| RB0                | 21                    | 18          | ANB0                         | I         | C2IN1+           |     | _        |                    |     |     | CWG1IN <sup>(1)</sup> | SS2 <sup>(1)</sup>             | ZCD1 |                           |                       | I    | INT <sup>(1)</sup><br>IOCB0 | Y       | _              |

| RB1                | 22                    | 19          | ANB1                         | I         | C1IN3-<br>C2IN3- |     | _        |                    |     |     | _                     | SCK2,<br>SCL2 <sup>(1,4)</sup> | -    |                           |                       | I    | IOCB1                       | Y       | —              |

| RB2                | 23                    | 20          | ANB2                         |           | —                | _   | -        |                    |     |     | -                     | SDA2,<br>SDI2 <sup>(1,4)</sup> | _    |                           |                       | I    | IOCB2                       | Y       | _              |

| RB3                | 24                    | 21          | ANB3                         | Ι         | C1IN2-<br>C2IN2- | -   | _        |                    |     | -   | -                     | -                              |      | -                         | -                     |      | IOCB3                       | Y       | —              |

| RB4                | 25                    | 22          | ANB4<br>ADACT <sup>(1)</sup> | _         | —                | _   | _        | _                  | _   | _   | _                     | _                              | _    | _                         | _                     | _    | IOCB4                       | Y       | _              |

| RB5                | 26                    | 23          | ANB5                         | _         | _                | l   | _        | T1G <sup>(1)</sup> |     |     | _                     | l                              | _    |                           | l                     |      | IOCB5                       | Y       | _              |

| RB6                | 27                    | 24          | ANB6                         |           | _                | _   | -        | _                  |     |     | _                     | _                              | _    | TX2<br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> |      | IOCB6                       | Y       | ICSPCLK        |

| RB7                | 28                    | 25          | ANB7                         | _         | —                | _   | DAC1OUT2 | _                  |     |     | _                     | _                              | _    | RX2<br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> | -    | IOCB7                       | Y       | ICSPDAT        |

PIC16(L)F15356/75/76/85/86

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

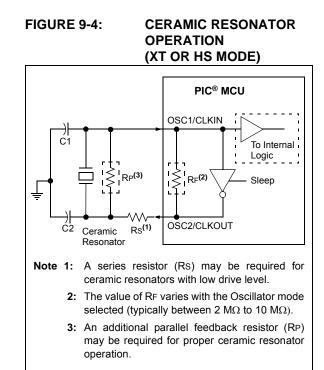

#### 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

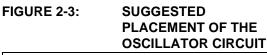

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, refer to these Microchip Application Notes, available at the corporate website (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### 4.3.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains:

- the arithmetic status of the ALU

- the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

# For example, CLRF STATUS will clear bits <4:3> and <1:0>, and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, refer to **Section 36.0** "Instruction Set Summary".

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

#### REGISTER 4-1: STATUS: STATUS REGISTER

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| —     |     |     | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                                                                     |

|         | <ul> <li>1 = After power-up, CLRWDT instruction or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                                                                                                 |

| bit 3   | PD: Power-Down bit                                                                                                                                                                                                   |

|         | 1 = After power-up or by the CLRWDT instruction                                                                                                                                                                      |

|         | 0 = By execution of the SLEEP instruction                                                                                                                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | 1 = The result of an arithmetic or logic operation is zero                                                                                                                                                           |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                       |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                                                                                                                    |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                                                                                                                            |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                          |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                                                                                 |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

#### **BANK 8** BANK 9 **BANK 10 BANK 11 BANK 12 BANK 13 BANK 14 BANK 15** 400h 480h 500h 580h 600h 680h 700h 780h Core Register (Table 4-3) 48Bh 50Bh 58Bh 60Bh 70Bh 78Bh 40Bh 68Bh 50Ch NCO1ACCL CWG1CLK 40Ch \_ 48Ch \_ \_ 58Ch 60Ch 68Ch \_ 70Ch PIR0 78Ch \_\_\_\_ NCO1ACCH CWG1DAT \_ 48Dh \_ 50Dh \_\_\_ \_\_\_\_ PIR1 40Dh 58Dh 60Dh 68Dh 70Dh 78Dh \_ 48Eh \_ 50Eh NCO1ACCU CWG1DBR PIR2 78Eh 40Eh \_ \_ 58Eh 60Eh 68Eh \_ 70Eh \_ 48Fh \_ 50Fh NCO1INCL CWG1DBF PIR3 40Fh \_ \_ 58Fh 60Fh 68Fh \_ 70Fh 78Fh CWG1CON0 490h 510h NCO1INCH PIR4 \_ \_ \_ 590h 610h 690h 710h 790h 410h \_ \_ CWG1CON1 491h \_ 511h NCO1INCU PIR5 411h \_ \_ 591h 611h 691h \_ 711h 791h \_ NCO1CON CWG1AS0 512h \_ 492h \_ \_ 592h 612h 692h \_ 712h PIR6 792h 412h 513h NCO1CLK CWG1AS1 493h 593h 613h 693h 713h PIR7 793h 413h \_ \_ \_ \_ \_ CWG1STR \_ 494h \_ 514h \_ 594h \_ 614h 694h \_ 714h — 794h 414h 495h \_ 515h \_ 595h 615h \_\_\_\_ 695h 715h \_ 795h 415h \_ \_ 496h 516h PIE0 PMD0 416h \_ \_ \_ 596h \_ 616h \_ 696h \_ 716h 796h \_ 517h \_ \_ PMD1 497h \_ PIE1 417h 597h 617h 697h 717h 797h PMD2 \_ 518h \_ PIE2 418h — 498h \_ 598h \_ 618h 698h \_ 718h 798h PMD3 419h \_ 499h \_ 519h \_ 599h \_ 619h \_ 699h \_ 719h PIE3 799h \_ 49Ah \_ 51Ah \_\_\_\_ \_ \_ \_ PIE4 79Ah PMD4 41Ah 59Ah 61Ah 69Ah 71Ah 49Bh \_ 51Bh \_ \_ PIE5 PMD5 41Bh \_ \_ 59Bh 61Bh 69Bh \_ 71Bh 79Bh 41Ch 49Ch 51Ch TMR0 61Ch \_ \_\_\_\_ PIE6 \_\_\_\_ \_\_\_ \_ \_ 59Ch 69Ch 71Ch 79Ch 49Dh 51Dh PR0 PIE7 \_ 79Dh \_ 41Dh — \_ \_ 59Dh 61Dh 69Dh \_ 71Dh TMR0CON0 \_ \_ 59Eh \_ 69Eh \_ \_ 79Eh 41Eh 49Eh 51Eh \_ 61Eh 71Eh \_ TMR0CON1 41Fh 49Fh 51Fh 59Fh 61Fh \_ 69Fh 71Fh 79Fh \_ \_ \_ \_ — \_ General 420h 4A0h 520h 5A0h 620h 6A0h 720h 7A0h Purpose General Register General General General General General General 48 Bytes Purpose Purpose Purpose 64Fh Purpose Purpose Purpose Purpose Register Register General Register Register Register Register 650h Register 80 Bytes<sup>(2)</sup> 80 Bytes 80 Bytes 80 Bytes 80 Bytes Purpose 80 Bytes(2) 80 Bytes<sup>(2)</sup> Register 32 Bytes<sup>(2)</sup> 46Fh 4EFh 56Fh 5EFh 66Fh 6EFh 76Fh 7EFh Common RAM 470h 4F0h 570h 5F0h 670h 6F0h 770h 7F0h Accesses Accesses Accesses Accesses Accesses Accesses Accesses Accesses 70h-7Fh 47Fh 70h-7Fh 4FFh 70h-7Fh 57Fh 70h-7Fh 5FFh 70h-7Fh 67Fh 70h-7Fh 6FFh 70h-7Fh 77Fh 70h-7Fh 7FFh

#### TABLE 4-5: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANKS 8-15

Note 1: Unimplemented locations read as '0'.

2: Present only on PIC16(L)F15356/76/86.

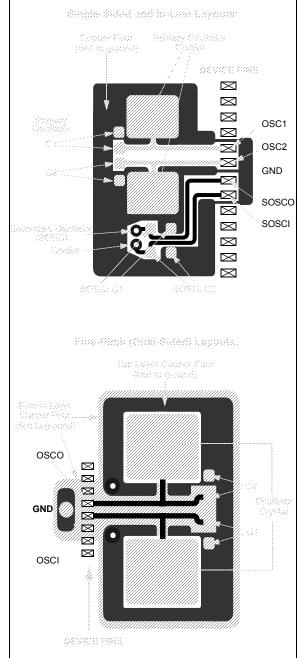

### 4.6.1 TRADITIONAL/BANKED DATA MEMORY

The traditional or banked data memory is a region from FSR address 0x000 to FSR address 0x1FFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

## PIC16(L)F15356/75/76/85/86

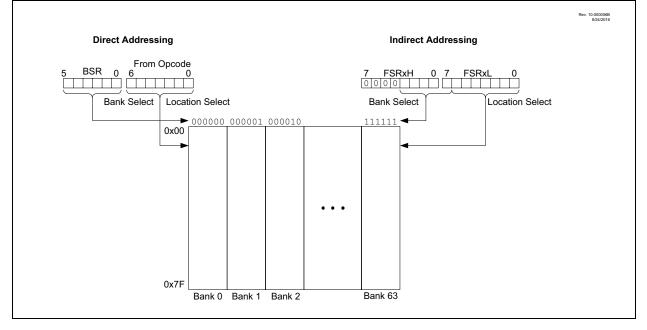

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

#### 9.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR), Brown-out Reset (BOR) or a wake-up from Sleep. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

#### 14.2 PORTA Registers

#### 14.2.1 DATA REGISTER

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 14-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 14.2.8 shows how to initialize PORTA.

Reading the PORTA register (Register 14-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The PORT data latch LATA (Register 14-3) holds the output port data, and contains the latest value of a LATA or PORTA write.

#### EXAMPLE 14-1: INITIALIZING PORTA

| ; This code example illustrates<br>; initializing the PORTA register. The<br>; other ports are initialized in the same<br>; manner. |             |                        |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------|--|--|--|--|--|

| BANKSEL                                                                                                                             | PORTA       | ;                      |  |  |  |  |  |

| CLRF                                                                                                                                | PORTA       | ;Init PORTA            |  |  |  |  |  |

| BANKSEL                                                                                                                             | LATA        | ;Data Latch            |  |  |  |  |  |

| CLRF                                                                                                                                | LATA        | ;                      |  |  |  |  |  |

| BANKSEL                                                                                                                             | ANSELA      | ;                      |  |  |  |  |  |

| CLRF                                                                                                                                | ANSELA      | ;digital I/O           |  |  |  |  |  |

| BANKSEL                                                                                                                             | TRISA       | ;                      |  |  |  |  |  |

| MOVLW                                                                                                                               | B'00111000' | ;Set RA<5:3> as inputs |  |  |  |  |  |

| MOVWF                                                                                                                               | TRISA       | ;and set RA<2:0> as    |  |  |  |  |  |

|                                                                                                                                     |             | ;outputs               |  |  |  |  |  |

#### 14.2.2 DIRECTION CONTROL

The TRISA register (Register 14-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.2.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 14-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for I <sup>2</sup> C; the I <sup>2</sup> C |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                                       |

#### 14.2.4 SLEW RATE CONTROL

The SLRCONA register (Register 14-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.2.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 14-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

| Note: | Changing the input threshold selection should be performed while all peripheral |

|-------|---------------------------------------------------------------------------------|

|       | modules are disabled. Changing the                                              |

|       | threshold level during the time a module is                                     |

|       | active may inadvertently generate a                                             |

|       | transition associated with an input pin,                                        |

|       | regardless of the actual voltage level on                                       |

|       | that pin.                                                                       |

| DIL 7   |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         |         |         |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| ODCF7   | ODCF6   | ODCF5   | ODCF4   | ODCF3   | ODCF2   | ODCF1   | ODCF0   |

| R/W-0/0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

ODCF<7:0>: PORTF Open-Drain Enable bits

For RF<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 14-47: SLRCONF: PORTF SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRF7   | SLRF6   | SLRF5   | SLRF4   | SLRF3   | SLRF2   | SLRF1   | SLRF0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRF<7:0>: PORTF Slew Rate Enable bits

For RF<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### REGISTER 14-48: INLVLF: PORTF INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4 | INLVLF3 | INLVLF2 | INLVLF1 | INLVLF0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLF<7:0>: PORTF Input Level Select bits

For RF<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

#### 23.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See Comparator Specifications in Table 37-14 for more information.

#### 23.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 26.6 "Timer Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 23.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 23-2) and the Timer1 Block Diagram (Figure 26-1) for more information.

#### 23.5 Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

## 23.6 Comparator Positive Input Selection

Configuring the CxPCH<2:0> bits of the CMxPSEL register directs an internal voltage reference or an analog pin to the noninverting input of the comparator:

- CxIN0+ analog pin

- DAC output

- FVR (Fixed Voltage Reference)

- Vss (Ground)

See **Section 18.0** "**Fixed Voltage Reference (FVR)**" for more information on the Fixed Voltage Reference module.

See Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

## 23.7 Comparator Negative Input Selection

The CxNCH<2:0> bits of the CMxCON1 register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- CxIN- pin

- FVR (Fixed Voltage Reference)

- · Analog Ground

Note: To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

## PIC16(L)F15356/75/76/85/86

#### EXAMPLE 24-1:

VRMS = 120 VPEAK =VRMS\*  $\sqrt{2}$  = 169.7 f = 60 Hz C = 0.1 uF Z = VPEAK/3x10<sup>-4</sup> = 169.7/(3x10<sup>-4</sup>) = 565.7 kOhms Xc = 1/(2 $\Pi$ fC) = 1/(2 $\Pi$ \*60\*1\*10<sup>-7</sup>) = 26.53 kOhms R =  $\sqrt{(Z^2 - Xc^2)}$  = 565.1 kOhms (computed) R = 560 kOhms (used) ZR =  $\sqrt{(R^2 + Xc^2)}$  = 560.6 kOhms (using actual resistor) IPEAK = VPEAK/ZR = 302.7\*10<sup>-6</sup> VC = Xc\* IPEAK = 8.0 V  $\Phi$  = Tan<sup>-1</sup>(Xc/R) = 0.047 radians T $_{\Phi}$  =  $\Phi/(2\Pi f)$  = 125.6 us

#### 24.5.2 CORRECTION BY OFFSET CURRENT

When the waveform is varying relative to VSS, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 24-3.

#### EQUATION 24-3: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{Vcpinv}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VDD - Vcpinv}{VPEAK}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to Vss. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the VCPINV switching voltage. The pull-up or pull-down value can be determined with the equation shown in Equation 24-4.

#### EQUATION 24-4: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$R_{PULLUP} = \frac{R_{SERIES}(V_{PULLUP} - V_{cpinv})}{V_{cpinv}}$$

When External Signal is relative to VDD:

$$\left(RPULLDOWN = \frac{RSERIES \times (Vcpinv)}{(VDD - Vcpinv)}\right)$$

#### 24.6 Handling VPEAK variations

If the peak amplitude of the external voltage is expected to vary, the series resistor must be selected to keep the ZCD current source and sink below the design maximum range of  $\pm 600 \ \mu$ A and above a reasonable minimum range. A general rule of thumb is that the maximum peak voltage can be no more than six times the minimum peak voltage. To ensure that the maximum current does not exceed  $\pm 600 \ \mu$ A and the minimum is at least  $\pm 100 \ \mu$ A, compute the series resistance as shown in Equation 24-5. The compensating pull-up for this series resistance can be determined with Equation 24-4 because the pull-up value is not dependent from the peak voltage.

#### EQUATION 24-5: SERIES R FOR V RANGE

$$R_{SERIES} = \frac{V_{MAXPEAK} + V_{MINPEAK}}{7 \times 10^{-4}}$$

© 2016 Microchip Technology Inc.

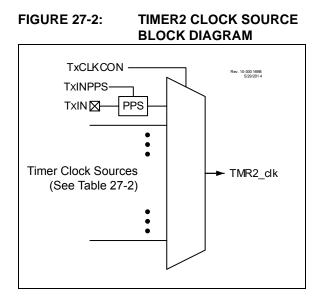

#### 27.1 Timer2 Operation

Timer2 operates in three major modes:

- Free Running Period

- One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 27-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- · any device Reset

- External Reset Source event that resets the timer.

| Note:    | TMR2 | is | not | cleared | when | T2CON | is |

|----------|------|----|-----|---------|------|-------|----|

| written. |      |    |     |         |      |       |    |

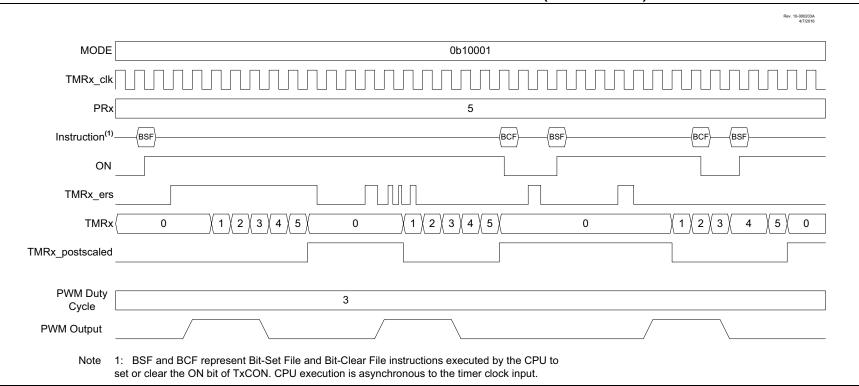

#### 27.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each TMR2\_clk cycle. When the two values match, the comparator resets the value of TMR2 to 00h on the next rising TMR2\_clk edge and increments

the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register, a one TMR2\_clk period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

#### 27.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

#### 27.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

#### 27.2 Timer2 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- The ADC module, as an Auto-conversion Trigger

- · COG, as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See Section 28.0 "Capture/Compare/PWM Modules" for more details on setting up Timer2 for use with the CCP, as well as the timing diagrams in Section 27.5 "Operation Examples" for examples of how the varying Timer2 modes affect CCP PWM output.

#### 27.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2 with the T2RST register. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

#### FIGURE 27-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

#### REGISTER 28-1: CCPxCON: CCPx CONTROL REGISTER (CONTINUED)

- bit 3-0 MODE<3:0>: CCPx Mode Select bits<sup>(1)</sup>

- 1111 1100 = PWM mode (Timer2 as the timer source)

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Reserved

- 1011 = Compare mode: output will pulse 0-1-0; Clears TMR1

- 1010 = Compare mode: output will pulse 0-1-0

- 1001 = Compare mode: clear output on compare match

- 1000 = Compare mode: set output on compare match

- 0111 = Capture mode: every 16th rising edge of CCPx input

- 0110 = Capture mode: every 4th rising edge of CCPx input

- 0101 = Capture mode: every rising edge of CCPx input

- 0100 = Capture mode: every falling edge of CCPx input

- 0011 = Capture mode: every edge of CCPx input

- 0010 = Compare mode: toggle output on match

- 0001 = Compare mode: toggle output on match; clear TMR1

- 0000 = Capture/Compare/PWM off (resets CCPx module)

- **Note 1:** All modes will set the CCPxIF bit, and will trigger an ADC conversion if CCPx is selected as the ADC trigger source.

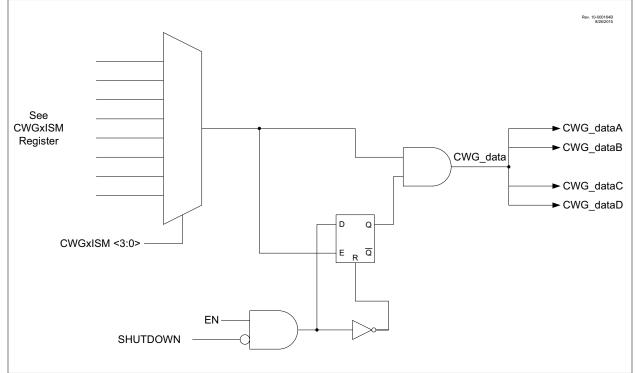

#### 30.1.4 STEERING MODES

In Steering modes, the data input can be steered to any or all of the four CWG output pins. In Synchronous Steering mode, changes to steering selection registers take effect on the next rising input.

In Non-Synchronous mode, steering takes effect on the next instruction cycle. Additional details are provided in **Section 30.9 "CWG Steering Mode"**.

#### 30.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the CS bit of the CWG1CLKCON register.

#### **30.3 Selectable Input Sources**

The CWG generates the output waveforms from the input sources in Table 30-2.

#### TABLE 30-2: SELECTABLE INPUT SOURCES

| Source Peripheral | Signal Name |  |  |

|-------------------|-------------|--|--|

| CWG input PPS pin | CWG1IN PPS  |  |  |

| CCP1              | CCP1_out    |  |  |

| CCP2              | CCP2_out    |  |  |

| PWM3              | PWM3_out    |  |  |

| PWM4              | PWM4_out    |  |  |

| PWM5              | PWM5_out    |  |  |

| PWM6              | PWM6_out    |  |  |

| NCO               | NCO1_out    |  |  |

| Comparator C1     | C1OUT_sync  |  |  |

| Comparator C2     | C2OUT_sync  |  |  |

| CLC1              | LC1_out     |  |  |

| CLC2              | LC2_out     |  |  |

| CLC3              | LC3_out     |  |  |

| CLC4              | LC4_out     |  |  |

The input sources are selected using the CWG1ISM register.

#### 30.4 Output Control

#### 30.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWG1CON1. Auto-shutdown and steering options are unaffected by polarity.

#### 30.5 Dead-Band Control

The dead-band control provides non-overlapping PWM signals to prevent shoot-through current in PWM switches. Dead-band operation is employed for Half-Bridge and Full-Bridge modes. The CWG contains two 6-bit dead-band counters. One is used for the rising edge of the input source control in Half-Bridge mode or for reverse dead-band Full-Bridge mode. The other is used for the falling edge of the input source control in Half-Bridge mode or for forward dead band in Full-Bridge mode.

Dead band is timed by counting CWG clock periods from zero up to the value in the rising or falling deadband counter registers. See CWG1DBR and CWG1DBF registers, respectively.

### 30.5.1 DEAD-BAND FUNCTIONALITY IN HALF-BRIDGE MODE

In Half-Bridge mode, the dead-band counters dictate the delay between the falling edge of the normal output and the rising edge of the inverted output. This can be seen in Figure 30-9.

### 30.5.2 DEAD-BAND FUNCTIONALITY IN FULL-BRIDGE MODE

In Full-Bridge mode, the dead-band counters are used when undergoing a direction change. The MODE<0> bit of the CWG1CON0 register can be set or cleared while the CWG is running, allowing for changes from Forward to Reverse mode. The CWG1A and CWG1C signals will change upon the first rising input edge following a direction change, but the modulated signals (CWG1B or CWG1D, depending on the direction of the change) will experience a delay dictated by the deadband counters. This is demonstrated in Figure 30-3.

## 30.6 Rising Edge and Reverse Dead Band

CWG1DBR controls the rising edge dead-band time at the leading edge of CWG1A (Half-Bridge mode) or the leading edge of CWG1B (Full-Bridge mode). The CWG1DBR value is double-buffered. When EN = 0, the CWG1DBR register is loaded immediately when CWG1DBR is written. When EN = 1, then software must set the LD bit of the CWG1CON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

## 30.7 Falling Edge and Forward Dead Band

CWG1DBF controls the dead-band time at the leading edge of CWG1B (Half-Bridge mode) or the leading edge of CWG1D (Full-Bridge mode). The CWG1DBF value is double-buffered. When EN = 0, the CWG1DBF register is loaded immediately when CWG1DBF is written. When EN = 1 then software must set the LD bit of the CWG1CON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

Refer to Figure 30-6 and Figure 30-7 for examples.

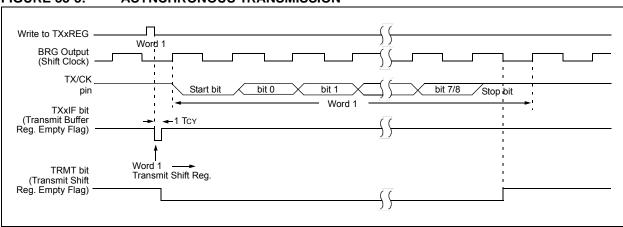

#### 33.1.1.5 TSR Status

The TRMT bit of the TXxSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXxREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 33.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXxSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXxSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXxREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXxREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 33.1.2.7** "Address **Detection**" for more information on the Address mode.

#### 33.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXxIF interrupt bit to be set.

- If interrupts are desired, set the TXxIE interrupt enable bit of the PIE3 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXxREG register. This will start the transmission.

#### FIGURE 33-3: ASYNCHRONOUS TRANSMISSION

## PIC16(L)F15356/75/76/85/86

| TRIS             | Load TRIS Register with W                                                                                                                            |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                       |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                    |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |  |  |  |

| Status Affected: | None                                                                                                                                                 |  |  |  |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                   |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                      |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

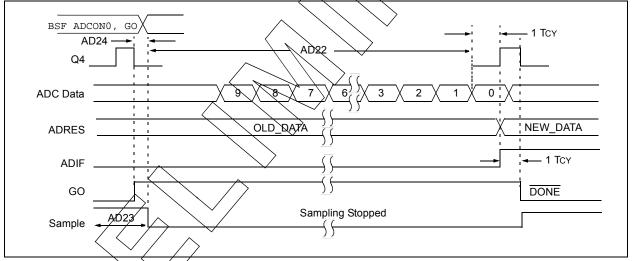

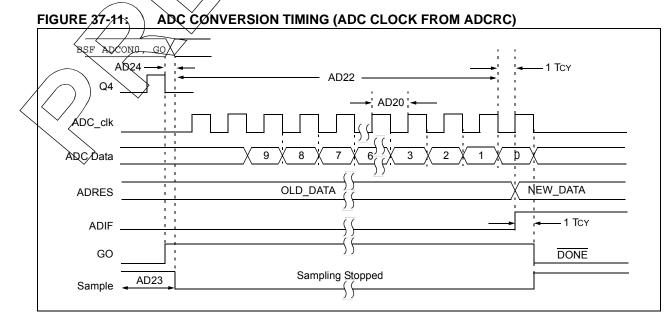

#### TABLE 37-13: ANALOG-TO-DIGITAL CONVERTER (ADC) CONVERSION TIMING SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |      |                                              |      |      |      |       |                                                                              |  |

|---------------------------------------------------------|------|----------------------------------------------|------|------|------|-------|------------------------------------------------------------------------------|--|

| Param.<br>No.                                           | Sym. | Characteristic                               | Min. | Тур† | Max. | Units | Conditions                                                                   |  |

| AD20                                                    | Tad  | ADC Clock Period                             | 1    | _    | 9    | μs    | The requirement is to set ADCCS correctly to produce this period/friequency. |  |

| AD21                                                    |      |                                              | 1    | 2    | 6    | μs    | Using FRC as the ADC clock<br>source ADOSC = 1                               |  |

| AD22                                                    | TCNV | Conversion Time                              | -    | 11   | -    | TAD   | Set of GO/DONE bit to Clear of GO/DONE bit                                   |  |

| AD23                                                    | TACQ | Acquisition Time                             | —    | 2    | Ύ,   | μs    |                                                                              |  |

| AD24                                                    | Тнср | Sample and Hold Capacitor<br>Disconnect Time | —    | -    | _/   | μs    | Fosc-based clock source<br>FRC-based clock source                            |  |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 37-10: ADC CONVERSION TIMING (AQC CLOCK Fosc-BASED)

© 2016 Microchip Technology Inc.

#### APPENDIX A: DATA SHEET REVISION HISTORY

#### Revision A (12/2016)

Initial release of the document.