Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XE

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

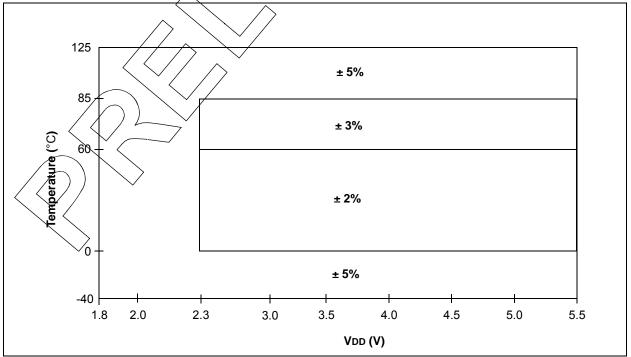

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

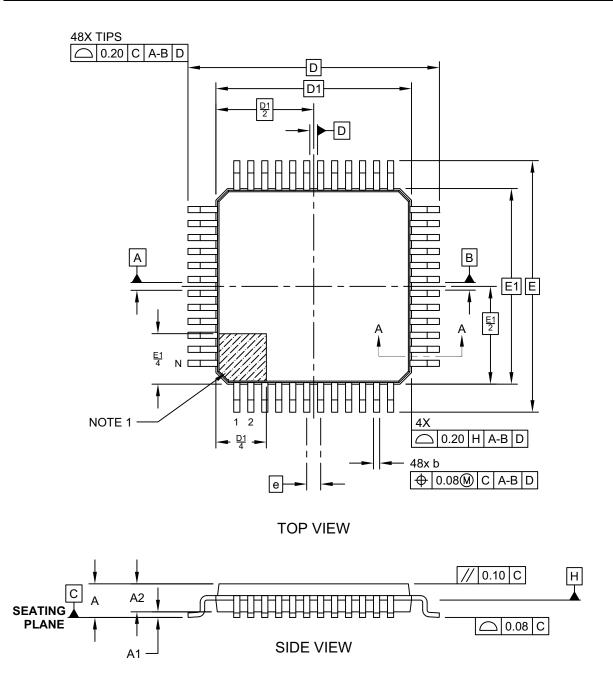

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15356t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Н |          |

|---|----------|

|   | _        |

|   |          |

|   |          |

|   |          |

|   |          |

|   | <b>O</b> |

|   |          |

|   |          |

|   | Ŧ        |

|   |          |

|   |          |

|   |          |

|   | 35       |

|   |          |

|   | 5        |

|   |          |

|   | UT I     |

|   |          |

|   |          |

|   | 6        |

| I |          |

| I | 85/      |

| I |          |

| I | 8        |

| I | ő        |

| н |          |

Preliminary

| I/O <sup>(2)</sup> | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO | DAC | Timers              | CCP                 | MWM | SWC | ASSM                          | ZCD | EUSART                    | CLC | CLKR | Interrupt | Pull-up | Basic       |

|--------------------|------------------|------|-----------|------------|-----|-----|---------------------|---------------------|-----|-----|-------------------------------|-----|---------------------------|-----|------|-----------|---------|-------------|

| RC2                | 40               | ANC2 | —         | —          | —   | _   | —                   | CCP1 <sup>(1)</sup> | -   | —   | —                             |     | —                         | -   | —    | IOCC2     | Y       | —           |

| RC3                | 41               | ANC3 | -         | -          | -   | _   | T2IN <sup>(1)</sup> | -                   | _   | _   | SCL1<br>SCL2 <sup>(1,4)</sup> | _   | —                         | _   | -    | IOCC3     | Y       | -           |

| RC4                | 46               | ANC4 | -         | _          | _   | _   | -                   | —                   | _   | -   | SDA1<br>SDI1 <sup>(1,4)</sup> | _   | —                         | _   | _    | IOCC4     | Y       | _           |

| RC5                | 47               | ANC5 | _         | —          | _   | _   | _                   | _                   | _   | _   | _                             | _   | —                         | _   | _    | IOCC5     | Υ       | _           |

| RC6                | 48               | ANC6 | -         | —          | —   | _   | —                   | —                   | _   | —   | —                             |     | TX1<br>CK1 <sup>(1)</sup> | _   | -    | IOCC6     | Y       | —           |

| RC7                | 1                | ANC7 | -         | —          | —   | _   | —                   | —                   | _   | —   | _                             |     | RX1<br>DT1 <sup>(1)</sup> | _   | -    | IOCC7     | Y       | —           |

| RD0                | 42               | AND0 | -         | —          | -   | -   | -                   | —                   | —   | -   | SCK2<br>SCL2 <sup>(1,4)</sup> | —   | -                         | —   | -    | -         | Y       | —           |

| RD1                | 43               | AND1 | —         | —          | —   |     | —                   | —                   | _   | —   | SDA2<br>SDI2 <sup>(1,4)</sup> |     | _                         | _   | -    | —         | Y       | —           |

| RD2                | 44               | AND2 | _         | _          | —   | _   | _                   | _                   | -   | _   | _                             | _   | —                         | -   | _    | _         | Y       | _           |

| RD3                | 45               | AND3 | _         | _          | _   | _   | _                   | _                   |     | _   | _                             |     | _                         |     | —    | _         | Y       | _           |

| RD4                | 2                | AND4 | _         | _          | —   | _   | _                   | —                   | _   | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RD5                | 3                | AND5 | _         | _          | —   | _   | _                   | —                   | -   | _   | _                             | -   | _                         | -   | _    | _         | Υ       | _           |

| RD6                | 4                | AND6 | _         | _          | —   | _   | _                   | _                   | _   | —   | _                             | _   | _                         | _   | _    | —         | Υ       | _           |

| RD7                | 5                | AND7 | —         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE0                | 27               | ANE0 | -         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE1                | 28               | ANE1 | _         | —          | —   | _   | -                   | —                   | _   | -   | _                             | _   | _                         | _   | —    | -         | Υ       | —           |

| RE2                | 29               | ANE2 | _         | —          | —   | —   | —                   | —                   | —   | —   | —                             | _   | —                         | —   | —    | —         | Y       | —           |

| RE3                | 20               | _    | -         | —          | —   |     | —                   | —                   | _   | —   | —                             | _   | —                         | _   | _    | IOCE3     | Y       | MCLR<br>VPP |

| RF0                | 36               | ANF0 | _         | _          | —   | _   | —                   | _                   | _   | —   | _                             |     | _                         | _   | _    | —         | Y       | _           |

| RF1                | 37               | ANF1 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF2                | 38               | ANF2 | _         | —          | —   | _   | -                   | _                   | _   | —   | —                             | _   | —                         | _   | —    | —         | Υ       | _           |

| RF3                | 39               | ANF3 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF4                | 12               | ANF4 | —         | —          | —   |     | —                   | —                   |     | _   | _                             |     | _                         |     | —    | —         | Υ       | —           |

TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

#### **TABLE 1-4:** PIC16(L)F15385/86 PINOUT DESCRIPTION (CONTINUED)

| Name                                                            | Function | Input<br>Type | Output Type       | Description                    |

|-----------------------------------------------------------------|----------|---------------|-------------------|--------------------------------|

| RF5/ANF5                                                        | RF5      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF5     | AN            | _                 | ADC Channel D0 input.          |

| RF6/ANF6                                                        | RF6      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF6     | AN            | —                 | ADC Channel D0 input.          |

| RF7/ANF7                                                        | RF5      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF5     | AN            | _                 | ADC Channel D0 input.          |

| VDD                                                             | Vdd      | Power         | _                 | Positive supply voltage input. |

| Vss                                                             | Vss      | Power         | _                 | Ground reference.              |

| Legend: AN = Analog input or outp<br>TTL = TTL compatible input |          |               | mpatible input or |                                |

TTL = TTL compatible input

HV = High Voltage

XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-7.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for  $l^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the  $l^2C$  specific or SMBus input buffer thresholds. 4:

read program and data memory.

The hardware stack is 16-levels deep and has Overflow and Underflow Reset capability. Direct,

Indirect, and Relative Addressing modes are available.

Two File Select Registers (FSRs) provide the ability to

## 3.0 ENHANCED MID-RANGE CPU

This family of devices contains an enhanced mid-range 8-bit CPU core. The CPU has 48 instructions. Interrupt capability includes automatic context saving.

FIGURE 3-1: CORE DATA PATH DIAGRAM

Rev. 10-000055C 11/30/2016 15 Configuration Data Bus 15 8 Program Counter Flash MUX Program Memory 16-Level Stack RAM (15-bit) 14 Program Program Memory 12 RAM Addr Bus Read (PMR) Addr MUX Instruction Reg Indirect Direct Addr Addr 7 12 5 12 BSR Reg 15, FSR0 Reg 15, FSR1 Reg STATUS Reg 8 MUX Power-up Instruction Timer Decode and Power-on Control Reset ALU 8 Watchdog CLKIN Timer Brown-out CLKOUT Timing Reset W Reg Generation  $\boxtimes$ SOSCI sosco 🖂 囟 囟 Vdd Vss Internal Oscillator Block

The HIGH directive will set bit 7 if a label points to a location in the program memory. This applies to the assembly code Example 4-2 shown below.

#### EXAMPLE 4-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants  |            |      |         |      |  |

|------------|------------|------|---------|------|--|

| RETLW      | DATA0      |      | ;Index0 | data |  |

| RETLW      | DATA1      |      | ;Index1 | data |  |

| RETLW      | DATA2      |      |         |      |  |

| RETLW      | DATA3      |      |         |      |  |

| my_functi  | on         |      |         |      |  |

| ;… LOI     | IS OF CODE | c    |         |      |  |

| MOVLW      | LOW con    | stan | ts      |      |  |

| MOVWF      | FSR1L      |      |         |      |  |

| MOVLW      | HIGH CO    | nsta | nts     |      |  |

| MOVWF      | FSR1H      |      |         |      |  |

| MOVIW      | 0[FSR1]    |      |         |      |  |

| ; THE PROG | RAM MEMORY | Y IS | IN W    |      |  |

|            |            |      |         |      |  |

#### 4.2 Memory Access Partition (MAP)

User Flash is partitioned into:

- Application Block

- Boot Block, and

- Storage Area Flash (SAF) Block

The user can allocate the memory usage by setting the BBEN bit, selecting the size of the partition defined by BBSIZE[2:0] bits and enabling the Storage Area Flash by the SAFEN bit of the Configuration Word (see Register 5-4). Refer to Table 4-2 for the different user Flash memory partitions.

#### 4.2.1 APPLICATION BLOCK

Default settings of the Configuration bits ( $\overline{BBEN} = 1$ and  $\overline{SAFEN} = 1$ ) assign all memory in the user Flash area to the Application Block.

#### 4.2.2 BOOT BLOCK

If  $\overline{\text{BBEN}} = 1$ , the Boot Block is enabled and a specific address range is alloted as the Boot Block based on the value of the BBSIZE bits of Configuration Word (Register 5-4) and the sizes provided in Table 5-1.

#### 4.2.3 STORAGE AREA FLASH

Storage Area Flash (SAF) is enabled by clearing the SAFEN bit of the Configuration Word in Register 5-4. If enabled, the SAF block is placed at the end of memory and spans 128 words. If the Storage Area Flash (SAF) is enabled, the SAF area is not available for program execution.

#### 4.2.4 MEMORY WRITE PROTECTION

All the memory blocks have corresponding write protection fuses WRTAPP, WRTB and WRTC bits in the Configuration Word 4 (Register 5-4). If write-protected locations are written from NVMCON registers, memory is not changed and the WRERR bit defined in Register 12-5 is set as explained in **Section 13.3.8 "WRERR Bit**".

#### 4.2.5 MEMORY VIOLATION

A Memory Execution Violation Reset occurs while executing an instruction that has been fetched from outside a valid execution area, clearing the MEMV bit. Refer to **Section 8.12 "Memory Execution Violation"** for the available valid program execution areas and the PCON1 register definition (Register 8-3) for MEMV bit conditions.

| TABLE 4                      | 1-11: SPECI                                     | AL FUNCTION | REGISTER     | SUMMARY                    | BANKS 0- | 63 (CONTIN | IUED)   |           |         |                       |                            |

|------------------------------|-------------------------------------------------|-------------|--------------|----------------------------|----------|------------|---------|-----------|---------|-----------------------|----------------------------|

| Address                      | Name                                            | Bit 7       | Bit 6        | Bit 5                      | Bit 4    | Bit 3      | Bit 2   | Bit 1     | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 17                      | ank 17                                          |             |              |                            |          |            |         |           |         |                       |                            |

|                              | CPU CORE REGISTERS; see Table 4-3 for specifics |             |              |                            |          |            |         |           |         |                       |                            |

| 88Ch                         | CPUDOZE                                         | IDLEN       | DOZEN        | ROI                        | DOE      | _          | DOZE2   | DOZE1     | DOZE0   | 0000 -000             | u000 -000                  |

| 88Dh                         | OSCCON1                                         | —           |              | NOSC<2:0>                  |          |            | ND      | IV<3:0>   |         | -qqq 0000             | -qqq 0000                  |

| 88Eh                         | OSCCON2                                         | —           |              | COSC<2:0>                  |          |            | CD      | IV<3:0>   |         | -বর্বর বর্ববর         | -বর্বর বর্ববর              |

| 88Fh                         | OSCCON3                                         | CSWHOLD     | SOSCPWR      | _                          | ORDY     | NOSCR      | —       | —         | —       | 00-0 0                | 00-0 0                     |

| 890h                         | OSCSTAT                                         | EXTOR       | HFOR         | MFOR                       | LFOR     | SOR        | ADOR    | —         | PLLR    | d000 dd-0             | বর্ববুর বর-ব               |

| 891h                         | OSCEN                                           | EXTOEN      | HFOEN        | MFOEN                      | LFOEN    | SOSCEN     | ADOEN   | —         | —       | 0000 00               | 0000 00                    |

| 892h                         | OSCTUNE                                         | —           | -            |                            |          | HFT        | UN<5:0> |           |         | 10 0000               | 10 0000                    |

| 893h                         | OSCFRQ                                          | —           | -            | _                          | _        | —          |         | HFFRQ<2:0 | >       | वेर्वेवे              | ddd                        |

| 894h                         | —                                               |             |              |                            | Unimpler | nented     |         |           |         | —                     | —                          |

| 895h                         | CLKRCON                                         | CLKREN      | -            | - CLKRDC<1:0> CLKRDIV<2:0> |          |            |         |           | 0x xxxx | 0u uuuu               |                            |

| 896h                         | CLKRCLK                                         | —           | CLKRCLK<3:0> |                            |          |            |         |           | 0000    | 0000                  |                            |

| 897h<br>89Fh — Unimplemented |                                                 |             |              |                            |          |            | _       | _         |         |                       |                            |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| R/W-0/0                                                                                                                                                           | R/W-0/0                                                      | R/W-0/0                                                  | R/W-0/0   | U-0         | U-0              | U-0              | R/W-0/0      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|-----------|-------------|------------------|------------------|--------------|

| CLC4IE                                                                                                                                                            | CLC3IE                                                       | CLC2IE                                                   | CLC1IE    | —           | —                | —                | TMR1GIE      |

| bit 7                                                                                                                                                             |                                                              |                                                          |           |             |                  |                  | bit 0        |

|                                                                                                                                                                   |                                                              |                                                          |           |             |                  |                  |              |

| Legend:                                                                                                                                                           |                                                              |                                                          |           |             |                  |                  |              |

| R = Readab                                                                                                                                                        |                                                              | W = Writable                                             |           | •           | mented bit, read |                  |              |

| u = Bit is un                                                                                                                                                     | 0                                                            | x = Bit is unkr                                          |           |             | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se                                                                                                                                                   | et                                                           | '0' = Bit is cle                                         | ared      | HS = Hardwa | are set          |                  |              |

| bit 7 <b>CLC4IE:</b> CLC4 Interrupt Enable bit<br>1 = CLC4 interrupt enabled<br>0 = CLC4 interrupt disabled                                                       |                                                              |                                                          |           |             |                  |                  |              |

| bit 6                                                                                                                                                             | 1 = CLC3 i                                                   | C3 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable | b         |             |                  |                  |              |

| bit 5                                                                                                                                                             | 1 = CLC2 i                                                   | C2 Interrupt Ena<br>nterrupt enabled<br>nterrupt disable | t         |             |                  |                  |              |

| bit 4                                                                                                                                                             | 1 = CLC1 i                                                   | C1 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable | b         |             |                  |                  |              |

| bit 3-1                                                                                                                                                           | Unimpleme                                                    | nted: Read as '                                          | 0'        |             |                  |                  |              |

| bit 0 <b>TMR1GIE:</b> Timer1 Gate Interrupt Enable bit<br>1 = Enables the Timer1 gate acquisition interrupt<br>0 = Disables the Timer1 gate acquisition interrupt |                                                              |                                                          |           |             |                  |                  |              |

| s                                                                                                                                                                 | Bit PEIE of the IN<br>set to enable a<br>controlled by regis | any peripheral                                           | interrupt |             |                  |                  |              |

#### REGISTER 10-7: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

#### 13.2 FSR and INDF Access

The FSR and INDF registers allow indirect access to the PFM.

#### 13.2.1 FSR READ

With the intended address loaded into an FSR register a MOVIW instruction or read of INDF will read data from the PFM.

Reading from NVM requires one instruction cycle. The CPU operation is suspended during the read, and resumes immediately after. Read operations return a single byte of memory.

#### 13.2.2 FSR WRITE

Writing/erasing the NVM through the FSR registers (ex. MOVWI instruction) is not supported in the PIC16(L)F15356/75/76/85/86 devices.

#### 13.3 NVMREG Access

The NVMREG interface allows read/write access to all the locations accessible by FSRs, and also read/write access to the User ID locations, and read-only access to the device identification, revision, and Configuration data.

Writing or erasing of NVM via the NVMREG interface is prevented when the device is write-protected.

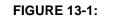

#### 13.3.1 NVMREG READ OPERATION

To read a NVM location using the NVMREG interface, the user must:

- 1. Clear the NVMREGS bit of the NVMCON1 register if the user intends to access PFM locations, or set NMVREGS if the user intends to access User ID, or Configuration locations.

- Write the desired address into the NVMADRH:NVMADRL register pair (Table 13-2).

- 3. Set the RD bit of the NVMCON1 register to initiate the read.

Once the read control bit is set, the CPU operation is suspended during the read, and resumes immediately after. The data is available in the very next cycle, in the NVMDATH:NVMDATL register pair; therefore, it can be read as two bytes in the following instructions.

NVMDATH:NVMDATL register pair will hold this value until another read or until it is written to by the user.

Upon completion, the RD bit is cleared by hardware.

#### FLASH PROGRAM MEMORY READ FLOWCHART

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSD<7:0>**: Analog Select between Analog or Digital Function on Pins RD<7:0>, respectively<sup>(1)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### REGISTER 14-29: WPUD: WEAK PULL-UP PORTD REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2   | WPUD1   | WPUD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUD<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

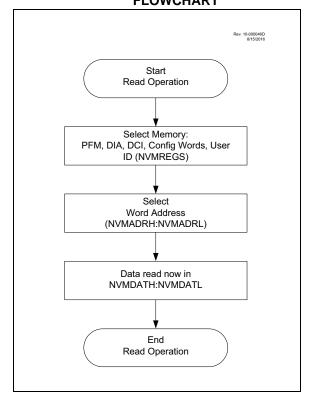

| ADC Clock P         | eriod (TAD) |                             | Device Frequency (Fosc)     |                             |                             |                               |                             |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|-----------------------------|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                         | 1 MHz                       |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>         | 2.0 μs                      |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                        | 4.0 μs                      |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                        | 8.0 μs <sup>(3)</sup>       |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                        | 16.0 μs <sup>(3)</sup>      |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <b><sup>(3)</sup></b>  | 32.0 μs <sup>(2)</sup>      |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <b><sup>(2)</sup></b> | 64.0 μs <sup>(2)</sup>      |  |

| ADCRC               | x11         | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup> |  |

#### TABLE 20-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

Note 1: See TAD parameter for ADCRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

**4:** The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the ADCRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

#### FIGURE 20-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

## 25.0 TIMER0 MODULE

The Timer0 module is an 8/16-bit timer/counter with the following features:

- 16-bit timer/counter

- 8-bit timer/counter with programmable period

- Synchronous or asynchronous operation

- Selectable clock sources

- Programmable prescaler (independent of Watchdog Timer)

- Programmable postscaler

- Operation during Sleep mode

- · Interrupt on match or overflow

- Output on I/O pin (via PPS) or to other peripherals

### 25.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

#### 25.1.1 16-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

## 25.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0, which is neither directly readable nor writable (see Figure 25-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### 25.1.2 8-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

The value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh.

Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- <u>Any device Reset Power-on Reset (POR),</u> <u>MCLR Reset, Watchdog Timer Reset (WDTR) or</u>

- Brown-out Reset (BOR)

#### 25.1.3 COUNTER MODE

In Counter mode, the prescaler is normally disabled by setting the T0CKPS bits of the T0CON1 register to '0000'. Each rising edge of the clock input (or the output of the prescaler if the prescaler is used) increments the counter by '1'.

#### 25.1.4 TIMER MODE

In Timer mode, the Timer0 module will increment every instruction cycle as long as there is a valid clock signal and the T0CKPS bits of the T0CON1 register (Register 25-2) are set to '0000'. When a prescaler is added, the timer will increment at the rate based on the prescaler value.

#### 25.1.5 ASYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is set (T0ASYNC = '1'), the counter increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows the counter to continue operation during Sleep mode provided that the clock also continues to operate during Sleep.

#### 25.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system oscillator (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

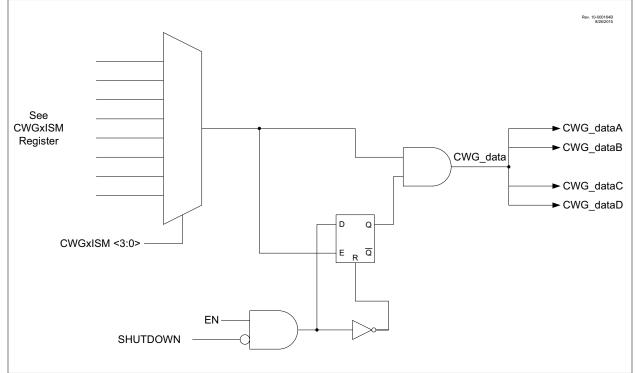

#### 30.1.4 STEERING MODES

In Steering modes, the data input can be steered to any or all of the four CWG output pins. In Synchronous Steering mode, changes to steering selection registers take effect on the next rising input.

In Non-Synchronous mode, steering takes effect on the next instruction cycle. Additional details are provided in **Section 30.9 "CWG Steering Mode"**.

#### 30.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the CS bit of the CWG1CLKCON register.

#### 30.9 CWG Steering Mode

In Steering mode (MODE = 00x), the CWG allows any combination of the CWG1x pins to be the modulated signal. The same signal can be simultaneously available on multiple pins, or a fixed-value output can be presented.

When the respective STRx bit of CWG1OCON0 is '0', the corresponding pin is held at the level defined. When the respective STRx bit of CWG1OCON0 is '1', the pin is driven by the input data signal. The user can assign the input data signal to one, two, three, or all four output pins.

The POLx bits of the CWG1CON1 register control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 30.10** "**Auto-Shutdown**". An auto-shutdown event will only affect pins that have STRx = 1.

#### 30.9.1 STEERING SYNCHRONIZATION

Changing the MODE bits allows for two modes of steering, synchronous and asynchronous.

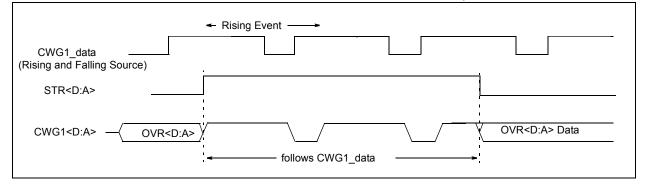

When MODE = 000, the steering event is asynchronous and will happen at the end of the instruction that writes to STRx (that is, immediately). In this case, the output signal at the output pin may be an incomplete waveform. This can be useful for immediately removing a signal from the pin.

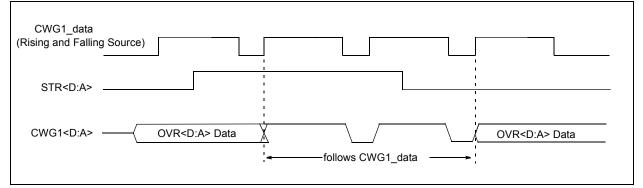

When MODE = 001, the steering update is synchronous and occurs at the beginning of the next rising edge of the input data signal. In this case, steering the output on/off will always produce a complete waveform.

Figure 30-10 and Figure 30-11 illustrate the timing of asynchronous and synchronous steering, respectively.

#### FIGURE 30-11: EXAMPLE OF STEERING EVENT (MODE<2:0> = 001)

#### 30.13 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripherals are shown in **Section 1.1 "Register and Bit Naming Conventions"**.

#### REGISTER 30-1: CWG1CON0: CWG1 CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> | —   | —   | —   |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     |         |           | bit 0   |

| Legend:                     |                      |                                                       |

|-----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by hard | ware                 | HS = Bit is set by hardware                           |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged        | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set            | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | EN: CWG1 Enable bit<br>1 = Module is enabled                                                                                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0 = Module is disabled                                                                                                                                                                                                                                                                                                                                                                  |

| bit 6   | LD: CWG1 Load Buffer bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                |

|         | <ul><li>1 = Buffers to be loaded on the next rising/falling event</li><li>0 = Buffers not loaded</li></ul>                                                                                                                                                                                                                                                                              |

| bit 5-3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0 | MODE<2:0>: CWG1 Mode bits<br>111 = Reserved<br>110 = Reserved<br>101 = CWG outputs operate in Push-Pull mode<br>100 = CWG outputs operate in Half-Bridge mode<br>011 = CWG outputs operate in Reverse Full-Bridge mode<br>010 = CWG outputs operate in Forward Full-Bridge mode<br>001 = CWG outputs operate in Synchronous Steering mode<br>000 = CWG outputs operate in Steering mode |

**Note 1:** This bit can only be set after EN = 1 and cannot be set in the same instruction that EN is set.

| U-0                                                                | U-0                                                              | R-x                                    | U-0        | R/W-0/0        | R/W-0/0       | R/W-0/0          | R/W-0/0      |

|--------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------|------------|----------------|---------------|------------------|--------------|

|                                                                    | —                                                                | IN                                     |            | POLD           | POLC          | POLB             | POLA         |

| bit 7                                                              |                                                                  |                                        |            |                |               |                  | bit C        |

|                                                                    |                                                                  |                                        |            |                |               |                  |              |

| Legend:                                                            |                                                                  |                                        |            |                |               |                  |              |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                  |                                        |            |                |               |                  |              |

| u = Bit is un                                                      | changed                                                          | x = Bit is unkr                        | nown       | -n/n = Value a | at POR and BO | R/Value at all c | other Resets |

| '1' = Bit is se                                                    | = Bit is set '0' = Bit is cleared q = Value depends on condition |                                        |            |                |               |                  |              |

|                                                                    |                                                                  |                                        |            |                |               |                  |              |

| bit 7-6 Unimplemented: Read as '0'                                 |                                                                  |                                        |            |                |               |                  |              |

| bit 5                                                              | IN: CWG Input Value bit                                          |                                        |            |                |               |                  |              |

| bit 4                                                              | Unimplem                                                         | ented: Read as '                       | 0'         |                |               |                  |              |

| bit 3                                                              | POLD: CW                                                         | /G1D Output Pola                       | arity bit  |                |               |                  |              |

|                                                                    | 1 = Signal                                                       | output is inverted                     | l polarity |                |               |                  |              |

|                                                                    | 0 = Signal                                                       | output is normal                       | polarity   |                |               |                  |              |

| bit 2                                                              | POLC: CW                                                         | /G1C Output Pola                       | arity bit  |                |               |                  |              |

|                                                                    | 0                                                                | output is inverted                     |            |                |               |                  |              |

| 0 = Signal output is normal polarity                               |                                                                  |                                        |            |                |               |                  |              |

| bit 1 POLB: CWG1B Output Polarity bit                              |                                                                  |                                        |            |                |               |                  |              |

|                                                                    |                                                                  | 1 = Signal output is inverted polarity |            |                |               |                  |              |

|                                                                    | 0 = Signal                                                       | output is normal                       | polarity   |                |               |                  |              |

| bit 0                                                              | POLA: CW                                                         | /G1A Output Pola                       | rity bit   |                |               |                  |              |

|                                                                    | 1 = Signal                                                       | output is inverted                     | l polarity |                |               |                  |              |

#### **REGISTER 30-2:** CWG1CON1: CWG1 CONTROL REGISTER 1

0 = Signal output is normal polarity

# PIC16(L)F15356/75/76/85/86

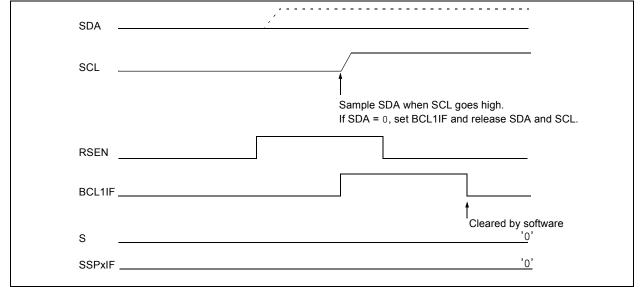

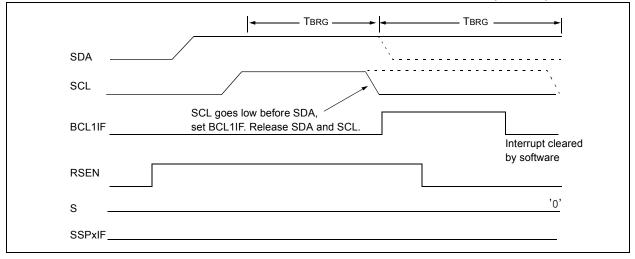

# 32.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 32-36). If SDA is sampled high, the BRG is reloaded and begins

counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 32-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 32-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### **REGISTER 32-2:** SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0         | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                       | R/W-0/0                                                                                                                                               | R/W-0/0                                                                                                                                                                                               | R/W-0/0                                                                                                                                     | R/W-0/0                                    | R/W-0/0                                        | R/W-0/0                                      |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------|----------------------------------------------|--|

| WCOL               | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                                             | SSPEN                                                                                                                                                 | CKP                                                                                                                                                                                                   |                                                                                                                                             | SSPM                                       | 1<3:0>                                         |                                              |  |

| pit 7              |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                       |                                                                                                                                                                                                       | -                                                                                                                                           |                                            |                                                | bit                                          |  |

| ogondu             |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                       |                                                                                                                                                                                                       |                                                                                                                                             |                                            |                                                |                                              |  |

| <b>_egend:</b>     |                                                                                                                                                                                                                                                                                                                                  | W - Writchlo hit                                                                                                                                      |                                                                                                                                                                                                       |                                                                                                                                             | ad hit road as 'O'                         |                                                |                                              |  |

| R = Readable bit   |                                                                                                                                                                                                                                                                                                                                  | W = Writable bit                                                                                                                                      | _                                                                                                                                                                                                     | U = Unimplement                                                                                                                             |                                            |                                                |                                              |  |

| u = Bit is unchang | gea                                                                                                                                                                                                                                                                                                                              | x = Bit is unknow                                                                                                                                     |                                                                                                                                                                                                       | -n/n = Value at POR and BOR/Value at all other Resets                                                                                       |                                            |                                                |                                              |  |

| 1' = Bit is set    |                                                                                                                                                                                                                                                                                                                                  | '0' = Bit is cleared                                                                                                                                  | 1                                                                                                                                                                                                     | HS = Bit is set by                                                                                                                          | hardware                                   | C = User cleared                               |                                              |  |

| bit 7              |                                                                                                                                                                                                                                                                                                                                  | ollision Detect bit (Tr<br>3UF register is written<br>n                                                                                               |                                                                                                                                                                                                       |                                                                                                                                             | word (must be cleare                       | ed in software)                                |                                              |  |

| bit 6              | In SPI mode:<br>1 = A new byte<br>Overflow c<br>setting ove<br>SSPxBUF<br>0 = No overflov<br>In I <sup>2</sup> C mode:<br>1 = A byte is m                                                                                                                                                                                        | eceived while the S<br>leared in software).                                                                                                           | SSPxBUF registe<br>e mode. In Slave<br>e, the overflow bit i<br>ared in software).                                                                                                                    | mode, the user must<br>s not set since each r                                                                                               | read the SSPxBUF,<br>new reception (and tr | even if only transmi<br>ansmission) is initiat | tting data, to avoid<br>ed by writing to the |  |

| bit 5              | In both modes, v<br>In <u>SPI mode:</u><br>1 = Enables se<br>0 = Disables s<br>In I <sup>2</sup> C mode:<br>1 = Enables the                                                                                                                                                                                                      | onous Serial Port Er<br>when enabled, the fo<br>erial port and configur<br>erial port and config<br>e serial port and config<br>erial port and config | bllowing pins mus<br>res SCK, SDO, SI<br>ures these pins a<br>igures the SDA ar                                                                                                                       | DI and SS as the sou<br>as I/O port pins<br>ad SCL pins as the so                                                                           | rce of the serial port                     | pins <sup>(2)</sup>                            |                                              |  |

| bit 4              | 0 = Idle state for<br>In I <sup>2</sup> C Slave mod<br>SCL release cor<br>1 = Enable clock                                                                                                                                                                                                                                       | clock is a high leve<br>clock is a low level<br><u>de:</u><br>htrol<br>(<br>low (clock stretch). (<br>ode:                                            |                                                                                                                                                                                                       | lata setup time.)                                                                                                                           |                                            |                                                |                                              |  |

| bit 3-0            | 1111 = I <sup>2</sup> C Slav<br>1110 = I <sup>2</sup> C Slav<br>1101 = Reserve<br>1100 = Reserve<br>1001 = I <sup>2</sup> C firmw<br>1010 = SPI Mas<br>1001 = Reserve<br>1000 = I <sup>2</sup> C Mas<br>0111 = I <sup>2</sup> C Slav<br>0110 = SPI Slav<br>0100 = SPI Slav<br>0101 = SPI Mas<br>0011 = SPI Mas<br>0010 = SPI Mas | ed<br>ware controlled Mas<br>ster mode, clock = F                                                                                                     | ess with Start and<br>ss with Start and<br>ter mode (slave i<br>osc/(4 * (SSPxAl<br>osc / (4 * (SSPxAl<br>ess<br>ss<br>K pin, <u>SS</u> pin coi<br>X pin, SS pin coi<br>2_match/2<br>osc/64<br>osc/66 | d Stop bit interrupts e<br>Stop bit interrupts e<br>dle)<br>DD+1)) <sup>(5)</sup><br>(DD+1)) <sup>(4)</sup><br>ntrol disabled, <u>SS</u> ca | nabled                                     | n                                              |                                              |  |

| 2: Wh<br>Rxy       | Master mode, the ov                                                                                                                                                                                                                                                                                                              | verflow bit is not set<br>bins must be properl<br>bins.                                                                                               | since each new r<br>y configured as i                                                                                                                                                                 | nput or output. Use                                                                                                                         | SSPxSSPPS, SSP>                            | CLKPPS, SSPxDA                                 | TPPS, and                                    |  |

- When enabled, the SDA and SCL pins must be configured as inputs. Use SSPxCLKPPS, SSPxDATPPS, and RxyPPS to select the pins.

SSPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

SSPxADD value of '0' is not supported. Use SSPM = 0000 instead.

|  | REGISTER 32-4: | SSPxCON3: SSPx CONTROL REGISTER 3 |

|--|----------------|-----------------------------------|

|--|----------------|-----------------------------------|

| R-0/0          | R/W-0/0                                                                                                                                                     | R/W-0/0                                 | R/W-0/0                       | R/W-0/0                                                                                                           | R/W-0/0              | R/W-0/0             | R/W-0/0          |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|------------------|--|--|--|

| ACKTIM         | <sup>3)</sup> PCIE                                                                                                                                          | SCIE                                    | BOEN                          | SDAHT                                                                                                             | SBCDE                | AHEN                | DHEN             |  |  |  |

| bit 7          | <u>.</u>                                                                                                                                                    |                                         | <u> </u>                      |                                                                                                                   | •                    |                     | bit              |  |  |  |

|                |                                                                                                                                                             |                                         |                               |                                                                                                                   |                      |                     |                  |  |  |  |

| Legend:        |                                                                                                                                                             |                                         |                               |                                                                                                                   |                      |                     |                  |  |  |  |

| R = Readab     | ole bit                                                                                                                                                     | W = Writable b                          | bit                           | U = Unimplem                                                                                                      | ented bit, read as   | ʻ0'                 |                  |  |  |  |

| u = Bit is ur  | changed                                                                                                                                                     | x = Bit is unkn                         | own                           | -n/n = Value at                                                                                                   | POR and BOR/V        | alue at all other l | Resets           |  |  |  |

| '1' = Bit is s | et                                                                                                                                                          | '0' = Bit is clea                       | red                           |                                                                                                                   |                      |                     |                  |  |  |  |

|                |                                                                                                                                                             |                                         | 0                             | (2)                                                                                                               |                      |                     |                  |  |  |  |

| bit 7          |                                                                                                                                                             | nowledge Time S                         |                               |                                                                                                                   | oth curr             |                     |                  |  |  |  |

|                |                                                                                                                                                             |                                         |                               | edge sequence, set on 8 <sup>th</sup> falling edge of SCL clock<br>ed on 9 <sup>TH</sup> rising edge of SCL clock |                      |                     |                  |  |  |  |

| bit 6          |                                                                                                                                                             | ondition Interrupt                      |                               |                                                                                                                   |                      |                     |                  |  |  |  |

|                |                                                                                                                                                             | errupt on detection                     |                               |                                                                                                                   |                      |                     |                  |  |  |  |

|                |                                                                                                                                                             | ction interrupts ar                     |                               |                                                                                                                   |                      |                     |                  |  |  |  |

| bit 5          | SCIE: Start Condition Interrupt Enable bit (I <sup>2</sup> C mode only)                                                                                     |                                         |                               |                                                                                                                   |                      |                     |                  |  |  |  |

|                |                                                                                                                                                             | errupt on detection ction interrupts ar |                               | start conditions                                                                                                  |                      |                     |                  |  |  |  |

| oit 4          |                                                                                                                                                             | Overwrite Enabl                         |                               |                                                                                                                   |                      |                     |                  |  |  |  |

| 511 4          | In SPI Slave n                                                                                                                                              |                                         |                               |                                                                                                                   |                      |                     |                  |  |  |  |

|                |                                                                                                                                                             |                                         |                               |                                                                                                                   | shifted in ignoring  |                     |                  |  |  |  |

|                |                                                                                                                                                             | •                                       |                               |                                                                                                                   | egister already se   | et, SSPOV bit of    | the SSPxCON      |  |  |  |

|                | · · ·                                                                                                                                                       | ster is set, and the<br>mode and SPI M  | •                             | dated                                                                                                             |                      |                     |                  |  |  |  |