Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15375-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

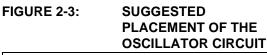

# 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, refer to these Microchip Application Notes, available at the corporate website (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

# 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

| Bank Offset<br>Bank 0-Bank 63 | Name   | Bit 7                     | Bit 6                    | Bit 5                                                    | Bit 4       | Bit 3       | Bit 2      | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------------------|--------|---------------------------|--------------------------|----------------------------------------------------------|-------------|-------------|------------|-----------|-----------|-----------------------|----------------------------|

| All Banks                     |        |                           |                          |                                                          |             |             |            |           |           |                       |                            |

| x00h or x80h                  | INDF0  | Addressing<br>physical re | this location<br>gister) | n uses cont                                              | ents of FSF | ROH/FSROL   | to address | data memo | ry (not a | XXXX XXXX             | XXXX XXXX                  |

| x01h or x81h                  | INDF1  | Addressing<br>physical re | this location<br>gister) | n uses cont                                              | ents of FSF | R1H/FSR1L   | to address | data memo | ry (not a | xxxx xxxx             | xxxx xxxx                  |

| x02h or x82h                  | PCL    |                           |                          |                                                          | PC          | L           |            |           |           | 0000 0000             | 0000 0000                  |

| x03h or x83h                  | STATUS | _                         | _                        | _                                                        | TO          | PD          | Z          | DC        | С         | 1 1000                | q quuu                     |

| x04h or x84h                  | FSR0L  | FSR0L                     | Indirect Da              | ta Memory                                                | Address 0 I | _ow Pointer |            |           |           | 0000 0000             | uuuu uuuu                  |

| x05h or x85h                  | FSR0H  | FSR0H                     | Indirect Da              | ta Memory                                                | Address 0 I | High Pointe | r          |           |           | 0000 0000             | 0000 0000                  |

| x06h or x86h                  | FSR1L  | FSR1L                     | Indirect Da              | ndirect Data Memory Address 1 Low Pointer                |             |             |            |           |           | 0000 0000             | uuuu uuuu                  |

| x07h or x87h                  | FSR1H  | FSR1H                     | Indirect Da              | ndirect Data Memory Address 1 High Pointer               |             |             |            |           | 0000 0000 | 0000 0000             |                            |

| x08h or x88h                  | BSR    | _                         | _                        | — BSR<5:0>                                               |             |             |            |           | 00 0000   | 00 0000               |                            |

| x09h or x89h                  | WREG   | Working Re                | egister                  | gister                                                   |             |             |            |           | 0000 0000 | uuuu uuuu             |                            |

| x0Ah or x8Ah                  | PCLATH | _                         | Write Buffe              | Nrite Buffer for the upper 7 bits of the Program Counter |             |             |            |           |           | -000 0000             | -000 0000                  |

| x0Bh or x8Bh                  | INTCON | GIE                       | PEIE                     | —                                                        | _           | —           | _          | —         | INTEDG    | 001                   | 001                        |

TABLE 4-10:

SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (ALL BANKS)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: These Registers can be accessed from any bank.

# 5.2 Register Definitions: Configuration Words

| REGISTER          | 5-1: CO                                                                                                                                                                                                                                                     | NFIGURATIO                                                                                                | N WORD 1:                                                                          | OSCILLATO                                                                  | RS                                                            |                                |                     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------|---------------------|

|                   |                                                                                                                                                                                                                                                             | R/P-1                                                                                                     | U-1                                                                                | R/P-1                                                                      | U-1                                                           | U-1                            | R/P-1               |

|                   |                                                                                                                                                                                                                                                             | FCMEN                                                                                                     | _                                                                                  | CSWEN                                                                      | _                                                             | _                              | CLKOUTEN            |

|                   |                                                                                                                                                                                                                                                             | bit 13                                                                                                    |                                                                                    |                                                                            |                                                               |                                | bit 8               |

| 11.1              | R/P-1                                                                                                                                                                                                                                                       | R/P-1                                                                                                     | R/P-1                                                                              | 11.1                                                                       | R/P-1                                                         | R/P-1                          | R/P-1               |

| U-1               |                                                                                                                                                                                                                                                             |                                                                                                           |                                                                                    | U-1                                                                        |                                                               |                                |                     |

|                   | RSTOSC2                                                                                                                                                                                                                                                     | RSTOSC1                                                                                                   | RSTOSC0                                                                            | —                                                                          | FEXTOSC2                                                      | FEXTOSC1                       | FEXTOSC0            |

| bit 7             |                                                                                                                                                                                                                                                             |                                                                                                           |                                                                                    |                                                                            |                                                               |                                | bit (               |

| Legend:           |                                                                                                                                                                                                                                                             |                                                                                                           |                                                                                    |                                                                            |                                                               |                                |                     |

| R = Readable      | e bit                                                                                                                                                                                                                                                       | P = Programma                                                                                             | able bit                                                                           | x = Bit is unkno                                                           | own                                                           | U = Unimpleme<br>'1'           | nted bit, read as   |

| '0' = Bit is clea | ared                                                                                                                                                                                                                                                        | '1' = Bit is set                                                                                          |                                                                                    | W = Writable b                                                             | it                                                            | n = Value when l<br>Erase      | blank or after Bull |

| bit 13            | FCMEN: Fail-<br>1 = FSCM tir<br>0 = FSCM tir                                                                                                                                                                                                                |                                                                                                           | or Enable bit                                                                      |                                                                            |                                                               |                                |                     |

| bit 12            | Unimplement                                                                                                                                                                                                                                                 | ed: Read as '1'                                                                                           |                                                                                    |                                                                            |                                                               |                                |                     |

| bit 11            | 1 = Writing to                                                                                                                                                                                                                                              | k Switch Enable<br>NOSC and NDI<br>C and NDIV bits                                                        | / is allowed                                                                       | ged by user soft                                                           | ware                                                          |                                |                     |

| bit 10-9          | Unimplement                                                                                                                                                                                                                                                 | ed: Read as '1'                                                                                           |                                                                                    |                                                                            |                                                               |                                |                     |

| bit 8             | If FEXTOSC =<br>1 = CLKOUT                                                                                                                                                                                                                                  | Clock Out Enable<br><u>EC (high, mid or</u><br>function is disable<br>function is enable<br>pred.         | <u>low) or Not En</u><br>ed; I/O or oscill                                         | ator function on (                                                         |                                                               |                                |                     |

| bit 7             | Unimplement                                                                                                                                                                                                                                                 | ed: Read as '1'                                                                                           |                                                                                    |                                                                            |                                                               |                                |                     |

| bit 6-4           | This value is t           111 =         EXTC           110 =         HFIN           101 =         LFIN           100 =         SOSC           011 =         Reserved           010 =         EXTC           001 =         EXTC           001 =         EXTC | OSC operating per<br>TOSC with HFFR<br>TOSC                                                               | value for COSC<br>FEXTOSC bits<br>Q = 3 ' b010<br>with EXTOSC of<br>with EXTOSC of | and selects the<br>(device manufa<br>pperating per FE<br>pperating per FE  | cturing default)<br>XTOSC bits                                | ed by user softwa              | re.                 |

| bit 3             | Unimplement                                                                                                                                                                                                                                                 | ed: Read as '1'                                                                                           |                                                                                    |                                                                            |                                                               |                                |                     |

| bit 2-0           | 111 =         EC (E           110 =         EC (E           101 =         EC (E           100 =         Oscill           011 =         Reset           010 =         HS (C           001 =         XT (C                                                    | External Clock) for<br>External Clock) be<br>ator not enabled<br>rved (do not use)<br>Crystal oscillator) | ove 8 MHz; PF<br>100 kHz to 8 M<br>low 100 kHz<br>above 4 MHz; F<br>above 100 kHz, | M set to high po<br>IHz; PFM set to<br>PFM set to high p<br>below 4 MHz; P | wer (device manu<br>medium power<br>power<br>FM set to mediun | ifacturing default)<br>n power |                     |

# REGISTER 5-1: CONFIGURATION WORD 1: OSCILLATORS

# 11.1.2 INTERRUPTS DURING DOZE

If an interrupt occurs and the Recover-on-Interrupt bit is clear (ROI = 0) at the time of the interrupt, the Interrupt Service Routine (ISR) continues to execute at the rate selected by DOZE<2:0>. Interrupt latency is extended by the DOZE<2:0> ratio.

If an interrupt occurs and the ROI bit is set (ROI = 1) at the time of the interrupt, the DOZEN bit is cleared and the CPU executes at full speed. The prefetched instruction is executed and then the interrupt vector sequence is executed. In Figure 11-1, the interrupt occurs during the  $2^{nd}$  instruction cycle of the Doze period, and immediately brings the CPU out of Doze. If the Doze-On-Exit (DOE) bit is set (DOE = 1) when the RETFIE operation is executed, DOZEN is set, and the CPU executes at the reduced rate based on the DOZE<2:0> ratio.

# 11.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0). If the SLEEP instruction is executed while the IDLEN bit is set (IDLEN = 1), the CPU will enter the IDLE mode (Section 11.2.3 "Low-Power Sleep Mode").

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The  $\overline{PD}$  bit of the STATUS register is cleared

- 3. The  $\overline{\text{TO}}$  bit of the STATUS register is set

- 4. CPU Clock and System Clock

- 5. 31 kHz LFINTOSC, HFINTOSC and SOSC are unaffected and peripherals using them may continue operation in Sleep.

- 6. ADC is unaffected if the dedicated FRC oscillator is selected the conversion will be left abandoned if FOSC is selected and ADRES will have an incorrect value

- 7. I/O ports maintain the status they had before Sleep was executed (driving high, low, or high-impedance). This does not apply in the case of any asynchronous peripheral which is active and may affect the I/O port value

- 8. Resets other than WDT are not affected by Sleep mode

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or VSS externally to avoid switching currents caused by floating inputs.

Any module with a clock source that is not Fosc can be enabled. Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module", Section 18.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

### 11.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled.

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled.

- 5. Any external interrupt.

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 8.12 "Memory Execution Violation**".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

# 12.7 Register Definitions: Windowed Watchdog Timer Control

# REGISTER 12-1: WDTCON0: WATCHDOG TIMER CONTROL REGISTER 0

| U-0   | U-0 | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0 |

|-------|-----|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|---------|

| —     | -   |                                        |                                        | WDTPS<4:0>(1)                          |                                        |                                        | SWDTEN  |

| bit 7 |     |                                        |                                        |                                        |                                        |                                        | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| 1' = Bit is set | '0' = Bit is cleared q = Value depends on condition                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------|

|                 |                                                                                                                        |

| bit 7-6         | Unimplemented: Read as '0'                                                                                             |

| bit 5-1         | WDTPS<4:0>: Watchdog Timer Prescale Select bits <sup>(1)</sup>                                                         |

|                 | Bit Value = Prescale Rate                                                                                              |

|                 | 11111 = Reserved. Results in minimum interval (1:32)                                                                   |

|                 | •                                                                                                                      |

|                 | •                                                                                                                      |

|                 | •                                                                                                                      |

|                 | 10011 = Reserved. Results in minimum interval (1:32)                                                                   |

|                 | 10010 = 1:8388608 (2 <sup>23</sup> ) (Interval 256s nominal)                                                           |

|                 | 10001 = 1:4194304 (2 <sup>22</sup> ) (Interval 128s nominal)                                                           |

|                 | 10000 = 1:2097152 ( $2^{21}_{20}$ ) (Interval 64s nominal)                                                             |

|                 | $01111 = 1:1048576 (2^{20}) $ (Interval 32s nominal)                                                                   |

|                 | $01110 = 1:524288 (2^{19}) (Interval 16s nominal)$                                                                     |

|                 | 01101 = 1:262144 (2 <sup>18</sup> ) (Interval 8s nominal)<br>01100 = 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal) |

|                 | 01001 = 1.65536 (Interval 2s nominal) (Reset value)                                                                    |

|                 | 01010 = 1:32768 (Interval 1s nominal)                                                                                  |

|                 | 01001 = 1:16384 (Interval 512 ms nominal)                                                                              |

|                 | 01000 = 1:8192 (Interval 256 ms nominal)                                                                               |

|                 | 00111 = 1:4096 (Interval 128 ms nominal)                                                                               |

|                 | 00110 = 1:2048 (Interval 64 ms nominal)                                                                                |

|                 | 00101 = 1:1024 (Interval 32 ms nominal)                                                                                |

|                 | 00100 = 1:512 (Interval 16 ms nominal)<br>00011 = 1:256 (Interval 8 ms nominal)                                        |

|                 | 00011 = 1.230 (Interval 4 ms nominal)<br>00010 = 1.128 (Interval 4 ms nominal)                                         |

|                 | 00001 = 1:64 (Interval 2 ms nominal)                                                                                   |

|                 | 00000 = 1:32 (Interval 1 ms nominal)                                                                                   |

| bit 0           | SWDTEN: Software Enable/Disable for Watchdog Timer bit                                                                 |

|                 | If WDTE<1:0> = 1x:                                                                                                     |

|                 | This bit is ignored.                                                                                                   |

|                 | If WDTE<1:0> = 01:                                                                                                     |

|                 | 1 = WDT is turned on                                                                                                   |

|                 | 0 = WDT is turned off                                                                                                  |

|                 | $\frac{\text{If WDTE} < 1:0> = 00:}{\text{This bit is ignored.}}$                                                      |

|                 | -                                                                                                                      |

| Note 1. Tin     | nes are approximate_WDT time is based on 31 kHz LEINTOSC                                                               |

- **Note 1:** Times are approximate. WDT time is based on 31 kHz LFINTOSC.

- 2: When WDTCPS <4:0> in CONFIG3 = 11111, the Reset value of WDTPS<4:0> is 01011. Otherwise, the Reset value of WDTPS<4:0> is equal to WDTCPS<4:0> in CONFIG3.

- 3: When WDTCPS <4:0> in CONFIG3  $\neq$  11111, these bits are read-only.

| W-0/0                             | W-0/0                                  | W-0/0             | W-0/0        | W-0/0            | W-0/0         | W-0/0            | W-0/0        |

|-----------------------------------|----------------------------------------|-------------------|--------------|------------------|---------------|------------------|--------------|

|                                   |                                        |                   | NVMC         | ON2<7:0>         |               |                  |              |

| bit 7                             |                                        |                   |              |                  |               |                  | bit 0        |

|                                   |                                        |                   |              |                  |               |                  |              |

| Legend:                           |                                        |                   |              |                  |               |                  |              |

| R = Readable bit W = Writable bit |                                        | oit               | U = Unimpler | nented bit, read | l as '0'      |                  |              |

| S = Bit can only b                | Bit can only be set x = Bit is unknown |                   | own          | -n/n = Value a   | at POR and BO | R/Value at all c | other Resets |

| '1' = Bit is set                  |                                        | '0' = Bit is clea | red          |                  |               |                  |              |

## REGISTER 13-6: NVMCON2: NONVOLATILE MEMORY CONTROL 2 REGISTER

bit 7-0 **NVMCON2<7:0>:** Flash Memory Unlock Pattern bits To unlock writes, a 55h must be written first followed by an AAh before setting the WR bit of the NVMCON1 register. The value written to this register is used to unlock the writes.

TABLE 13-5: SUMMARY OF REGISTERS ASSOCIATED WITH NONVOLATILE MEMORY (NVM)

| Name    | Bit 7 | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on Page |

|---------|-------|--------------|-------|--------|-------|---------|-------|--------|---------------------|

| INTCON  | GIE   | PEIE         | —     | —      | —     | —       | —     | INTEDG | 146                 |

| PIE7    | —     | —            | NVMIE | NCO1IE | —     | —       | —     | CWG1IE | 154                 |

| PIR7    | _     | _            | NVMIF | NCO1IF | _     | _       | _     | CWG1IF | 162                 |

| NVMCON1 | _     | NVMREGS      | LWLO  | FREE   | WRERR | WREN    | WR    | RD     | 195                 |

| NVMCON2 |       | NVMCON2<7:0> |       |        |       |         |       |        | 196                 |

| NVMADRL |       | NVMADR<7:0>  |       |        |       |         |       |        | 194                 |

| NVMADRH | _(1)  | NVMADR<14:8> |       |        |       |         |       | 194    |                     |

| NVMDATL |       | NVMDAT<7:0>  |       |        |       |         |       | 194    |                     |

| NVMDATH |       | _            |       |        | NVMDA | T<13:8> |       |        | 194                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by NVM.

**Note 1:** Unimplemented, read as '1'.

# PIC16(L)F15356/75/76/85/86

# **REGISTER 14-39: SLRCONE: PORTE SLEW RATE CONTROL REGISTER<sup>(1)</sup>**

|                                             | Logondy |     |     |     |     |         |         |         |

|---------------------------------------------|---------|-----|-----|-----|-----|---------|---------|---------|

|                                             |         |     |     |     |     |         |         |         |

|                                             | bit 7   |     |     |     |     |         |         | bit 0   |

| U-0 U-0 U-0 U-0 U-0 R/W-1/1 R/W-1/1 R/W-1/1 | —       | —   | _   | _   | _   | SLRE2   | SLRE1   | SLRE0   |

|                                             | U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

| Legend |  |

|--------|--|

|--------|--|

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as '0'             |

|---------|----------------------------------------|

| bit 2-0 | SLRE<2:0>: PORTE Slew Rate Enable bits |

|         | For RE<2:0> pins, respectively         |

|         | 1 = Port pin slew rate is limited      |

|         | 0 = Port pin slews at maximum rate     |

Note 1: Present on PIC16(L)F15375/76/85/86 only.

#### **REGISTER 14-40: INLVLE: PORTE INPUT LEVEL CONTROL REGISTER**

| U-0   | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1                | R/W-1/1                | R/W-1/1                |

|-------|-----|-----|-----|---------|------------------------|------------------------|------------------------|

| —     | _   | _   | —   | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> |

| bit 7 |     |     |     |         |                        |                        | bit 0                  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 3-0 INLVLE<3:0>: PORTE Input Level Select bits For RE<3:0> pins, 1 = ST input used for PORT reads and interrupt-on-change 0 = TTL input used for PORT reads and interrupt-on-change

Note 1: Present on PIC16(L)F15375/76/85/86 only.

# TABLE 14-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Register<br>on Page |

|-----------------------|-------|-------|-------|-------|---------|------------------------|------------------------|------------------------|---------------------|

| PORTE                 | —     |       |       |       | RE3     | RE2 <sup>(1)</sup>     | RE1 <sup>(1)</sup>     | RE0 <sup>(1)</sup>     | 222                 |

| TRISE                 | —     | —     | _     | _     | (2)     | TRISE2 <sup>(1)</sup>  | TRISE2 <sup>(1)</sup>  | TRISE2 <sup>(1)</sup>  | 222                 |

| LATE <sup>(1)</sup>   | —     | —     |       |       |         | LATE2                  | LATE2                  | LATE2                  | 223                 |

| ANSELE <sup>(1)</sup> | —     | —     | -     | -     | -       | ANSE2                  | ANSE1                  | ANSE0                  | 217                 |

| WPUE                  | —     | —     |       |       | WPUE3   | WPUE2 <sup>(1)</sup>   | WPUE1 <sup>(1)</sup>   | WPUE0 <sup>(1)</sup>   | 224                 |

| ODCONE <sup>(1)</sup> | —     | —     | -     | -     | -       | ODCE2                  | ODCE1                  | ODCE0                  | 224                 |

| SLRCONE               | _     | _     | _     | _     | SLRE3   | SLRE2 <sup>(1)</sup>   | SLRE1 <sup>(1)</sup>   | SLRE0 <sup>(1)</sup>   | 225                 |

| INLVLE                | —     |       |       |       | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> | 225                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Present only in PIC16(L)F15375/76/85/86.

2: Unimplemented, read as '1'

#### TABLE 14-7: SUMMARY OF CONFIGURATION WORD WITH PORTE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         | _       | DEBUG    | STVREN   | PPS1WAY  | ZCDDIS   | BORV    |         | 102                 |

| CONFIG2 | 7:0  | BOREN   | l <1:0> | LPBOREN  |          |          | _        | PWRTE   | MCLRE   | 103                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTE.

# TABLE 15-5:PPS OUTPUT SIGNAL<br/>ROUTING OPTIONS<br/>(PIC16(L)F15356)

| (FICTO(E)) 15550) |                    |       |                      |         |  |  |

|-------------------|--------------------|-------|----------------------|---------|--|--|

| Output<br>Signal  | RxyPPS<br>Register | Rema  | ppable to I<br>PORTx | Pins of |  |  |

| Name              | Value              | PI    | 356                  |         |  |  |

|                   |                    | PORTA | PORTB                | PORTC   |  |  |

| CLKR              | 0x1B               |       | ٠                    | •       |  |  |

| NCO10UT           | 0x1A               | •     |                      | •       |  |  |

| TMR0              | 0x19               |       | ٠                    | •       |  |  |

| SDO2/SDA2         | 0x18               |       | ٠                    | •       |  |  |

| SCK2/SCL2         | 0x17               |       | •                    | •       |  |  |

| SDO1/SDA1         | 0x16               |       | •                    | •       |  |  |

| SCK1/SCL1         | 0x15               |       | •                    | •       |  |  |

| C2OUT             | 0x14               | •     |                      | •       |  |  |

| C1OUT             | 0x13               | •     |                      | •       |  |  |

| DT2               | 0x12               |       | •                    | •       |  |  |

| TX2/CK2           | 0x11               |       | •                    | •       |  |  |

| DT1               | 0x10               |       | •                    | •       |  |  |

| TX1/CK1           | 0x0F               |       | •                    | •       |  |  |

| PWM6OUT           | 0x0E               | •     |                      | •       |  |  |

| PWM5OUT           | 0x0D               | •     |                      | •       |  |  |

| PWM4OUT           | 0x0C               |       | ٠                    | •       |  |  |

| PWM3OUT           | 0x0B               |       | ٠                    | •       |  |  |

| CCP2              | 0x0A               |       | ٠                    | •       |  |  |

| CCP1              | 0x09               |       | •                    | •       |  |  |

| CWG1D             | 0x08               |       | •                    | •       |  |  |

| CWG1C             | 0x07               |       | ٠                    | •       |  |  |

| CWG1B             | 0x06               |       | •                    | •       |  |  |

| CWG1A             | 0x05               |       | •                    | •       |  |  |

| CLC4OUT           | 0x04               |       | ٠                    | •       |  |  |

| CLC3OUT           | 0x03               |       | •                    | •       |  |  |

| CLC2OUT           | 0x02               | •     |                      | •       |  |  |

| CLC1OUT           | 0x01               | •     |                      | •       |  |  |

| U-0                                     | U-0 | R/W/HS-0/0 | R/W/HS-0/0                                            | R/W/HS-0/0                         | R/W/HS-0/0 | R/W/HS-0/0            | R/W/HS-0/0            |  |

|-----------------------------------------|-----|------------|-------------------------------------------------------|------------------------------------|------------|-----------------------|-----------------------|--|

| _                                       | —   | IOCAF5     | IOCAF4                                                | IOCAF3                             | IOCAF2     | IOCAF1 <sup>(1)</sup> | IOCAF0 <sup>(1)</sup> |  |

| bit 7                                   |     |            |                                                       |                                    |            |                       | bit 0                 |  |

|                                         |     |            |                                                       |                                    |            |                       |                       |  |

| Legend:                                 |     |            |                                                       |                                    |            |                       |                       |  |

| R = Readable bit W = Writable bit       |     |            | bit                                                   | U = Unimplemented bit, read as '0' |            |                       |                       |  |

| u = Bit is unchanged x = Bit is unknown |     |            | -n/n = Value at POR and BOR/Value at all other Resets |                                    |            |                       |                       |  |

### REGISTER 17-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

bit 7-6 Unimplemented: read as '0'

'1' = Bit is set

bit 5-0

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

'0' = Bit is cleared

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

HS - Bit is set in hardware

0 = No change was detected, or the user cleared the detected change.

**Note 1:** If the debugger is enabled, these bits are not available for use.

# 23.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 37-14 for more details.

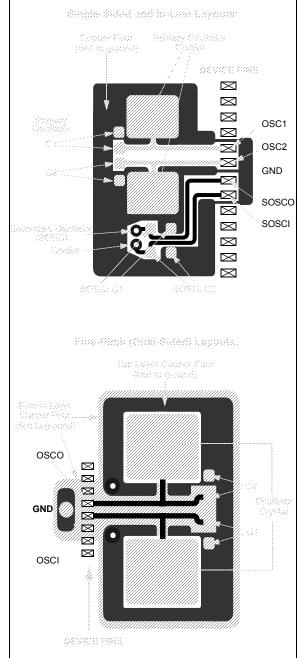

# 23.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 23-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

| M - 1-            | MODE                                             | <4:0> | Output                   | Onenetien                                                 |                                         | Timer Control |                                 |  |

|-------------------|--------------------------------------------------|-------|--------------------------|-----------------------------------------------------------|-----------------------------------------|---------------|---------------------------------|--|

| Mode              | <4:3>                                            | <2:0> | Operation                | Operation                                                 | Start                                   | Reset         | Stop                            |  |

|                   |                                                  | 000   |                          | Software gate (Figure 27-4)                               | <b>ON =</b> 1                           | _             | ON = 0                          |  |

|                   |                                                  | 001   | Period<br>Pulse          | Hardware gate, active-high<br>(Figure 27-5)               | ON = 1 and<br>TMRx_ers = 1              | _             | ON = 0 or<br>TMRx_ers = 0       |  |

|                   |                                                  | 010   | Fuise                    | Hardware gate, active-low                                 |                                         | _             | ON = 0 or<br>TMRx_ers = 1       |  |

| Free              | 0.0                                              | 011   |                          | Rising or falling edge Reset                              |                                         | TMRx_ers      |                                 |  |

| Running<br>Period | 00                                               | 100   | Period                   | Rising edge Reset (Figure 27-6)                           |                                         | TMRx_ers ↑    | <b>ON =</b> 0                   |  |

|                   |                                                  | 101   | Pulse                    | Falling edge Reset                                        | -                                       | TMRx_ers ↓    |                                 |  |

|                   |                                                  | 110   | with<br>Hardware         | Low level Reset                                           | ON = 1                                  | TMRx_ers = 0  | ON = 0 or<br>TMRx_ers = 0       |  |

|                   |                                                  | 111   | Reset                    | High level Reset (Figure 27-7)                            |                                         | TMRx_ers = 1  | ON = 0 or<br>TMRx_ers = 1       |  |

|                   |                                                  | 000   | One-shot                 | Software start (Figure 27-8)                              | ON = 1                                  | _             |                                 |  |

|                   |                                                  | 001   | Edge                     | Rising edge start (Figure 27-9)                           | ON = 1 and<br>TMRx_ers ↑                | _             |                                 |  |

|                   |                                                  | 010   | triggered<br>start       | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓                | —             |                                 |  |

|                   |                                                  | 011   | (Note 1)                 | Any edge start                                            | ON = 1 and<br>TMRx_ers                  |               | ON = 0<br>or<br>Next clock      |  |

| One-shot          | shot 01                                          |       | Edge                     | Rising edge start and<br>Rising edge Reset (Figure 27-10) | ON = 1 and<br>TMRx_ers ↑                | TMRx_ers ↑    | after<br>TMRx = PRx             |  |

|                   |                                                  | 101   | triggered<br>start       | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓                | TMRx_ers ↓    | (Note 2)                        |  |

|                   |                                                  | 110   | and<br>hardware<br>Reset | Rising edge start and<br>Low level Reset (Figure 27-11)   | ON = 1 and<br>TMRx_ers ↑                | TMRx_ers = 0  |                                 |  |

|                   |                                                  | 111   | (Note 1)                 | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓                | TMRx_ers = 1  |                                 |  |

|                   |                                                  | 000   |                          | Rese                                                      | rved                                    |               |                                 |  |

|                   |                                                  | 001   | Edge                     | Rising edge start<br>(Figure 27-12)                       | ON = 1 and<br>TMRx_ers ↑                | _             | ON = 0<br>or                    |  |

| Mono-stable       |                                                  | 010   | triggered<br>start       | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓                | _             | Next clock<br>after             |  |

|                   |                                                  | 011   | (Note 1)                 | Any edge start                                            | ON = 1 and<br>TMRx_ers                  | -             | TMRx = PRx<br>( <b>Note 3</b> ) |  |

| Reserved          | 10                                               | 100   | Reserved                 |                                                           |                                         |               |                                 |  |

| Reserved          |                                                  | 101   |                          | Rese                                                      | rved                                    |               |                                 |  |

|                   |                                                  | 110   | Level<br>triggered       | High level start and<br>Low level Reset (Figure 27-13)    | ON = 1 and<br>TMRx_ers = 1              | TMRx_ers = 0  | ON = 0 or                       |  |

| One-shot          | start<br>and<br><sup>111</sup> hardware<br>Reset |       | and<br>hardware          | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0 TMRx_ers = 1 |               | Held in Reset<br>(Note 2)       |  |

| Reserved          | 11                                               | xxx   |                          | Rese                                                      | rved                                    |               |                                 |  |

# TABLE 27-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

### REGISTER 28-1: CCPxCON: CCPx CONTROL REGISTER (CONTINUED)

- bit 3-0 MODE<3:0>: CCPx Mode Select bits<sup>(1)</sup>

- 1111 1100 = PWM mode (Timer2 as the timer source)

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Reserved

- 1011 = Compare mode: output will pulse 0-1-0; Clears TMR1

- 1010 = Compare mode: output will pulse 0-1-0

- 1001 = Compare mode: clear output on compare match

- 1000 = Compare mode: set output on compare match

- 0111 = Capture mode: every 16th rising edge of CCPx input

- 0110 = Capture mode: every 4th rising edge of CCPx input

- 0101 = Capture mode: every rising edge of CCPx input

- 0100 = Capture mode: every falling edge of CCPx input

- 0011 = Capture mode: every edge of CCPx input

- 0010 = Compare mode: toggle output on match

- 0001 = Compare mode: toggle output on match; clear TMR1

- 0000 = Capture/Compare/PWM off (resets CCPx module)

- **Note 1:** All modes will set the CCPxIF bit, and will trigger an ADC conversion if CCPx is selected as the ADC trigger source.

PIC16(L)F15356/75/76/85/86

### REGISTER 31-3: CLCxSEL0: GENERIC CLCx DATA 0 SELECT REGISTER

| U-0              | U-0 | R/W-x/u          | R/W-x/u | R/W-x/u         | R/W-x/u             | R/W-x/u | R/W-x/u |

|------------------|-----|------------------|---------|-----------------|---------------------|---------|---------|

| —                | _   |                  |         | LCxD            | 1S<5:0>             |         |         |

| bit 7            |     |                  |         |                 |                     |         | bit 0   |

|                  |     |                  |         |                 |                     |         |         |

| Legend:          |     |                  |         |                 |                     |         |         |

| R = Readable bit |     | W = Writable bit |         | U = Unimplement | ed bit, read as '0' |         |         |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

|----------------------|----------------------|-------------------------------------------------------|

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 LCxD1S<5:0>: CLCx Data1 Input Selection bits See Table 31-2.

#### REGISTER 31-4: CLCxSEL1: GENERIC CLCx DATA 1 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | LCxD2   | 2S<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 5-0 LCxD2S<5:0>: CLCx Data 2 Input Selection bits See Table 31-2.

#### REGISTER 31-5: CLCxSEL2: GENERIC CLCx DATA 2 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | LCxD    | 3S<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

```

bit 7-6 Unimplemented: Read as '0'

```

bit 5-0 LCxD3S<5:0>: CLCx Data 3 Input Selection bits See Table 31-2.

# REGISTER 31-6: CLCxSEL3: GENERIC CLCx DATA 3 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | LCxD4   | 4S<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

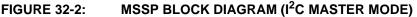

bit 5-0 LCxD4S<5:0>: CLCx Data 4 Input Selection bits See Table 31-2. The  $\mathsf{I}^2\mathsf{C}$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited multi-master support

- · 7-bit and 10-bit addressing

- Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- General call address matching

- · Address masking

- Selectable SDA hold times

Figure 32-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 32-3 is a diagram of the  $I^2C$  interface module in Slave mode.

Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

> 2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

# 32.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 32.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 32-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 32-5) affects the address matching process. See **Section 32.5.9** "**SSP Mask Register**" for more information.

32.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

32.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 32.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 32-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register.

32.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 7-bit Addressing mode. Figure 32-14 and Figure 32-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDA low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes idle.

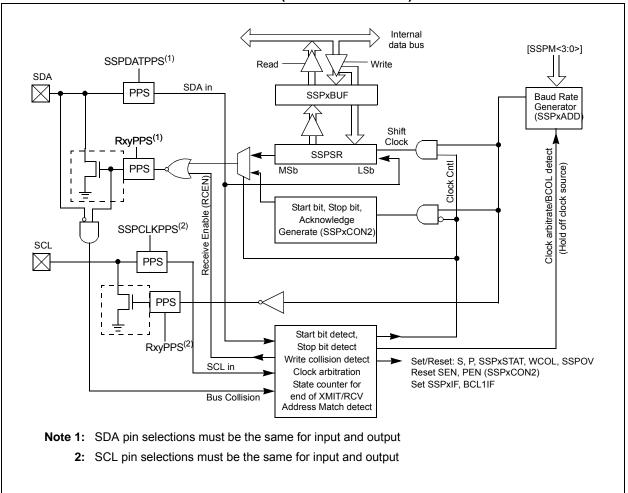

## 33.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDxCON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPxBRG begins counting up using the BRG counter clock as shown in Figure 33-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPxBRGH, SPxBRGL register pair, the ABDEN bit is automatically cleared and the RXxIF interrupt flag is set. The value in the RCxREG needs to be read to clear the RXxIF interrupt. RCxREG content should be discarded. When calibrating for modes that do not use the SPxBRGH register the user can verify that the SPxBRGL register did not overflow by checking for 00h in the SPxBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 33-1. During ABD, both the SPxBRGH and SPxBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPxBRGH and SPxBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 33.3.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPxBRGH:SPxBRGL register pair.

#### TABLE 33-1: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPxBRGL and SPxBRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

#### FIGURE 33-6: AUTOMATIC BAUD RATE CALIBRATION

# PIC16(L)F15356/75/76/85/86

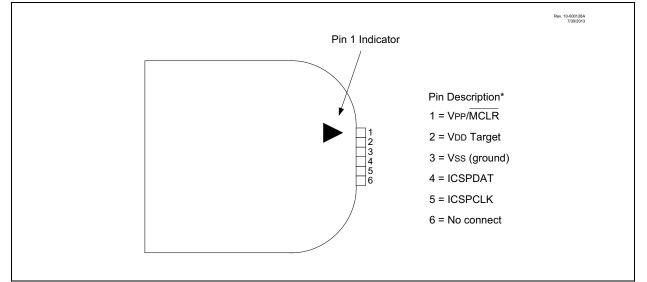

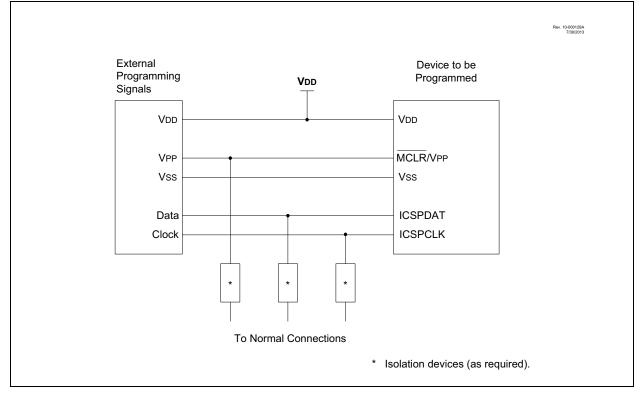

#### FIGURE 35-2: PICkit<sup>™</sup> PROGRAMMER STYLE CONNECTOR INTERFACE

# PIC16(L)F15356/75/76/85/86

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<6:3>) \rightarrow PC<14:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                        |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                              |

| Operands:                      | None                                                                                                                                                                                        |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$<br>are set.                    |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                | COMF                                        |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       | Syntax:                                     |

| Operands:        | None                                                                                                                                                                                                                  | Operands:                                   |