#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15375-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-4:** PIC16(L)F15385/86 PINOUT DESCRIPTION (CONTINUED)

| Name                                                            | Function | Input<br>Type | Output Type       | Description                    |  |  |

|-----------------------------------------------------------------|----------|---------------|-------------------|--------------------------------|--|--|

| RF5/ANF5                                                        | RF5      | TTL/ST        | CMOS/OD           | General purpose I/O.           |  |  |

|                                                                 | ANF5     | AN            | _                 | ADC Channel D0 input.          |  |  |

| RF6/ANF6                                                        | RF6      | TTL/ST        | CMOS/OD           | General purpose I/O.           |  |  |

|                                                                 | ANF6     | AN            | —                 | ADC Channel D0 input.          |  |  |

| RF7/ANF7                                                        | RF5      | TTL/ST        | CMOS/OD           | General purpose I/O.           |  |  |

|                                                                 | ANF5     | AN            | _                 | ADC Channel D0 input.          |  |  |

| VDD                                                             | Vdd      | Power         | _                 | Positive supply voltage input. |  |  |

| Vss                                                             | Vss      | Power         | _                 | Ground reference.              |  |  |

| Legend: AN = Analog input or outp<br>TTL = TTL compatible input |          |               | mpatible input or |                                |  |  |

TTL = TTL compatible input

HV = High Voltage

XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-7.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for  $l^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the  $l^2C$  specific or SMBus input buffer thresholds. 4:

| Address | Name                                        | Bit 7                                | Bit 6             | Bit 5  | Bit 4        | Bit 3             | Bit 2     | Bit 1    | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|---------------------------------------------|--------------------------------------|-------------------|--------|--------------|-------------------|-----------|----------|-----------|-----------------------|----------------------------|

| Bank 6  |                                             |                                      |                   |        |              |                   |           |          |           |                       |                            |

|         |                                             |                                      |                   |        |              | see Table 4-3 for | anacifica |          |           |                       |                            |

|         |                                             |                                      |                   | CFUCOF | L REGISTERS, | See Table 4-5 101 | specifics |          |           |                       |                            |

| 30Ch    | CCPR1L                                      | Capture/Compare/PV                   | VM Register 1 (LS | SB)    |              |                   |           |          |           | xxxx xxxx             | uuuu uuuu                  |

| 30Dh    | CCPR1H                                      | Capture/Compare/PV                   | VM Register 1 (M  | SB)    |              |                   |           |          |           | xxxx xxxx             | uuuu uuuu                  |

| 30Eh    | CCP1CON                                     | EN                                   | _                 | OUT    | FMT          |                   | MOI       | DE<3:0>  |           | 0-00 0000             | 0-00 0000                  |

| 30Fh    | CCP1CAP                                     | _                                    | —                 | —      | —            | —                 |           | CTS<2:0> |           | 000                   | 000                        |

| 310h    | CCPR2L Capture/Compare/PWM Register 2 (LSB) |                                      |                   |        |              |                   |           |          | xxxx xxxx | uuuu uuuu             |                            |

| 311h    | CCPR2H                                      | Capture/Compare/PWM Register 2 (MSB) |                   |        |              |                   |           |          | XXXX XXXX | uuuu uuuu             |                            |

| 312h    | CCP2CON                                     | EN                                   | —                 | OUT    | FMT          | MODE<3:0>         |           |          |           | 0-00 0000             | 0-00 0000                  |

| 313h    | CCP2CAP                                     | _                                    | —                 | —      | _            | —                 |           | CTS<2:0> |           | 000                   | 000                        |

| 314h    | PWM3DCL                                     | DC<1:                                | 0>                | —      |              | —                 | —         | _        | _         | xx                    | uu                         |

| 315h    | PWM3DCH                                     |                                      |                   |        | DC<9         | 9:0>              |           |          |           | XXXX XXXX             | uuuu uuuu                  |

| 316h    | PWM3CON                                     | EN                                   | —                 | OUT    | POL          | —                 | —         | _        | _         | 0-00                  | 0-00                       |

| 317h    | —                                           |                                      |                   |        | Unimple      | mented            |           |          |           | —                     |                            |

| 318h    | PWM4DCL                                     | DC<1:                                | 0>                | —      |              | —                 | —         | _        |           | xx                    | uu                         |

| 319h    | PWM4DCH                                     |                                      |                   |        | DC<9         | 9:0>              |           |          |           | XXXX XXXX             | uuuu uuuu                  |

| 31Ah    | PWM4CON                                     | EN                                   | —                 | OUT    | POL          | —                 | _         | —        |           | 0-00                  | 0-00                       |

| 31Bh    | —                                           |                                      |                   |        | Unimple      | mented            |           |          |           | —                     |                            |

| 31Ch    | PWM5DCL                                     | DC<1:                                | 0>                | —      | _            |                   | _         | _        | _         | xx                    | uu                         |

| 31Dh    | PWM5DCH                                     |                                      | DC<9:0>           |        |              |                   |           |          | xxxx xxxx | uuuu uuuu             |                            |

| 31Eh    | PWM5CON                                     | EN                                   | _                 | OUT    | POL          | —                 | _         | _        |           | 0-00                  | 0-00                       |

| 31Fh    | _                                           |                                      |                   |        | Unimple      | mented            |           |          |           | —                     | _                          |

####

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

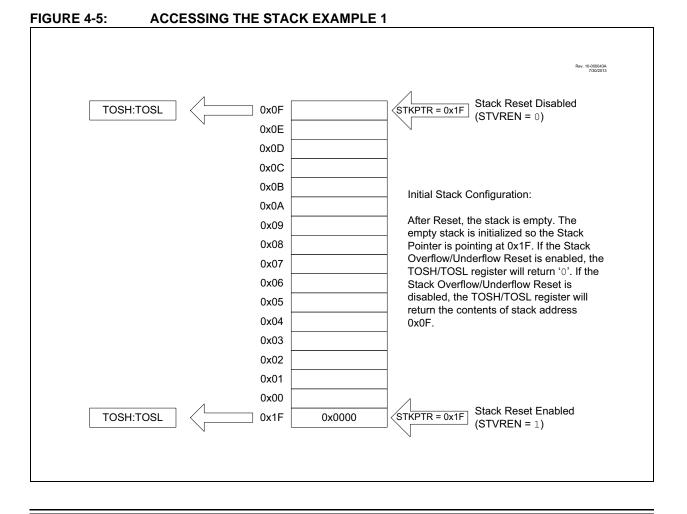

#### 4.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figure 4-5 through Figure 4-8). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 4.5.1 ACCESSING THE STACK

The stack is accessible through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. STKPTR can be monitored to obtain to value of stack memory left at any given time. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC value from the stack and then decrement the STKPTR.

Reference Figure 4-5 through Figure 4-8 for examples of accessing the stack.

## PIC16(L)F15356/75/76/85/86

#### EXAMPLE 13-3: ERASING ONE ROW OF PROGRAM FLASH MEMORY (PFM)

|                |                  | ( )                                                                                                   |

|----------------|------------------|-------------------------------------------------------------------------------------------------------|

| ; 1.A valid ad |                  | umes the following:<br>e row is loaded in variables ADDRH:ADDRL<br>common RAM (locations 0x70 - 0x7F) |

| BANKSEL        | NVMADRL          |                                                                                                       |

| MOVF           | ADDRL,W          |                                                                                                       |

| MOVWF          | NVMADRL          | ; Load lower 8 bits of erase address boundary                                                         |

| MOVF           | ADDRH,W          |                                                                                                       |

| MOVWF          | NVMADRH          | ; Load upper 6 bits of erase address boundary                                                         |

| BCF            | NVMCON1, NVMREGS | ; Choose PFM memory area                                                                              |

| BSF            | NVMCON1, FREE    | ; Specify an erase operation                                                                          |

| BSF            | NVMCON1,WREN     | ; Enable writes                                                                                       |

| BCF            | INTCON,GIE       | ; Disable interrupts during unlock sequence                                                           |

| ;              | REQ              | UIRED UNLOCK SEQUENCE:                                                                                |

| MOVLW          | 55h              | ; Load 55h to get ready for unlock sequence                                                           |

| MOVWF          | NVMCON2          | ; First step is to load 55h into NVMCON2                                                              |

| MOVLW          | AAh              | ; Second step is to load AAh into W                                                                   |

| MOVWF          | NVMCON2          | ; Third step is to load AAh into NVMCON2                                                              |

| BSF            | NVMCON1,WR       | ; Final step is to set WR bit                                                                         |

| ;              |                  |                                                                                                       |

| BSF            | INTCON, GIE      | ; Re-enable interrupts, erase is complete                                                             |

| BCF            | NVMCON1,WREN     | ; Disable writes                                                                                      |

#### TABLE 13-2: NVM ORGANIZATION AND ACCESS INFORMATION

|                    | Master Values                                |                       | N                           | VMREG Acce       | ess                   | FSR Access     |                               |   |

|--------------------|----------------------------------------------|-----------------------|-----------------------------|------------------|-----------------------|----------------|-------------------------------|---|

| Memory<br>Function | Program<br>Counter (PC),<br>ICSP™<br>Address | Memory<br>Type        | NVMREGS<br>bit<br>(NVMCON1) | NVMADR<<br>14:0> | Allowed<br>Operations | FSR<br>Address | FSR<br>Programming<br>Address |   |

| Reset Vector       | 0000h                                        |                       | 0                           | 0000h            |                       | 8000h          |                               |   |

| Llear Momony       | 0001h                                        |                       | 0                           | 0001h            |                       | 8001h          |                               |   |

| User Memory        | 0003h                                        |                       | 0                           | 0003h            |                       | 8003h          |                               |   |

| INT Vector         | 0004h                                        | PFM                   | 0                           | 0004h            | Read<br>Write         | 8004h          | Read-0nly                     |   |

|                    | 0005h                                        |                       | 0                           | 0005h            | White                 | 8005h          |                               |   |

| User Memory        | 1FFFh                                        |                       |                             | 1FFFh            |                       | 9FFFh          |                               |   |

|                    | 3FFFh                                        |                       |                             | 3FFFh            |                       | BFFFh          |                               |   |

|                    | 8000h                                        | DEM                   | PFM 1                       | 1                | 0000h                 | Read           |                               | • |

| User ID            | 8003h                                        | PEM                   | 1                           | 0003h            | Write                 |                |                               |   |

| Reserved           | 8004h                                        | —                     | -                           | 0004h            | _                     |                |                               |   |

| Rev ID             | 8005h                                        |                       | 1                           | 0005h            | Deed Only             | - No Access    |                               |   |

| Device ID          | 8006h                                        |                       | 1                           | 0006h            | Read-Only             |                |                               |   |

| CONFIG1            | 8007h                                        |                       | 1                           | 0007h            |                       |                |                               |   |

| CONFIG2            | 8008h                                        | PFM                   | 1                           | 0008h            | <b>_</b> .            |                |                               |   |

| CONFIG3            | 8009h                                        |                       | 1                           | 0009h            | Read<br>Write         |                |                               |   |

| CONFIG4            | 800Ah                                        | 1                     | 1                           | 000Ah            | VVIILE                |                |                               |   |

| CONFIG5            | 800Bh                                        |                       | 1                           | 000Bh            |                       |                |                               |   |

| DIA and DCI        | 8100h-82FFh                                  | PFM and<br>Hard coded | 1                           | 0100h-<br>02FFh  | Read-Only             | No             | Access                        |   |

### 14.3 Register Definitions: PORTA

#### REGISTER 14-1: PORTA: PORTA REGISTER

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|---------|---------|-------|---------|---------|---------|

| RA7     | RA6     | RA5     | RA4     | RA3   | RA2     | RA1     | RA0     |

| bit 7   |         |         | •       |       |         |         | bit 0   |

|         |         |         |         |       |         |         |         |

| Legend: |         |         |         |       |         |         |         |

|         |         |         |         |       |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 14-2: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register returns of actual I/O pin values.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSC<7:0>: Analog Select between Analog or Digital Function on Pins RC<7:0>, respectively<sup>(1)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### REGISTER 14-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| VALUES             |                            |  |  |  |  |

|--------------------|----------------------------|--|--|--|--|

| Desired Input Pin  | Value to Write to Register |  |  |  |  |

| RA0                | 0x00                       |  |  |  |  |

| RA1                | 0x01                       |  |  |  |  |

| RA2                | 0x02                       |  |  |  |  |

| RA3                | 0x03                       |  |  |  |  |

| RA4                | 0x04                       |  |  |  |  |

| RA5                | 0x05                       |  |  |  |  |

| RA6                | 0x06                       |  |  |  |  |

| RA7                | 0x07                       |  |  |  |  |

| RB0                | 0x08                       |  |  |  |  |

| RB1                | 0x09                       |  |  |  |  |

| RB2                | 0x0A                       |  |  |  |  |

| RB3                | 0x0B                       |  |  |  |  |

| RB4                | 0x0C                       |  |  |  |  |

| RB5                | 0x0D                       |  |  |  |  |

| RB6                | 0x0E                       |  |  |  |  |

| RB7                | 0x0F                       |  |  |  |  |

| RC0                | 0x10                       |  |  |  |  |

| RC1                | 0x11                       |  |  |  |  |

| RC2                | 0x12                       |  |  |  |  |

| RC3                | 0x13                       |  |  |  |  |

| RC4                | 0x14                       |  |  |  |  |

| RC5                | 0x15                       |  |  |  |  |

| RC6                | 0x16                       |  |  |  |  |

| RC7                | 0x17                       |  |  |  |  |

| RD0 <sup>(2)</sup> | 0x18                       |  |  |  |  |

| RD1 <sup>(2)</sup> | 0x19                       |  |  |  |  |

| RD2 <sup>(2)</sup> | 0x1A                       |  |  |  |  |

| RD3 <sup>(2)</sup> | 0x1B                       |  |  |  |  |

| RD4 <sup>(2)</sup> | 0x1C                       |  |  |  |  |

| RD5 <sup>(2)</sup> | 0x1D                       |  |  |  |  |

| RD6 <sup>(2)</sup> | 0x1E                       |  |  |  |  |

| RD7 <sup>(2)</sup> | 0x1F                       |  |  |  |  |

| RE0 <sup>(2)</sup> | 0x20                       |  |  |  |  |

| RE1 <sup>(2)</sup> | 0x21                       |  |  |  |  |

| RE2 <sup>(2)</sup> | 0x22                       |  |  |  |  |

| l                  | 1                          |  |  |  |  |

#### TABLE 15-4: PPS INPUT REGISTER VALUES

Note 1: Only a few of the values in this column are valid for any given signal. For example, since the INT signal can only be mapped to PORTA or PORTB pins, only the register values 0x00-0x0F (corresponding to RA<7:0> and RB<7:0>) are valid values to write to the INTPPS register.

- 2: Present on PIC16(L)F15375/76/85/86 only.

- **3:** Present on PIC16(L)F15385/86 only.

#### TABLE 15-4: PPS INPUT REGISTER VALUES

| Desired Input Pin  | Value to Write to Register |

|--------------------|----------------------------|

| RF0 <sup>(3)</sup> | 0x28                       |

| RF1 <sup>(3)</sup> | 0x29                       |

| RF2 <sup>(3)</sup> | 0x2A                       |

| RF3 <sup>(3)</sup> | 0x2B                       |

| RF4 <sup>(3)</sup> | 0x2C                       |

| RF5 <sup>(3)</sup> | 0x2D                       |

| RF6 <sup>(3)</sup> | 0x2E                       |

| RF7 <sup>(3)</sup> | 0x2F                       |

Note 1: Only a few of the values in this column are valid for any given signal. For example, since the INT signal can only be mapped to PORTA or PORTB pins, only the register values 0x00-0x0F (corresponding to RA<7:0> and RB<7:0>) are valid values to write to the INTPPS register.

- 2: Present on PIC16(L)F15375/76/85/86 only.

- **3:** Present on PIC16(L)F15385/86 only.

| R/W-0/0          | R/W-0/0                                                 | R/W-0/0                                                                                         | R/W-0/0                        | U-0            | U-0             | R/W-0/0             | R/W-0/0      |

|------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------|----------------|-----------------|---------------------|--------------|

| ADFM             |                                                         | ADCS<2:0>                                                                                       |                                | _              | _               | ADPRE               | F<1:0>       |

| bit 7            |                                                         |                                                                                                 |                                |                |                 |                     | bit 0        |

|                  |                                                         |                                                                                                 |                                |                |                 |                     |              |

| Legend:          |                                                         |                                                                                                 |                                |                |                 |                     |              |

| R = Readable     | e bit                                                   | W = Writable b                                                                                  | it                             | U = Unimpler   | nented bit, rea | d as '0'            |              |

| u = Bit is uncl  | hanged                                                  | x = Bit is unkno                                                                                | own                            | -n/n = Value a | at POR and BC   | R/Value at all o    | other Resets |

| '1' = Bit is set | :                                                       | '0' = Bit is clea                                                                               | red                            |                |                 |                     |              |

|                  | loaded.                                                 | stified. Six Most                                                                               | •                              |                |                 |                     |              |

| bit 6-4          | 111 = ADCF<br>110 = Fosc/<br>101 = Fosc/<br>100 = Fosc/ | /16<br>/4<br>RC (dedicated R(<br>/32<br>/8                                                      | C oscillator)                  | ct bits        |                 |                     |              |

| bit 3-2          | Unimpleme                                               | nted: Read as '0                                                                                | ,                              |                |                 |                     |              |

| bit 1-0          | 11 = VREF+<br>10 = VREF+<br>01 = Reserv                 | <b>0&gt;:</b> ADC Positive<br>is connected to i<br>is connected to e<br>ed<br>is connected to N | nternal Fixed<br>external VREF | Voltage Refere |                 | dule <sup>(1)</sup> |              |

#### REGISTER 20-2: ADCON1: ADC CONTROL REGISTER 1

**Note 1:** When selecting the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See Table 37-14 for details.

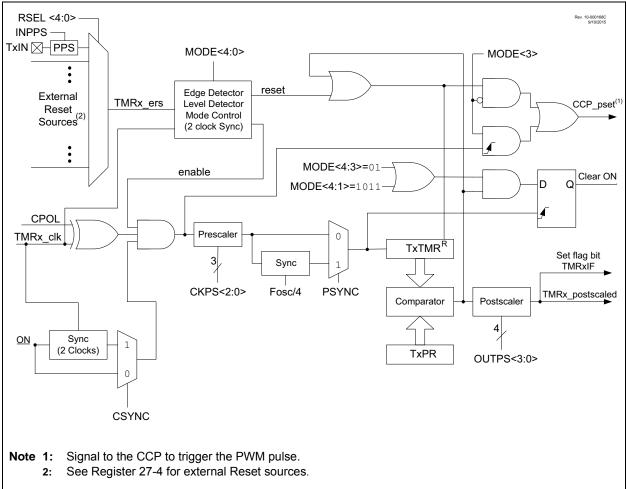

## 27.0 TIMER2 MODULE WITH HARDWARE LIMIT TIMER (HLT)

The Timer2 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- 8-bit period register

- · Selectable external hardware timer Resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- · Selectable synchronous/asynchronous operation

- Alternate clock sources

- Interrupt-on-period

- · Three modes of operation:

- Free Running Period

- One-shot

- Monostable

See Figure 27-1 for a block diagram of Timer2. See Figure 27-2 for the clock source block diagram.

## FIGURE 27-1: TIMER2 BLOCK DIAGRAM

#### REGISTER 30-3: CWG1DBR: CWG1 RISING DEAD-BAND COUNTER REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | DBR     | <5:0>   |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 DBR<5:0>: Rising Event Dead-Band Value for Counter bits

#### REGISTER 30-4: CWG1DBF: CWG1 FALLING DEAD-BAND COUNTER REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | DBF     | <5:0>   |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 DBF<5:0>: Falling Event Dead-Band Value for Counter bits

© 2016 Microchip Technology Inc.

## 31.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) module provides programmable logic that operates outside the speed limitations of software execution. The logic cell selects from 40 input signals and, through the use of configurable gates, reduces the inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

The CLC modules available are shown in Table 31-1.

TABLE 31-1: AVAILABLE CLC MODULES

| Device                         | CLC1 | CLC2 | CLC3 | CLC4 |

|--------------------------------|------|------|------|------|

| PIC16(L)F15356/75/76/85/8<br>6 | •    | •    | •    | ٠    |

| Note: | The CLC1, CLC2, CLC3 and CLC4 are            |

|-------|----------------------------------------------|

|       | four separate module instances of the        |

|       | same CLC module design. Throughout           |

|       | this section, the lower case 'x' in register |

|       | and bit names is a generic reference to      |

|       | the CLC number (which should be substi-      |

|       | tuted with 1, 2, 3, or 4 during code devel-  |

|       | opment). For example, the control register   |

|       | is generically described in this chapter as  |

|       | CLCxCON, but the actual device registers     |

|       | are CLC1CON, CLC2CON, CLC3CON                |

|       | and CLC4CON. Similarly, the LCxEN bit        |

|       | represents the LC1EN, LC2EN, LC3EN           |

|       | and LC4EN bits.                              |

Refer to Figure 31-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

#### 31.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 31-3 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

#### TABLE 31-3: DATA GATING LOGIC

| CLCxGLSy | LCxGyPOL | Gate Logic   |

|----------|----------|--------------|

| 0x55     | 1        | 4-input AND  |

| 0x55     | 0        | 4-input NAND |

| 0xAA     | 1        | 4-input NOR  |

| 0xAA     | 0        | 4-input OR   |

| 0x00     | 0        | Logic 0      |

| 0x00     | 1        | Logic 1      |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 31-7)

- Gate 2: CLCxGLS1 (Register 31-8)

- Gate 3: CLCxGLS2 (Register 31-9)

- Gate 4: CLCxGLS3 (Register 31-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 31-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 31.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 31-2. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 31.1.4 OUTPUT POLARITY

The last stage in the Configurable Logic Cell is the output polarity. Setting the LCxPOL bit of the CLCxPOL register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

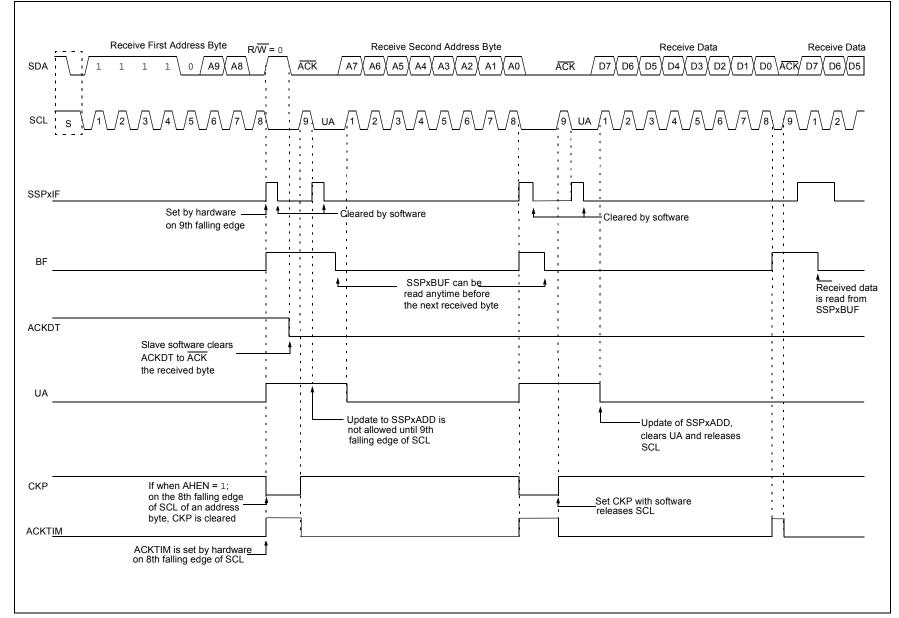

### FIGURE 32-21: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 1, DHEN = 0)

PIC16(L)F15356/75/76/85/86

| R/W-0/0          | U-0                                                                          | U-0               | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |

|------------------|------------------------------------------------------------------------------|-------------------|----------------|----------------|------------------|------------------|--------------|--|--|

| CLKREN           | _                                                                            | —                 | CLKRI          | DC<1:0>        | (                | CLKRDIV<2:0>     |              |  |  |

| bit 7            |                                                                              |                   |                |                |                  |                  | bit C        |  |  |

| Legend:          |                                                                              |                   |                |                |                  |                  |              |  |  |

| R = Readable     | bit                                                                          | W = Writable      | bit            | U = Unimpler   | nented bit, read | l as '0'         |              |  |  |

| u = Bit is unch  | anged                                                                        | x = Bit is unkr   | iown           | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is set |                                                                              | '0' = Bit is clea | ared           |                |                  |                  |              |  |  |

|                  |                                                                              |                   |                |                |                  |                  |              |  |  |

| bit 7            | CLKREN: Re                                                                   | ference Clock     | Module Enable  | e bit          |                  |                  |              |  |  |

|                  | 1 = Reference clock module enabled                                           |                   |                |                |                  |                  |              |  |  |

|                  | 0 = Referen                                                                  | ce clock modul    | le is disabled |                |                  |                  |              |  |  |

| bit 6-5          | Unimplemen                                                                   | ted: Read as '    | כי             |                |                  |                  |              |  |  |

| bit 4-3          | CLKRDC<1:0>: Reference Clock Duty Cycle bits <sup>(1)</sup>                  |                   |                |                |                  |                  |              |  |  |

|                  | 11 = Clock outputs duty cycle of 75%                                         |                   |                |                |                  |                  |              |  |  |

|                  | 10 = Clock outputs duty cycle of 50%                                         |                   |                |                |                  |                  |              |  |  |

|                  | 01 = Clock outputs duty cycle of 25%<br>00 = Clock outputs duty cycle of 0%  |                   |                |                |                  |                  |              |  |  |

|                  |                                                                              |                   |                |                |                  |                  |              |  |  |

| bit 2-0          |                                                                              | 0>: Reference     |                | bits           |                  |                  |              |  |  |

|                  | 111 = Base clock value divided by 128                                        |                   |                |                |                  |                  |              |  |  |

|                  | 110 = Base clock value divided by 64<br>101 = Base clock value divided by 32 |                   |                |                |                  |                  |              |  |  |

|                  | 100 = Base clock value divided by 32                                         |                   |                |                |                  |                  |              |  |  |

|                  |                                                                              | lock value divid  |                |                |                  |                  |              |  |  |

|                  |                                                                              | lock value divid  | •              |                |                  |                  |              |  |  |

|                  |                                                                              | lock value divid  | led by 2       |                |                  |                  |              |  |  |

|                  | 000 <b>= Base c</b>                                                          | lock value        |                |                |                  |                  |              |  |  |

#### REGISTER 34-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

**Note 1:** Bits are valid for reference clock divider values of two or larger, the base clock cannot be further divided.

# PIC16(L)F15356/75/76/85/86

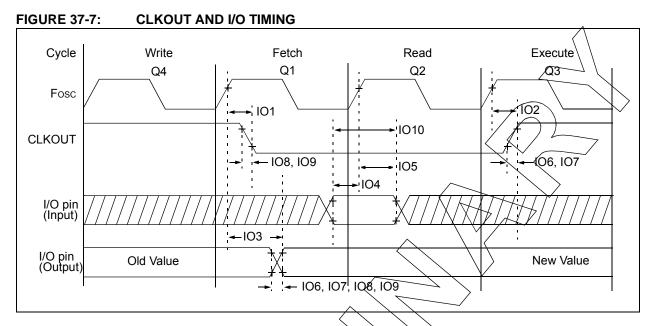

| TABLE 37-10: | I/O AND CLKOUT TIMING SPECIFICATIONS |

|--------------|--------------------------------------|

|--------------|--------------------------------------|

| Standar                                             | Standard Operating Conditions (unless otherwise stated) |                                                                                    |      |      |      |       |            |  |

|-----------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------|------|------|------|-------|------------|--|

| Param.<br>No.                                       | Sym.                                                    | Characteristic                                                                     | Min. | Тур† | Max. | Units | Conditions |  |

| IO1*                                                | T <sub>CLKOUTH</sub>                                    | CLKOUT rising edge delay (rising<br>edge Fosc (Q1 cycle) to falling edge<br>CLKOUT | > -  | —    | 70   | ns    |            |  |

| IO2*                                                | T <sub>CLKOUTL</sub>                                    | CLKOUT falling edge delay (rising<br>edge Fosc (Q3 cycle) to rising edge<br>CLKOUT | —    | _    | 72   | ns    |            |  |

| IO3*                                                | T <sub>IO_VALID</sub>                                   | Port output valid time (rising edge<br>Fose (Q1 cycle) to port valid)              | —    | 50   | 70   | ns    |            |  |

| 104*                                                | T <sub>IO_SETUP</sub>                                   | Port input setup time (Setup time<br>before rising edge Fosc – Q2 cycle)           | 20   | -    | —    | ns    |            |  |

| IO5*                                                | T <sub>IO_HOLD</sub>                                    | Port input hold time (Hold time after<br>rising edge Fosc – Q2 cycle)              | 50   | -    | —    | ns    |            |  |

| 106*                                                | TIOR_SLREN                                              | Port I/O rise time, slew rate enabled                                              | _    | 25   |      | ns    | VDD = 3.0V |  |

| 107*                                                | TIOR SLADIS                                             | Port I/O rise time, slew rate disabled                                             | _    | 5    |      | ns    | VDD = 3.0V |  |

| 108*                                                | FIOR SLREN                                              | Port I/O fall time, slew rate enabled                                              | _    | 25   |      | ns    | VDD = 3.0V |  |

| 109*/ /                                             | TIOF_SLRDIS                                             | Port I/O fall time, slew rate disabled                                             | _    | 5    |      | ns    | VDD = 3.0V |  |

|                                                     | FINT                                                    | INT pin high or low time to trigger an interrupt                                   | 25   | —    | —    | ns    |            |  |

| IO11*                                               | V.OC                                                    | Interrupt-on-Change minimum high or low time to trigger interrupt                  | 25   |      |      | ns    |            |  |

| *These parameters are characterized but not tested. |                                                         |                                                                                    |      |      |      |       |            |  |

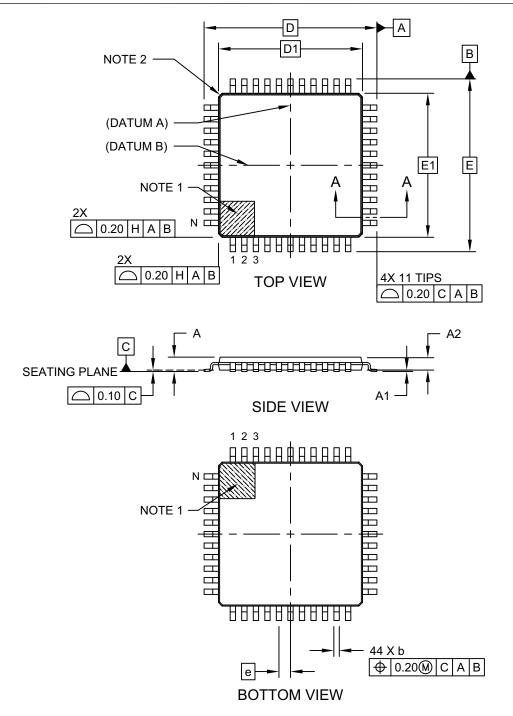

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2

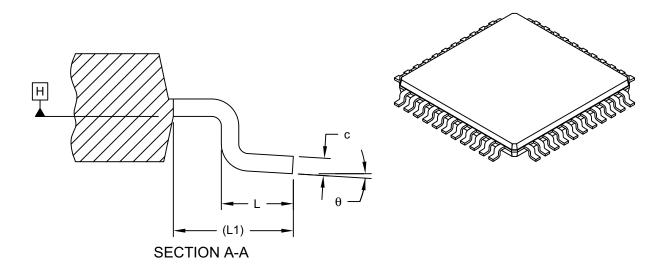

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |                |          |      |  |  |

|--------------------------|-------------|----------------|----------|------|--|--|

| Dimension                | MIN         | NOM            | MAX      |      |  |  |

| Number of Leads          | N           |                | 44       |      |  |  |

| Lead Pitch               | е           |                | 0.80 BSC |      |  |  |

| Overall Height           | Α           | -              | -        | 1.20 |  |  |

| Standoff                 | A1          | 0.05 - 0.15    |          |      |  |  |

| Molded Package Thickness | A2          | 0.95 1.00 1.05 |          |      |  |  |

| Overall Width            | E           | 12.00 BSC      |          |      |  |  |

| Molded Package Width     | E1          | 10.00 BSC      |          |      |  |  |

| Overall Length           | D           | 12.00 BSC      |          |      |  |  |

| Molded Package Length    | D1          | 10.00 BSC      |          |      |  |  |

| Lead Width               | b           | 0.30           | 0.37     | 0.45 |  |  |

| Lead Thickness           | С           | 0.09 - 0.20    |          |      |  |  |

| Lead Length              | L           | 0.45 0.60 0.75 |          |      |  |  |

| Footprint                | L1          | 1.00 REF       |          |      |  |  |

| Foot Angle               | θ           | 0° 3.5° 7°     |          |      |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2

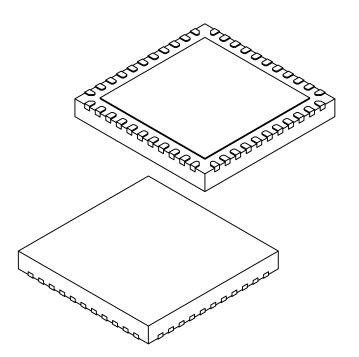

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |                |          |      |  |  |

|-------------------------|-------------|----------------|----------|------|--|--|

| Dimension               | MIN         | NOM            | MAX      |      |  |  |

| Number of Pins          | N           | 44             |          |      |  |  |

| Pitch                   | е           |                | 0.65 BSC |      |  |  |

| Overall Height          | Α           | 0.80           | 0.90     | 1.00 |  |  |

| Standoff                | A1          | 0.00 0.02 0.05 |          |      |  |  |

| Terminal Thickness      | A3          | 0.20 REF       |          |      |  |  |

| Overall Width           | E           | 8.00 BSC       |          |      |  |  |

| Exposed Pad Width       | E2          | 6.25 6.45 6.60 |          |      |  |  |

| Overall Length          | D           | 8.00 BSC       |          |      |  |  |

| Exposed Pad Length      | D2          | 6.25           | 6.45     | 6.60 |  |  |

| Terminal Width          | b           | 0.20 0.30 0.35 |          |      |  |  |

| Terminal Length         | L           | 0.30 0.40 0.50 |          |      |  |  |

| Terminal-to-Exposed-Pad | К           | 0.20           |          |      |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103D Sheet 2 of 2

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELoq, KEELoq logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, All Rights Reserved. ISBN: 978-1-5224-1167-3