#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

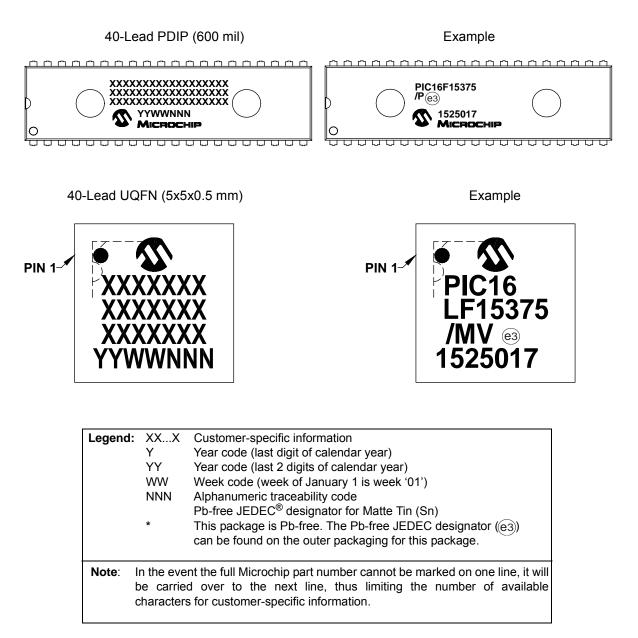

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15375-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1 Register and Bit Naming Conventions

## 1.1.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

## 1.1.2 BIT NAMES

There are two variants for bit names:

- Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

### 1.1.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is *RegisterName*bits.*ShortName*. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

## 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

## 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

COG1CON0bits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

Example 1:

MOVLW ~(1<<G1MD1) ANDWF COG1CON0,F MOVLW 1<<G1MD2 | 1<<G1MD0 IORWF COG1CON0,F

### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

## 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

## 1.1.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

## 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

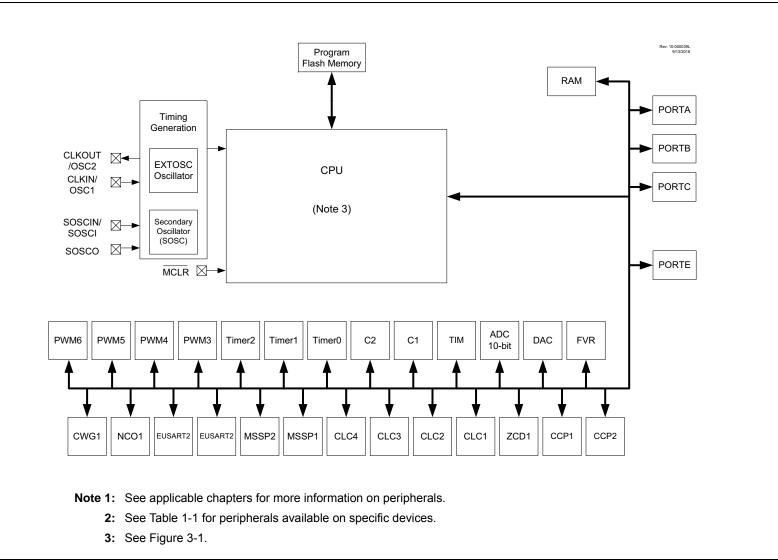

## FIGURE 1-1: PIC16(L)F15356 BLOCK DIAGRAM

| TABLE 4 | -11: SPEC | IAL FUNCTION             | REGISTER            | SUMMARY             | BANKS 0-        | 63 (CONTIN        | IUED)     | 1                 | 1     |                       |                            |

|---------|-----------|--------------------------|---------------------|---------------------|-----------------|-------------------|-----------|-------------------|-------|-----------------------|----------------------------|

| Address | Name      | Bit 7                    | Bit 6               | Bit 5               | Bit 4           | Bit 3             | Bit 2     | Bit 1             | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 11 |           |                          |                     |                     |                 |                   |           |                   |       |                       |                            |

|         |           |                          |                     |                     |                 | see Table 4-3 for | anacifica |                   |       |                       |                            |

|         |           |                          |                     | CPUCOF              | KE KEGISTERS,   | see Table 4-3 Iol | specifics |                   |       |                       |                            |

| 58Ch    | NCO1ACCL  |                          |                     |                     | NCO1AC          | C<7:0>            |           |                   |       | 0000 0000             | 0000 0000                  |

| 58Dh    | NCO1ACCH  |                          |                     |                     | NCO1AC          | C<15:8>           |           |                   |       | 0000 0000             | 0000 0000                  |

| 58Eh    | NCO1ACCU  | —                        | —                   | —                   | —               |                   | NCO1A     | ACC<19:16>        |       | 0000                  | 0000                       |

| 58Fh    | NCO1INCL  | NCO1INCL NCO1INC<7:0>    |                     |                     |                 |                   |           |                   |       | 0000 0001             | 0000 0001                  |

| 590h    | NCO1INCH  |                          |                     |                     | NCO1IN          | C<15:8>           |           |                   |       | 0000 0000             | 0000 0000                  |

| 591h    | NCO1INCU  | —                        | —                   | —                   | —               |                   | NCO1      | NC<19:16>         |       | 0000                  | 0000                       |

| 592h    | NCO1CON   | N1EN                     | —                   | N1OUT               | N1POL           | —                 | —         | _                 | N1PFM | 0-000                 | 0-000                      |

| 593h    | NCO1CLK   |                          | N1PWS<2:0>          |                     | —               | —                 |           | N1CKS<2:0         | >     | 000000                | 000000                     |

| 594h    | —         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | —                          |

| 595h    | —         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | —                          |

| 596h    | —         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | —                          |

| 597h    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | _                     | _                          |

| 598h    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | _                          |

| 599h    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | _                          |

| 59Ah    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | _                          |

| 59Bh    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | _                          |

| 59Ch    | TMR0L     | Holding Register for the | ne Least Significan | t Byte of the 16-bi | t TMR0 Register |                   |           |                   |       | 0000 0000             | 0000 0000                  |

| 59Dh    | TMR0H     | Holding Register for the | ne Most Significant | Byte of the 16-bit  | TMR0 Register   | •                 |           |                   |       | 1111 1111             | 1111 1111                  |

| 59Eh    | T0CON0    | TOEN                     | _                   | TOOUT               | T016BIT         |                   | TOOL      | JTPS<3:0>         |       | 0-00 0000             | 0-00 0000                  |

| 59Fh    | T0CON1    |                          | T0CS<2:0>           |                     | T0ASYNC         |                   | TOCH      | <ps<3:0></ps<3:0> |       | 0000 0000             | 0000 0000                  |

## - - - - - - -

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**REGISTER 5-2:**

### **CONFIGURATION WORD 2: SUPERVISORS**

| REGISTER                | 5-2:                                                                                                                                                                                                                                                                                                                                                                                         | CONFIGUR                                                                                | ATION WOR        | D 2: SUPER         | VISORS                                 |                                |                     |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------|--------------------|----------------------------------------|--------------------------------|---------------------|--|--|

|                         |                                                                                                                                                                                                                                                                                                                                                                                              | R/P-1                                                                                   | R/P-1            | R/P-1              | R/P-1                                  | R/P-1                          | U-1                 |  |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                              | DEBUG                                                                                   | STVREN           | PPS1WAY            | ZCDDIS                                 | BORV                           |                     |  |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                              | bit 13                                                                                  |                  |                    |                                        |                                | bit 8               |  |  |

| <b></b>                 |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |                  |                    |                                        |                                |                     |  |  |

| R/P-1                   | R/P-1                                                                                                                                                                                                                                                                                                                                                                                        | R/P-1                                                                                   | U-1              | U-1                | U-1                                    | R/P-1                          | R/P-1               |  |  |

| BOREN1                  | BOREN0                                                                                                                                                                                                                                                                                                                                                                                       | LPBOREN                                                                                 | —                |                    |                                        | PWRTE                          | MCLRE               |  |  |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |                  |                    |                                        |                                | bit 0               |  |  |

| Lonondi                 |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |                  |                    |                                        |                                |                     |  |  |

| Legend:<br>R = Readable | a bit                                                                                                                                                                                                                                                                                                                                                                                        | P = Programma                                                                           | ahle hit         | x = Bit is unkno   |                                        | U = Unimpleme                  | nted hit read as    |  |  |

|                         | , Dit                                                                                                                                                                                                                                                                                                                                                                                        | i – i logramma                                                                          |                  |                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | '1'                            | ited bit, read as   |  |  |

| '0' = Bit is cle        | ared                                                                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is set                                                                        |                  | W = Writable bi    | t                                      | n = Value when I<br>Erase      | olank or after Bulk |  |  |

| bit 13                  | 1 = Backgrour                                                                                                                                                                                                                                                                                                                                                                                | ugger Enable bit<br>nd debugger disa<br>nd debugger ena                                 |                  |                    |                                        |                                |                     |  |  |

| bit 12                  | 1 = Stack Ove                                                                                                                                                                                                                                                                                                                                                                                | ck Overflow/Unde<br>erflow or Underflo<br>erflow or Underflo                            | w will cause a F | Reset              |                                        |                                |                     |  |  |

| bit 11                  | 1 = The PPSL                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         | cleared and set  | only once; PPS i   | egisters remain l                      | ocked after one c<br>sequence) | lear/set cycle      |  |  |

| bit 10                  | 1 = ZCD disab                                                                                                                                                                                                                                                                                                                                                                                | -Cross Detect Di<br>bled. ZCD can be<br>ys enabled (ZCD                                 | enabled by sett  |                    | I bit of the ZCDC                      | ON register                    |                     |  |  |

| bit 9                   | 1 = Brown-out                                                                                                                                                                                                                                                                                                                                                                                | -out Reset Voltag<br>t Reset voltage (\<br>t Reset voltage (\                           | /BOR) set to low | er trip point leve |                                        |                                |                     |  |  |

| bit 8                   | Unimplement                                                                                                                                                                                                                                                                                                                                                                                  | ed: Read as '1'                                                                         |                  |                    |                                        |                                |                     |  |  |

| bit 7-6                 | Unimplemented: Read as '1'<br>BOREN<1:0>: Brown-out Reset Enable bits<br>When enabled, Brown-out Reset Voltage (VBOR) is set by the BORV bit<br>11 = Brown-out Reset is enabled; SBOREN bit is ignored<br>10 = Brown-out Reset is enabled while running, disabled in Sleep; SBOREN bit is ignored<br>01 = Brown-out Reset is enabled according to SBOREN<br>00 = Brown-out Reset is disabled |                                                                                         |                  |                    |                                        |                                |                     |  |  |

| bit 5                   | 1 = ULPBOR<br>0 = ULPBOR                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         | nable bit        |                    |                                        |                                |                     |  |  |

| bit 4-2                 | Unimplement                                                                                                                                                                                                                                                                                                                                                                                  | ed: Read as '1'                                                                         |                  |                    |                                        |                                |                     |  |  |

| bit 1                   | 1 = PWRT is a                                                                                                                                                                                                                                                                                                                                                                                | <b>PWRTE</b> : Power-up Timer Enable bit<br>1 = PWRT is disabled<br>0 = PWRT is enabled |                  |                    |                                        |                                |                     |  |  |

| bit 0                   | $\frac{\text{If LVP} = 1}{\text{RE3 pin function}}$ $\frac{\text{If LVP} = 0}{1 = \text{MCLR pin}}$                                                                                                                                                                                                                                                                                          | RE3 pin function is MCLR (it will reset the device when driven low)                     |                  |                    |                                        |                                |                     |  |  |

|                         | see <u>Vbor pa</u> rame                                                                                                                                                                                                                                                                                                                                                                      | eter for specific tri                                                                   | p point voltages | s.                 | by device develo                       | pment tools includ             | lina debuaaers      |  |  |

2: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

condition or the VDD level.

BOR IS ALWAYS OFF

When the BOREN bits of the Configuration Words are

programmed to '00', the BOR is off at all times. The

device start-up is not delayed by the BOR ready

8.2.4

## 8.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

## FIGURE 8-2: BROWN-OUT SITUATIONS

## VDD VBOR Internal T<sub>PWRT</sub>(1) Reset VDD VBOR Internal < TPWR TPWRT(1) Reset VDD VBOR Internal T<sub>PWRT</sub>(1) Reset Note 1: TPWRT delay only if PWRTE bit is programmed to '0'.

© 2016 Microchip Technology Inc.

## 10.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) of the PIEx[y] registers for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIEx registers)

The PIR1, PIR2, PIR3, PIR4, PIR5, PIR6, and PIR7 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 10.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupts operation, refer to its peripheral chapter.

| Note 1: | Individual interrupt flag bits are set, regardless of the state of any other enable bits.                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| 2:      | All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced |

when the GIE bit is set again.

## 10.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The interrupt is sampled during Q1 of the instruction cycle. The actual interrupt latency then depends on the instruction that is executing at the time the interrupt is detected. See Figure 10-2 and Figure 10-3 for more details.

| U-0          | U-0                                                                                                              | U-0               | U-0  | U-0            | U-0              | R/W-0/0          | R/W-0/0     |  |

|--------------|------------------------------------------------------------------------------------------------------------------|-------------------|------|----------------|------------------|------------------|-------------|--|

|              | —                                                                                                                | —                 | —    | —              | —                | TMR2IE           | TMR1IE      |  |

| bit 7        |                                                                                                                  |                   |      |                |                  |                  | bit 0       |  |

|              |                                                                                                                  |                   |      |                |                  |                  |             |  |

| Legend:      |                                                                                                                  |                   |      |                |                  |                  |             |  |

| R = Read     | able bit                                                                                                         | W = Writable      | bit  | U = Unimpler   | mented bit, read | as '0'           |             |  |

| u = Bit is   | unchanged                                                                                                        | x = Bit is unkr   | nown | -n/n = Value a | at POR and BOI   | R/Value at all o | ther Resets |  |

| '1' = Bit is | s set                                                                                                            | '0' = Bit is clea | ared | HS = Hardwa    | are set          |                  |             |  |

|              |                                                                                                                  |                   |      |                |                  |                  |             |  |

| bit 7-2      | Unimpleme                                                                                                        | nted: Read as '   | כ'   |                |                  |                  |             |  |

| bit 1        |                                                                                                                  | IR2 to PR2 Mate   |      |                |                  |                  |             |  |

|              |                                                                                                                  | s the Timer2 to   |      |                |                  |                  |             |  |

| 1.11.0       |                                                                                                                  | s the Timer2 to   |      | ·              |                  |                  |             |  |

| bit 0        |                                                                                                                  | ner1 Overflow Ir  | •    |                |                  |                  |             |  |

|              | <ul> <li>1 = Enables the Timer1 overflow interrupt</li> <li>0 = Enables the Timer1 overflow interrupt</li> </ul> |                   |      |                |                  |                  |             |  |

|              |                                                                                                                  |                   |      |                |                  |                  |             |  |

| Note:        | Note: Bit PEIE of the INTCON register must be                                                                    |                   |      |                |                  |                  |             |  |

|              | set to enable a                                                                                                  |                   |      |                |                  |                  |             |  |

|              | controlled by regis                                                                                              | sters PIE1-PIE7   | -    |                |                  |                  |             |  |

## REGISTER 10-6: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LK 10-0. FILO                                           |                  |           |                   | KEGISTER U       |                  |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|-----------|-------------------|------------------|------------------|-------------|--|

| U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                     | U-0              | U-0       | U-0               | U-0              | R/W-0/0          | R/W-0/0     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —                                                       | —                |           | —                 | —                | CCP2IE           | CCP1IE      |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |                  |           |                   |                  |                  | bit 0       |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                         |                  |           |                   |                  |                  |             |  |

| R = Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | dable bit                                               | W = Writable     | bit       | U = Unimplei      | mented bit, read | as '0'           |             |  |

| u = Bit is                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | unchanged                                               | x = Bit is unki  | nown      | -n/n = Value      | at POR and BO    | R/Value at all c | ther Resets |  |

| '1' = Bit is                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s set                                                   | '0' = Bit is cle | ared      | HS = Hardware set |                  |                  |             |  |

| bit 7-2       Unimplemented: Read as '0'.         bit 1       CCP2IE: CCP2 Interrupt Enable bit         1 =       CCP2 interrupt is enabled         0 =       CCP2 interrupt is disabled         bit 0       CCP1IE: CCP1 Interrupt Enable bit         1 =       CCP1 Interrupt is enabled         0 =       CCP1 interrupt is disabled |                                                         |                  |           |                   |                  |                  |             |  |

| Note:                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit PEIE of the l<br>set to enable<br>controlled by reg | any peripheral   | interrupt |                   |                  |                  |             |  |

## REGISTER 10-8: PIE6: PERIPHERAL INTERRUPT ENABLE REGISTER 6

## 14.6 PORTC Registers

## 14.6.1 DATA REGISTER

PORTC is an 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 14-18). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 14-17) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The PORT data latch LATC (Register 14-19) holds the output port data, and contains the latest value of a LATC or PORTC write.

## 14.6.2 DIRECTION CONTROL

The TRISC register (Register 14-18) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

## 14.6.3 OPEN-DRAIN CONTROL

The ODCONC register (Register 14-22) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONC bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONC bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for $I^2C$ ; the $I^2C$ |

|-------|------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                    |

## 14.6.4 SLEW RATE CONTROL

The SLRCONC register (Register 14-23) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONC bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONC bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

## 14.6.5 INPUT THRESHOLD CONTROL

The INLVLC register (Register 14-24) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 14.6.6 ANALOG CONTROL

The ANSELC register (Register 14-20) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |  |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |  |  |

## 14.6.7 WEAK PULL-UP CONTROL

The WPUC register (Register 14-21) controls the individual weak pull-ups for each port pin.

### 14.6.8 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

## 24.0 ZERO-CROSS DETECTION (ZCD) MODULE

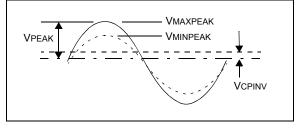

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero crossing threshold is the zero crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 24-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- Low EMI cycle switching

## 24.1 External Resistor Selection

The ZCD module requires a current limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 24-1 and Figure 24-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

## EQUATION 24-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

FIGURE 24-1: EXTERNAL VOLTAGE

| R/W-0/0              | U-0                        | R-0                                                              | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|----------------------|----------------------------|------------------------------------------------------------------|---------|----------------|------------------|------------------|--------------|--|--|--|

| T0EN                 | _                          | TOOUT                                                            | T016BIT |                | TOOUTI           | PS<3:0>          |              |  |  |  |

| bit 7                |                            |                                                                  |         |                |                  |                  | bit          |  |  |  |

|                      |                            |                                                                  |         |                |                  |                  |              |  |  |  |

| Legend:              |                            |                                                                  |         |                |                  |                  |              |  |  |  |

| R = Readable         | e bit                      | W = Writable                                                     | bit     | U = Unimplen   | nented bit, read | l as '0'         |              |  |  |  |

| u = Bit is unchanged |                            | x = Bit is unk                                                   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is se      | t                          | '0' = Bit is cle                                                 | ared    |                |                  |                  |              |  |  |  |

|                      |                            |                                                                  |         |                |                  |                  |              |  |  |  |

| bit 7                | TOEN: Time                 | r0 Enable bit                                                    |         |                |                  |                  |              |  |  |  |

|                      |                            | dule is enabled                                                  |         |                |                  |                  |              |  |  |  |

|                      |                            | dule is disabled                                                 |         | vest power mod | de               |                  |              |  |  |  |

| bit 6                | Unimpleme                  | Jnimplemented: Read as '0'                                       |         |                |                  |                  |              |  |  |  |

| bit 5                |                            | <b>T0OUT:</b> Timer0 Output bit (read-only)<br>Timer0 output bit |         |                |                  |                  |              |  |  |  |

| bit 4                | T016BIT: Tir               | T016BIT: Timer0 Operating as 16-bit Timer Select bit             |         |                |                  |                  |              |  |  |  |

|                      |                            | 1 = Timer0 is a 16-bit timer                                     |         |                |                  |                  |              |  |  |  |

|                      | 0 = Timer0 i               | s an 8-bit timer                                                 |         |                |                  |                  |              |  |  |  |

| bit 3-0              | T0OUTPS<                   | T0OUTPS<3:0>: Timer0 output postscaler (divider) select bits     |         |                |                  |                  |              |  |  |  |

|                      |                            | 1111 = 1:16 Postscaler                                           |         |                |                  |                  |              |  |  |  |

|                      | 1110 = 1:15<br>1101 = 1:14 |                                                                  |         |                |                  |                  |              |  |  |  |

|                      | 1101 - 1.14<br>1100 = 1:13 |                                                                  |         |                |                  |                  |              |  |  |  |

|                      | 1011 = 1:12                |                                                                  |         |                |                  |                  |              |  |  |  |

|                      | 1010 = 1:11                |                                                                  |         |                |                  |                  |              |  |  |  |

|                      | 1001 = 1:10                | Postscaler                                                       |         |                |                  |                  |              |  |  |  |

|                      | 1000 <b>= 1:9</b>          | 1000 = 1:9 Postscaler                                            |         |                |                  |                  |              |  |  |  |

|                      |                            | 0111 = 1:8 Postscaler                                            |         |                |                  |                  |              |  |  |  |

|                      |                            | 0110 = 1:7 Postscaler                                            |         |                |                  |                  |              |  |  |  |

|                      |                            | 0101 = 1:6 Postscaler<br>0100 = 1:5 Postscaler                   |         |                |                  |                  |              |  |  |  |

|                      | 0100 = 1:5<br>0011 = 1:4   |                                                                  |         |                |                  |                  |              |  |  |  |

|                      | 0011 = 1.41<br>0010 = 1:31 |                                                                  |         |                |                  |                  |              |  |  |  |

|                      | 0001 = 1:2                 |                                                                  |         |                |                  |                  |              |  |  |  |

|                      | 0000 = 1:1                 |                                                                  |         |                |                  |                  |              |  |  |  |

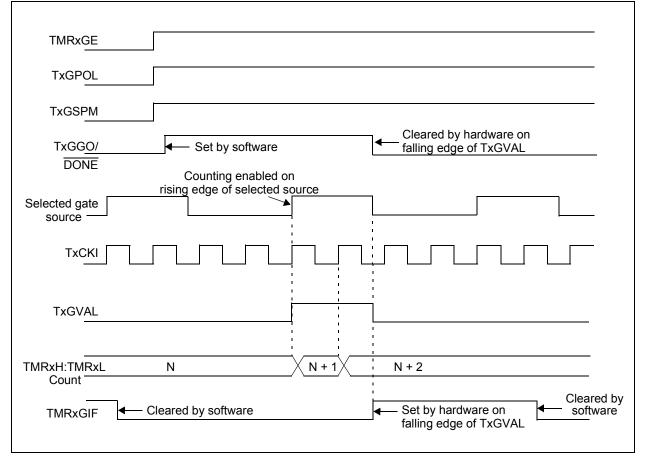

| FIGURE 26-4:           | TIMER1 GATE TOGGLE MODE                                                                                                                  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                                                                                                                          |

| TMRxGE                 |                                                                                                                                          |

| TxGPOL                 |                                                                                                                                          |

| TxGT <u>M</u>          |                                                                                                                                          |

| Selected<br>gate input |                                                                                                                                          |

| TxCKI                  |                                                                                                                                          |

| TxGVAL                 |                                                                                                                                          |

| TMRxH:TMRxL<br>Count   | $N \qquad \qquad$ |

## FIGURE 26-5: TIMER1 GATE SINGLE-PULSE MODE

## REGISTER 27-4: T2RST: TIMER2 EXTERNAL RESET SIGNAL SELECTION REGISTER

| U-0                                                                                         | U-0                                  | U-0          | U-0 | R/W-0/0      | R/W-0/0          | R/W-0/0      | R/W-0/0 |  |  |

|---------------------------------------------------------------------------------------------|--------------------------------------|--------------|-----|--------------|------------------|--------------|---------|--|--|

| —                                                                                           | _                                    | —            | -   |              | RSEL<3:0>        |              |         |  |  |

| bit 7 bit 0                                                                                 |                                      |              |     |              |                  |              |         |  |  |

|                                                                                             |                                      |              |     |              |                  |              |         |  |  |

| Legend:                                                                                     |                                      |              |     |              |                  |              |         |  |  |

| R = Readable                                                                                | bit                                  | W = Writable | bit | U = Unimplen | nented bit, read | l as '0'     |         |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese |                                      |              |     |              |                  | other Resets |         |  |  |

| '1' = Bit is set                                                                            | 1' = Bit is set '0' = Bit is cleared |              |     |              |                  |              |         |  |  |

| bit 7-4 | Unimplemented: Read as '0'                                    |

|---------|---------------------------------------------------------------|

| bit 3-0 | RSEL<3:0>: Timer2 External Reset Signal Source Selection bits |

|         | 1111 = Reserved                                               |

|         | 1101 = LC4_out                                                |

|         | 1100 = LC3_out                                                |

|         | 1011 = LC2_out                                                |

|         | 1010 = LC1_out                                                |

|         | 1001 = ZCD1_output                                            |

|         | 1000 = C2OUT_sync                                             |

|         | 0111 = C1OUT_sync                                             |

|         | 0110 = PWM6_out                                               |

|         | 0101 = PWM5_out                                               |

|         | $0100 = PWM4_out$                                             |

|         | 0011 = PWM3_out                                               |

|         | 0010 = CCP2_out                                               |

|         | 0001 = CCP1_out                                               |

|         | 0000 = T2INPPS                                                |

| PWM Frequency             | 1.22 kHz | 1.22 kHz 4.88 kHz 19.53 kHz |      | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|-----------------------------|------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4                           | 1    | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF                        | 0xFF | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10                          | 10   | 8         | 7         | 6.6       |

## TABLE 28-2:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

## TABLE 28-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz 19.61 kHz |      | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|--------------------|------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4                  | 1    | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65               | 0x65 | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8                  | 8    | 6         | 5          | 5         |

## 28.3.8 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

## 28.3.9 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

## 28.3.10 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

## 30.5 Dead-Band Control

The dead-band control provides non-overlapping PWM signals to prevent shoot-through current in PWM switches. Dead-band operation is employed for Half-Bridge and Full-Bridge modes. The CWG contains two 6-bit dead-band counters. One is used for the rising edge of the input source control in Half-Bridge mode or for reverse dead-band Full-Bridge mode. The other is used for the falling edge of the input source control in Half-Bridge mode or for forward dead band in Full-Bridge mode.

Dead band is timed by counting CWG clock periods from zero up to the value in the rising or falling deadband counter registers. See CWG1DBR and CWG1DBF registers, respectively.

## 30.5.1 DEAD-BAND FUNCTIONALITY IN HALF-BRIDGE MODE

In Half-Bridge mode, the dead-band counters dictate the delay between the falling edge of the normal output and the rising edge of the inverted output. This can be seen in Figure 30-9.

## 30.5.2 DEAD-BAND FUNCTIONALITY IN FULL-BRIDGE MODE

In Full-Bridge mode, the dead-band counters are used when undergoing a direction change. The MODE<0> bit of the CWG1CON0 register can be set or cleared while the CWG is running, allowing for changes from Forward to Reverse mode. The CWG1A and CWG1C signals will change upon the first rising input edge following a direction change, but the modulated signals (CWG1B or CWG1D, depending on the direction of the change) will experience a delay dictated by the deadband counters. This is demonstrated in Figure 30-3.

## 30.6 Rising Edge and Reverse Dead Band

CWG1DBR controls the rising edge dead-band time at the leading edge of CWG1A (Half-Bridge mode) or the leading edge of CWG1B (Full-Bridge mode). The CWG1DBR value is double-buffered. When EN = 0, the CWG1DBR register is loaded immediately when CWG1DBR is written. When EN = 1, then software must set the LD bit of the CWG1CON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

## 30.7 Falling Edge and Forward Dead Band

CWG1DBF controls the dead-band time at the leading edge of CWG1B (Half-Bridge mode) or the leading edge of CWG1D (Full-Bridge mode). The CWG1DBF value is double-buffered. When EN = 0, the CWG1DBF register is loaded immediately when CWG1DBF is written. When EN = 1 then software must set the LD bit of the CWG1CON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

Refer to Figure 30-6 and Figure 30-7 for examples.

## 33.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCxSTA register and the received data as indicated by RCxREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when:

- · RXxIF bit is set

- · FERR bit is set

- RCxREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 33.3.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RXxIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDxCON register before placing the EUSART in Sleep mode.

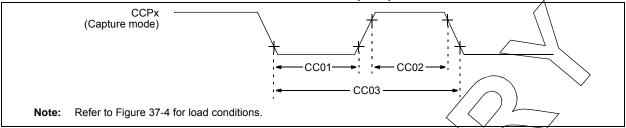

#### FIGURE 37-13: **CAPTURE/COMPARE/PWM TIMINGS (CCP)**

## TABLE 37-19: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                      |                |                       |                               |                          |            |                    |

|----------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|-----------------------|-------------------------------|--------------------------|------------|--------------------|

| Param.<br>No.                                                                                                        | Sym. | Characteri           | Min.           | Турт                  | Max                           | Units                    | Conditions |                    |

| CC01*                                                                                                                | TccL | CCPx Input Low Time  | No Prescaler   | 0.5Tcy + 20           | X                             | 1                        | ns         |                    |

|                                                                                                                      |      |                      | With Prescaler | 20/                   | -                             | $\overline{\mathcal{A}}$ | ns         |                    |

| CC02*                                                                                                                | TccH | CCPx Input High Time | No Prescaler   | 0.5Tcy + 20           |                               | /                        | ns         |                    |

|                                                                                                                      |      |                      | With Prescaler | 20                    | $\langle \mathcal{A} \rangle$ | _                        | ns         |                    |

| CC03*                                                                                                                | TccP | CCPx Input Period    |                | <u>3767 + 40</u><br>N |                               | > -                      | ns         | N = prescale value |

These parameters are characterized but not tested. Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

## 39.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

## 39.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 39.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 39.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 39.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 39.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradeable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 39.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 39.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 39.10 MPLAB PM3 Device Programmer