Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 201010                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15375t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                               | Function              | Input<br>Type | Output Type | Description                                                          |

|------------------------------------------------------------------------------------|-----------------------|---------------|-------------|----------------------------------------------------------------------|

| RB4/ANB4/ADACT <sup>(1)</sup> /IOCB4                                               | RB4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                 |

|                                                                                    | ANB4                  | AN            | _           | ADC Channel B4 input.                                                |

|                                                                                    | ADACT <sup>(1)</sup>  | TTL/ST        | _           | ADC Auto-Conversion Trigger input.                                   |

|                                                                                    | IOCB4                 | TTL/ST        | _           | Interrupt-on-change input.                                           |

| RB5/ANB5/IOCB5                                                                     | RB5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                 |

|                                                                                    | ANB5                  | AN            | —           | ADC Channel B5 input.                                                |

|                                                                                    | IOCB5                 | TTL/ST        | —           | Interrupt-on-change input.                                           |

| RB6/ANB6/CLCIN2 <sup>(1)</sup> /TX2/CK2 <sup>(1)</sup> /<br>IOCB6/ICSPCLK          | RB6                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                 |

| ICCB0/ICSF CER                                                                     | ANB6                  | AN            | —           | ADC Channel B6 input.                                                |

|                                                                                    | CLCIN2 <sup>(1)</sup> | TTL/ST        | —           | Configurable Logic Cell source input.                                |

|                                                                                    | TX2                   | TTL/ST        | —           | EUSART2 Asynchronous mode receiver data input.                       |

|                                                                                    | CK2 <sup>(1)</sup>    | TTL/ST        | CMOS/OD     | EUSART2 Synchronous mode clock input/output.                         |

|                                                                                    | IOCB6                 | TTL/ST        | —           | Interrupt-on-change input.                                           |

|                                                                                    | ICSPCLK               | ST            | —           | In-Circuit Serial Programming™ and debugging clock input.            |

| RB7/ANB7/DAC1OUT2/CLCIN3 <sup>(1)</sup> /<br>RX2/DT2 <sup>(1)</sup> /IOCB7/ICSPDAT | RB7                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                 |

| KAZID IZ: MOCDINCSFDAI                                                             | ANB7                  | AN            | —           | ADC Channel B7 input.                                                |

|                                                                                    | DAC10UT2              | —             | AN          | Digital-to-Analog Converter output.                                  |

|                                                                                    | CLCIN3 <sup>(1)</sup> | TTL/ST        | —           | Configurable Logic Cell source input.                                |

|                                                                                    | RX2                   | TTL/ST        | —           | EUSART2 Asynchronous mode receiver data input.                       |

|                                                                                    | DT2                   | TTL/ST        | CMOS/OD     | EUSART2 Synchronous mode data input/output.                          |

|                                                                                    | IOCB7                 | TTL/ST        | —           | Interrupt-on-change input.                                           |

|                                                                                    | ICSPDAT               | ST            | CMOS        | In-Circuit Serial Programming™ and debugging data input/out-<br>put. |

| RC0/ANC0/T1CKI <sup>(1)</sup> /IOCC0/SOSCO                                         | RC0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                 |

|                                                                                    | ANC0                  | AN            | —           | ADC Channel C0 input.                                                |

|                                                                                    | T1CKI <sup>(1)</sup>  | TTL/ST        | —           | Timer1 external digital clock input.                                 |

|                                                                                    | IOCC0                 | TTL/ST        | —           | Interrupt-on-change input.                                           |

|                                                                                    | SOSCO                 | —             | AN          | 32.768 kHz secondary oscillator crystal driver output.               |

| RC1/ANC1/CCP2 <sup>(1)</sup> /IOCC1/SOSCI                                          | RC1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                 |

|                                                                                    | ANC1                  | AN            | _           | ADC Channel C1 input.                                                |

|                                                                                    | CCP2 <sup>(1)</sup>   | TTL/ST        | CMOS/OD     | Capture/compare/PWM2 (default input location for capture function).  |

|                                                                                    | IOCC1                 | TTL/ST        | _           | Interrupt-on-change input.                                           |

|                                                                                    | SOSCI                 | AN            | _           | 32.768 kHz secondary oscillator crystal driver input.                |

#### **TABLE 1-3:** PIC16(L)F15375/76 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS = CMOS compatible input or output TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

Note

XTAL = Crystal levels 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

OD

l<sup>2</sup>C

= Open-Drain

= Schmitt Trigger input with I<sup>2</sup>C

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-6.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

HV = High Voltage

# 3.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 10.5 "Automatic Context Saving"** for more information.

# 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 4.5 "Stack**" for more details.

# 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. See **Section 4.6** "**Indirect Addressing**" for more details.

# 3.4 Instruction Set

There are 48 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 36.0 "Instruction Set Summary**" for more details.

| IADLE 4          | ABLE 4-11. SPECIAL FUNCTION REGISTER SUMMART BANKS 0-03 (CONTINUED) |                       |       |           |               |                   |           |         |          |                       |                            |  |  |

|------------------|---------------------------------------------------------------------|-----------------------|-------|-----------|---------------|-------------------|-----------|---------|----------|-----------------------|----------------------------|--|--|

| Address          | Name                                                                | Bit 7                 | Bit 6 | Bit 5     | Bit 4         | Bit 3             | Bit 2     | Bit 1   | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |

| Bank 1           |                                                                     |                       |       |           |               |                   |           |         |          |                       |                            |  |  |

|                  |                                                                     |                       |       | CPU COF   | RE REGISTERS; | see Table 4-3 for | specifics |         |          |                       |                            |  |  |

| 08Ch<br><br>09Ah | - Unimplemented                                                     |                       |       |           |               |                   |           |         |          |                       | -                          |  |  |

| 09Bh             | ADRESL                                                              | ADC Result Register L | _OW   |           |               |                   |           |         |          | xxxx xxxx             | uuuu uuuu                  |  |  |

| 09Ch             | ADRESH                                                              | ADC Result Register H | High  |           |               |                   |           |         |          | xxxx xxxx             | uuuu uuuu                  |  |  |

| 09Dh             | ADCON0                                                              |                       |       | CHS<5:    | 0>            |                   |           | GO/DONE | ADON     | 0000 0000             | 0000 0000                  |  |  |

| 09Eh             | ADCON1                                                              | ADFM                  |       | ADCS<2:0> |               | —                 | _         | ADPF    | REF<1:0> | 000000                | 000000                     |  |  |

| 09Fh             | ADACT                                                               | —                     | _     | —         | _             |                   | ADA       | CT<3:0> |          | 0000                  | 0000                       |  |  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address | Name | Bit 7  | Bit 6  | Bit 5   | Bit 4         | Bit 3             | Bit 2       | Bit 1  | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |  |  |

|---------|------|--------|--------|---------|---------------|-------------------|-------------|--------|---------|-----------------------|----------------------------|--|--|--|--|

| Bank 14 |      |        | 1      |         |               |                   |             |        |         |                       |                            |  |  |  |  |

|         |      |        |        | CPU COP | RE REGISTERS; | see Table 4-3 for | r specifics |        |         |                       |                            |  |  |  |  |

| 70Ch    | PIR0 | _      | —      | TMR0IF  | IOCIF         | —                 | _           | —      | INTF    | 000                   | 000                        |  |  |  |  |

| 70Dh    | PIR1 | OSFIF  | CSWIF  | —       | -             | _                 | -           | —      | ADIF    | 0000                  | 0000                       |  |  |  |  |

| 70Eh    | PIR2 | _      | ZCDIF  | _       | -             | _                 | _           | C2IF   | C1IF    | -000                  | -000                       |  |  |  |  |

| 70Fh    | PIR3 | RC2IF  | TX2IF  | RC1IF   | TX1IF         | BCL2IF            | SSP2IF      | BCL1IF | SSP1IF  | 0000 0000             | 0000 0000                  |  |  |  |  |

| 710h    | PIR4 | _      | _      | _       | _             | _                 | _           | TMR2IF | TMR1IF  | 00                    | 00                         |  |  |  |  |

| 711h    | PIR5 | CLC4IF | CLC3IF | CLC2IF  | CLC1IF        | _                 | _           | _      | TMR1GIF | 00000                 | 00000                      |  |  |  |  |

| 712h    | PIR6 | _      | _      | _       | _             | _                 | _           | CCP2IF | CCP1IF  | 00                    | 00                         |  |  |  |  |

| 713h    | PIR7 | _      | _      | NVMIF   | NCO1IF        | _                 | _           | _      | CWG1IF  | 000                   | 000                        |  |  |  |  |

| 714h    | _    |        |        | •       | Unimple       | mented            |             |        |         | _                     | _                          |  |  |  |  |

| 715h    | _    |        |        |         | Unimple       | mented            |             |        |         | _                     | _                          |  |  |  |  |

| 716h    | PIE0 | —      | —      | TMR0IE  | IOCIE         | —                 | —           | —      | INTE    | 000                   | 000                        |  |  |  |  |

| 717h    | PIE1 | OSFIE  | CSWIE  | _       | _             | _                 | _           | _      | ADIE    | 0000                  | 0000                       |  |  |  |  |

| 718h    | PIE2 | _      | ZCDIE  | —       | -             | _                 | -           | C2IE   | C1IE    | -000                  | -000                       |  |  |  |  |

| 719h    | PIE3 | RC2IE  | TX2IE  | RC1IE   | TX1IE         | BCL2IE            | SSP2IE      | BCL1IE | SSP1IE  | 0000 0000             | 0000 000                   |  |  |  |  |

| 71Ah    | PIE4 | _      | _      | _       | _             | _                 | —           | TMR2IE | TMR1IE  | 00                    | 0                          |  |  |  |  |

| 71Bh    | PIE5 | CLC4IE | CLC3IE | CLC2IE  | CLC1IE        | _                 | _           |        | TMR1GIE | 00000                 | 0000                       |  |  |  |  |

| 71Ch    | PIE6 | _      | _      | —       | _             | _                 | _           | CCP2IE | CCP1IE  | 00                    | 0                          |  |  |  |  |

| 71Dh    | PIE7 |        | —      | NVMIE   | NCO1IE        | _                 | —           | —      | CWG1IE  | 000                   | 00                         |  |  |  |  |

| 71Eh    | —    |        |        |         | Unimple       | mented            |             |        |         | —                     | _                          |  |  |  |  |

| 71Fh    | _    |        |        |         |               |                   |             |        |         |                       |                            |  |  |  |  |

# TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4         | Bit 3            | Bit 2     | Bit 1       | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|---------|----------|----------|----------|----------|---------------|------------------|-----------|-------------|----------|-----------------------|----------------------------|--|

| Bank 60 |          |          |          |          |               |                  |           |             |          |                       |                            |  |

|         |          |          |          | CPU COF  | RE REGISTERS; | see Table 4-3 fo | specifics |             |          |                       |                            |  |

| 1E0Ch   | _        |          |          |          | Unimpler      | mented           |           |             |          | —                     | _                          |  |

| 1E0Dh   | _        |          |          |          | Unimpler      | nented           |           |             |          | _                     | _                          |  |

| 1E0Eh   | _        |          |          |          | Unimpler      | nented           |           |             |          | —                     | _                          |  |

| 1E0Fh   | CLCDATA  | —        | —        | —        | —             | MLC4OUT          | MLC3OUT   | MLC2OUT     | MLC1OUT  | xxxx                  | uuuu                       |  |

| 1E10h   | CLCCON   | LC1EN    | —        | LC1OUT   | LC1INTP       | LC1INTN          |           | LC1MODE<2:0 | )>       | 0-00 0000             | 0-00 0000                  |  |

| 1E11h   | CLC1POL  | LC1POL   | —        | —        | —             | LC1G4POL         | LC1G3POL  | LC1G2POL    | LC1G1POL | 0 xxxx                | 0 uuuu                     |  |

| 1E12h   | CLC1SEL0 |          | _        |          |               |                  | xx xxxx   | uu uuuu     |          |                       |                            |  |

| 1E13h   | CLC1SEL1 |          | _        |          |               | xx xxxx          | uu uuu    |             |          |                       |                            |  |

| 1E14h   | CLC1SEL2 |          | _        |          | LC1D3S<5:0>   |                  |           |             |          |                       |                            |  |

| 1E15h   | CLC1SEL3 |          | _        |          | xx xxxx       | uu uuu           |           |             |          |                       |                            |  |

| 1E16h   | CLC1GLS0 | LC1G1D4T | LC1G4D3N | LC1G1D3T | LC1G1D3N      | LC1G1D2T         | LC1G1D2N  | LC1G1D1T    | LC1G1D1N | xxxx xxxx             | uuuu uuu                   |  |

| 1E17h   | CLC1GLS1 | LC1G2D4T | LC1G4D3N | LC1G2D3T | LC1G2D3N      | LC1G2D2T         | LC1G2D2N  | LC1G2D1T    | LC1G2D1N | xxxx xxxx             | uuuu uuu                   |  |

| 1E18h   | CLC1GLS2 | LC1G3D4T | LC1G4D3N | LC1G3D3T | LC1G3D3N      | LC1G3D2T         | LC1G3D2N  | LC1G3D1T    | LC1G3D1N | xxxx xxxx             | uuuu uuu                   |  |

| 1E19h   | CLC1GLS3 | LC1G4D4T | LC1G4D3N | LC1G4D3T | LC1G4D3N      | LC1G4D2T         | LC1G4D2N  | LC1G4D1T    | LC1G4D1N | xxxx xxxx             | uuuu uuu                   |  |

| 1E1Ah   | CLC2CON  | LC2EN    | _        | LC2OUT   | LC2INTP       | LC2INTN          |           | LC2MODE<2:0 | )>       | 0-00 0000             | 0-00 000                   |  |

| 1E1Bh   | CLC2POL  | LC2POL   | _        | —        | _             | LC2G4POL         | LC2G3POL  | LC2G2POL    | LC2G1POL | 0 xxxx                | 0 uuu                      |  |

| 1E1Ch   | CLC2SEL0 |          | _        |          |               | LC2              | 01S<5:0>  |             |          | xx xxxx               | uu uuu                     |  |

| 1E1Dh   | CLC2SEL1 | _        | _        |          |               | LC2              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |  |

| 1E1Eh   | CLC2SEL2 | _        | _        |          |               | LC2              | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |  |

| 1E1Fh   | CLC2SEL3 | _        | _        |          |               | LC2              | 04S<5:0>  |             |          | xx xxxx               | uu uuu                     |  |

| 1E20h   | CLC2GLS0 | LC2G1D4T | LC2G4D3N | LC2G1D3T | LC2G1D3N      | LC2G1D2T         | LC2G1D2N  | LC2G1D1T    | LC2G1D1N | xxxx xxxx             | uuuu uuu                   |  |

| 1E21h   | CLC2GLS1 | LC2G2D4T | LC2G4D3N | LC2G2D3T | LC2G2D3N      | LC2G2D2T         | LC2G2D2N  | LC2G2D1T    | LC2G2D1N | xxxx xxxx             | นนนน นนนา                  |  |

| 1E22h   | CLC2GLS2 | LC2G3D4T | LC2G4D3N | LC2G3D3T | LC2G3D3N      | LC2G3D2T         | LC2G3D2N  | LC2G3D1T    | LC2G3D1N | xxxx xxxx             | uuuu uuu                   |  |

| 1E23h   | CLC2GLS3 | LC2G4D4T | LC2G4D3N | LC2G4D3T | LC2G4D3N      | LC2G4D2T         | LC2G4D2N  | LC2G4D1T    | LC2G4D1N | xxxx xxxx             | uuuu uuu                   |  |

| 1E24h   | CLC3CON  | LC3EN    | —        | LC3OUT   | LC3INTP       | LC3INTN          |           | LC3MODE     |          | 0-00 0000             | 0-00 000                   |  |

| 1E25h   | CLC3POL  | LC3POL   | _        | —        | _             | LC3G4POL         | LC3G3POL  | LC3G2POL    | LC3G1POL | 0 xxxx                | 0 uuu                      |  |

| 1E26h   | CLC3SEL0 | _        |          |          |               | LC3              | 01S<5:0>  |             |          | xx xxxx               | uu uuu                     |  |

| 1E27h   | CLC3SEL1 | _        |          |          |               | LC3              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |  |

| 1E28h   | CLC3SEL2 | _        |          |          |               | LC3              | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |  |

| 1E29h   | CLC3SEL3 | _        | _        |          |               | LC3              | 04S<5:0>  |             |          | xx xxxx               | uu uuu                     |  |

| 1E2Ah   | CLC3GLS0 | LC3G1D4T | LC3G4D3N | LC3G1D3T | LC3G1D3N      | LC3G1D2T         | LC3G1D2N  | LC3G1D1T    | LC3G1D1N | xxxx xxxx             | uuuu uuu                   |  |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address | Name                  | Bit 7 | Bit 6 | Bit 5   | Bit 4         | Bit 3            | Bit 2        | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|-----------------------|-------|-------|---------|---------------|------------------|--------------|---------|---------|-----------------------|----------------------------|

| Bank 62 |                       |       |       |         |               |                  |              |         |         |                       |                            |

|         |                       |       |       | CPU COF | RE REGISTERS; | see Table 4-3 fo | or specifics |         |         |                       |                            |

| 1F0Ch   | _                     |       |       |         | Unimple       | mented           |              |         |         | _                     | _                          |

| 1F0Dh   | _                     |       |       |         | Unimple       | mented           |              |         |         | _                     | _                          |

| 1F0Eh   | —                     |       |       |         | Unimple       | mented           |              |         |         | —                     |                            |

| 1F0Fh   | —                     |       |       |         | Unimple       | mented           |              |         |         | —                     | _                          |

| 1F10h   | RA0PPS                | —     | —     | —       |               |                  | RA0PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F11h   | RA1PPS                | —     | —     | —       |               |                  |              | 00 0000 | uu uuuu |                       |                            |

| 1F12h   | RA2PPS                | _     | _     | _       |               |                  |              | 00 0000 | uu uuui |                       |                            |

| 1F13h   | <b>RA3PPS</b>         | —     | —     | —       |               |                  | RA3PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F14h   | RA4PPS                | —     | —     | —       |               |                  | RA4PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

| 1F15h   | RA5PPS                | —     | —     | —       |               |                  | 00 0000      | uu uuu  |         |                       |                            |

| 1F16h   | RA6PPS                | —     | —     | —       |               |                  | 00 0000      | uu uuu  |         |                       |                            |

| 1F17h   | RA7PPS                | _     | —     | —       |               |                  | 00 0000      | uu uuu  |         |                       |                            |

| 1F18h   | RB0PPS                | _     | —     | —       |               |                  | 00 0000      | uu uuu  |         |                       |                            |

| 1F19h   | RB1PPS                | _     | —     | —       |               |                  | 00 0000      | uu uuu  |         |                       |                            |

| 1F1Ah   | RB2PPS                | —     | —     | —       |               |                  | RB2PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

| 1F1Bh   | RB3PPS                | —     | —     | —       |               |                  | RB3PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F1Ch   | RB4PPS                | —     | —     | —       |               |                  | RB4PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

| 1F1Dh   | RB5PPS                | —     | —     | —       |               |                  | RB5PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F1Eh   | RB6PPS                | —     | —     | —       |               |                  | RB6PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F1Fh   | RB7PPS                | —     | —     | —       |               |                  | RB7PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F20h   | RC0PPS                | —     | —     | —       |               |                  | RC0PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

| 1F21h   | RC1PPS                | —     | —     | —       |               |                  | RC1PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F22h   | RC2PPS                | _     | —     | —       |               |                  | RC2PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

| 1F23h   | RC3PPS                | _     | —     | —       |               |                  | RC3PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

| 1F24h   | RC4PPS                | _     | —     | —       |               |                  | RC4PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F25h   | RC5PPS                | _     | —     | —       |               |                  | 00 0000      | uu uuuu |         |                       |                            |

| 1F26h   | RC6PPS                | _     | —     | —       |               |                  | RC6PPS<4:0   | >       |         | 00 0000               | uu uuuu                    |

| 1F27h   | RC7PPS                | —     | —     | —       |               |                  | RC7PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

| 1F28h   | RD0PPS <sup>(1)</sup> | —     | —     | —       |               |                  | RD0PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

| 1F29h   | RD1PPS <sup>(1)</sup> | _     | _     |         |               |                  | RD1PPS<4:0   | >       |         | 00 0000               | uu uuu                     |

#### SPECIAL EUNCTION DECISTED SUMMARY PANKS 0.62 (CONTINUED) A 44.

Legend:x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.Note1:Present only on PIC16(L)F15375/76/85/86.

# 8.13 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 8-3 and Table 8-4 show the Reset conditions of these registers.

| STOVF | STKUNF | RWDT | RMCLR | I.R. | POR | BOR | 10 | DA | MEMV | Condition                          |

|-------|--------|------|-------|------|-----|-----|----|----|------|------------------------------------|

| 0     | 0      | 1    | 1     | 1    | 0   | x   | 1  | 1  | 1    | Power-on Reset                     |

| 0     | 0      | 1    | 1     | 1    | 0   | x   | 0  | x  | u    | Illegal, TO is set on POR          |

| 0     | 0      | 1    | 1     | 1    | 0   | x   | x  | 0  | u    | Illegal, PD is set on POR          |

| 0     | 0      | u    | 1     | 1    | u   | 0   | 1  | 1  | u    | Brown-out Reset                    |

| u     | u      | 0    | u     | u    | u   | u   | 0  | u  | u    | WWDT Reset                         |

| u     | u      | u    | u     | u    | u   | u   | 0  | 0  | u    | WWDT Wake-up from Sleep            |

| u     | u      | u    | u     | u    | u   | u   | 1  | 0  | u    | Interrupt Wake-up from Sleep       |

| u     | u      | u    | 0     | u    | u   | u   | u  | u  | 1    | MCLR Reset during normal operation |

| u     | u      | u    | 0     | u    | u   | u   | 1  | 0  | u    | MCLR Reset during Sleep            |

| u     | u      | u    | u     | 0    | u   | u   | u  | u  | u    | RESET Instruction Executed         |

| 1     | u      | u    | u     | u    | u   | u   | u  | u  | u    | Stack Overflow Reset (STVREN = 1)  |

| u     | 1      | u    | u     | u    | u   | u   | u  | u  | u    | Stack Underflow Reset (STVREN = 1) |

| u     | u      | u    | u     | u    | u   | u   | u  | u  | 0    | Memory violation Reset             |

### TABLE 8-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

# TABLE 8-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON0<br>Register | PCON1<br>Register |

|------------------------------------|-----------------------|--------------------|-------------------|-------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 0011 110x         | 1-                |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uuuu Ouuu         | 1-                |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uuuu Ouuu         | u-                |

| WWDT Timeout Reset                 | 0000h                 | 0 uuuu             | uuu0 uuuu         | u-                |

| WWDT Wake-up from Sleep            | PC + 1                | 0 Ouuu             | uuuu uuuu         | u-                |

| WWDT Window Violation              | 0000h                 | u uuuu             | uu0u uuuu         | u-                |

| Brown-out Reset                    | 0000h                 | 1 1000             | 0011 11u0         | u-                |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uuuu uuuu         | u-                |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uuuu u0uu         | u-                |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | luuu uuuu         | u-                |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | uluu uuuu         | u-                |

| Memory Violation Reset (MEMV = 0)  | 0                     | -uuu uuuu          | uuuu uuuu         | 0-                |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# 8.15 Register Definitions: Power Control

# REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:          |                        |                                                                             |                                                                                                                                                     |  |  |  |  |  |  |

|------------------|------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| HC = Bit is clo  | eared by hardv         | vare                                                                        | HS = Bit is set by hardware                                                                                                                         |  |  |  |  |  |  |

| R = Readable     | e bit                  | W = Writable bit                                                            | U = Unimplemented bit, read as '0'                                                                                                                  |  |  |  |  |  |  |

| u = Bit is uncl  | hanged                 | x = Bit is unknown                                                          | -m/n = Value at POR/Value at all other Resets                                                                                                       |  |  |  |  |  |  |

| '1' = Bit is set |                        | '0' = Bit is cleared                                                        | q = Value depends on condition                                                                                                                      |  |  |  |  |  |  |

| bit 7            | 1 = A Stack            | tack Overflow Flag bit<br>Overflow occurred<br>Overflow has not occurre     | ed or cleared by firmware                                                                                                                           |  |  |  |  |  |  |

| bit 6            | 1 = A Stack            | tack Underflow Flag bit<br>Underflow occurred<br>Underflow has not occurr   | red or cleared by firmware                                                                                                                          |  |  |  |  |  |  |

| bit 5            | 1 = A WDT<br>0 = A WDT | Window Violation Reset h                                                    | g bit<br>as not occurred or set to '1' by firmware<br>as occurred (a CLRWDT instruction was executed either without<br>window (cleared by hardware) |  |  |  |  |  |  |

| bit 4            | 1 = A Watch            |                                                                             | it<br>occurred or set to '1' by firmware<br>urred (cleared by hardware)                                                                             |  |  |  |  |  |  |

| bit 3            | 1 = A MCLR             | CLR Reset Flag bit<br>Reset has not occurred of<br>Reset has occurred (clea |                                                                                                                                                     |  |  |  |  |  |  |

| bit 2            | 1 = A RESET            |                                                                             | executed or set to '1' by firmware<br>ecuted (cleared by hardware)                                                                                  |  |  |  |  |  |  |

| bit 1            | 1 = No Pow             | r-on Reset Status bit<br>er-on Reset occurred<br>r-on Reset occurred (must  | t be set in software after a Power-on Reset occurs)                                                                                                 |  |  |  |  |  |  |

| bit 0            | 1 = No Brow            | •                                                                           | t be set in software after a Power-on Reset or Brown-out Reset                                                                                      |  |  |  |  |  |  |

# PIC16(L)F15356/75/76/85/86

### **REGISTER 9-7: OSCTUNE: HFINTOSC TUNING REGISTER**

| U-0   | U-0 | R/W-1/1 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|-------|-----|---------|------------|---------|---------|---------|---------|--|--|--|--|

| —     | —   |         | HFTUN<5:0> |         |         |         |         |  |  |  |  |

| bit 7 |     |         |            |         |         |         | bit 0   |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 <b>U</b> | nimplemented: Read as '0'.                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01               | FTUN<5:0>: HFINTOSC Frequency Tuning bits 1 1111 = Maximum frequency 1 1110 =                                                                                                                                       |

|                  | <ul> <li>0 0001 =</li> <li>0 0000 = Center frequency. Oscillator module is running at the calibrated frequency (default value).</li> <li>1 1111 =</li> <li>0 0001 =</li> <li>0 0000 = Minimum frequency.</li> </ul> |

| U-0              | U-0                                                                                                                                          | R/W/HS-0/0        | R/W/HS-0/0 | U-0                                                   | U-0              | U-0    | R/W/HS-0/0 |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|-------------------------------------------------------|------------------|--------|------------|--|

| _                | _                                                                                                                                            | NVMIF             | NCO1IF     | —                                                     | _                | —      | CWG1IF     |  |

| bit 7            |                                                                                                                                              |                   |            |                                                       |                  |        | bit 0      |  |

|                  |                                                                                                                                              |                   |            |                                                       |                  |        |            |  |

| Legend:          |                                                                                                                                              |                   |            |                                                       |                  |        |            |  |

| R = Readable I   | oit                                                                                                                                          | W = Writable      | bit        | U = Unimpler                                          | mented bit, read | as '0' |            |  |

| u = Bit is uncha | anged                                                                                                                                        | x = Bit is unkr   | nown       | -n/n = Value at POR and BOR/Value at all other Resets |                  |        |            |  |

| '1' = Bit is set |                                                                                                                                              | '0' = Bit is clea | ared       | HS = Hardware set                                     |                  |        |            |  |

|                  |                                                                                                                                              |                   |            |                                                       |                  |        |            |  |

| bit 7-6          | Unimplemen                                                                                                                                   | ted: Read as '    | 0'         |                                                       |                  |        |            |  |

| bit 5            | 5 <b>NVMIF:</b> Nonvolatile Memory (NVM) Interrupt Flag bit                                                                                  |                   |            |                                                       |                  |        |            |  |

|                  | <ul><li>1 = The requested NVM operation has completed</li><li>0 = NVM interrupt not asserted</li></ul>                                       |                   |            |                                                       |                  |        |            |  |

| bit 4            | NCO1IF: Numerically Controlled Oscillator (NCO) Interrupt Flag bit<br>1 = The NCO has rolled over<br>0 = No NCO interrupt event has occurred |                   |            |                                                       |                  |        |            |  |

### REGISTER 10-17: PIR7: PERIPHERAL INTERRUPT REQUEST REGISTER 7

| bit 3-1 | Unimplemented: Read as '0'      |

|---------|---------------------------------|

| bit 0   | CWG1IF: CWG1 Interrupt Flag bit |

- 1 = CWG1 has gone into shutdown

- 0 = CWG1 is operating normally, or interrupt cleared

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |

| Legend: |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| bit 7   |         |         |         |         |         |         | bit 0   |

| SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   |

| R/W-1/1 |

# REGISTER 14-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRA<7:0>:** PORTA Slew Rate Enable bits For RA<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

# REGISTER 14-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLA<7:0>: PORTA Input Level Select bits

For RA<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

© 2016 Microchip Technology Inc.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRB<7:0>:** PORTB Slew Rate Enable bits For RB<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

0 = Port pin slews at maximum rate

## REGISTER 14-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLB<7:0>: PORTB Input Level Select bits For RB<7:0> pins, respectively

$\ensuremath{\mathtt{1}}$  = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

### TABLE 14-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTB   | RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     | 206                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  | 206                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   | 207                 |

| ANSELB  | ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 207                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 208                 |

| ODCONB  | ODCB7   | ODCB6   | ODCB5   | ODCB4   | ODCB3   | ODCB2   | ODCB1   | ODCB0   | 208                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 209                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 209                 |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

© 2016 Microchip Technology Inc.

| U-0              | U-0   | U-0               | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|-------|-------------------|---------|----------------|------------------|------------------|--------------|

| —                | —     | —                 | _       |                | ADAC1            | -<3:0>           |              |

| bit 7            |       |                   |         |                |                  |                  | bit 0        |

|                  |       |                   |         |                |                  |                  |              |

| Legend:          |       |                   |         |                |                  |                  |              |

| R = Readable     | bit   | W = Writable      | bit     | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is uncha | anged | x = Bit is unkr   | iown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared    |                |                  |                  |              |

|                  |       |                   |         |                |                  |                  |              |

REGISTER 20-3: ADACT: A/D AUTO-CONVERSION TRIGGER

bit 7-4 Unimplemented: Read as '0'

bit 3-0 ADACT<3:0>: Auto-Conversion Trigger Selection bits<sup>(1)</sup> (see Table 20-2)

**Note 1:** This is a rising edge sensitive input for all sources.

### REGISTER 23-3: CMxNSEL: COMPARATOR Cx NEGATIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| —     | _   | _   | _   | —   |         | NCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

# Legend:

| Logonan              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as '0'                              |

|---------|---------------------------------------------------------|

| bit 2-0 | NCH<2:0>: Comparator Negative Input Channel Select bits |

|         | 111 = CxVN connects to AVss                             |

|         | 110 = CxVN connects to FVR Buffer 2                     |

|         | 101 = CxVN unconnected                                  |

|         | 100 = CxVN unconnected                                  |

- 100 = CxVN unconnected

- 011 = CxVN connects to CxIN3- pin

- 010 = CxVN connects to CxIN2- pin

- 001 = CxVN connects to CxIN1- pin

- 000 = CxVN connects to CxIN0- pin

### REGISTER 23-4: CMxPSEL: COMPARATOR Cx POSITIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| —     | _   | —   | —   | —   |         | PCH<2:0> |         |

| bit 7 |     |     |     | •   |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 7-3 Unimplemented: Read as '0'

- bit 2-0 PCH<2:0>: Comparator Positive Input Channel Select bits

- 111 = CxVP connects to AVss

- 110 = CxVP connects to FVR Buffer 2

- 101 = CxVP connects to DAC output

- 100 = CxVP unconnected

- 011 = CxVP unconnected

- 010 = CxVP unconnected

- 001 = CxVP connects to CxIN1+ pin

- 000 = CxVP connects to CxIN0+ pin

# PIC16(L)F15356/75/76/85/86

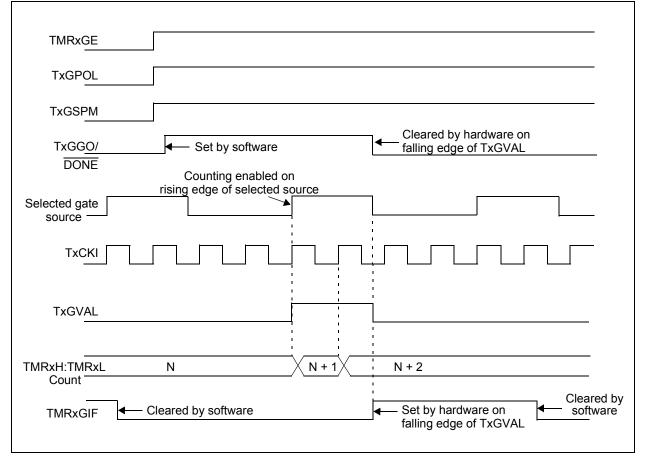

| FIGURE 26-4:           | TIMER1 GATE TOGGLE MODE                                                                                                                  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                                                                                                                          |

| TMRxGE                 |                                                                                                                                          |

| TxGPOL                 |                                                                                                                                          |

| TxGT <u>M</u>          |                                                                                                                                          |

| Selected<br>gate input |                                                                                                                                          |

| TxCKI                  |                                                                                                                                          |

| TxGVAL                 |                                                                                                                                          |

| TMRxH:TMRxL<br>Count   | $N \qquad \qquad$ |

# FIGURE 26-5: TIMER1 GATE SINGLE-PULSE MODE

# 28.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

The Capture/Compare/PWM modules available are shown in Table 28-1.

| TABLE 28-1: AVAILABLE CCP MODULE |

|----------------------------------|

|----------------------------------|

| Device                     | CCP1 | CCP2 |

|----------------------------|------|------|

| PIC16(L)F15356/75/76/85/86 | •    | •    |

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

#### 32.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 32-19 displays a standard waveform of a 7-bit address slave transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCL line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- Slave software reads ACKTIM bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: <u>SSPxBUF</u> cannot be loaded until after the ACK.

- 13. Slave sets the CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the ninth SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not  $\overline{ACK}$  the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

# 32.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPxCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPxIF, to be set (SSP interrupt, if enabled):

- Start condition generated

- · Stop condition generated

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

#### 32.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 32.7** "**Baud Rate Generator**" for more detail.

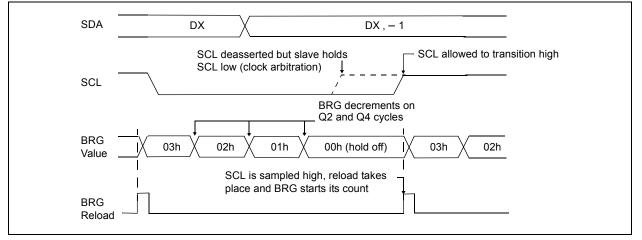

#### 32.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 32-25).

#### FIGURE 32-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

#### 32.6.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | writing to the lower five bits of SSPxCON2 |  |  |  |  |  |  |  |

|       | is disabled until the Start condition is   |  |  |  |  |  |  |  |

|       | complete.                                  |  |  |  |  |  |  |  |

| TABLE 37-9: P | LL SPECIFICATIONS |

|---------------|-------------------|

|---------------|-------------------|

| Standard Operating Conditions (unless otherwise stated) VDD $\ge 2.5V$ |         |                                             |       |       |                     |       |            |

|------------------------------------------------------------------------|---------|---------------------------------------------|-------|-------|---------------------|-------|------------|

| Param.<br>No.                                                          | Sym.    | Characteristic                              | Min.  | Тур†  | Max.                | Units | Conditions |

| PLL01                                                                  | FPLLIN  | PLL Input Frequency Range                   | 4     | _     | 8                   | MHz   |            |

| PLL02                                                                  | FPLLOUT | PLL Output Frequency Range                  | 16    | —     | 32                  | MHz   | Note 1     |

| PLL03                                                                  | TPLLST  | PLL Lock Time from Start-up                 | —     | 200 / | $\langle - \rangle$ | μs_   | -          |

| PLL04                                                                  | FPLLJIT | PLL Output Frequency Stability (Jitter)     | -0.25 | \     | 0.25                | -%    |            |

| *                                                                      | These p | arameters are characterized but not tested. | •     | •     |                     | •     |            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: The output frequency of the PLL must meet the Fosc requirements listed in Parameter D002.