Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15376-e-mv |

## **Digital Peripherals (Cont.)**

- · I/O Pins:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

- Input level selection control (ST or TTL)

- Digital open-drain enable

- · Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

### **Analog Peripherals**

- Analog-to-Digital Converter (ADC):

- 10-bit with up to 43 external channels

- Operates in Sleep

- · Two Comparators:

- FVR, DAC and external input pin available on inverting and noninverting input

- Software selectable hysteresis

- Outputs available internally to other modules, or externally through PPS

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- · Voltage Reference:

- Fixed Voltage Reference with 1.024V, 2.048V and 4.096V output levels

- Zero-Cross Detect module:

- AC high voltage zero-crossing detection for simplifying TRIAC control

- Synchronized switching control and timing

#### **Flexible Oscillator Structure**

- · High-Precision Internal Oscillator:

- Software selectable frequency range up to 32 MHz, ±1% typical

- x2/x4 PLL with Internal and External Sources

- Low-Power Internal 32 kHz Oscillator (LFINTOSC)

- External 32 kHz Crystal Oscillator (SOSC)

- External Oscillator Block with:

- Three crystal/resonator modes up to 20 MHz

- Three external clock modes up to 32 MHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if primary clock stops

- Oscillator Start-up Timer (OST):

- Ensures stability of crystal oscillator resources

PIC16(L)F15356/75/76/85/86

| TABLE 4: | 40/44-PIN ALLOCATION TABLE (F       | PIC16(L)F15375, PIC16(L)F15376)       |

|----------|-------------------------------------|---------------------------------------|

| ·/ \     | 10/11   IN //LLCC//IION   I/(BLL (I | 1 10 10(2): 100/0, 1 10 10(2): 100/0/ |

| VO(2) | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC                  | Reference | Comparator       | NCO | DAC      | Timers                        | CCP                 | PWM | CWG                 | MSSP                          | ZCD  | EUSART                    | CLC                   | CLKR | Interrupt                   | dn-IIn4 | Basic           |

|-------|-------------|-------------|------------|-------------|----------------------|-----------|------------------|-----|----------|-------------------------------|---------------------|-----|---------------------|-------------------------------|------|---------------------------|-----------------------|------|-----------------------------|---------|-----------------|

| RA0   | 2           | 17          | 19         | 19          | ANA0                 | -         | C1IN0-<br>C2IN0- | 1   | _        | _                             | _                   | _   | _                   | _                             | _    | _                         | CLCINO <sup>(1)</sup> | -    | IOCA0                       | Υ       | _               |

| RA1   | 3           | 18          | 20         | 20          | ANA1                 | _         | C1IN1-<br>C2IN1- | _   | _        | _                             | _                   | _   | _                   | _                             | _    | _                         | CLCIN1 <sup>(1)</sup> | _    | IOCA1                       | Y       | _               |

| RA2   | 4           | 19          | 21         | 21          | ANA2                 | _         | C1IN0+<br>C2IN0+ | _   | DAC1OUT1 | _                             | _                   | _   | _                   | _                             | _    | _                         | _                     | _    | IOCA2                       | Y       | _               |

| RA3   | 5           | 20          | 22         | 22          | ANA3                 | VREF+     | C1IN1+           | 1   | DACREF+  | _                             | _                   | _   | _                   | _                             | _    | _                         | _                     | _    | IOCA3                       | Υ       | _               |

| RA4   | 6           | 21          | 23         | 23          | ANA4                 | _         | _                | _   | _        | T0CKI <sup>(1)</sup>          | _                   | _   | _                   | _                             | _    | _                         | _                     | _    | IOCA4                       | Υ       | _               |

| RA5   | 7           | 22          | 24         | 24          | ANA5                 | _         | _                | _   | _        | T1G <sup>(1)</sup>            | _                   | _   | _                   | SS1 <sup>(1)</sup>            | _    | _                         | _                     | _    | IOCA5                       | Υ       | _               |

| RA6   | 14          | 29          | 33         | 31          | ANA6                 | _         | _                | _   | _        | _                             | _                   | _   | _                   | _                             | _    | _                         | _                     | _    | IOCA6                       | Υ       | CLKOUT/<br>OSC1 |

| RA7   | 13          | 28          | 32         | 30          | ANA7                 | _         | _                | _   | _        | _                             | _                   | _   | _                   | _                             | _    | _                         | _                     | _    | IOCA7                       | Y       | CLKIN/<br>OSC2  |

| RB0   | 33          | 8           | 9          | 8           | ANB0                 | _         | C2IN1+           | -   | _        | _                             | _                   | _   | CWG1 <sup>(1)</sup> | SS2 <sup>(1)</sup>            | ZCD1 | _                         | _                     | _    | INT <sup>(1)</sup><br>IOCB0 | Υ       | _               |

| RB1   | 34          | 9           | 10         | 9           | ANB1                 | _         | C1IN3-<br>C2IN3- | _   | _        | _                             | _                   | _   | _                   | SCL1<br>SCK1 <sup>(1,4)</sup> | _    | _                         | _                     | _    | IOCB1                       | Υ       | _               |

| RB2   | 34          | 10          | 11         | 10          | ANB2                 | _         | _                | _   | -        | _                             | _                   | _   | _                   | SDA1<br>SDI1 <sup>(1,4)</sup> | _    | _                         | _                     | _    | IOCB2                       | Y       | _               |

| RB3   | 36          | 11          | 12         | 11          | ANB3                 | _         | C1IN2-<br>C2IN2- | _   | _        | _                             | _                   | _   | _                   | _                             | _    | _                         | _                     | _    | IOCB3                       | Y       | _               |

| RB4   | 37          | 12          | 14         | 14          | ANB4<br>ADACT<br>(1) | _         |                  | ı   | _        | _                             | _                   | _   | _                   | _                             | ı    | 1                         | -                     | ı    | IOCB4                       | Y       | _               |

| RB5   | 38          | 13          | 15         | 15          | ANB5                 | _         | _                | 1   | _        | _                             | _                   | _   | _                   | _                             | _    | _                         | _                     | _    | IOCB5                       | Υ       | _               |

| RB6   | 39          | 14          | 16         | 16          | ANB6                 | _         | _                |     | _        | _                             | _                   | _   | _                   | _                             | _    | TX2<br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> | ı    | IOCB6                       | Y       | ICSPCLK         |

| RB7   | 40          | 15          | 17         | 17          | ANB7                 | _         | _                | -   | DAC1OUT2 | _                             | _                   | _   | _                   | _                             | _    | RX2<br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> |      | IOCB7                       | Y       | ICSPDAT         |

| RC0   | 15          | 30          | 34         | 32          | ANC0                 | _         | _                | _   | _        | SOSCO<br>T1CKI <sup>(1)</sup> | _                   | _   | _                   | -                             | _    | _                         | _                     | ı    | IOCC0                       | Υ       | _               |

| RC1   | 16          | 31          | 35         | 35          | ANC1                 | _         | _                | ı   | _        | SOSCI                         | CCP2 <sup>(1)</sup> | _   | _                   | _                             | _    | _                         | _                     | _    | IOCC1                       | Υ       | _               |

| RC2   | 17          | 32          | 36         | 36          | ANC2                 | _         | _                | -   | _        | _                             | CCP1 <sup>(1)</sup> | _   | _                   | _                             | _    | _                         | _                     | -    | IOCC2                       | Υ       | _               |

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

<sup>2:</sup> All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options.

<sup>3:</sup> This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

<sup>4:</sup> These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address          | Name     | Bit 7                                   | Bit 6       | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|------------------|----------|-----------------------------------------|-------------|---------|---------------|-------------------|-----------|-----------|-----------|-----------------------|----------------------------|

| Bank 2           |          |                                         |             |         |               |                   |           |           |           |                       |                            |

|                  |          |                                         |             | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics |           |           |                       |                            |

| 10Ch<br><br>118h | -        |                                         |             |         | Unimpler      | mented            |           |           |           | _                     | ı                          |

| 119h             | RC1REG   | EUSART Receive Dat                      | a Register  |         |               |                   |           |           |           | 0000 0000             | 0000 0000                  |

| 11Ah             | TX1REG   | EUSART Transmit Da                      | ta Register |         |               |                   |           |           |           | 0000 0000             | 0000 0000                  |

| 11Bh             | SP1BRGL  |                                         |             |         | SP1BR0        | G<7:0>            |           |           |           | 0000 0000             | 0000 0000                  |

| 11Ch             | SP1BRGH  |                                         |             |         | SP1BRG        | <15:8>            |           |           |           | 0000 0000             | 0000 0000                  |

| 11Dh             | RC1STA   | SPEN RX9 SREN CREN ADDEN FERR OERR RX9D |             |         |               |                   |           | 0000 0000 | 0000 0000 |                       |                            |

| 11Eh             | TX1STA   | CSRC                                    | TX9         | TXEN    | SYNC          | SENDB             | BRGH      | TRMT      | TX9D      | 0000 0010             | 0000 0010                  |

| 11Fh             | BAUD1CON | ABDOVF                                  | RCIDL       | _       | SCKP          | BRG16             | _         | WUE       | ABDEN     | 01-0 0-00             | 01-0 0-00                  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                             | Name            | Bit 7 | Bit 6 | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------------------------|-----------------|-------|-------|---------|---------------|-------------------|-----------|-------|-------|-----------------------|----------------------------|

| Bank 8-10                           |                 |       |       |         |               |                   |           |       |       |                       |                            |

|                                     |                 |       |       | CPU COR | RE REGISTERS; | see Table 4-3 for | specifics |       |       |                       |                            |

| x0Ch/<br>x8Ch<br>—<br>x1Fh/<br>x9Fh | — Unimplemented |       |       |         |               |                   |           |       |       |                       |                            |

$\textbf{Legend:} \qquad \textbf{x} \ = \text{unknown}, \textbf{u} \ = \text{unchanged}, \textbf{q} \ = \text{depends on condition}, \textbf{-} = \text{unimplemented}, \text{read as '0'}, \textbf{r} \ = \text{reserved}. \ Shaded \ locations \ unimplemented}, \text{read as '0'}.$

TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address           | Name    | Bit 7         | Bit 6            | Bit 5     | Bit 4         | Bit 3             | Bit 2     | Bit 1       | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------|---------|---------------|------------------|-----------|---------------|-------------------|-----------|-------------|-------|-----------------------|----------------------------|

| Bank 17           |         |               |                  |           |               |                   |           |             |       |                       |                            |

|                   |         |               |                  | CPU COF   | RE REGISTERS; | see Table 4-3 for | specifics |             |       |                       |                            |

| 88Ch              | CPUDOZE | IDLEN         | DOZEN            | ROI       | DOE           | _                 | DOZE2     | DOZE1       | DOZE0 | 0000 -000             | u000 -000                  |

| 88Dh              | OSCCON1 | _             |                  | NOSC<2:0> |               |                   | ND        | IV<3:0>     |       | -qqq 0000             | -qqq 0000                  |

| 88Eh              | OSCCON2 | _             |                  | COSC<2:0> |               | CDIV<3:0>         |           |             |       | -ddd dddd             | -qqq qqqq                  |

| 88Fh              | OSCCON3 | CSWHOLD       | SOSCPWR          | _         | ORDY          | NOSCR             | _         | _           | _     | 00-0 0                | 00-0 0                     |

| 890h              | OSCSTAT | EXTOR         | HFOR             | MFOR      | LFOR          | SOR               | ADOR      | _           | PLLR  | q000 qq-0             | qqqq qq-q                  |

| 891h              | OSCEN   | EXTOEN        | HFOEN            | MFOEN     | LFOEN         | SOSCEN            | ADOEN     | _           | _     | 0000 00               | 0000 00                    |

| 892h              | OSCTUNE | _             | _                |           |               | HFT               | JN<5:0>   |             |       | 10 0000               | 10 0000                    |

| 893h              | OSCFRQ  | _             | _                | _         | _             | _                 |           | HFFRQ<2:0   | >     | qqq                   | qqq                        |

| 894h              | _       |               |                  |           | Unimpler      | nented            |           |             |       | _                     | _                          |

| 895h              | CLKRCON | CLKREN        | _                | _         | CLKRD         | C<1:0>            |           | CLKRDIV<2:0 | )>    | 0x xxxx               | 0u uuuu                    |

| 896h              | CLKRCLK | _             | — — CLKRCLK<3:0> |           |               |                   |           |             | 0000  | 0000                  |                            |

| 897h<br>—<br>89Fh | _       | Unimplemented |                  |           |               |                   |           | _           | _     |                       |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

### 5.0 DEVICE CONFIGURATION

Device configuration consists of the Configuration Words, User ID, Device ID, Device Information Area (DIA), (see **Section 6.0 "Device Information Area"**), and the Device Configuration Information (DCI) regions, (see **Section 7.0 "Device Configuration Information"**).

## 5.1 Configuration Words

The devices have several Configuration Words starting at address 8007h. The Configuration bits establish configuration values prior to the execution of any software; Configuration bits enable or disable device-specific features.

In terms of programming, these important Configuration bits should be considered:

#### 1. LVP: Low-Voltage Programming Enable bit

- 1 = ON Low-Voltage Programming is enabled. MCLR/VPP pin function is MCLR. MCLRE Configuration bit is ignored.

- 0 = OFF HV on MCLR/VPP must be used for programming.

## 2. CP: User Nonvolatile Memory (NVM) Program Memory Code Protection bit

- 1 = OFF User NVM code protection disabled

- 0 = ON User NVM code protection enabled

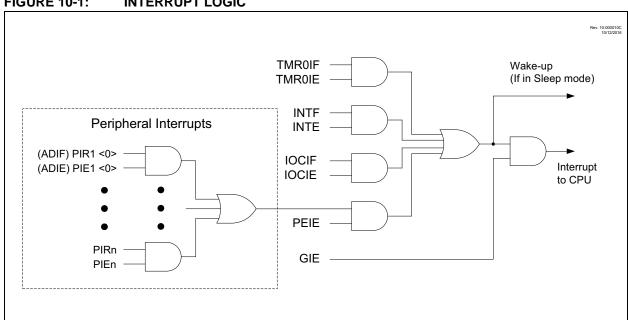

### 10.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- · Interrupt Latency

- · Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 10-1.

**FIGURE 10-1: INTERRUPT LOGIC**

**Preliminary** © 2016 Microchip Technology Inc. DS40001866A-page 142

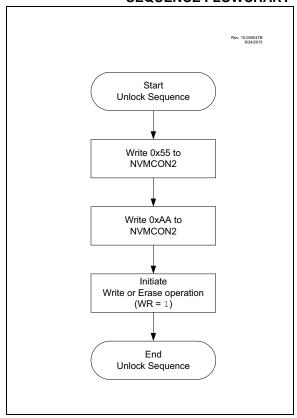

#### 13.3.2 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- · Load of PFM write latches

- · Write of PFM write latches to PFM memory

- · Write of PFM write latches to User IDs

The unlock sequence consists of the following steps and must be completed in order:

- Write 55h to NVMCON2

- · Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Note: The two NOP instructions after setting the WR bit that were required in previous devices are not required for PIC16(L)F15356/75/76/85/86 devices. See Figure 13-2.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

## FIGURE 13-2: NVM UNLOCK SEQUENCE FLOWCHART

### **EXAMPLE 13-2: NVM UNLOCK SEQUENCE**

```

BCF

INTCON, GIE

; Recommended so sequence is not interrupted

BANKSEL

NVMCON1

NVMCON1, WREN

; Enable write/erase

MOVLW

55h

; Load 55h

NVMCON2

MOVWF

; Step 1: Load 55h into NVMCON2

; Step 2: Load W with AAh

MOVLW

AAh

MOVWF

NVMCON2

; Step 3: Load AAH into NVMCON2

BSF

NVMCON1, WR

; Step 4: Set WR bit to begin write/erase

BSF

INTCON, GIE

; Re-enable interrupts

```

Note 1: Sequence begins when NVMCON2 is written; steps 1-4 must occur in the cycle-accurate order shown.

2: Opcodes shown are illustrative; any instruction that has the indicated effect may be used.

### REGISTER 14-30: ODCOND: PORTD OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2   | ODCD1   | ODCD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **ODCD<7:0>:** PORTD Open-Drain Enable bits

For RD<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 14-31: SLRCOND: PORTD SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 SLRD<7:0>: PORTD Slew Rate Enable bits

For RD<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

## REGISTER 14-32: INLVLD: PORTD INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 INLVLD<7:0>: PORTD Input Level Select bits

For RD<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

## REGISTER 16-4: PMD3: PMD CONTROL REGISTER 3

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | PWM6MD  | PWM5MD  | PWM4MD  | PWM3MD  | CCP2MD  | CCP1MD  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-6 | Unimplemented: Read as '0'                                                                             |

|---------|--------------------------------------------------------------------------------------------------------|

| bit 5   | <b>PWM6MD:</b> Disable Pulse-Width Modulator PWM6 bit 1 = PWM6 module disabled 0 = PWM6 module enabled |

| bit 4   | <b>PWM5MD:</b> Disable Pulse-Width Modulator PWM5 bit 1 = PWM5 module disabled 0 = PWM5 module enabled |

| bit 3   | <b>PWM4MD:</b> Disable Pulse-Width Modulator PWM4 bit 1 = PWM4 module disabled 0 = PWM4 module enabled |

| bit 2   | <b>PWM3MD:</b> Disable Pulse-Width Modulator PWM3 bit 1 = PWM3 module disabled 0 = PWM3 module enabled |

| bit 1   | CCP2MD: Disable CCP2 bit  1 = CCP2 module disabled  0 = CCP2 module enabled                            |

| bit 0   | CCP1MD: Disable CCP1 bit  1 = CCP1 module disabled  0 = CCP1 module enabled                            |

#### REGISTER 17-10: IOCEP: INTERRUPT-ON-CHANGE PORTE POSITIVE EDGE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0            | R/W/HS-0/0            | R/W/HS-0/0            |

|-------|-----|-----|-----|------------|-----------------------|-----------------------|-----------------------|

| _     | _   | _   | _   | IOCEP3     | IOCEP2 <sup>(1)</sup> | IOCEP1 <sup>(1)</sup> | IOCEP0 <sup>(1)</sup> |

| bit 7 |     |     |     |            |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 IOCEP<3:0>: Interrupt-on-Change PORTE Positive Edge Enable bit

1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

**Note 1:** Present only on PIC16(L)F15375/76/85/86.

#### REGISTER 17-11: IOCEN: INTERRUPT-ON-CHANGE PORTE NEGATIVE EDGE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0            | R/W/HS-0/0            | R/W/HS-0/0            |

|-------|-----|-----|-----|------------|-----------------------|-----------------------|-----------------------|

| _     | _   | _   | _   | IOCEN3     | IOCEN2 <sup>(1)</sup> | IOCEN1 <sup>(1)</sup> | IOCEN0 <sup>(1)</sup> |

| bit 7 |     |     |     |            |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 **IOCEN<3:0>:** Interrupt-on-Change PORTE Negative Edge Enable bit

1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

Note 1: Present only on PIC16(L)F15375/76/85/86.

## 20.4 Register Definitions: ADC Control

### REGISTER 20-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------|---------|---------|---------|---------|---------|---------|---------|

| CHS<5:0> |         |         |         | GO/DONE | ADON    |         |         |

| bit 7    |         |         |         |         |         |         | bit 0   |

```

Legend:

W = Writable bit

U = Unimplemented bit, read as '0'

u = Bit is unchanged

x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set

'0' = Bit is cleared

```

```

bit 7-2

CHS<5:0>: Analog Channel Select bits

111111 = FVR Buffer 2 reference voltage<sup>(2)</sup>

111110 =

FVR 1Buffer 1 reference voltage<sup>(2)</sup>

111101 = DAC1 output voltage<sup>(1)</sup>

Temperature sensor output(3)

111100 =

111011 = AVss (Analog Ground)

111010-100000 = Reserved. No channel connected

101111 = RF7

101110 =

RF6

101101 =

RF5

101100 =

RF4

101011 =

RF3

101010 =

RF2

101001 =

RF1

101000 =

RF0

100010 =

RE2

100001 =

RE1

100000 =

RE0

011111 =

RD7

011110 =

RD5

011101 =

011100 =

RD4

011011 =

RD3

RD2

011010 =

011001 =

RD1

011000 =

RD0

RC7<sup>(4)</sup>

010111 =

RC6<sup>(4)</sup>

010110 =

010101 =

RC5

010100 =

RC4

010011 =

RC3

010010 =

RC2

010001 =

RC1

RC0

010000 =

RB7<sup>(4)</sup>

001111 =

RB6<sup>(4)</sup>

001110 =

RB5<sup>(4)</sup>

001101 =

RB4<sup>(4)</sup>

001100 =

001011-000110 = Reserved

000101 = RA5

000100 =

RA4

RA3

000011 =

000010 =

RA2

000001 =

RA1

000000 =

RA0

```

bit 1 GO/DONE: ADC Conversion Status bit

1 = ADC conversion cycle in progress. Setting this bit starts an ADC conversion cycle.

This bit is automatically cleared by hardware when the ADC conversion has completed.

0 = ADC conversion completed/not in progress

### REGISTER 20-2: ADCON1: ADC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----------|---------|-----|-----|---------|---------|

| ADFM    |         | ADCS<2:0> |         | _   | _   | ADPRE   | F<1:0>  |

| bit 7   |         |           |         |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 ADFM: ADC Result Format Select bit

1 = Right justified. Six Most Significant bits of ADRESH are set to '0' when the conversion result is loaded.

0 = Left justified. Six Least Significant bits of ADRESL are set to '0' when the conversion result is loaded.

bit 6-4 ADCS<2:0>: ADC Conversion Clock Select bits

111 = ADCRC (dedicated RC oscillator)

110 = Fosc/64

101 = Fosc/16

100 = Fosc/4

011 = ADCRC (dedicated RC oscillator)

010 = Fosc/32

001 = Fosc/8

000 = Fosc/2

bit 3-2 **Unimplemented:** Read as '0'

bit 1-0 ADPREF<1:0>: ADC Positive Voltage Reference Configuration bits

11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module<sup>(1)</sup>

10 = VREF+ is connected to external VREF+  $pin^{(1)}$

01 = Reserved

00 = VREF+ is connected to VDD

**Note 1:** When selecting the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See Table 37-14 for details.

### 25.0 TIMERO MODULE

The Timer0 module is an 8/16-bit timer/counter with the following features:

- 16-bit timer/counter

- · 8-bit timer/counter with programmable period

- · Synchronous or asynchronous operation

- · Selectable clock sources

- Programmable prescaler (independent of Watchdog Timer)

- · Programmable postscaler

- · Operation during Sleep mode

- · Interrupt on match or overflow

- · Output on I/O pin (via PPS) or to other peripherals

## 25.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

#### 25.1.1 16-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

## 25.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0, which is neither directly readable nor writable (see Figure 25-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### 25.1.2 8-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

The value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- · TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh.

Both the prescaler and postscaler counters are cleared on the following events:

- · A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or

- Brown-out Reset (BOR)

#### 25.1.3 COUNTER MODE

In Counter mode, the prescaler is normally disabled by setting the T0CKPS bits of the T0CON1 register to '0000'. Each rising edge of the clock input (or the output of the prescaler if the prescaler is used) increments the counter by '1'.

#### 25.1.4 TIMER MODE

In Timer mode, the Timer0 module will increment every instruction cycle as long as there is a valid clock signal and the T0CKPS bits of the T0CON1 register (Register 25-2) are set to '0000'. When a prescaler is added, the timer will increment at the rate based on the prescaler value.

### 25.1.5 ASYNCHRONOUS MODE

When the TOASYNC bit of the TOCON1 register is set (TOASYNC = '1'), the counter increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows the counter to continue operation during Sleep mode provided that the clock also continues to operate during Sleep.

### 25.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system oscillator (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

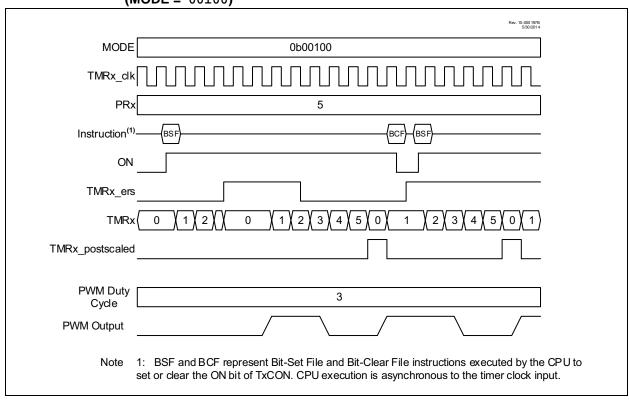

## 27.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- Reset on rising or falling edge (MODE<4:0>= 00011)

- Reset on rising edge (MODE<4:0> = 00100)

- Reset on falling edge (MODE<4:0> = 00101)

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two clock delay. Refer to Figure 27-6.

# FIGURE 27-6: EDGE-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00100)

## 32.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an I<sup>2</sup>C slave in 10-bit Addressing mode.

Figure 32-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish I<sup>2</sup>C communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- Software clears the SSPxIF bit.

- Software reads received address from SSPxBUF clearing the BF flag.

- Slave loads low address into SSPxADD, releasing SCL.

- Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

Slave sends ACK and SSPxIF is set.

**Note:** If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCL pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

## 32.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 32-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 32-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

#### 33.1.2.3 Receive Interrupts

The RXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RXxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RXxIF interrupts are enabled by setting all of the following bits:

- RXxIE, Interrupt Enable bit of the PIE3 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RXxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

### 33.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCxSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCxREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCxSTA register which resets the EUSART. Clearing the CREN bit of the RCxSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note: If all receive characters in the receive FIFO have framing errors, repeated reads of the RCxREG will not clear the FERR bit.

#### 33.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCxSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCxSTA register or by resetting the EUSART by clearing the SPEN bit of the RCxSTA register.

#### 33.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

#### 33.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RXxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

| BCF              | Bit Clear f                                                            |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                      |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ 0 &\leq b \leq 7 \end{aligned}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                              |

| Status Affected: | None                                                                   |

| Description:     | Bit 'b' in register 'f' is cleared.                                    |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$                                                                                                                                                                               |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.  If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRA label<br>[ label ] BRA \$+k                                                                                                                                                                                     |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255<br>-256 ≤ k ≤ 255                                                                                                                                                                                 |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |

| BRW              | Relative Branch with W                                                                                                                                                                        |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRW                                                                                                                                                                                 |

| Operands:        | None                                                                                                                                                                                          |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + (W). This instruction is a 2-cycle instruction |

| BSF              | Bit Set f                                                              |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [ label ] BSF f,b                                                      |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ 0 &\leq b \leq 7 \end{aligned}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                              |

| Status Affected: | None                                                                   |

| Description:     | Bit 'b' in register 'f' is set.                                        |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2-cycle instruction. |

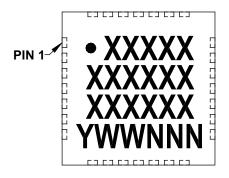

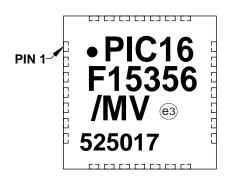

#### 40.1 **Package Marking Information (Continued)**

28-Lead UQFN (4x4x0.5 mm) and (6x6 mm)

Legend: XX...X Customer-specific information

> Υ Year code (last digit of calendar year) ΥY Year code (last 2 digits of calendar year)  $\mathsf{WW}$ Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

**Preliminary** © 2016 Microchip Technology Inc. DS40001866A-page 553

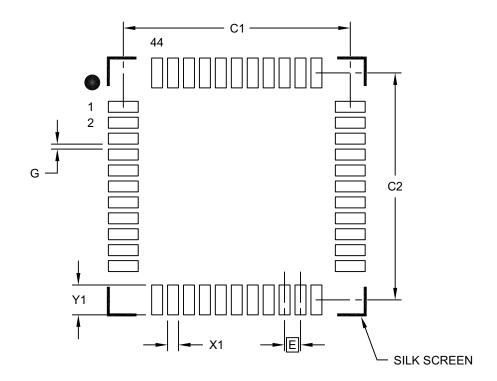

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |       |      |

|--------------------------|-------------|----------|-------|------|

| Dimension Limits         |             | MIN      | NOM   | MAX  |

| Contact Pitch            | Е           | 0.80 BSC |       |      |

| Contact Pad Spacing      | C1          |          | 11.40 |      |

| Contact Pad Spacing      | C2          |          | 11.40 |      |

| Contact Pad Width (X44)  | X1          |          |       | 0.55 |

| Contact Pad Length (X44) | Y1          |          |       | 1.50 |

| Distance Between Pads    | G           | 0.25     |       |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B