Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15376-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-4:** PIC16(L)F15385/86 PINOUT DESCRIPTION (CONTINUED)

| Name                                                            | Function | Input<br>Type | Output Type       | Description                    |

|-----------------------------------------------------------------|----------|---------------|-------------------|--------------------------------|

| RF5/ANF5                                                        | RF5      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF5     | AN            | _                 | ADC Channel D0 input.          |

| RF6/ANF6                                                        | RF6      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF6     | AN            | —                 | ADC Channel D0 input.          |

| RF7/ANF7                                                        | RF5      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF5     | AN            | _                 | ADC Channel D0 input.          |

| VDD                                                             | Vdd      | Power         | _                 | Positive supply voltage input. |

| Vss                                                             | Vss      | Power         | _                 | Ground reference.              |

| Legend: AN = Analog input or outp<br>TTL = TTL compatible input |          |               | mpatible input or |                                |

TTL = TTL compatible input

HV = High Voltage

XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-7.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for  $l^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the  $l^2C$  specific or SMBus input buffer thresholds. 4:

|      | BANK 24                                                   |      | BANK 25                                                   |      | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                       |

|------|-----------------------------------------------------------|------|-----------------------------------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| C00h | Core Registers<br>(Table 4-3)                             | C80h | Core Registers<br>(Table 4-3)                             | D00h | Core Registers<br>(Table 4-3) | D80h | Core Registers<br>(Table 4-3) | E00h | Core Registers<br>(Table 4-3) | E80h | Core Registers<br>(Table 4-3) | F00h | Core Registers<br>(Table 4-3) | F80h | Core Registers<br>(Table 4-3) |

| C0Bh |                                                           | C8Bh |                                                           | D0Bh |                               | D8Bh |                               | E0Bh |                               | E8Bh |                               | F0Bh |                               | F8Bh |                               |

| COCh | Unimplemented<br>Read as '0'                              | C8Ch | Unimplemented<br>Read as '0'                              | DOCh | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |

| C1Fh |                                                           | C9Fh |                                                           |      |                               |      |                               |      |                               |      |                               |      |                               |      |                               |

| C20h |                                                           | CA0h |                                                           |      |                               |      |                               |      |                               |      |                               |      |                               |      |                               |

|      | General<br>Purpose<br>Register<br>80 Bytes <sup>(1)</sup> |      | General<br>Purpose<br>Register<br>80 Bytes <sup>(1)</sup> |      |                               |      |                               |      |                               |      |                               |      |                               |      |                               |

| C6Fh |                                                           | CEFh |                                                           | D6Fh |                               | DEFh |                               | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                               |

| C70h | Accesses<br>70h – 7Fh                                     | CF0h | Accesses<br>70h – 7Fh                                     | D70h | Accesses<br>70h – 7Fh         | DF0h | Accesses<br>70h – 7Fh         | E70h | Accesses<br>70h – 7Fh         | EF0h | Accesses<br>70h – 7Fh         | F70h | Accesses<br>70h – 7Fh         | FF0h | Accesses<br>70h – 7Fh         |

|      |                                                           |      |                                                           |      |                               |      |                               |      |                               |      |                               |      |                               |      |                               |

#### TABLE 4-7: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANK 24-31

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Present only in PIC16(L)F15356/76/86.

| Address  | Name | Bit 7         | Bit 6         | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|----------|------|---------------|---------------|---------|---------------|-------------------|-----------|--------|--------|-----------------------|----------------------------|

| Bank 15  |      |               |               |         |               |                   |           |        |        |                       |                            |

|          |      |               |               | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics |        |        |                       |                            |

| 78Ch<br> | _    |               | Unimplemented |         |               |                   |           |        |        | —                     | _                          |

| 796h     | PMD0 | SYSCMD        | FVRMD         | _       | _             | _                 | NVMMD     | CLKRMD | IOCMD  | 00000                 | 00000                      |

| 797h     | PMD1 | NCO1MD        | _             | _       | _             | _                 | TMR2MD    | TMR1MD | TMR0MD | 0000                  | 0000                       |

| 798h     | PMD2 | _             | DAC1MD        | ADCMD   | _             | _                 | CMP2MD    | CMP1MD | ZCDMD  | -00000                | -00000                     |

| 799h     | PMD3 | _             | _             | PWM6MD  | PWM5MD        | PWM4MD            | PWM3MD    | CCP2MD | CCP1MD | 00 0000               | 00 0000                    |

| 79Ah     | PMD4 | UART2MD       | UART1MD       | MSSP2MD | MSSP1MD       |                   |           | _      | CWG1MD | 00000                 | 00000                      |

| 79Bh     | PMD5 | _             | _             | —       | CLC4MD        | CLC3MD            | CLC2MD    | CLC1MD | _      | 0 000-                | 0 000-                     |

| 79Ch     | _    |               | Unimplemented |         |               |                   |           |        |        | —                     | _                          |

| 79Dh     | _    | Unimplemented |               |         |               |                   |           | —      | _      |                       |                            |

| 79Eh     | _    |               | Unimplemented |         |               |                   |           |        |        | —                     | _                          |

| 79Fh     | _    |               | Unimplemented |         |               |                   |           |        |        | _                     | _                          |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address             | Name    | Bit 7   | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------------------|---------|---------|---------------|---------|---------|---------|---------|---------|---------|-----------------------|----------------------------|

| Bank 62 (Continued) |         |         |               |         |         |         |         |         |         |                       |                            |

| 1F38h               | ANSELA  | ANSA7   | ANSA6         | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 1111 1111             | 1111 1111                  |

| 1F39h               | WPUA    | WPUA7   | WPUA6         | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 0000 0000             | 0000 0000                  |

| 1F3Ah               | ODCONA  | ODCA7   | ODCA6         | ODCA5   | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   | 0000 0000             | 0000 0000                  |

| 1F3Bh               | SLRCONA | SLRA7   | SLRA6         | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 1111 1111             | 1111 1111                  |

| 1F3Ch               | INLVLA  | INLVLA7 | INLVLA6       | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 1111 1111             | 1111 1111                  |

| 1F3Dh               | IOCAP   | IOCAP7  | IOCAP6        | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  | 0000 0000             | 0000 0000                  |

| 1F3Eh               | IOCAN   | IOCAN7  | IOCAN6        | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  | 0000 0000             | 0000 0000                  |

| 1F3Fh               | IOCAF   | IOCAF7  | IOCAF6        | IOCAF5  | IOCAF4  | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  | 0000 0000             | 0000 0000                  |

| 1F40h               | _       |         |               |         | Unimple | mented  |         |         |         | _                     | —                          |

| 1F41h               | _       |         |               |         | Unimple | mented  |         |         |         | _                     | _                          |

| 1F42h               | _       |         |               |         | Unimple | mented  |         |         |         | _                     | _                          |

| 1F43h               | ANSELB  | ANSB7   | ANSB6         | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 1111 1111             | 1111 1111                  |

| 1F44h               | WPUB    | WPUB7   | WPUB6         | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 0000 0000             | 0000 0000                  |

| 1F45h               | ODCONB  | ODCB7   | ODCB6         | ODCB5   | ODCB4   | ODCB3   | ODCB2   | ODCB1   | ODCB0   | 0000 0000             | 0000 0000                  |

| 1F46h               | SLRCONB | SLRB7   | SLRB6         | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 1111 1111             | 1111 1111                  |

| 1F47h               | INLVLB  | INLVLB7 | INLVLB6       | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 1111 1111             | 1111 1111                  |

| 1F48h               | IOCBP   | IOCBP7  | IOCBP6        | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2  | IOCBP1  | IOCBP0  | 0000 0000             | 0000 0000                  |

| 1F49h               | IOCBN   | IOCBN7  | IOCBN6        | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  | 0000 0000             | 0000 0000                  |

| 1F4Ah               | IOCBF   | IOCBF7  | IOCBF6        | IOCBF5  | IOCBF4  | IOCBF3  | IOCBF2  | IOCBF1  | IOCBF0  | 0000 0000             | 0000 0000                  |

| 1F4Bh               | _       |         | Unimplemented |         |         |         |         |         |         | _                     | —                          |

| 1F4Ch               | _       |         | Unimplemented |         |         |         |         |         |         | _                     | —                          |

| 1F4Dh               | _       |         |               |         | Unimple | mented  |         |         |         | _                     | _                          |

#### DECISTED SUMMADY DANKS 0 62 (CONTINUED)

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

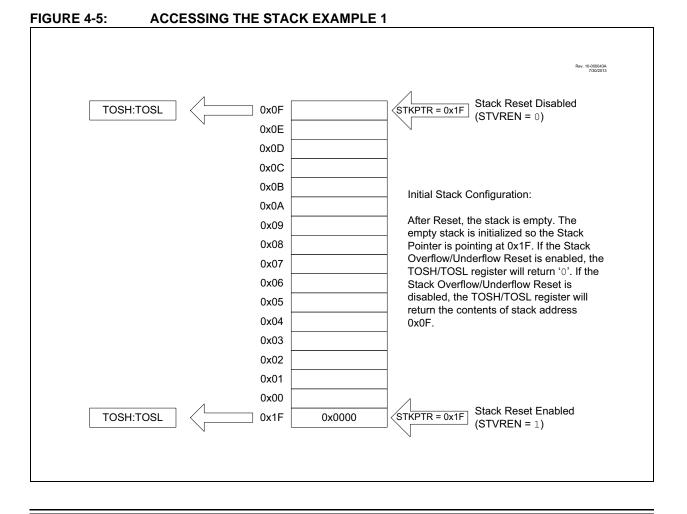

#### 4.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figure 4-5 through Figure 4-8). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 4.5.1 ACCESSING THE STACK

The stack is accessible through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. STKPTR can be monitored to obtain to value of stack memory left at any given time. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC value from the stack and then decrement the STKPTR.

Reference Figure 4-5 through Figure 4-8 for examples of accessing the stack.

condition or the VDD level.

BOR IS ALWAYS OFF

When the BOREN bits of the Configuration Words are

programmed to '00', the BOR is off at all times. The

device start-up is not delayed by the BOR ready

8.2.4

#### 8.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### FIGURE 8-2: BROWN-OUT SITUATIONS

### VDD VBOR Internal T<sub>PWRT</sub>(1) Reset VDD VBOR Internal < TPWR TPWRT(1) Reset VDD VBOR Internal T<sub>PWRT</sub>(1) Reset Note 1: TPWRT delay only if PWRTE bit is programmed to '0'.

© 2016 Microchip Technology Inc.

| FIGURE 10    | )-2: II                                                                                                                                     | NTERRUPT LA                              | TENCY  |         |             |                |                              |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------|---------|-------------|----------------|------------------------------|--|

|              |                                                                                                                                             |                                          |        |         |             |                | Rev. 10-000269E<br>8/31/2016 |  |

| osc1 /       | $OSC1 \wedge \wedge$ |                                          |        |         |             |                |                              |  |

| CLKOUT \     | CLKOUT                                                                                                                                      |                                          |        |         |             |                |                              |  |

| INT<br>pin _ |                                                                                                                                             |                                          |        |         |             |                |                              |  |

| Fetch(       | PC - 1                                                                                                                                      | PC                                       | PC + 1 |         | PC = 0x0004 | PC = 0x0005    | PC = 0x0006                  |  |

| Execute(     | PC - 21                                                                                                                                     | PC - 1                                   | РС     | NOP     | NOP         | PC = 0x0004    | PC = 0x0005                  |  |

|              |                                                                                                                                             | Indeterminate<br>Laten cy <sup>(2)</sup> |        | Latency |             |                |                              |  |

|              |                                                                                                                                             | may occur at any t<br>errupt may occur a |        |         |             | ency can vary. |                              |  |

|                                         | Q1   Q2   Q3   Q4                                                                                                                                                                                    | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4     | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4 |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|-------------------|-------------------|--|--|

| OSC1                                    |                                                                                                                                                                                                      |                   |                       |                   |                   |  |  |

|                                         | (4)                                                                                                                                                                                                  |                   |                       | 1<br>1<br>1       |                   |  |  |

| INT pin                                 |                                                                                                                                                                                                      | , (1)             | 1<br>1                | i<br>1            | <u> </u>          |  |  |

| INTF                                    | , (1) (5)                                                                                                                                                                                            | 1                 | Interrupt Latency (2) |                   |                   |  |  |

| GIE                                     |                                                                                                                                                                                                      |                   |                       |                   |                   |  |  |

|                                         | — — — — — — -<br>N FLOW                                                                                                                                                                              |                   |                       |                   |                   |  |  |

| PC                                      | ( PC                                                                                                                                                                                                 | PC + 1            | PC + 1                | X 0004h           | X 0005h           |  |  |

| Instruction<br>Fetched                  | Inst (PC)                                                                                                                                                                                            | Inst (PC + 1)     | —                     | Inst (0004h)      | Inst (0005h)      |  |  |

| Instruction<br>Executed <sup>&lt;</sup> | Inst (PC – 1)                                                                                                                                                                                        | Inst (PC)         | Forced NOP            | Forced NOP        | Inst (0004h)      |  |  |

| Note 1:                                 | NTF flag is sampled here                                                                                                                                                                             | e (every Q1).     |                       |                   |                   |  |  |

|                                         | 2: Asynchronous interrupt latency = 3-5 Tcy. Synchronous latency = 3-4 Tcy, where Tcy = instruction cycle time.<br>Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction. |                   |                       |                   |                   |  |  |

| 3: F                                    | 3: For minimum width of INT pulse, refer to AC specifications in Section 37.0 "Electrical Specifications".                                                                                           |                   |                       |                   |                   |  |  |

4: INTF may be set any time during the Q4-Q1 cycles.

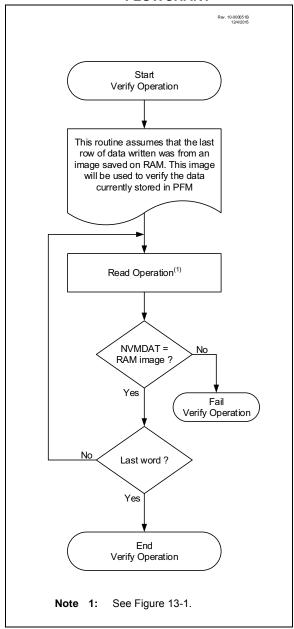

#### 13.3.7 WRITE VERIFY

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full row then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 13-7: FLASH PROGRAM MEMORY VERIFY FLOWCHART

#### 13.3.8 WRERR BIT

The WRERR bit can be used to determine if a write error occurred.

WRERR will be set if one of the following conditions occurs:

- If WR is set while the NVMADRH:NMVADRL points to a write-protected address

- A Reset occurs while a self-write operation was in progress

- An unlock sequence was interrupted

The WRERR bit is normally set by hardware, but can be set by the user for test purposes. Once set, WRERR must be cleared in software.

| Free | LWLO | Actions for PFM when WR = 1                                                                                          | Comments                                                                                                                                              |

|------|------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | x    | Erase the 32-word row of NVMADRH:NVMADRL<br>location. See Section 13.3.3 "NVMREG Erase<br>of PFM"                    | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>All 32 words are erased</li> <li>NVMDATH:NVMDATL is ignored</li> </ul>         |

| 0    | 1    | Copy NVMDATH:NVMDATL to the write latch<br>corresponding to NVMADR LSBs. See Section<br>13.3.3 "NVMREG Erase of PFM" | <ul><li>Write protection is ignored</li><li>No memory access occurs</li></ul>                                                                         |

| 0    | 0    | Write the write-latch data to PFM row. See Sec-<br>tion 13.3.3 "NVMREG Erase of PFM"                                 | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>Write latches are reset to 3FFh</li> <li>NVMDATH:NVMDATL is ignored</li> </ul> |

TABLE 13-4: ACTIONS FOR PFM WHEN WR = 1

| U-0   | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u     | R/W-0/u | R/W-0/u |

|-------|-----|-----|---------|---------|-------------|---------|---------|

| —     | —   | —   |         |         | RxyPPS<4:0> | •       |         |

| bit 7 |     |     |         |         |             |         | bit 0   |

|       |     |     |         |         |             |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 4-0 **RxyPPS<4:0>:** Pin Rxy Output Source Selection bits See Table 15-5 through Table 15-7.

Note 1: TRIS control is overridden by the peripheral as required.

#### REGISTER 15-3: PPSLOCK: PPS LOCK REGISTER

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-----------|--|--|

| —           | _   |     | —   | —   | —   | —   | PPSLOCKED |  |  |

| bit 7 bit 0 |     |     |     |     |     |     |           |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

1= PPS is locked. PPS selections can not be changed.

0= PPS is not locked. PPS selections can be changed.

© 2016 Microchip Technology Inc.

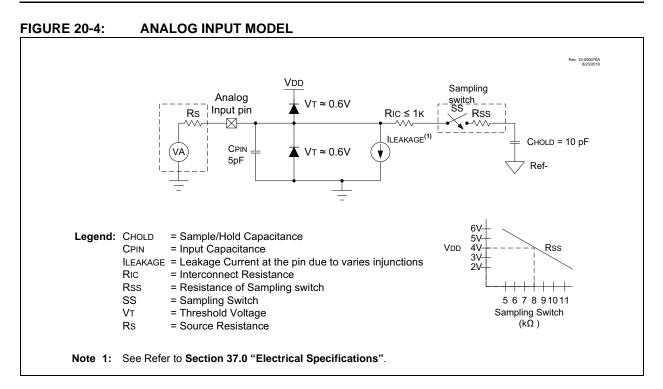

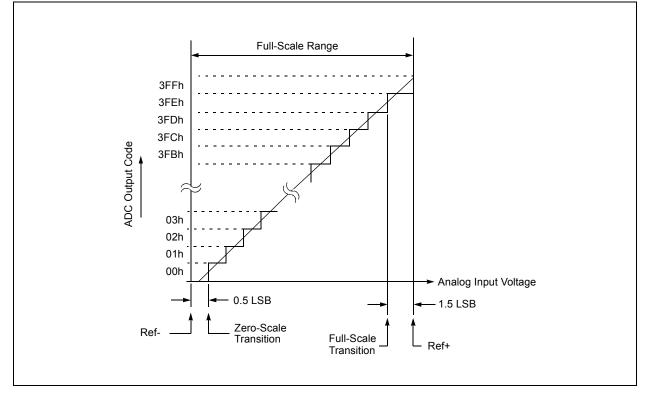

#### FIGURE 20-5: ADC TRANSFER FUNCTION

© 2016 Microchip Technology Inc.

DS40001866A-page 276

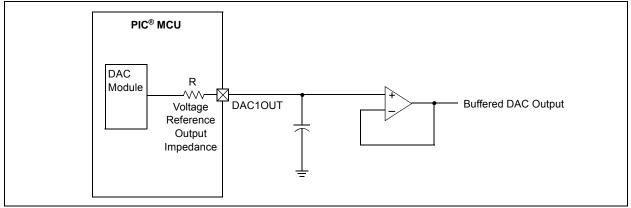

#### FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

© 2016 Microchip Technology Inc.

#### 26.6.2 TIMER GATE SOURCE SELECTION

One of the several different external or internal signal sources may be chosen to gate the timer and allow the timer to increment. The gate input signal source can be selected based on the T1GATE register setting. See the T1GATE register (Register 26-4) description for a complete list of the available gate sources. The polarity for each available source is also selectable. Polarity selection is controlled by the GPOL bit of the T1GCON register.

#### 26.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for the timer gate control. It can be used to supply an external source to the time gate circuitry.

#### 26.6.2.2 Timer0 Overflow Gate Operation

When Timer0 overflows, or a period register match condition occurs (in 8-bit mode), a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 26.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for the timer gate control. The Comparator 1 output can be synchronized to the timer clock or left asynchronous. For more information see Section 23.4.1 "Comparator Output Synchronization".

#### 26.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for the timer gate control. The Comparator 2 output can be synchronized to the timer clock or left asynchronous. For more information see Section 23.4.1 "Comparator Output Synchronization".

#### 26.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a timer gate signal, as opposed to the duration of a single level pulse.

The timer gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 26-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the GTM bit of the T1GCON register. When the GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

#### 26.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the GSPM bit in the T1GCON register. Next, the GGO/DONE bit in the T1GCON register must be set. The timer will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment the timer until the GGO/DONE bit is once again set in software. See Figure 26-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the GSPM bit in the T1GCON register, the GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the timer gate source to be measured. See Figure 26-6 for timing details.

#### 26.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the GVAL bit in the T1GCON register. The GVAL bit is valid even when the timer gate is not enabled (GE bit is cleared).

#### 26.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of GVAL occurs, the TMR1GIF flag bit in the PIR5 register will be set. If the TMR1GIE bit in the PIE5 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the timer gate is not enabled (TMR1GE bit is cleared).

#### 30.12 Configuring the CWG

The following steps illustrate how to properly configure the CWG.

- 1. Ensure that the TRIS control bits corresponding to the desired CWG pins for your application are set so that the pins are configured as inputs.

- 2. Clear the EN bit, if not already cleared.

- 3. Set desired mode of operation with the MODE bits.

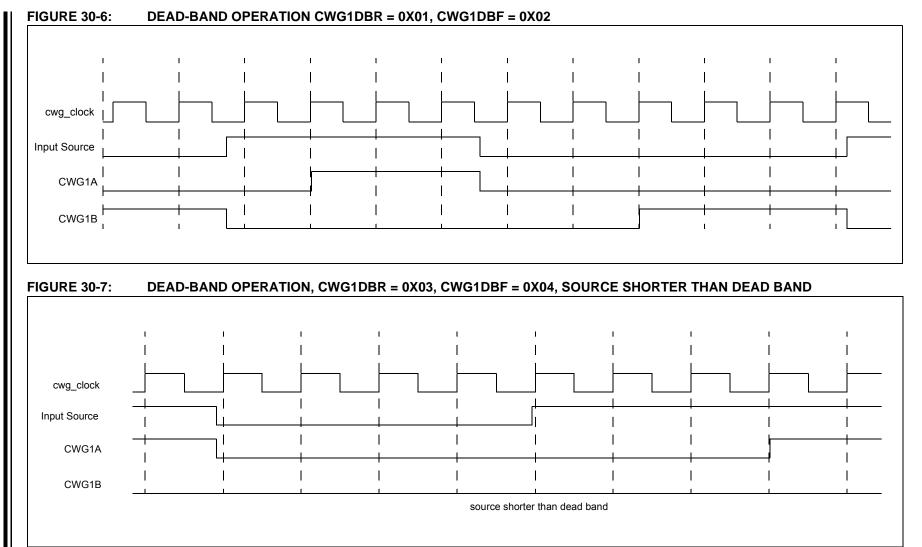

- Set desired dead-band times, if applicable to mode, with the CWG1DBR and CWG1DBF registers.

- 5. Setup the following controls in the CWG1AS0 and CWG1AS1 registers.

- a. Select the desired shutdown source.

- b. Select both output overrides to the desired levels (this is necessary even if not using autoshutdown because start-up will be from a shutdown state).

- c. Set which pins will be affected by auto-shutdown with the CWG1AS1 register.

- d. Set the SHUTDOWN bit and clear the REN bit.

- 6. Select the desired input source using the CWG1ISM register.

- 7. Configure the following controls.

- a. Select desired clock source using the CWG1CLKCON register.

- b. Select the desired output polarities using the CWG1CON1 register.

- c. Set the output enables for the desired outputs.

- 8. Set the EN bit.

- Clear TRIS control bits corresponding to the desired output pins to configure these pins as outputs.

- If auto-restart is to be used, set the REN bit and the SHUTDOWN bit will be cleared automatically. Otherwise, clear the SHUTDOWN bit to start the CWG.

#### 30.12.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the LSBD and LSAC bits of the CWG1AS0 register. LSBD<1:0> controls the CWG1B and D override levels and LSAC<1:0> controls the CWG1A and C override levels. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not affect the override level.

#### 30.12.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the REN bit of the CWG1CON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 30-13 and Figure 30-14.

#### 30.12.2.1 Software Controlled Restart

When the REN bit of the CWG1AS0 register is cleared, the CWG must be restarted after an auto-shutdown event by software. Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the SHUTDOWN bit will remain set. The overrides will remain in effect until the first rising edge event after the SHUTDOWN bit is cleared. The CWG will then resume operation.

#### 30.12.2.2 Auto-Restart

When the REN bit of the CWG1CON2 register is set, the CWG will restart from the auto-shutdown state automatically. The SHUTDOWN bit will clear automatically when all shutdown sources go low. The overrides will remain in effect until the first rising edge event after the SHUTDOWN bit is cleared. The CWG will then resume operation.

| R/W-0/0                 | R-1/1                                                                                                                         | U-0                              | R/W-0/0                           | R/W-0/0           | U-0              | R/W-0/0           | R/W-0/0     |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------|-------------------|------------------|-------------------|-------------|--|--|--|

| ABDOVF                  | RCIDL                                                                                                                         | —                                | SCKP                              | BRG16             | _                | WUE               | ABDEN       |  |  |  |

| bit 7                   |                                                                                                                               |                                  |                                   |                   |                  |                   | bit 0       |  |  |  |

|                         |                                                                                                                               |                                  |                                   |                   |                  |                   |             |  |  |  |

| Legend:<br>R = Readable | hit                                                                                                                           | W = Writable                     | hit                               | =   Inimpler      | nented bit, read | 1 26 '0'          |             |  |  |  |

| u = Bit is unch         |                                                                                                                               | x = Bit is unk                   |                                   | •                 |                  | R/Value at all o  | thar Pasats |  |  |  |

| (1) = Bit is unch       | angeu                                                                                                                         | $(0)^{2} = Bit is cle$           |                                   |                   |                  |                   |             |  |  |  |

|                         |                                                                                                                               |                                  | arcu                              |                   |                  |                   |             |  |  |  |

| bit 7                   | ABDOVF: Au                                                                                                                    | ito-Baud Dete                    | ct Overflow bit                   |                   |                  |                   |             |  |  |  |

|                         | Asynchronou                                                                                                                   | <u>s mode</u> :                  |                                   |                   |                  |                   |             |  |  |  |

|                         |                                                                                                                               | d timer overflo                  |                                   |                   |                  |                   |             |  |  |  |

|                         | 0 = Auto-bau<br>Synchronous                                                                                                   | d timer did not                  | overflow                          |                   |                  |                   |             |  |  |  |

|                         | Don't care                                                                                                                    | <u>mode</u> .                    |                                   |                   |                  |                   |             |  |  |  |

| bit 6                   | RCIDL: Rece                                                                                                                   | ive Idle Flag b                  | it                                |                   |                  |                   |             |  |  |  |

|                         | Asynchronou                                                                                                                   | •                                |                                   |                   |                  |                   |             |  |  |  |

|                         | 1 = Receiver                                                                                                                  |                                  |                                   |                   |                  |                   |             |  |  |  |

|                         | 0 = Start bit h                                                                                                               |                                  | ved and the re                    | ceiver is receiv  | ing              |                   |             |  |  |  |

|                         | Don't care                                                                                                                    | <u>moue</u> .                    |                                   |                   |                  |                   |             |  |  |  |

| bit 5                   | Unimplemen                                                                                                                    | ted: Read as                     | ʻ0'                               |                   |                  |                   |             |  |  |  |

| bit 4                   | SCKP: Clock/Transmit Polarity Select bit                                                                                      |                                  |                                   |                   |                  |                   |             |  |  |  |

|                         | Asynchronous mode:                                                                                                            |                                  |                                   |                   |                  |                   |             |  |  |  |

|                         | <ul> <li>1 = Idle state for transmit (TX) is a low level</li> <li>0 = Idle state for transmit (TX) is a high level</li> </ul> |                                  |                                   |                   |                  |                   |             |  |  |  |

|                         | <u>Synchronous mode</u> :<br>1 = Idle state for clock (CK) is a high level                                                    |                                  |                                   |                   |                  |                   |             |  |  |  |

|                         |                                                                                                                               | for clock (CK)<br>for clock (CK) | •                                 |                   |                  |                   |             |  |  |  |

| bit 3                   |                                                                                                                               | it Baud Rate (                   |                                   |                   |                  |                   |             |  |  |  |

| bit o                   |                                                                                                                               | ud Rate Gene                     |                                   |                   |                  |                   |             |  |  |  |

|                         |                                                                                                                               | id Rate Generation               |                                   |                   |                  |                   |             |  |  |  |

| bit 2                   | Unimplemen                                                                                                                    | ted: Read as                     | '0'                               |                   |                  |                   |             |  |  |  |

| bit 1                   | WUE: Wake-                                                                                                                    | up Enable bit                    |                                   |                   |                  |                   |             |  |  |  |

|                         | Asynchronous mode:                                                                                                            |                                  |                                   |                   |                  |                   |             |  |  |  |

|                         |                                                                                                                               |                                  |                                   | c pin – interrupt | generated on     | falling edge; bit | cleared in  |  |  |  |

|                         |                                                                                                                               | on following ri                  | sing eage.<br>or rising edge (    | detected          |                  |                   |             |  |  |  |

|                         | Synchronous                                                                                                                   |                                  | or noning ougo                    |                   |                  |                   |             |  |  |  |

|                         | Unused in thi                                                                                                                 | s mode – valu                    | e ignored                         |                   |                  |                   |             |  |  |  |

| bit 0                   | ABDEN: Auto-Baud Detect Enable bit                                                                                            |                                  |                                   |                   |                  |                   |             |  |  |  |

|                         | Asynchronou                                                                                                                   | <u>s mode</u> :                  |                                   |                   |                  |                   |             |  |  |  |

|                         | (55h);                                                                                                                        |                                  |                                   |                   | cter – requires  | reception of a    | SYNCH field |  |  |  |

|                         |                                                                                                                               |                                  | on completion<br>at disabled or o |                   |                  |                   |             |  |  |  |

|                         | Synchronous                                                                                                                   |                                  |                                   | Simpleted         |                  |                   |             |  |  |  |

|                         |                                                                                                                               | s mode – valu                    | e ianored                         |                   |                  |                   |             |  |  |  |

#### REGISTER 33-3: BAUDxCON: BAUD RATE CONTROL REGISTER

| U-0                                     | U-0                       | U-0                           | U-0  | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |

|-----------------------------------------|---------------------------|-------------------------------|------|----------------|------------------|------------------|--------------|--|--|

|                                         | _                         | _                             |      | CLKRCLK<3:0>   |                  |                  |              |  |  |

| bit 7                                   |                           |                               |      |                |                  |                  | bit (        |  |  |

| Legend:                                 |                           |                               |      |                |                  |                  |              |  |  |

| R = Readat                              | ole bit                   | W = Writable                  | oit  | U = Unimplen   | nented bit, read | d as '0'         |              |  |  |

| u = Bit is unchanged x = Bit is unknown |                           |                               |      | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |  |  |

| '1' = Bit is s                          | •                         | '0' = Bit is clea             | ared |                |                  |                  |              |  |  |

|                                         |                           |                               |      |                |                  |                  |              |  |  |

| bit 7-4                                 | Unimpleme                 | nted: Read as '               | )'   |                |                  |                  |              |  |  |

| bit 3-0                                 | CLKRCLK<                  | CLKRCLK<3:0>: CLKR Input bits |      |                |                  |                  |              |  |  |

|                                         |                           | Clock Selection               |      |                |                  |                  |              |  |  |

|                                         | 1111 = Rese               | erved                         |      |                |                  |                  |              |  |  |

|                                         | •                         |                               |      |                |                  |                  |              |  |  |

|                                         | •                         |                               |      |                |                  |                  |              |  |  |

|                                         | •                         |                               |      |                |                  |                  |              |  |  |

|                                         | 1011 <b>= Rese</b>        |                               |      |                |                  |                  |              |  |  |

|                                         | 1010 = LC4_               |                               |      |                |                  |                  |              |  |  |

|                                         | 1001 = LC3_               |                               |      |                |                  |                  |              |  |  |

|                                         | 1000 = LC2_<br>0111 = LC1 |                               |      |                |                  |                  |              |  |  |

|                                         | 0110 = NCC                |                               |      |                |                  |                  |              |  |  |

|                                         | 0101 = SOS                |                               |      |                |                  |                  |              |  |  |

|                                         |                           | NTOSC (31.25 k                | Hz)  |                |                  |                  |              |  |  |

|                                         |                           | NTOSC (500 kH                 |      |                |                  |                  |              |  |  |

|                                         | 0010 = LFIN               |                               | ,    |                |                  |                  |              |  |  |

|                                         | 0001 = HFIN               | ITOSC                         |      |                |                  |                  |              |  |  |

|                                         | 0000 <b>=</b> Foso        | 2                             |      |                |                  |                  |              |  |  |

| TABLE 34-1: | SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK REFERENCE OUTPUT |

|-------------|-------------------------------------------------------------|

|-------------|-------------------------------------------------------------|

| Name     | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit 6 | Bit 5 | Bit 4       | Bit 3                    | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------------|--------------------------|-------|-------|-------|---------------------|

| CLKRCON  | CLKREN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _     | _     | CLKRD       | CLKRDC<1:0> CLKRDIV<2:0> |       |       |       |                     |

| CLKRCLK  | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —     | _     | —           |                          |       | 502   |       |                     |

| CLCxSELy | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —     |       | LCxDyS<5:0> |                          |       |       |       |                     |

| RxyPPS   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _     | _     | RxyPPS<4:0> |                          |       |       |       | 242                 |

|          | Leavenuel and a second se |       |       |             |                          |       |       |       |                     |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the CLKR module.

#### TABLE 37-17: ZERO CROSS DETECT (ZCD) SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |          |                                |      |      |      |       |          |  |  |

|----------------------------------------------------------------------------------|----------|--------------------------------|------|------|------|-------|----------|--|--|

| Param.<br>No.                                                                    | Sym.     | Characteristics                | Min. | Тур† | Max. | Units | Comments |  |  |

| ZC01                                                                             | VPINZC   | Voltage on Zero Cross Pin      | —    | 0.75 | —    | V     |          |  |  |

| ZC02                                                                             | IZCD_MAX | Maximum source or sink current | —    | _    | 600  | μΑ)   |          |  |  |

| ZC03                                                                             | TRESPH   | Response Time, Rising Edge     | —    | 1    |      | /us   |          |  |  |

|                                                                                  | TRESPL   | Response Time, Falling Edge    | _    | 1    | _    | μs    |          |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

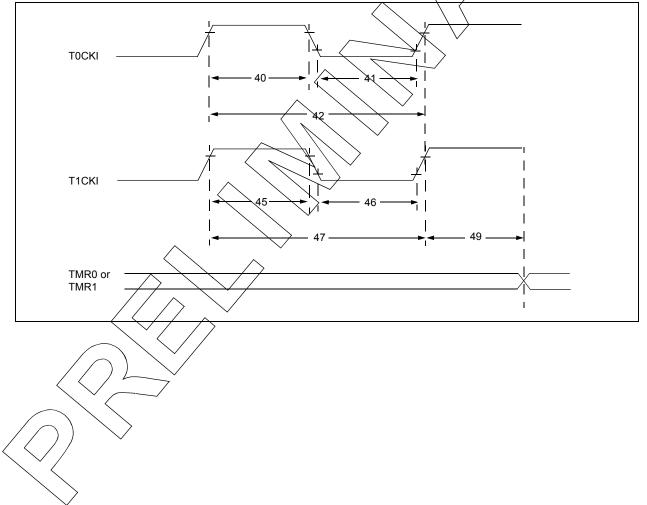

#### FIGURE 37-12: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

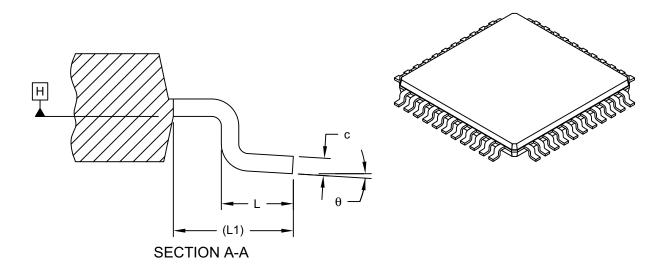

#### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Ν            | <b>IILLIMETER</b> | S         |      |  |

|--------------------------|--------------|-------------------|-----------|------|--|

| Dimension                | MIN          | NOM               | MAX       |      |  |

| Number of Leads          | N            |                   | 44        |      |  |

| Lead Pitch               | е            |                   | 0.80 BSC  |      |  |

| Overall Height           | Α            | -                 | -         | 1.20 |  |

| Standoff                 | A1           | 0.05              | -         | 0.15 |  |

| Molded Package Thickness | A2           | 0.95 1.00 1.0     |           |      |  |

| Overall Width            | E            | 12.00 BSC         |           |      |  |

| Molded Package Width     | E1           |                   | 10.00 BSC |      |  |

| Overall Length           | D            |                   | 12.00 BSC |      |  |

| Molded Package Length    | D1           |                   | 10.00 BSC |      |  |

| Lead Width               | b            | 0.30              | 0.37      | 0.45 |  |

| Lead Thickness           | С            | 0.09              | -         | 0.20 |  |

| Lead Length              | L            | 0.45 0.60 0.75    |           |      |  |

| Footprint                | Footprint L1 |                   |           |      |  |

| Foot Angle               | θ            | 0°                | 3.5°      | 7°   |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2

### APPENDIX A: DATA SHEET REVISION HISTORY

#### Revision A (12/2016)

Initial release of the document.