Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15376t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| PIC16(   |

|----------|

| L)F1535  |

| 56/75/76 |

| 6/85/86  |

#### 40/44-PIN ALLOCATION TABLE (PIC16(L)F15375, PIC16(L)F15376) (CONTINUED) TABLE 4:

|                    |             |             |            |             |      |           |            |     | ( ) |                     |     | ,   | <i>,</i> , | -                              |     |                           |     |      |           |         |             |

|--------------------|-------------|-------------|------------|-------------|------|-----------|------------|-----|-----|---------------------|-----|-----|------------|--------------------------------|-----|---------------------------|-----|------|-----------|---------|-------------|

| I/O <sup>(2)</sup> | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC  | Reference | Comparator | NCO | DAC | Timers              | ССР | MWA | CWG        | ASSM                           | ZCD | EUSART                    | CLC | CLKR | Interrupt | Bull-up | Basic       |

| RC3                | 18          | 33          | 37         | 37          | ANC3 | —         | —          | _   | -   | T2IN <sup>(1)</sup> |     | _   | -          | SCL1<br>SCK1 <sup>(1,4)</sup>  | _   | -                         | _   | —    | IOCC3     | Y       |             |

| RC4                | 23          | 38          | 42         | 42          | ANC4 | —         | —          | _   | _   | —                   | _   | _   | —          | SDA1<br>SDI1 <sup>(1,4)</sup>  | —   | -                         | _   | _    | IOCC4     | Y       | _           |

| RC5                | 24          | 39          | 43         | 43          | ANC5 | _         | _          | _   | _   | _                   | _   | _   | _          | _                              | _   | _                         | _   | _    | IOCC5     | Υ       | —           |

| RC6                | 25          | 40          | 44         | 44          | ANC6 | —         | —          | _   | -   | _                   | _   | _   | —          | —                              | _   | TX1<br>CK1 <sup>(1)</sup> | _   | _    | IOCC6     | Y       | _           |

| RC7                | 26          | 1           | 1          | 1           | ANC7 | —         | —          |     |     | _                   |     | _   | —          | —                              | _   | RX1<br>DT1 <sup>(1)</sup> | —   | —    | IOCC7     | Y       |             |

| RD0                | 19          | 34          | 38         | 38          | AND0 | —         | —          | _   | -   | —                   |     | —   | —          | SCK2,<br>SCL2 <sup>(1,4)</sup> | —   | -                         | —   | —    | —         | -       | —           |

| RD1                | 20          | 35          | 39         | 39          | AND1 | _         | —          | _   | -   | _                   | _   | _   | _          | SDA2,<br>SDI2 <sup>(1,4)</sup> | _   | -                         | _   | _    | —         | -       |             |

| RD2                | 21          | 36          | 40         | 40          | AND2 | _         | _          | _   | _   | _                   | _   | _   | _          | _                              | _   |                           | —   | _    | _         | —       | —           |

| RD3                | 22          | 37          | 41         | 41          | AND3 | _         | —          | _   | _   | _                   | _   | —   | _          | _                              | _   | _                         | _   | _    | _         | —       | - 1         |

| RD4                | 27          | 2           | 2          | 2           | AND4 | -         | —          | -   |     | _                   |     | —   | —          | _                              | —   | —                         | —   | -    | _         | _       | —           |

| RD5                | 28          | 3           | 3          | 3           | AND5 | _         | —          |     |     | —                   |     | —   | —          | —                              | —   | —                         | —   | _    | —         | -       | —           |

| RD6                | 29          | 4           | 4          | 4           | AND6 | _         | —          |     |     | —                   |     | —   | —          | _                              | —   | —                         | —   | _    | —         | _       | —           |

| RD7                | 30          | 5           | 5          | 5           | AND7 | -         | —          |     |     | —                   |     | —   | _          | —                              | —   | —                         | _   | _    | —         | —       | —           |

| RE0                | 8           | 23          | 25         | 25          | ANE0 | _         | —          | _   | _   | _                   | _   | —   | —          | _                              | —   | —                         | _   | _    | —         | —       |             |

| RE1                | 9           | 24          | 26         | 26          | ANE1 | _         | —          | _   | —   | _                   | _   | —   | —          | _                              | —   | _                         | _   | _    | —         | —       | —           |

| RE2                | 10          | 25          | 27         | 27          | ANE2 | —         | —          | _   | —   | —                   | _   | —   | —          | —                              | —   | —                         | —   | —    | —         | —       | —           |

| RE3                | 1           | 16          | 18         | 18          | —    | -         | —          | —   | —   | —                   | —   | —   | —          | —                              | —   | _                         | —   | —    | IOCE3     | Y       | MCLR<br>VPP |

| VDD                | 11          | 26          | 7          | 7           | _    |           | —          | _   | -   | _                   | -   | —   | _          | _                              | _   | —                         | _   |      | _         | —       | Vdd         |

| VDD                | 32          | 7           | 28         | 28          | —    | -         | —          | _   | -   | —                   | _   | —   | —          | —                              | _   | —                         | —   | _    | —         | -       | Vdd         |

| Vss                | 12          | 27          | 6          | 6           | _    | —         | —          | _   | _   | _                   | _   | _   | _          | _                              | —   | _                         | _   | _    | _         | —       | Vss         |

| Vss                | 31          | 6           | 30         | 29          | —    | _         | —          | —   | —   | -                   | —   | —   | —          | —                              | —   | —                         | —   | _    | —         | -       | Vss         |

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. 1: Note

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or 4: SMBUS input buffer thresholds.

| Name             | Function              | Input<br>Type | Output Type | Description                                        |

|------------------|-----------------------|---------------|-------------|----------------------------------------------------|

| T <sup>(2)</sup> | C1OUT                 | _             | CMOS/OD     | Comparator 1 output.                               |

|                  | C2OUT                 | _             | CMOS/OD     | Comparator 2 output.                               |

|                  | NCO10UT               | _             | CMOS/OD     | Numerically Controller Oscillator output.          |

|                  | TMR0                  | _             | CMOS/OD     | Timer0 output.                                     |

|                  | CCP1                  | _             | CMOS/OD     | Capture/Compare/PWM1 output (compare/PWM functions |

|                  | CCP2                  | _             | CMOS/OD     | Capture/Compare/PWM2 output (compare/PWM functions |

|                  | PWM3OUT               |               | CMOS/OD     | PWM3 output.                                       |

|                  | PWM4OUT               | _             | CMOS/OD     | PWM4 output.                                       |

|                  | PWM5OUT               | _             | CMOS/OD     | PWM5 output.                                       |

|                  | CWG1A                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output A.       |

|                  | CWG1B                 |               | CMOS/OD     | Complementary Waveform Generator 1 output B.       |

|                  | CWG1C                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output C.       |

|                  | CWG1D                 |               | CMOS/OD     | Complementary Waveform Generator 1 output D.       |

|                  | CWG2A                 |               | CMOS/OD     | Complementary Waveform Generator 2 output A.       |

|                  | CWG2B                 |               | CMOS/OD     | Complementary Waveform Generator 2 output B.       |

|                  | CWG2C                 |               | CMOS/OD     | Complementary Waveform Generator 2 output C.       |

|                  | CWG2D                 |               | CMOS/OD     | Complementary Waveform Generator 2 output D.       |

|                  | SDO1                  | -             | CMOS/OD     | MSSP1 SPI serial data output.                      |

|                  | SDO2                  | _             | CMOS/OD     | MSSP2 SPI serial data output.                      |

|                  | SCL1 <sup>(3,4)</sup> |               | CMOS/OD     | MSSP1 SPI serial clock output.                     |

|                  | SCL2 <sup>(3,4)</sup> | _             | CMOS/OD     | MSSP2 SPI serial clock output.                     |

|                  | SDA1 <sup>(3,4)</sup> | _             | CMOS/OD     | MSSP1 I <sup>2</sup> C serial data input/output.   |

|                  | SDA2 <sup>(3,4)</sup> |               | CMOS/OD     | MSSP2 I <sup>2</sup> C serial data input/output.   |

|                  | DT <sup>(3)</sup>     |               | CMOS/OD     | EUSART Synchronous mode data output.               |

|                  | CK1                   | _             | CMOS/OD     | EUSART1 Synchronous mode clock output.             |

|                  | CK2                   |               | CMOS/OD     | EUSART2 Synchronous mode clock output.             |

|                  | TX1                   | _             | CMOS/OD     | EUSART1 Asynchronous mode transmitter data output. |

|                  | TX2                   |               | CMOS/OD     | EUSART2 Asynchronous mode transmitter data output. |

|                  | CLC1OUT               | _             | CMOS/OD     | Configurable Logic Cell 1 output.                  |

|                  | CLC2OUT               |               | CMOS/OD     | Configurable Logic Cell 2 output.                  |

|                  | CLC3OUT               | _             | CMOS/OD     | Configurable Logic Cell 3 output.                  |

|                  | CLC4OUT               | _             | CMOS/OD     | Configurable Logic Cell 4 output.                  |

|                  | CLKR                  |               | CMOS/OD     | Clock Reference module output.                     |

#### **TABLE 1-3**: PIC16(L)F15375/76 PINOUT DESCRIPTION (CONTINUED)

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels

HV = High Voltage

Note

= Crystal levels XTAL This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options

as described in Table 15-5, Table 15-6 and Table 15-6.

I<sup>2</sup>C

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

= Schmitt Trigger input with I<sup>2</sup>C

#### TABLE 4-2: MEMORY ACCESS PARTITION

|         |                                                                                                     |                                     | Part                  | tition                       |                                     |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|------------------------------|-------------------------------------|--|--|--|

| REG     | Address                                                                                             | <u>BBEN</u> = 1<br>SAFEN = 1        | BBEN = 1<br>SAFEN = 0 | <u>BBEN</u> = 0<br>SAFEN = 1 | <u>BBEN</u> = 0<br>SAFEN = 0        |  |  |  |

|         | 00 0000h<br>•••<br>Last Boot Block Memory<br>Address                                                |                                     | APPLICATION           | BOOT BLOCK <sup>(4)</sup>    | BOOT BLOCK <sup>(4)</sup>           |  |  |  |

| PFM     | Last Boot Block Memory<br>Address + 1 <sup>(1)</sup><br>•••<br>Last Program Memory<br>Address - 80h | APPLICATION<br>BLOCK <sup>(4)</sup> | BLOCK <sup>(4)</sup>  | APPLICATION                  | APPLICATION<br>BLOCK <sup>(4)</sup> |  |  |  |

|         | Last Program Memory<br>Address - 7Fh <sup>(2)</sup><br>•••<br>Last Program Memory<br>Address        |                                     | SAF <sup>(4)</sup>    | BLOCK <sup>(4)</sup>         | SAF <sup>(4)</sup>                  |  |  |  |

| CONF IG |                                                                                                     |                                     |                       |                              |                                     |  |  |  |

Note 1: Last Boot Block Memory Address is based on BBSIZE<2:0> given in Table 5-1.

2: Last Program Memory Address is the Flash size given in Table 4-1.

3: Config Memory Address are the address locations of the Configuration Words given in Table 13-2.

**4:** Each memory block has a corresponding write protection fuse defined by the WRTAPP, WRTB and WRTC bits in the Configuration Word (Register 5-4).

| Address | Name                | Bit 7              | Bit 6                                   | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |

|---------|---------------------|--------------------|-----------------------------------------|---------|---------------|-------------------|-----------|-------|-------|-----------------------|----------------------------|--|--|

| Bank 2  |                     |                    |                                         |         | •             | •                 |           |       | •     |                       |                            |  |  |

|         |                     |                    |                                         | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics |       |       |                       |                            |  |  |

|         |                     |                    |                                         |         |               |                   |           |       |       |                       |                            |  |  |

| 10Ch    | OCh _ Unimplemented |                    |                                         |         |               |                   |           |       |       |                       |                            |  |  |

| 118h    |                     |                    | en importante                           |         |               |                   |           |       |       |                       |                            |  |  |

| 119h    | RC1REG              | EUSART Receive Dat | a Register                              |         |               |                   |           |       |       | 0000 0000             | 0000 0000                  |  |  |

| 11Ah    | TX1REG              | EUSART Transmit Da | ta Register                             |         |               |                   |           |       |       | 0000 0000             | 0000 0000                  |  |  |

| 11Bh    | SP1BRGL             |                    |                                         |         | SP1BR0        | G<7:0>            |           |       |       | 0000 0000             | 0000 0000                  |  |  |

| 11Ch    | SP1BRGH             |                    |                                         |         | SP1BRG        | 6<15:8>           |           |       |       | 0000 0000             | 0000 0000                  |  |  |

| 11Dh    | RC1STA              | SPEN               | SPEN RX9 SREN CREN ADDEN FERR OERR RX9D |         |               |                   |           |       |       |                       | 0000 0000                  |  |  |

| 11Eh    | TX1STA              | CSRC               | TX9                                     | TXEN    | SYNC          | SENDB             | BRGH      | TRMT  | TX9D  | 0000 0010             | 0000 0010                  |  |  |

| 11Fh    | BAUD1CON            | ABDOVF             | RCIDL                                   | _       | SCKP          | BRG16             | —         | WUE   | ABDEN | 01-0 0-00             | 01-0 0-00                  |  |  |

#### CISTED SUMMADY DANKS A 62 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address            | Name                   | Bit 7   | Bit 6                                                                    | Bit 5   | Bit 4   | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |  |

|--------------------|------------------------|---------|--------------------------------------------------------------------------|---------|---------|---------|------------------------|------------------------|------------------------|-----------------------|----------------------------|--|--|--|

| Bank 62 (Co        | ontinued)              | •       | •                                                                        |         | •       | •       | -                      | •                      |                        | •                     |                            |  |  |  |

| 1F4Eh              | ANSELC                 | ANSC7   | ANSC6                                                                    | ANSC5   | ANSC4   | ANSC3   | ANSC2                  | ANSC1                  | ANSC0                  | 1111 1111             | 1111 1111                  |  |  |  |

| 1F4Fh              | WPUC                   | WPUC7   | WPUC6                                                                    | WPUC5   | WPUC4   | WPUC3   | WPUC2                  | WPUC1                  | WPUC0                  | 0000 0000             | 0000 0000                  |  |  |  |

| 1F50h              | ODCONC                 | ODCC7   | ODCC6                                                                    | ODCC5   | ODCC4   | ODCC3   | ODCC2                  | ODCC1                  | ODCC0                  | 0000 0000             | 0000 0000                  |  |  |  |

| 1F51h              | SLRCONC                | SLRC7   | SLRC6                                                                    | SLRC5   | SLRC4   | SLRC3   | SLRC2                  | SLRC1                  | SLRC0                  | 1111 1111             | 1111 1111                  |  |  |  |

| 1F52h              | INLVLC                 | INLVLC7 | INLVLC6                                                                  | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2                | INLVLC1                | INLVLC0                | 1111 1111             | 1111 1111                  |  |  |  |

| 1F53h              | IOCCP                  | IOCCP7  | IOCCP6                                                                   | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2                 | IOCCP1                 | IOCCP0                 | 0000 0000             | 0000 0000                  |  |  |  |

| 1F54h              | IOCCN                  | IOCCN7  | IOCCN6                                                                   | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2                 | IOCCN1                 | IOCCN0                 | 0000 0000             | 0000 0000                  |  |  |  |

| 1F55h              | IOCCF                  | IOCCF7  | IOCCF6                                                                   | IOCCF5  | IOCCF4  | IOCCF3  | IOCCF2                 | IOCCF1                 | IOCCF0                 | 0000 0000             | 0000 0000                  |  |  |  |

| 1F56h<br><br>1F58h | _                      |         | _                                                                        | _       |         |         |                        |                        |                        |                       |                            |  |  |  |

| 1F59h              | ANSELD <sup>(1)</sup>  | ANSD7   | ANSD6                                                                    | ANSD5   | ANSD4   | ANSD3   | ANSD2                  | ANSD1                  | ANSD0                  | 1111 1111             | 1111 1111                  |  |  |  |

| 1F5Ah              | WPUD <sup>(1)</sup>    | WPUD7   | WPUD6                                                                    | WPUD5   | WPUD4   | WPUD3   | WPUD2                  | WPUD1                  | WPUD0                  | 0000 0000             | 0000 0000                  |  |  |  |

| 1F5Bh              | ODCOND <sup>(1)</sup>  | ODCD7   | ODCD6                                                                    | ODCD5   | ODCD4   | ODCD3   | ODCD2                  | ODCD1                  | ODCD0                  | 0000 0000             | 0000 0000                  |  |  |  |

| 1F5Ch              | SLRCOND <sup>(1)</sup> | SLRD7   | SLRD6                                                                    | SLRD5   | SLRD4   | SLRD3   | SLRD2                  | SLRD1                  | SLRD0                  | 1111 1111             | 1111 1111                  |  |  |  |

| 1F5Dh              | INLVLD <sup>(1)</sup>  | INLVLD7 | INLVLD6                                                                  | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2                | INLVLD1                | INLVLD0                | 1111 1111             | 1111 1111                  |  |  |  |

| 1F5Eh<br><br>1F63h | _                      |         |                                                                          |         | Unimple | mented  |                        |                        |                        | -                     | _                          |  |  |  |

| 1F64h              | ANSELE <sup>(1)</sup>  | _       | _                                                                        | _       | _       | _       | ANSE2                  | ANSE1                  | ANSE0                  | 111                   | uuu                        |  |  |  |

| 1F65h              | WPUE                   | _       | _                                                                        | _       | _       | WPUE3   | WPUE2 <sup>(1)</sup>   | WPUE1 <sup>(1)</sup>   | WPUE0 <sup>(1)</sup>   | 0000                  | uuuu                       |  |  |  |

| 1F66h              | ODCONE <sup>(1)</sup>  | _       | _                                                                        | _       | _       | _       | ODCE2                  | ODCE1                  | ODCE0                  | 000                   | 000                        |  |  |  |

| 1F67h              | SLRCONE <sup>(1)</sup> | _       | _                                                                        | _       | _       | _       | SLRE2                  | SLRE1                  | SLRE0                  | 111                   | 111                        |  |  |  |

| 1F68h              | INLVLE                 | _       | _                                                                        | _       | _       | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> | 1111                  | uuuu                       |  |  |  |

| 1F69h              | IOCEP                  | _       | _                                                                        | _       | _       | IOCEP3  | IOCEP2 <sup>(1)</sup>  | IOCEP1 <sup>(1)</sup>  | IOCEP0 <sup>(1)</sup>  | 0000                  | 0000                       |  |  |  |

| 1F6Ah              | IOCEN                  | —       | _                                                                        | _       | _       | IOCEN3  | IOCEN2 <sup>(1)</sup>  | IOCEN1 <sup>(1)</sup>  | IOCEN0 <sup>(1)</sup>  | 0000                  | 0000                       |  |  |  |

| 1F6Bh              | IOCEF                  | _       | _                                                                        | _       | _       | IOCEF3  | IOCEF2 <sup>(1)</sup>  | IOCEF1 <sup>(1)</sup>  | IOCEF0 <sup>(1)</sup>  | 0000                  | 0000                       |  |  |  |

| 1F6Ch<br><br>1F6Fh | _                      |         | IOCEF3 IOCEF2 <sup>(1)</sup> IOCEF1 <sup>(1)</sup> IOCEF0 <sup>(1)</sup> |         |         |         |                        |                        |                        |                       |                            |  |  |  |

#### SPECIAL EUNCTION DECISTED SUMMARY PANKS 0.62 (CONTINUED) TABLE A 44.

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Present only on PIC16(L)F15375/76/85/86.

| Address | Name        | Bit 7                 | Bit 6                   | Bit 5           | Bit 4           | Bit 3             | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|-------------|-----------------------|-------------------------|-----------------|-----------------|-------------------|-----------|-------|-------|-----------------------|----------------------------|

| Bank 63 |             | -                     |                         |                 |                 |                   |           |       |       |                       |                            |

|         |             |                       |                         | CPU CO          | RE REGISTERS;   | see Table 4-3 for | specifics |       |       |                       |                            |

|         |             |                       |                         |                 |                 |                   | ·         |       |       |                       |                            |

| 1F8Ch   | _           |                       |                         |                 | Unimple         | mented            |           |       |       | _                     | _                          |

| 1FE3h   |             |                       |                         |                 |                 |                   |           |       |       |                       |                            |

| 1FE4h   | STATUS_SHAD | —                     | —                       | —               | _               | _                 | Z         | DC    | С     | xxx                   | uui                        |

| 1FE5h   | WREG_SHAD   | Working Register Sha  | Working Register Shadow |                 |                 |                   |           |       |       |                       | uuuu uuu                   |

| 1FE6h   | BSR_SHAD    | _                     | _                       | —               | Bank Select Reg | gister Shadow     |           |       |       | x xxxx                | u uuu                      |

| 1FE7h   | PCLATH_SHAD | _                     | Program Counter         | Latch High Regi | ster Shadow     |                   |           |       |       | -xxx xxxx             | uuuu uuu                   |

| 1FE8h   | FSR0L_SHAD  | Indirect Data Memory  | Address 0 Low Po        | inter Shadow    |                 |                   |           |       |       | XXXX XXXX             | uuuu uuu                   |

| 1FE9h   | FSR0H_SHAD  | Indirect Data Memory  | Address 0 High Po       | pinter Shadow   |                 |                   |           |       |       | xxxx xxxx             | uuuu uuu                   |

| 1FEAh   | FSR1L_SHAD  | Indirect Data Memory  | Address 1 Low Po        | inter Shadow    |                 |                   |           |       |       | XXXX XXXX             | uuuu uuu                   |

| 1FEBh   | FSR1H_SHAD  | Indirect Data Memory  | Address 1 High Po       | binter Shadow   |                 |                   |           |       |       | XXXX XXXX             | นนนน นนนเ                  |

| 1FECh   | _           | Unimplemented         |                         |                 |                 |                   |           |       |       | —                     | _                          |

| 1FEDh   | STKPTR      | _                     | —                       | —               | Current Stack P | ointer            |           |       |       | 1 1111                | 1 111                      |

| 1FEEh   | TOSL        | Top of Stack Low byte |                         |                 | •               |                   |           |       |       | xxxx xxxx             | uuuu uuu                   |

| 1FEFh   | TOSH        | _                     | Top of Stack High       | byte            |                 |                   |           |       |       | -xxx xxxx             | -uuu uuu                   |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

### 9.5 Register Definitions: Oscillator Control

#### REGISTER 9-1: OSCCON1: OSCILLATOR CONTROL REGISTER1

| U-0   | R/W-f/f <sup>(1)</sup> | R/W-f/f <sup>(1)</sup>    | R/W-f/f <sup>(1)</sup> | R/W-q/q                      | R/W-q/q | R/W-q/q | R/W-q/q |  |  |

|-------|------------------------|---------------------------|------------------------|------------------------------|---------|---------|---------|--|--|

| _     | 1                      | NOSC<2:0> <sup>(2,3</sup> | 3)                     | NDIV<3:0> <sup>(2,3,4)</sup> |         |         |         |  |  |

| bit 7 |                        |                           |                        |                              |         |         | bit 0   |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | f = determined by fuse setting                        |

| bit 7   | Unimplemented: Read as '0'                                                  |

|---------|-----------------------------------------------------------------------------|

| bit 6-4 | NOSC<2:0>: New Oscillator Source Request bits                               |

|         | The setting requests a source oscillator and PLL combination per Table 9-1. |

|         | POR value = RSTOSC (Register 5-1).                                          |

| bit 3-0 | NDIV<3:0>: New Divider Selection Request bits                               |

|         | The setting determines the new postscaler division ratio per Table 9-1.     |

Note 1: The default value (f/f) is set equal to the RSTOSC Configuration bits.

- 2: If NOSC is written with a reserved value (Table 9-1), the operation is ignored and neither NOSC nor NDIV is written.

- 3: When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

- 4: When NOSC = 110 (HFINTOSC 4 MHz), the NDIV bits will default to '0010' upon Reset; for all other NOSC settings the NDIV bits will default to '0000' upon Reset.

#### REGISTER 9-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0   | R-n/n <sup>(2)</sup> |

|-------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| —     |                      | COSC<2:0>            |                      |                      | CDIV                 | <3:0>                |                      |

| bit 7 |                      |                      |                      |                      |                      |                      | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | <b>Unimplemented:</b> Read as '0' |

|-------|-----------------------------------|

|       |                                   |

- bit 6-4 **COSC<2:0>:** Current Oscillator Source Select bits (read-only)

- Indicates the current source oscillator and PLL combination per Table 9-1.

- bit 3-0 **CDIV<3:0>:** Current Divider Select bits (read-only) Indicates the current postscaler division ratio per Table 9-1.

**Note 1:** The POR value is the value present when user code execution begins.

**2:** The Reset value (n/n) is the same as the NOSC/NDIV bits.

# PIC16(L)F15356/75/76/85/86

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|---------|--------|--------|--------|--------|-----------|-----------------------|-----------------------|-----------------------|---------------------|

| INTCON  | GIE    | PEIE   | _      | _      | _         | —                     | _                     | INTEDG                | 146                 |

| PIE0    | —      |        | TMR0IE | IOCIE  | —         | _                     |                       | INTE                  | 147                 |

| PIE1    | OSFIE  | CSWIE  | _      |        | —         | —                     | _                     | ADIE                  | 148                 |

| PIE2    | _      | ZCDIE  | _      | _      | _         | _                     | C2IE                  | C1IE                  | 149                 |

| PIE3    | RC2IE  | TX2IE  | RC1IE  | TX1IE  | BCL2IE    | SSP2IE                | BCL1IE                | SSP1IE                | 150                 |

| PIE4    | —      | _      | _      | —      | —         | —                     | TMR2IE                | TMR1IE                | 151                 |

| PIR0    | —      | _      | TMR0IF | IOCIF  | —         | —                     |                       | INTF                  | 155                 |

| PIR1    | OSFIF  | CSWIF  | _      |        | _         | _                     | _                     | ADIF                  | 156                 |

| PIR2    | —      | ZCDIF  |        | _      | —         | —                     | C2IF                  | C1IF                  | 157                 |

| PIR3    | RC2IF  | TX2IF  | RC1IF  | TX1IF  | BCL2IF    | SSP2IF                | BCL1IF                | SSP1IF                | 158                 |

| PIR4    | _      |        | _      | _      | —         | _                     | TMR2IF                | TMR1IF                | 159                 |

| IOCAP   | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3    | IOCAP2                | IOCAP1                | IOCAP0                | 255                 |

| IOCAN   | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3    | IOCAN2                | IOCAN1                | IOCAN0                | 255                 |

| IOCAF   | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3    | IOCAF2                | IOCAF1                | IOCAF0                | 256                 |

| IOCBP   | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3    | IOCBP2                | IOCBP1                | IOCBP0                | 257                 |

| IOCBN   | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3    | IOCBN2                | IOCBN1                | IOCBN0                | 257                 |

| IOCBF   | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3    | IOCBF2                | IOCBF1                | IOCBF0                | 258                 |

| IOCCP   | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3    | IOCCP2                | IOCCP1                | IOCCP0                | 259                 |

| IOCCN   | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3    | IOCCN2                | IOCCN1                | IOCCN0                | 259                 |

| IOCCF   | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3    | IOCCF2                | IOCCF1                | IOCCF0                | 259                 |

| IOCEP   | —      |        |        | _      | IOCEP3    | IOCEP2 <sup>(1)</sup> | IOCEP1 <sup>(1)</sup> | IOCEP0 <sup>(1)</sup> | 260                 |

| IOCEN   | —      | _      | _      | —      | IOCEN3    | IOCEN2 <sup>(1)</sup> | IOCEN1 <sup>(1)</sup> | IOCEN0 <sup>(1)</sup> | 260                 |

| IOCEF   | —      |        |        | _      | IOCEF3    | IOCEF2 <sup>(1)</sup> | IOCEF1 <sup>(1)</sup> | IOCEF0 <sup>(1)</sup> | 261                 |

| STATUS  | _      | _      | _      | TO     | PD        | Z                     | DC                    | С                     | 54                  |

| VREGCON | _      | _      | _      | _      | _         | —                     | VREGPM                | _                     | 168                 |

| CPUDOZE | IDLEN  | DOZEN  | ROI    | DOE    | _         |                       | DOZE<2:0>             |                       | 169                 |

| WDTCON0 | —      | —      |        | ١      | NDTPS<4:0 | >                     |                       | SWDTEN                | 175                 |

### TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

**Note 1:** Present only in PIC16(L)F15375/76/85/86.

#### REGISTER 12-3: WDTPSL: WDT PRESCALE SELECT LOW BYTE REGISTER

| D 0/0               | D 0/0 | D 0/0                |                   |                   | D 0/0              | D 0/0             | D 0/0  |

|---------------------|-------|----------------------|-------------------|-------------------|--------------------|-------------------|--------|

| R-0/0               | R-0/0 | R-0/0                | R-0/0             | R-0/0             | R-0/0              | R-0/0             | R-0/0  |

|                     |       |                      | PSCN <sup>®</sup> | T<7:0> <b>(1)</b> |                    |                   |        |

| bit 7               |       |                      |                   |                   |                    |                   | bit C  |

|                     |       |                      |                   |                   |                    |                   |        |

| Legend:             |       |                      |                   |                   |                    |                   |        |

| R = Readable bit    |       | W = Writable bit     |                   | U = Unimpleme     | ented bit, read as | ·'O'              |        |

| u = Bit is unchange | d     | x = Bit is unknown   |                   | -n/n = Value at   | POR and BOR/\      | alue at all other | Resets |

| '1' = Bit is set    |       | '0' = Bit is cleared |                   |                   |                    |                   |        |

bit 7-0 PSCNT<7:0>: Prescale Select Low Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 12-4: WDTPSH: WDT PRESCALE SELECT HIGH BYTE REGISTER

| R-0/0                      | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 |  |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| PSCNT<15:8> <sup>(1)</sup> |       |       |       |       |       |       |       |  |

| bit 7                      |       |       |       |       |       |       | bit 0 |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PSCNT<15:8>**: Prescale Select High Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 12-5: WDTTMR: WDT TIMER REGISTER

| U-0   | R-0/0 | R-0/0       | R-0/0 | R-0/0 | R-0/0 | R-0/0                       | R-0/0 |

|-------|-------|-------------|-------|-------|-------|-----------------------------|-------|

| —     |       | WDTTMR<3:0> |       |       |       | PSCNT<17:16> <sup>(1)</sup> |       |

| bit 7 |       |             |       |       |       |                             | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '0'

bit 6-3 WDTTMR<3:0>: Watchdog Timer Value bits

bit 2 STATE: WDT Armed Status bit

1 = WDT is armed

0 = WDT is not armed

bit 1-0 **PSCNT<17:16>**: Prescale Select Upper Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

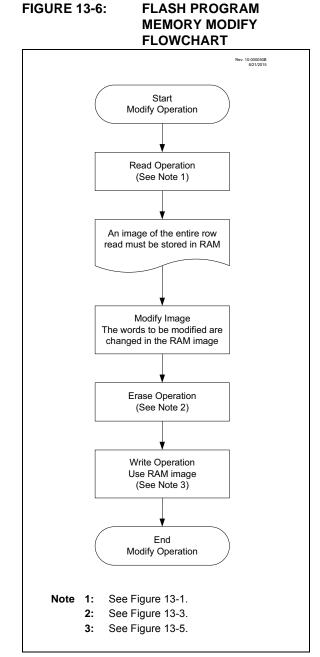

#### 13.3.5 MODIFYING FLASH PROGRAM MEMORY

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

#### 27.4 Timer2 Interrupt

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 27-3.

#### FIGURE 27-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

|                 | Rev. 10-00<br>4                                          | 00205A<br>/7/2016 |

|-----------------|----------------------------------------------------------|-------------------|

| CKPS            | 0b010                                                    |                   |

| PRx             | 1                                                        |                   |

| OUTPS           | 0b0001                                                   |                   |

| TMRx_clk        |                                                          |                   |

| TMRx            |                                                          |                   |

| TMRx_postscaled |                                                          |                   |

| TMRxIF          | (1) (2) (1)                                              |                   |

| Note 1:<br>2:   | Synchronization may take as many as 2 instruction cycles |                   |

### 27.5 Operation Examples

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the TxCON register are cleared).

- The diagrams illustrate any clock except Fosc/4 and show clock-sync delays of at least two full cycles for both ON and Timer2\_ers. When using Fosc/4, the clock-sync delay is at least one instruction period for Timer2\_ers; ON applies in the next instruction period.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in **Section 28.0** "**Capture/Compare/PWM Modules**". The signals are not a part of the Timer2 module.

#### 27.5.1 SOFTWARE GATE MODE

This mode corresponds to legacy Timer2 operation. The timer increments with each clock input when ON = 1 and does not increment when ON = 0. When the TMRx count equals the PRx period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 27-4. With PRx = 5, the counter advances until TMRx = 5, and goes to zero with the next clock.

PIC16(L)F15356/75/76/85/86

#### 32.6.10 SLEEP OPERATION

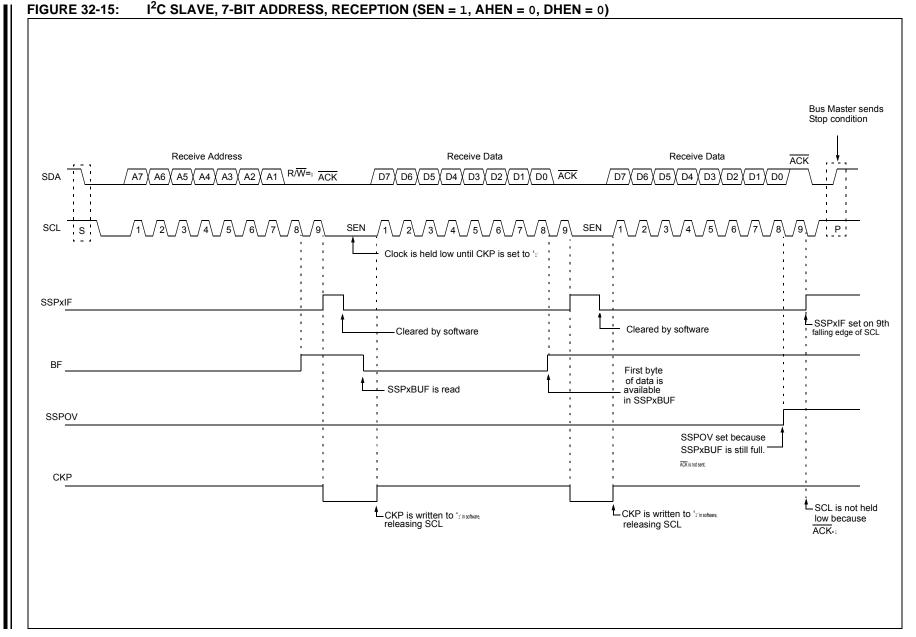

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 32.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

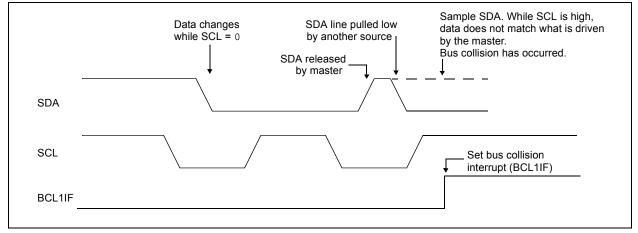

#### 32.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 32.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF and reset the I<sup>2</sup>C port to its Idle state (Figure 32-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 32-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

# PIC16(L)F15356/75/76/85/86

| R/W-0/0         | R/HS/HC-0        | R/W-0/0                                                                              | R/S/HC-0/0                                          | R/S/HC-0/0                 | R/S/HC-0/0                       | R/S/HC-0/0       | R/S/HC-0/0    |  |  |  |

|-----------------|------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------|----------------------------------|------------------|---------------|--|--|--|

| GCEN            | ACKSTAT          | ACKDT                                                                                | ACKEN                                               | RCEN                       | PEN                              | RSEN             | SEN           |  |  |  |

| bit 7           |                  |                                                                                      |                                                     |                            |                                  |                  | bit (         |  |  |  |

| Legend:         |                  |                                                                                      |                                                     |                            |                                  |                  |               |  |  |  |

| •               | la hit           | M = Mritabla                                                                         | hit                                                 |                            | monted bit read                  |                  |               |  |  |  |

| R = Readabl     |                  | W = Writable                                                                         |                                                     | •                          | nented bit, read                 |                  |               |  |  |  |

| u = Bit is und  | •                | x = Bit is unk                                                                       |                                                     |                            | at POR and BO                    |                  | other Resets  |  |  |  |

| '1' = Bit is se | et               | '0' = Bit is cle                                                                     | eared                                               | HC = Cleared               | d by hardware                    | S = User set     |               |  |  |  |

| bit 7           | 1 = Enable in    |                                                                                      | •                                                   | • •                        | or 00h) is receiv                | ed in the SSPx   | SR            |  |  |  |

| bit 6           | 1 = Acknowle     | cknowledge Si<br>dge was not r<br>dge was recei                                      |                                                     | mode only)                 |                                  |                  |               |  |  |  |

| bit 5           | In Receive me    | ode:<br>itted when the                                                               | a bit (in I <sup>2</sup> C moo<br>user initiates a  | • •                        | e sequence at                    | the end of a ree | ceive         |  |  |  |

|                 | 0 = Acknowle     | -                                                                                    |                                                     |                            |                                  |                  |               |  |  |  |

| bit 4           |                  | <b>ACKEN:</b> Acknowledge Sequence Enable bit (in I <sup>2</sup> C Master mode only) |                                                     |                            |                                  |                  |               |  |  |  |

|                 | Automati         |                                                                                      | by hardware.                                        | SDA and S                  | CL pins, and                     | transmit ACk     | (DT data bi   |  |  |  |

| bit 3           |                  | Receive mode                                                                         | (in I <sup>2</sup> C Master<br>for I <sup>2</sup> C | mode only)                 |                                  |                  |               |  |  |  |

| bit 2           | SCKMSSP R        | elease Contro                                                                        |                                                     |                            | y)<br>atically cleared           | by hardware.     |               |  |  |  |

|                 | 0 = Stop cond    | dition Idle                                                                          |                                                     |                            |                                  |                  |               |  |  |  |

| bit 1           | 1 = Initiate R   |                                                                                      |                                                     | •                          | er mode only)<br>ins. Automatica | lly cleared by h | nardware.     |  |  |  |

| bit 0           | In Master mo     | <u>de:</u><br>art condition o                                                        | e/Stretch Enab<br>n SDA and SC                      |                            | atically cleared                 | by hardware.     |               |  |  |  |

|                 |                  |                                                                                      |                                                     | ave transmit ar            | nd slave receive                 | e (stretch enabl | ed)           |  |  |  |

| Note 1: F       | or bits ACKEN, R | CEN. PEN. R                                                                          | SEN, SEN: If t                                      | he l <sup>2</sup> C module | is not in the IDI                | E mode, this b   | bit may not b |  |  |  |

## REGISTER 32-3: SSPxCON2: SSPx CONTROL REGISTER 2 (I<sup>2</sup>C MODE ONLY)<sup>(1)</sup>

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the IDLE mode, this bit may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

# PIC16(L)F15356/75/76/85/86

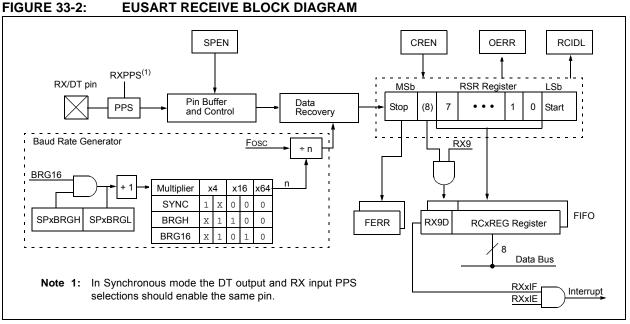

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 33-1, Register 33-2 and Register 33-3, respectively.

The RX input pin is selected with the RXPPS. The CK input is selected with the TXPPS register. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

| R/W-0/0          | U-0                                                                          | U-0                                   | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|------------------|------------------------------------------------------------------------------|---------------------------------------|----------------|----------------|------------------|------------------|--------------|--|--|--|

| CLKREN           | _                                                                            | —                                     | CLKRI          | DC<1:0>        | (                | CLKRDIV<2:0>     |              |  |  |  |

| bit 7            |                                                                              |                                       |                |                |                  |                  | bit C        |  |  |  |

| Legend:          |                                                                              |                                       |                |                |                  |                  |              |  |  |  |

| R = Readable     | bit                                                                          | W = Writable                          | bit            | U = Unimpler   | nented bit, read | l as '0'         |              |  |  |  |

| u = Bit is unch  | anged                                                                        | x = Bit is unkr                       | iown           | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set |                                                                              | '0' = Bit is clea                     | ared           |                |                  |                  |              |  |  |  |

|                  |                                                                              |                                       |                |                |                  |                  |              |  |  |  |

| bit 7            | CLKREN: Re                                                                   | ference Clock                         | Module Enable  | e bit          |                  |                  |              |  |  |  |

|                  | 1 = Referen                                                                  | 1 = Reference clock module enabled    |                |                |                  |                  |              |  |  |  |

|                  | 0 = Referen                                                                  | ce clock modul                        | le is disabled |                |                  |                  |              |  |  |  |

| bit 6-5          | Unimplemen                                                                   | ted: Read as '                        | כי             |                |                  |                  |              |  |  |  |

| bit 4-3          | CLKRDC<1:0>: Reference Clock Duty Cycle bits <sup>(1)</sup>                  |                                       |                |                |                  |                  |              |  |  |  |

|                  | 11 = Clock outputs duty cycle of 75%                                         |                                       |                |                |                  |                  |              |  |  |  |

|                  | 10 = Clock outputs duty cycle of 50%                                         |                                       |                |                |                  |                  |              |  |  |  |

|                  | 01 = Clock outputs duty cycle of 25%<br>00 = Clock outputs duty cycle of 0%  |                                       |                |                |                  |                  |              |  |  |  |

|                  |                                                                              |                                       |                |                |                  |                  |              |  |  |  |

| bit 2-0          |                                                                              | 0>: Reference                         |                | bits           |                  |                  |              |  |  |  |

|                  |                                                                              | 111 = Base clock value divided by 128 |                |                |                  |                  |              |  |  |  |

|                  | 110 = Base clock value divided by 64                                         |                                       |                |                |                  |                  |              |  |  |  |

|                  | 101 = Base clock value divided by 32<br>100 = Base clock value divided by 16 |                                       |                |                |                  |                  |              |  |  |  |

|                  |                                                                              | lock value divid                      |                |                |                  |                  |              |  |  |  |

|                  |                                                                              | lock value divid                      | •              |                |                  |                  |              |  |  |  |

|                  |                                                                              | lock value divid                      | led by 2       |                |                  |                  |              |  |  |  |

|                  | 000 <b>= Base c</b>                                                          | lock value                            |                |                |                  |                  |              |  |  |  |

#### REGISTER 34-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

**Note 1:** Bits are valid for reference clock divider values of two or larger, the base clock cannot be further divided.

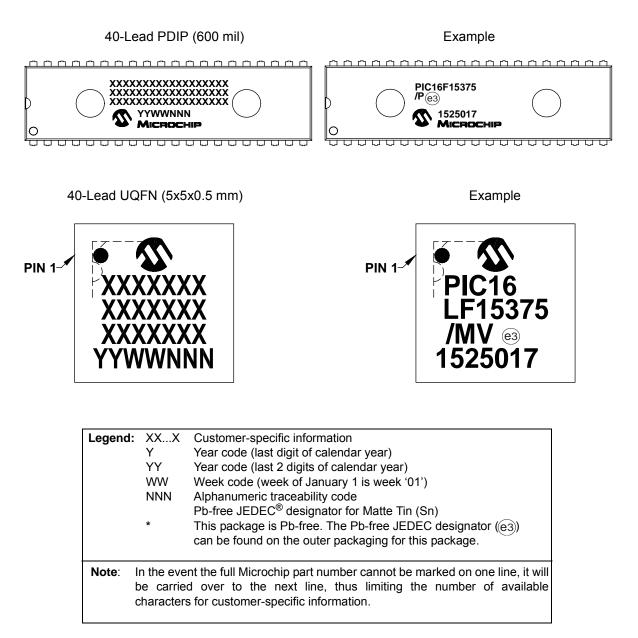

## 40.1 Package Marking Information (Continued)

#### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |      |           |      |  |

|------------------------|-------------|------|-----------|------|--|

| Dimensior              | Limits      | MIN  | NOM       | MAX  |  |

| Number of Pins         | Ν           |      | 28        |      |  |

| Pitch                  | е           |      | 0.40 BSC  |      |  |

| Overall Height         | Α           | 0.45 | 0.50      | 0.55 |  |

| Standoff               | A1          | 0.00 | 0.02      | 0.05 |  |

| Contact Thickness      | A3          |      | 0.127 REF |      |  |

| Overall Width          | Е           |      | 4.00 BSC  |      |  |

| Exposed Pad Width      | E2          | 2.55 | 2.65      | 2.75 |  |

| Overall Length         | D           |      | 4.00 BSC  |      |  |

| Exposed Pad Length     | D2          | 2.55 | 2.65      | 2.75 |  |

| Contact Width          | b           | 0.15 | 0.20      | 0.25 |  |

| Contact Length         | L           | 0.30 | 0.40      | 0.50 |  |

| Contact-to-Exposed Pad | K           | 0.20 | -         | -    |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2

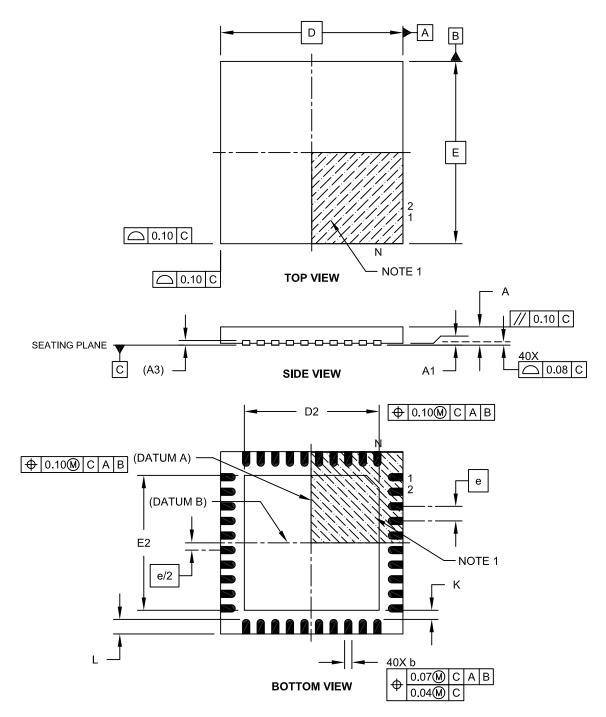

#### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2