Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

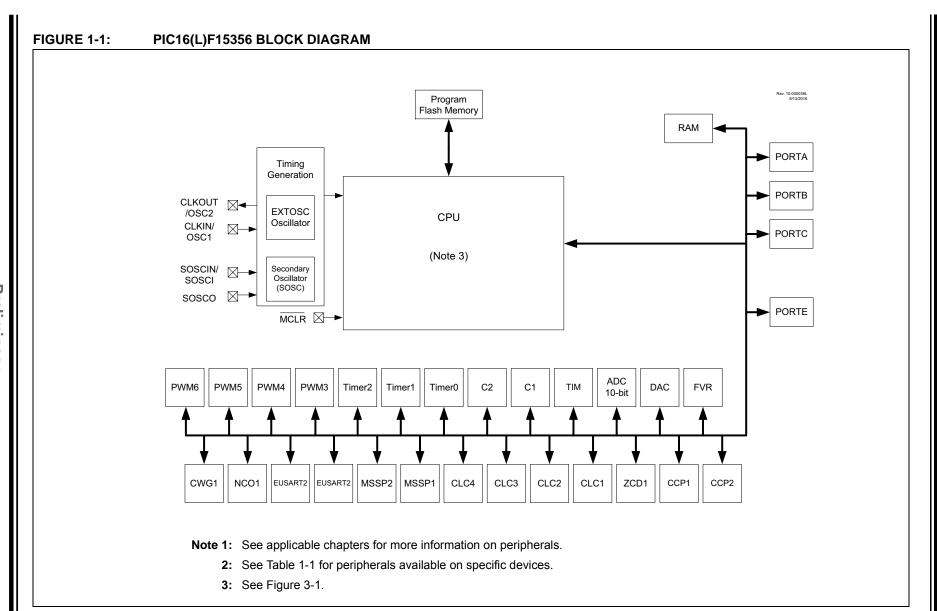

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-TQFP                                                                     |

| Supplier Device Package    | 48-TQFP (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15385t-i-pt |

PIC16(L)F15356/75/76/85/86

TABLE 1-2: PIC16(L)F15356 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                                    | Function              | Input<br>Type    | Output Type | Description                                                                                 |

|---------------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------|---------------------------------------------------------------------------------------------|

| RA6/ANA6/OSC2/CLKOUT/IOCA6                                                                              | RA6                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                         | ANA6                  | AN               | _           | ADC Channel A6 input.                                                                       |

|                                                                                                         | OSC2                  | _                | XTAL        | External Crystal/Resonator (LP, XT, HS modes) driver output.                                |

|                                                                                                         | CLKOUT                | _                | CMOS/OD     | Fosc/4 digital output (in non-crystal/resonator modes).                                     |

|                                                                                                         | IOCA6                 | TTL/ST           | -           | Interrupt-on-change input.                                                                  |

| RA7/ANA7/OSC1/CLKIN/IOCA7                                                                               | RA7                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                         | ANA7                  | AN               | -           | ADC Channel A7 input.                                                                       |

|                                                                                                         | OSC1                  | XTAL             | -           | External Crystal/Resonator (LP, XT, HS modes) driver input.                                 |

|                                                                                                         | CLKIN                 | TTL/ST           | _           | External digital clock input.                                                               |

|                                                                                                         | IOCA7                 | TTL/ST           | _           | Interrupt-on-change input.                                                                  |

| RB0/ANB0/C2IN1+/ZCD1/ <del>SS2<sup>(1)</sup>/</del><br>CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup> /IOCB0 | RB0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

| CWG IIIV /III I / /IOCBU                                                                                | ANB0                  | AN               | _           | ADC Channel B0 input.                                                                       |

|                                                                                                         | C2IN1+                | AN               | _           | Comparator 2 positive input.                                                                |

|                                                                                                         | ZCD1                  | AN               | AN          | Zero-cross detect input pin (with constant current sink/ source).                           |

|                                                                                                         | SS2 <sup>(1)</sup>    | TTL/ST           | -           | MSSP2 SPI slave select input.                                                               |

|                                                                                                         | CWG1IN <sup>(1)</sup> | TTL/ST           | -           | Complementary Waveform Generator 1 input.                                                   |

|                                                                                                         | INT <sup>(1)</sup>    | TTL/ST           | _           | External interrupt request input.                                                           |

|                                                                                                         | IOCB0                 | TTL/ST           | -           | Interrupt-on-change input.                                                                  |

| RB1/ANB1/C1IN3-/C2IN3-/SCL2 <sup>(3,4)</sup> /<br>SCK2 <sup>(1)</sup> /IOCB1                            | RB1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

| SCKZ* /IOCBT                                                                                            | ANB1                  | AN               | _           | ADC Channel B1 input.                                                                       |

|                                                                                                         | C1IN3-                | AN               | _           | Comparator 1 negative input.                                                                |

|                                                                                                         | C2IN3-                | AN               | _           | Comparator 2 negative input.                                                                |

|                                                                                                         | SCL2 <sup>(3,4)</sup> | I <sup>2</sup> C | OD          | MSSP2 I <sup>2</sup> C clock input/output.                                                  |

|                                                                                                         | SCK2 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | MSSP2 SPI serial clock (default input location, SCK2 is a PPS remappable input and output). |

|                                                                                                         | IOCB1                 | TTL/ST           | _           | Interrupt-on-change input.                                                                  |

| RB2/ANB2/SDA2 <sup>(3,4)</sup> /SDI2 <sup>(1)</sup> /IOCB2                                              | RB2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                         | ANB2                  | AN               | _           | ADC Channel B2 input.                                                                       |

|                                                                                                         | SDA2 <sup>(3,4)</sup> | I <sup>2</sup> C | OD          | MSSP2 I <sup>2</sup> C serial data input/output.                                            |

|                                                                                                         | SDI2 <sup>(1)</sup>   | TTL/ST           | _           | MSSP2 SPI serial data input.                                                                |

|                                                                                                         | IOCB2                 | TTL/ST           | _           | Interrupt-on-change input.                                                                  |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage XTAL = Crystal levels

e 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

- All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin

options as described in Table 15-3.

- 3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

- 4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

#### 5.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 5.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP}=0$ , external reads and writes of program memory are inhibited and a read will return all 'o's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See Section 5.4 "Write Protection" for more information.

#### 5.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRTAPP, WRTSAF, WRTB, WRTC bits in Configuration Words (Register 5-4) define whether the corresponding region of the program memory block is protected or not.

#### 5.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 13.3.6 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC16(L)F153xx Memory Programming Specification" (DS40001838).

#### 8.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 8.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 8-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 8-2 for more information.

TABLE 8-1: BOR OPERATING MODES

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |                             |

|------------|--------|-------------|----------|---------------------------------------------------------------------|-----------------------------|

| 11         | х      | Х           | Active   | Wait for release of BOR <sup>(1)</sup> (BORRDY = 1)                 |                             |

| 10         | 77     | Awake       | Active   | Waits for release of BOR (BORRDY = 1)                               |                             |

| 10         | X      | Α           | Sleep    | Disabled                                                            | Waits for BOR Reset release |

| 0.1        | 1      | X           | Active   | Waits for BOR Reset release (BORRDY = 1)                            |                             |

| 01         | 0      | Х           | Disabled | Regine immediately (RODDDV =)                                       |                             |

| 0.0        | Х      | Х           | Disabled | Begins immediately (BORRDY = x)                                     |                             |

**Note 1:** In this specific case, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 8.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 8.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

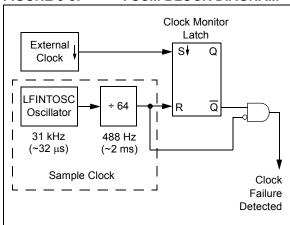

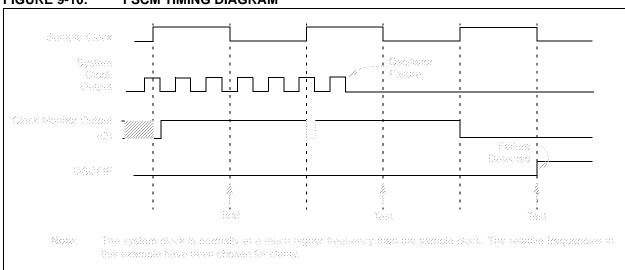

#### 9.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, ECL, ECM, ECH and Secondary Oscillator).

FIGURE 9-9: FSCM BLOCK DIAGRAM

#### 9.4.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 9-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 9.4.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to the HFINTOSC at 1 MHz clock frequency and sets the bit flag OSFIF of the PIR1 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE1 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation, by writing to the NOSC and NDIV bits of the OSCCON1 register.

#### 9.4.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the NOSC and NDIV bits of the OSCCON1 register. When switching to the external oscillator, or external oscillator and PLL, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON1. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

#### 9.4.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. Therefore, the device will always be executing code while the OST is operating.

#### REGISTER 10-9: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|---------|---------|-----|-----|-----|---------|

| _     | _   | NVMIE   | NCO1IE  | _   | _   | _   | CWG1IE  |

| bit 7 |     |         |         |     |     |     | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedHS = Hardware set

bit 7-6 **Unimplemented:** Read as '0'. bit 5 **NVMIE:** NVM Interrupt Enable bit

1 = NVM task complete interrupt enabled

0 = NVM interrupt not enabled

bit 4 NCO1IE: NCO Interrupt Enable bit

1 = NCO rollover interrupt enabled0 = NCO rollover interrupt disabled

bit 3-1 **Unimplemented:** Read as '0'.

bit 0 **CWG1IE:** Complementary Waveform Generator (CWG) 2 Interrupt Enable bit

1 = CWG1 interrupt is enabled0 = CWG1 interrupt disabled

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE7.

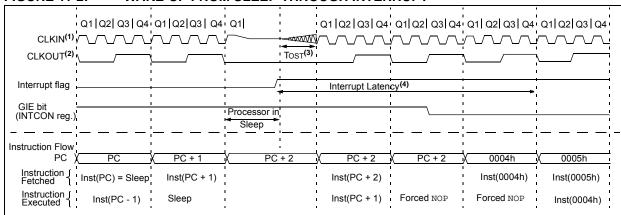

#### 11.2.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source, with the exception of the clock switch interrupt, has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs during or after the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

#### FIGURE 11-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT

#### Note

- 1: External clock. High, Medium, Low mode assumed.

- 2: CLKOUT is shown here for timing reference.

- 3: Tost = 1024 Tosc. This delay does not apply to EC and INTOSC Oscillator modes.

- 4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### 11.2.3 LOW-POWER SLEEP MODE

The PIC16F15356/75/76/85/86 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC16F15356/75/76/85/86 allows the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. Depending on the configuration of these bits, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

#### 11.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

# 12.0 WINDOWED WATCHDOG TIMER (WWDT)

The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WDT has the following features:

- · Selectable clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Configurable window size from 12.5 to 100 percent of the time-out period

- · Multiple Reset conditions

- · Operation during Sleep

#### REGISTER 17-4: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 IOCBP<7:4>: Interrupt-on-Change PORTB Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 3-0 **Unimplemented:** read as '0'

#### REGISTER 17-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 IOCBN<7:4>: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 3-0 **Unimplemented:** read as '0'

#### REGISTER 20-2: ADCON1: ADC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----------|---------|-----|-----|---------|---------|

| ADFM    |         | ADCS<2:0> |         | _   | _   | ADPRE   | F<1:0>  |

| bit 7   |         |           |         |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 ADFM: ADC Result Format Select bit

1 = Right justified. Six Most Significant bits of ADRESH are set to '0' when the conversion result is loaded.

0 = Left justified. Six Least Significant bits of ADRESL are set to '0' when the conversion result is loaded.

bit 6-4 ADCS<2:0>: ADC Conversion Clock Select bits

111 = ADCRC (dedicated RC oscillator)

110 = Fosc/64

101 = Fosc/16

100 = Fosc/4

011 = ADCRC (dedicated RC oscillator)

010 = Fosc/32

001 = Fosc/8

000 = Fosc/2

bit 3-2 Unimplemented: Read as '0'

bit 1-0 ADPREF<1:0>: ADC Positive Voltage Reference Configuration bits

11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module<sup>(1)</sup>

10 = VREF+ is connected to external VREF+  $pin^{(1)}$

01 = Reserved

00 = VREF+ is connected to VDD

**Note 1:** When selecting the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See Table 37-14 for details.

#### 22.2 FIXED DUTY CYCLE MODE

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled at a frequency rate half of the FOVERFLOW. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 22-2.

The FDC mode is selected by clearing the N1PFM bit in the NCO1CON register.

#### 22.3 PULSE FREQUENCY MODE

In Pulse Frequency (PF) mode, every time the Accumulator overflows, the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output. The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 22-2.

The value of the active and inactive states depends on the polarity bit, N1POL in the NCO1CON register.

The PF mode is selected by setting the N1PFM bit in the NCO1CON register.

#### 22.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the N1PWS<2:0> bits in the NCO1CLK register.

When the selected pulse width is greater than the Accumulator overflow time frame, then NCO1 output does not toggle.

#### 22.4 OUTPUT POLARITY CONTROL

The last stage in the NCO module is the output polarity. The N1POL bit in the NCO1CON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCO output signal (NCO1\_out) is available to the following peripherals:

- CLC

- CWG

- Timer1

- Timer2

- CLKR

#### 22.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCO Interrupt Flag bit, NCO1IF, of the PIR7 register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- · N1EN bit of the NCO1CON register

- · NCO1IE bit of the PIE7 register

- PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCO1IF bit in the Interrupt Service Routine.

#### 22.6 Effects of a Reset

All of the NCO registers are cleared to zero as the result of a Reset.

#### 22.7 Operation in Sleep

The NCO module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO clock source, when the NCO is enabled, the CPU will go idle during Sleep, but the NCO will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### REGISTER 29-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PWMxE   | C<9:2>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **PWMxDC<9:2>:** PWM Duty Cycle Most Significant bits

These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

#### REGISTER 29-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| PWMxD   | C<1:0>  | _   | _   | _   | _   | _   | _     |

| bit 7   |         |     |     |     |     |     | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-6 **PWMxDC<1:0>:** PWM Duty Cycle Least Significant bits

These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register.

bit 5-0 **Unimplemented:** Read as '0'

#### 30.12 Configuring the CWG

The following steps illustrate how to properly configure the CWG.

- Ensure that the TRIS control bits corresponding to the desired CWG pins for your application are set so that the pins are configured as inputs.

- 2. Clear the EN bit, if not already cleared.

- Set desired mode of operation with the MODE bits.

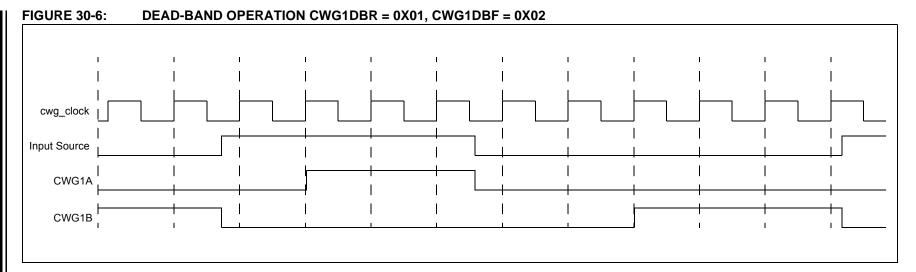

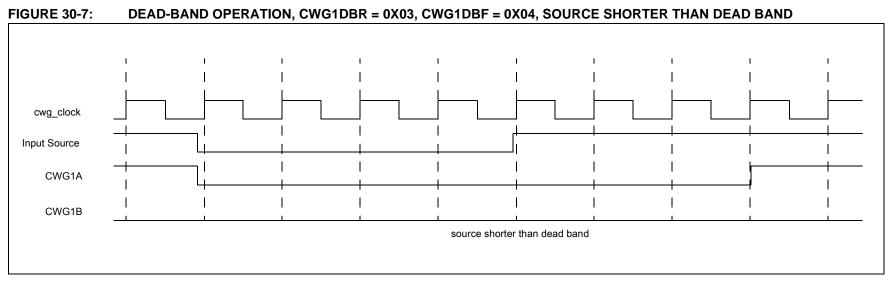

- Set desired dead-band times, if applicable to mode, with the CWG1DBR and CWG1DBF registers.

- Setup the following controls in the CWG1AS0 and CWG1AS1 registers.

- a. Select the desired shutdown source.

- Select both output overrides to the desired levels (this is necessary even if not using autoshutdown because start-up will be from a shutdown state).

- Set which pins will be affected by auto-shutdown with the CWG1AS1 register.

- d. Set the SHUTDOWN bit and clear the REN bit.

- Select the desired input source using the CWG1ISM register.

- 7. Configure the following controls.

- a. Select desired clock source using the CWG1CLKCON register.

- Select the desired output polarities using the CWG1CON1 register.

- c. Set the output enables for the desired outputs.

- 8. Set the EN bit.

- Clear TRIS control bits corresponding to the desired output pins to configure these pins as outputs.

- If auto-restart is to be used, set the REN bit and the SHUTDOWN bit will be cleared automatically. Otherwise, clear the SHUTDOWN bit to start the CWG.

#### 30.12.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the LSBD and LSAC bits of the CWG1AS0 register. LSBD<1:0> controls the CWG1B and D override levels and LSAC<1:0> controls the CWG1A and C override levels. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not affect the override level.

#### 30.12.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- · Software controlled

- Auto-restart

The restart method is selected with the REN bit of the CWG1CON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 30-13 and Figure 30-14.

#### 30.12.2.1 Software Controlled Restart

When the REN bit of the CWG1AS0 register is cleared, the CWG must be restarted after an auto-shutdown event by software. Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the SHUTDOWN bit will remain set. The overrides will remain in effect until the first rising edge event after the SHUTDOWN bit is cleared. The CWG will then resume operation.

#### 30.12.2.2 Auto-Restart

When the REN bit of the CWG1CON2 register is set, the CWG will restart from the auto-shutdown state automatically. The SHUTDOWN bit will clear automatically when all shutdown sources go low. The overrides will remain in effect until the first rising edge event after the SHUTDOWN bit is cleared. The CWG will then resume operation.

#### REGISTER 30-2: CWG1CON1: CWG1 CONTROL REGISTER 1

| U-0   | U-0 | R-x | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | IN  | _   | POLD    | POLC    | POLB    | POLA    |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-6 | Unimplemented: Read as '0'                                                                            |

|---------|-------------------------------------------------------------------------------------------------------|

| bit 5   | IN: CWG Input Value bit                                                                               |

| bit 4   | Unimplemented: Read as '0'                                                                            |

| bit 3   | POLD: CWG1D Output Polarity bit                                                                       |

|         | <ul><li>1 = Signal output is inverted polarity</li><li>0 = Signal output is normal polarity</li></ul> |

| bit 2   | POLC: CWG1C Output Polarity bit                                                                       |

|         | <ul><li>1 = Signal output is inverted polarity</li><li>0 = Signal output is normal polarity</li></ul> |

| bit 1   | POLB: CWG1B Output Polarity bit                                                                       |

|         | <ul><li>1 = Signal output is inverted polarity</li><li>0 = Signal output is normal polarity</li></ul> |

| bit 0   | POLA: CWG1A Output Polarity bit                                                                       |

|         | <ul><li>1 = Signal output is inverted polarity</li><li>0 = Signal output is normal polarity</li></ul> |

#### CWG1AS0: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 0 REGISTER 30-5:

| R/W/HS-0/0                 | R/W-0/0 | R/W-0/0   | R/W-1/1 | R/W-0/0   | R/W-1/1 | U-0 | U-0   |

|----------------------------|---------|-----------|---------|-----------|---------|-----|-------|

| SHUTDOWN <sup>(1, 2)</sup> | REN     | LSBD<1:0> |         | LSAC<1:0> |         | _   | _     |

| bit 7                      |         |           |         |           |         | •   | bit 0 |

Legend: HC = Bit is cleared by hardware HS = Bit is set by hardware R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared q = Value depends on condition

SHUTDOWN: Auto-Shutdown Event Status bit (1, 2) bit 7

> 1 = An Auto-Shutdown state is in effect 0 = No Auto-shutdown event has occurred

bit 6 **REN:** Auto-Restart Enable bit

> 1 = Auto-restart enabled 0 = Auto-restart disabled

bit 5-4 LSBD<1:0>: CWG1B and CWG1D Auto-Shutdown State Control bits

> 11 =A logic '1' is placed on CWG1B/D when an auto-shutdown event is present 10 =A logic '0' is placed on CWG1B/D when an auto-shutdown event is present 01 =Pin is tri-stated on CWG1B/D when an auto-shutdown event is present

00 =The inactive state of the pin, including polarity, is placed on CWG1B/D after the required dead-

band interval

bit 3-2 LSAC<1:0>: CWG1A and CWG1C Auto-Shutdown State Control bits

> 11 =A logic '1' is placed on CWG1A/C when an auto-shutdown event is present 10 =A logic '0' is placed on CWG1A/C when an auto-shutdown event is present 01 =Pin is tri-stated on CWG1A/C when an auto-shutdown event is present

00 =The inactive state of the pin, including polarity, is placed on CWG1A/C after the required deadband interval

bit 1-0 Unimplemented: Read as '0'

Note 1: This bit may be written while EN = 0 (CWG1CON0 register) to place the outputs into the shutdown configuration.

2: The outputs will remain in auto-shutdown state until the next rising edge of the input signal after this bit is cleared.

**Preliminary** © 2016 Microchip Technology Inc. DS40001866A-page 398

#### 32.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allows time for the slave software to decide whether it wants to  $\overline{\text{ACK}}$  the receive address or data byte.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 32-16 displays a module using both address and data holding. Figure 32-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to determine if the SSPxIF was after or before the ACK.

- Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the ninth falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set

- SSPxIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSPxSTAT register.

#### REGISTER 32-4: SSPxCON3: SSPx CONTROL REGISTER 3

| R-0/0                 | R/W-0/0 |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|

| ACKTIM <sup>(3)</sup> | PCIE    | SCIE    | BOEN    | SDAHT   | SBCDE   | AHEN    | DHEN    |

| bit 7                 |         | •       | •       |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 ACKTIM: Acknowledge Time Status bit (I<sup>2</sup>C mode only)<sup>(3)</sup>

1 = Indicates the I<sup>2</sup>C bus is in an Acknowledge sequence, set on 8<sup>th</sup> falling edge of SCL clock

0 = Not an Acknowledge sequence, cleared on 9<sup>TH</sup> rising edge of SCL clock

bit 6 **PCIE**: Stop Condition Interrupt Enable bit (I<sup>2</sup>C mode only)

1 = Enable interrupt on detection of Stop condition

0 = Stop detection interrupts are disabled(2)

bit 5 SCIE: Start Condition Interrupt Enable bit (I<sup>2</sup>C mode only)

1 = Enable interrupt on detection of Start or Restart conditions

0 = Start detection interrupts are disabled<sup>(2)</sup>

bit 4 **BOEN:** Buffer Overwrite Enable bit

In SPI Slave mode: (1)

1 = SSPxBUF updates every time that a new data byte is shifted in ignoring the BF bit

0 = If new byte is received with BF bit of the SSPxSTAT register already set, SSPOV bit of the SSPxCON1 register is set, and the buffer is not updated

In I<sup>2</sup>C Master mode and SPI Master mode:

This bit is ignored.

In I<sup>2</sup>C Slave mode:

1 = SSPxBUF is updated and ACK is generated for a received address/data byte, ignoring the state of the SSPOV bit only if the BF bit = 0.

0 = SSPxBUF is only updated when SSPOV is clear

bit 3 SDAHT: SDA Hold Time Selection bit (I<sup>2</sup>C mode only)

1 = Minimum of 300 ns hold time on SDA after the falling edge of SCL

0 = Minimum of 100 ns hold time on SDA after the falling edge of SCL

bit 2 SBCDE: Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

If, on the rising edge of SCL, SDA is sampled low when the module is outputting a high state, the BCL1IF bit of the PIR3 register is set, and bus goes idle

1 = Enable slave bus collision interrupts

0 = Slave bus collision interrupts are disabled

bit 1 AHEN: Address Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the eighth falling edge of SCL for a matching received address byte; CKP bit of the SSPxCON1 register will be cleared and the SCL will be held low.

0 = Address holding is disabled

bit 0 **DHEN:** Data Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the eighth falling edge of SCL for a received data byte; slave hardware clears the CKP bit of the SSPxCON1 register and SCL is held low.

0 = Data holding is disabled

**Note** 1: For daisy-chained SPI operation; allows the user to ignore all but the last received byte. SSPOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSPxBUF.

2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

3: The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

**TABLE 37-6:** THERMAL CHARACTERISTICS

| Standar       | d Operating | Conditions (unless otherwise stated)   |                    |                          |                                                          |

|---------------|-------------|----------------------------------------|--------------------|--------------------------|----------------------------------------------------------|

| Param.<br>No. | Sym.        | Characteristic                         | Тур.               | Units                    | Conditions                                               |

| TH01          | θЈА         | Thermal Resistance Junction to Ambient | 60                 | °C/W                     | 28-pin SPDIP package                                     |

|               |             |                                        | 80                 | °C/W                     | 28-pin SOJC package                                      |

|               |             |                                        | 90                 | °C/W                     | 28-pin SSOP package                                      |

|               |             |                                        | 48                 | °C/W                     | 28-pin UQFN 4x4mm package                                |

|               |             |                                        | 47.2               | °C/W                     | 40-pin PNP package                                       |

|               |             |                                        | 41.0               | °C/W ~                   | 40-pin UQFN 5x5 package                                  |

|               |             |                                        | 46.0               | °C/W/                    | 44-pin TQFP package                                      |

|               |             |                                        | 24.4               | °C/W\                    | 44-pin QFN 8X8mm package                                 |

|               |             |                                        | 27.6               | °C/W                     | 48-pin UQFN 6x6 package                                  |

|               |             |                                        | - (                | ∕∘c/w                    | 48-pin TQFP 7x7 package                                  |

| TH02          | θJC         | Thermal Resistance Junction to Case    | 31.4               | °C/W                     | 28-pin SPDIP package                                     |

|               |             |                                        | 2,4                | · CW                     | 28-pin SOIC package                                      |

|               |             |                                        | 24 -               | °C/W                     | 28-pin SSOP package                                      |

|               |             |                                        | /\12               | √C/W                     | 28-pin UQFN 4x4mm package                                |

|               |             | 24.70                                  | \ <sub>°</sub> C/W | 40-pin PDIP package      |                                                          |

|               |             | 5.5                                    | ∘c⁄w               | 40-pin UQFN 5x5 package  |                                                          |

|               |             | 14.5                                   | >°C/W              | 44-pin TQFP package      |                                                          |

|               | _ \ \       | 20.0                                   | °C/W               | 44-pin QFN 8X8mm package |                                                          |

|               |             | 6.7                                    | °C/W               | 48-pin UQFN 6x6 package  |                                                          |

|               |             |                                        | °C/W               | 48-pin TQFP 7x7 package  |                                                          |

| TH03          | ТЈМАХ       | Maximum Junction Temperature           | 150                | °C                       |                                                          |

| TH04          | PD          | Power Dissipation                      | _                  | W                        | PD = PINTERNAL + PI/O                                    |

| TH05          | PINTERNAL   | Internal Power Dissipation             | _                  | W                        | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| TH06          | Pı/o        | I/O Power Dissipation                  | _                  | W                        | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07          | PDER        | Derated Power                          | _                  | W                        | PDER = PDMAX (TJ - TA)/θJA <sup>(2)</sup>                |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, All Rights Reserved. ISBN: 978-1-5224-1167-3