Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 44                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-UQFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15386-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                         | ABLE 4-11. SPECIAL FUNCTION REGISTER SUMMART BANKS 0-05 (CONTINUED) |                     |       |               |               |                   |           |         |       |                       |                            |

|---------------------------------------------------------|---------------------------------------------------------------------|---------------------|-------|---------------|---------------|-------------------|-----------|---------|-------|-----------------------|----------------------------|

| Address                                                 | Name                                                                | Bit 7               | Bit 6 | Bit 5         | Bit 4         | Bit 3             | Bit 2     | Bit 1   | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 5                                                  | ink 5                                                               |                     |       |               |               |                   |           |         |       |                       |                            |

|                                                         |                                                                     |                     |       | CPU COF       | RE REGISTERS; | see Table 4-3 for | specifics |         |       |                       |                            |

| 28Ch T2TMR Holding Register for the 8-bit TMR2 Register |                                                                     |                     |       |               |               |                   |           |         |       | 0000 0000             | 0000 0000                  |

| 28Dh                                                    | T2PR                                                                | TMR2 Period Registe | er    |               |               |                   |           |         |       | 1111 1111             | 1111 1111                  |

| 28Eh                                                    | T2CON                                                               | ON                  |       | CKPS<2:0>     |               |                   | OUT       | PS<3:0> |       | 0000 0000             | 0000 0000                  |

| 28Fh                                                    | T2HLT                                                               | PSYNC               | CKPOL | CKSYNC        |               |                   | MODE<4:0> |         |       | 0000 0000             | 0000 0000                  |

| 290h                                                    | T2CLKCON                                                            | _                   | _     | _             | —             |                   | C         | S<3:0>  |       | 0000                  | 0000                       |

| 291h                                                    | T2RST                                                               | _                   | _     | — — RSEL<3:0> |               |                   |           | 0000    | 0000  |                       |                            |

| 292h<br><br>29Fh                                        | _                                                                   | Unimplemented       |       |               |               |                   |           |         | -     | —                     |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| TABLE 4 | -11: SPEC | IAL FUNCTION             | REGISTER            | SUMMARY             | BANKS 0-        | 63 (CONTIN        | IUED)     | 1                 |       |                       |                            |

|---------|-----------|--------------------------|---------------------|---------------------|-----------------|-------------------|-----------|-------------------|-------|-----------------------|----------------------------|

| Address | Name      | Bit 7                    | Bit 6               | Bit 5               | Bit 4           | Bit 3             | Bit 2     | Bit 1             | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 11 |           |                          |                     |                     |                 |                   |           |                   |       |                       |                            |

|         |           |                          |                     |                     |                 | see Table 4-3 for | anacifica |                   |       |                       |                            |

|         |           |                          |                     | CPUCOF              | KE KEGISTERS,   | see Table 4-3 Iol | specifics |                   |       |                       |                            |

| 58Ch    | NCO1ACCL  |                          |                     |                     | NCO1AC          | C<7:0>            |           |                   |       | 0000 0000             | 0000 0000                  |

| 58Dh    | NCO1ACCH  |                          |                     |                     | NCO1AC          | C<15:8>           |           |                   |       | 0000 0000             | 0000 0000                  |

| 58Eh    | NCO1ACCU  | —                        | —                   | —                   | —               |                   | NCO1A     | ACC<19:16>        |       | 0000                  | 0000                       |

| 58Fh    | NCO1INCL  |                          |                     |                     | NCO1IN          | C<7:0>            |           |                   |       | 0000 0001             | 0000 0001                  |

| 590h    | NCO1INCH  |                          | NCO1INC<15:8>       |                     |                 |                   |           |                   |       | 0000 0000             | 0000 0000                  |

| 591h    | NCO1INCU  | —                        | —                   | —                   | —               |                   | NCO1      | NC<19:16>         |       | 0000                  | 0000                       |

| 592h    | NCO1CON   | N1EN                     | —                   | N1OUT               | N1POL           | —                 | —         | _                 | N1PFM | 0-000                 | 0-000                      |

| 593h    | NCO1CLK   |                          | N1PWS<2:0>          |                     | —               | —                 |           | N1CKS<2:0         | >     | 000000                | 000000                     |

| 594h    | —         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | —                          |

| 595h    | —         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | —                          |

| 596h    | —         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | —                          |

| 597h    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | _                     | _                          |

| 598h    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | _                          |

| 599h    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | _                          |

| 59Ah    | _         |                          |                     |                     | Unimple         | mented            |           |                   |       | —                     | _                          |

| 59Bh    | _         | — Unimplemented          |                     |                     |                 |                   |           |                   |       | —                     | _                          |

| 59Ch    | TMR0L     | Holding Register for the | ne Least Significan | t Byte of the 16-bi | t TMR0 Register |                   |           |                   |       | 0000 0000             | 0000 0000                  |

| 59Dh    | TMR0H     | Holding Register for the | ne Most Significant | Byte of the 16-bit  | TMR0 Register   | •                 |           |                   |       | 1111 1111             | 1111 1111                  |

| 59Eh    | T0CON0    | TOEN                     | _                   | TOOUT               | T016BIT         |                   | TOOL      | JTPS<3:0>         |       | 0-00 0000             | 0-00 0000                  |

| 59Fh    | T0CON1    |                          | T0CS<2:0>           |                     | T0ASYNC         |                   | TOCH      | <ps<3:0></ps<3:0> |       | 0000 0000             | 0000 0000                  |

#### - - - - - -

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| IABLE 4 | ABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |               |              |         |               |                   |           |       |       |                       |                            |  |

|---------|---------------------------------------------------------------------|---------------|--------------|---------|---------------|-------------------|-----------|-------|-------|-----------------------|----------------------------|--|

| Address | Name                                                                | Bit 7         | Bit 6        | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

| Bank 20 | ink 20                                                              |               |              |         |               |                   |           |       |       |                       |                            |  |

|         |                                                                     |               |              | CPU COF | RE REGISTERS: | see Table 4-3 for | specifics |       |       |                       |                            |  |

|         |                                                                     | •             |              | 0.000   |               |                   | opeeniee  |       |       |                       |                            |  |

| A0Ch    |                                                                     | Unimplemented |              |         |               |                   |           |       |       |                       |                            |  |

| A18h    | —                                                                   |               |              |         | Onimplei      | nented            |           |       |       | _                     | _                          |  |

| A19h    | RC2REG                                                              |               | RC2REG<7:0>  |         |               |                   |           |       |       |                       |                            |  |

| A1Ah    | TX2REG                                                              |               | TX2REG<7:0>  |         |               |                   |           |       |       |                       |                            |  |

| A1Bh    | SP2BRGL                                                             | SP2BRGL<7:0>  |              |         |               |                   |           |       |       |                       | 0000 0000                  |  |

| A1Ch    | SP2BRGH                                                             |               | SP2BRGH<7:0> |         |               |                   |           |       |       |                       | 0000 0000                  |  |

| A1Dh    | RC2STA                                                              | SPEN          | RX9          | SREN    | CREN          | ADDEN             | FERR      | OERR  | RX9D  | 0000 0000             | 0000 0000                  |  |

| A1Eh    | TX2STA                                                              | CSRC          | TX9          | TXEN    | SYNC          | SENDB             | BRGH      | TRMT  | TX9D  | 0000 0010             | 0000 0010                  |  |

| A1Fh    | BAUD2CON                                                            | ABDOVF        | RCIDL        | —       | SCKP          | BRG16             | _         | WUE   | ABDEN | 01-0 0-00             | 01-0 0-00                  |  |

## TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

## 9.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use an internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 9.3 "Clock Switching" for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates up to 32 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

## 9.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (1 MHz) or '001' (32 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time.

The HFINTOSC frequency can be selected by setting the HFFRQ<2:0> bits of the OSCFRQ register. The MFINTOSC is an internal clock source within the HFINTOSC that provides two (500 kHz, 32 kHz) constant clock outputs. These constant clock outputs are available for selection to various peripherals, internally.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

## 10.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) of the PIEx[y] registers for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIEx registers)

The PIR1, PIR2, PIR3, PIR4, PIR5, PIR6, and PIR7 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 10.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupts operation, refer to its peripheral chapter.

| Note 1: | Individual interrupt flag bits are set, regardless of the state of any other enable bits.                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| 2:      | All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced |

when the GIE bit is set again.

## 10.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The interrupt is sampled during Q1 of the instruction cycle. The actual interrupt latency then depends on the instruction that is executing at the time the interrupt is detected. See Figure 10-2 and Figure 10-3 for more details.

## 12.0 WINDOWED WATCHDOG TIMER (WWDT)

The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WDT has the following features:

- Selectable clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Configurable window size from 12.5 to 100 percent of the time-out period

- Multiple Reset conditions

- Operation during Sleep

## REGISTER 14-22: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCC7   | ODCC6   | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ODCC<7:0>:** PORTC Open-Drain Enable bits For RC<7:0> pins, respectively 1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

## REGISTER 14-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits

- For RC<7:0> pins, respectively

- 1 = Port pin slew rate is limited

- 0 = Port pin slews at maximum rate

#### REGISTER 14-24: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits For RC<7:0> pins, respectively 1 = ST input used for PORT reads and interrupt-on-change 0 = TTL input used for PORT reads and interrupt-on-change

© 2016 Microchip Technology Inc.

| U-0                                     | U-0 | R/W/HS-0/0 | R/W/HS-0/0                                            | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0            | R/W/HS-0/0            |

|-----------------------------------------|-----|------------|-------------------------------------------------------|------------|------------|-----------------------|-----------------------|

| _                                       | —   | IOCAF5     | IOCAF4                                                | IOCAF3     | IOCAF2     | IOCAF1 <sup>(1)</sup> | IOCAF0 <sup>(1)</sup> |

| bit 7                                   |     |            |                                                       |            |            |                       | bit 0                 |

|                                         |     |            |                                                       |            |            |                       |                       |

| Legend:                                 |     |            |                                                       |            |            |                       |                       |

| R = Readable bit W = Writable b         |     | bit        | U = Unimplemented bit, read as '0'                    |            |            |                       |                       |

| u = Bit is unchanged x = Bit is unknown |     | nown       | -n/n = Value at POR and BOR/Value at all other Resets |            |            | ther Resets           |                       |

## REGISTER 17-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

bit 7-6 Unimplemented: read as '0'

'1' = Bit is set

bit 5-0

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

'0' = Bit is cleared

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

HS - Bit is set in hardware

0 = No change was detected, or the user cleared the detected change.

**Note 1:** If the debugger is enabled, these bits are not available for use.

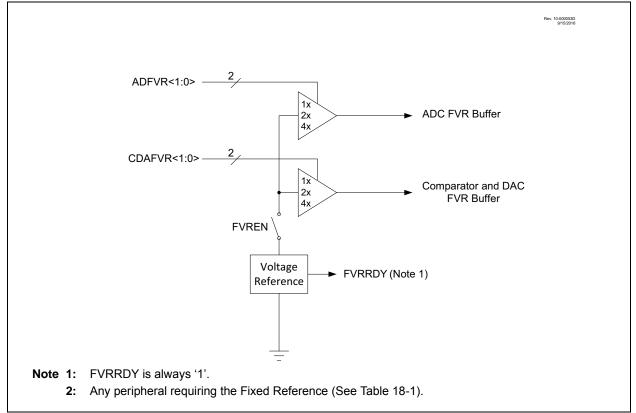

## 18.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · ADC positive reference

- · Comparator positive and negative input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

## 18.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 20.0 "Analog-to-Digital Converter (ADC) Module"** for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" and Section 23.0 "Comparator Module" for additional information.

## 18.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize.

FVRRDY is an indicator of the reference being ready. In the case of an LF device, or a device on which the BOR is enabled in the Configuration Word settings, then the FVRRDY bit will be high prior to setting FVREN as those module require the reference voltage.

FIGURE 18-1: VOLTAGE REFERENCE BLOCK DIAGRAM

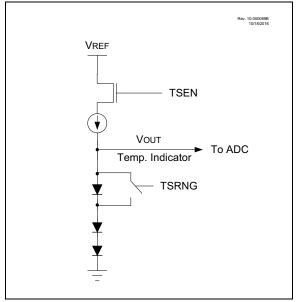

## 19.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The main purpose of the temperature indicator module is to provide a temperature-dependent voltage that can be measured by the Analog-to-Digital Converter.

The circuit's range of operating temperature falls between -40°C and +125°C. The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately.

## **19.1 Module Operation**

The temperature indicator module consists of a temperature-sensing circuit that provides a voltage to the device ADC. The analog voltage output, VTSENSE, varies inversely to the device temperature. The output of the temperature indicator is referred to as VOUT.

Figure 19-1 shows a simplified block diagram of the temperature indicator module.

### FIGURE 19-1: TEMPERATURE INDICATOR BLOCK DIAGRAM

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 20.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

The ON/OFF bit for the module is located in the FVRCON register. See **Section 18.0** "**Fixed Voltage Reference (FVR)**" for more information. The circuit is enabled by setting the TSEN bit of the FVRCON register. When the module is disabled, the circuit draws no current.

The circuit operates in either High or Low range. Refer to **Section 19.5** "**Temperature Indicator Range**" for more details on the range settings.

## 19.2 Estimation of Temperature

This section describes how the sensor voltage can be used to estimate the temperature of the module. To use the sensor, the output voltage, VTSENSE, is measured and the corresponding temperature is determined. Equation 19-1 provides an estimate for the die temperature based on the VTSENSE value.

## EQUATION 19-1: SENSOR TEMPERATURE

$$T_{SENSE} = V_{TSENSE} \times (-Mt) + T_{OFFSET}$$

Where:

Mt = 1/Mv, where Mv = sensor voltage sensitivity (V/°C). TOFFSET is the temperature difference between the theoretical temperature and the actual temperature.

## PIC16(L)F15356/75/76/85/86

## REGISTER 23-5: CMOUT: COMPARATOR OUTPUT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | _   | _   | _   | _   | _   | MC2OUT | MC10UT |

| bit 7 |     |     |     |     |     |        | bit 0  |

## Legend:

| •                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1 MC2OUT: Mirror Copy of C2OUT bit

bit 0 MC1OUT: Mirror Copy of C1OUT bit

## TABLE 23-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name      | Bit 7  | Bit 6  | Bit 5   | Bit 4          | Bit 3      | Bit 2   | Bit 1  | Bit 0   | Register<br>on Page |

|-----------|--------|--------|---------|----------------|------------|---------|--------|---------|---------------------|

| CMxCON0   | ON     | OUT    | _       | POL            | _          | —       | HYS    | SYNC    | 305                 |

| CMxCON1   | _      | _      | _       | _              | _          | _       | INTP   | INTN    | 306                 |

| CMOUT     | _      | _      | _       | _              | _          | _       | MC2OUT | MC1OUT  | 308                 |

| FVRCON    | FVREN  | FVRRDY | TSEN    | TSRNG          | CDAFV      | 'R<1:0> | ADFVF  | R<1:0>  | 264                 |

| DAC1CON0  | DAC1EN | _      | DAC10E1 | DAC10E2        | DAC1PS     | SS<1:0> | _      | DAC1NSS | 287                 |

| DAC1CON1  | _      | _      | _       |                | DAC1R<4:0> |         |        | 287     |                     |

| INTCON    | GIE    | PEIE   | _       |                |            |         |        | INTEDG  | 146                 |

| PIE2      | —      | ZCDIE  | _       | _              | _          | _       | C2IE   | C1IE    | 149                 |

| PIR2      | _      | ZCDIF  | _       | _              | _          | _       | C2IF   | C1IF    | 157                 |

| RxyPPS    | _      | _      | _       | RxyPPS<4:0>    |            |         | 242    |         |                     |

| CLCINxPPS | _      | _      |         | CLCIN0PPS<5:0> |            |         | 241    |         |                     |

| T1GPPS    | _      | _      |         |                | T1GPI      | PS<5:0> |        |         | 241                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

## 27.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

## 28.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

## 28.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE6 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR6 register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4).             |

## 28.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxMODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 28-1 demonstrates the code to perform this function.

#### EXAMPLE 28-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ; to CCPxCON            |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

|         |             |                         |

## 28.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

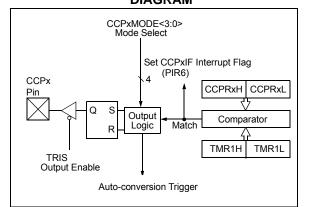

## 28.2 Compare Mode

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- Set the CCPx output

- · Clear the CCPx output

- · Generate an Auto-conversion Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxMODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set, and an ADC conversion can be triggered, if selected.

All Compare modes can generate an interrupt and trigger and ADC conversion.

Figure 28-2 shows a simplified diagram of the compare operation.

#### FIGURE 28-2: COMPARE MODE OPERATION BLOCK DIAGRAM

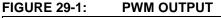

## 29.0 PULSE-WIDTH MODULATION (PWM)

The PWMx modules generate Pulse-Width Modulated (PWM) signals of varying frequency and duty cycle.

In addition to the CCP modules, the PIC16(L)F15356/75/76/85/86 devices contain four 10-bit PWM modules (PWM3, PWM4, PWM5 and PWM6). The PWM modules reproduce the PWM capability of the CCP modules.

The PWM3/4/5/6 Note: modules are four instances of the same PWM module design. Throughout this section, the lower case 'x' in register and bit names is a generic reference to the PWM module number (which should be substituted with 3, or 4, or, 5 or 6 during code development). For example, the control register is generically described in this chapter as PWMxCON, but the actual reaisters are PWM3CON. device PWM4CON, PWM5CON and PWM6CON. Similarly, the PWMxEN bit represents the PWM3EN, PWM4EN, PWM5EN and PWM6EN bits.

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the 'on' state (pulse width), and the low portion of the signal is considered the 'off' state. The term duty cycle describes the proportion of the 'on' time to the 'off' time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and, in turn, the power that is applied to the load.

Figure 29-1 shows a typical waveform of the PWM signal.

### **REGISTER 29-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS**

| R/W-x/u         | R/W-x/u | R/W-x/u         | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|-----------------|---------|-----------------|---------|----------------|------------------|------------------|-------------|

|                 |         |                 | PWMxI   | DC<9:2>        |                  |                  |             |

| bit 7           |         |                 |         |                |                  |                  | bit 0       |

|                 |         |                 |         |                |                  |                  |             |

| Legend:         |         |                 |         |                |                  |                  |             |

| R = Readable    | e bit   | W = Writable I  | oit     | U = Unimplen   | nented bit, read | l as '0'         |             |

| u = Bit is unch | nanged  | x = Bit is unkn | own     | -n/n = Value a | t POR and BO     | R/Value at all c | ther Resets |

bit 7-0 **PWMxDC<9:2>:** PWM Duty Cycle Most Significant bits These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

#### REGISTER 29-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

'0' = Bit is cleared

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| PWMxDC  | <1:0>   | —   | —   | —   | —   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **PWMxDC<1:0>:** PWM Duty Cycle Least Significant bits These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register.

bit 5-0 **Unimplemented:** Read as '0'

'1' = Bit is set

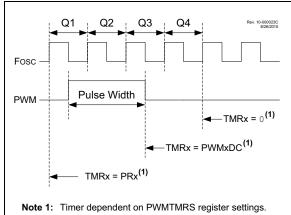

The  $\mathsf{I}^2\mathsf{C}$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited multi-master support

- 7-bit and 10-bit addressing

- Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- General call address matching

- · Address masking

- Selectable SDA hold times

Figure 32-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 32-3 is a diagram of the  $I^2C$  interface module in Slave mode.

Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

> 2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

PIC16(L)F15356/75/76/85/86

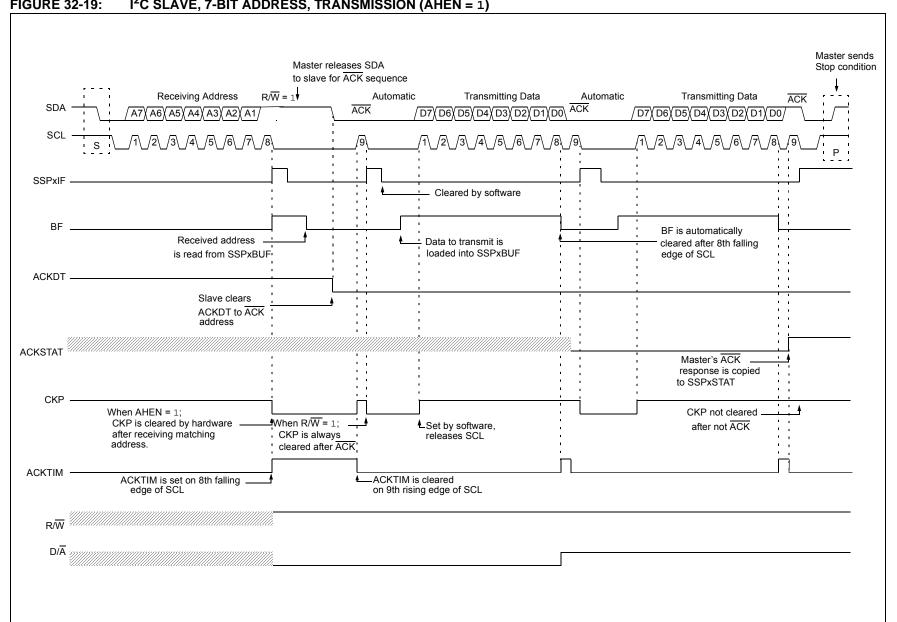

#### I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, TRANSMISSION (AHEN = 1) **FIGURE 32-19:**

## 32.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of  $\overline{ACK}$  is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCL low and SDA unchanged (Figure 32-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

## 32.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

## 32.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

## 32.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

32.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPx-CON2 register. Interrupt is generated once the Stop/Restart condition is complete.

# PIC16(L)F15356/75/76/85/86

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                 |

| Operands:        | None                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \mbox{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                    |

| Status Affected: | TO, PD                                                                                                                                                                                                                        |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is cleared. Time-out Status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>See <b>Section 11.2 "Sleep Mode"</b> for more information. |

| SUBWF            | Subtract W                                                                                                                                                                              | from f          |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| Syntax:          | [ <i>label</i> ] SL                                                                                                                                                                     | IBWF f,d        |  |  |

|                  | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                      |                 |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |                 |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                |                 |  |  |

| ·                | Subtract (2's complement method) '<br>register from register 'f'. If 'd' is '0', t<br>result is stored in the W<br>register. If 'd' is '1', the result is store<br>back in register 'f. |                 |  |  |

|                  | <b>C =</b> 0                                                                                                                                                                            | W > f           |  |  |

|                  | <b>C =</b> 1                                                                                                                                                                            | $W \leq f$      |  |  |

|                  | DC = 0                                                                                                                                                                                  | W<3:0> > f<3:0> |  |  |

$W<3:0> \le f<3:0>$

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                 |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                     |

| Status Affected: | C, DC, Z                                                                                                                                                                                          |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's<br>complement method). If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'. |

DC = 1

| SUBLW            | Subtract W from literal                                                                                                           |           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| Syntax:          | [label] SU                                                                                                                        | JBLW k    |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                 |           |  |  |  |

| Operation:       | $k - (W) \to (W)$                                                                                                                 |           |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                          |           |  |  |  |

| Description:     | The W register is subtracted (2's<br>complement method) from the 8-bit<br>literal 'k'. The result is placed in the W<br>register. |           |  |  |  |

|                  | <b>C</b> = 0                                                                                                                      | W > k     |  |  |  |

|                  | C = 1                                                                                                                             | $W \le k$ |  |  |  |

DC = 0

DC = 1

W<3:0> > k<3:0>

$W<3:0> \le k<3:0>$

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

## PIC16(L)F15356/75/76/85/86

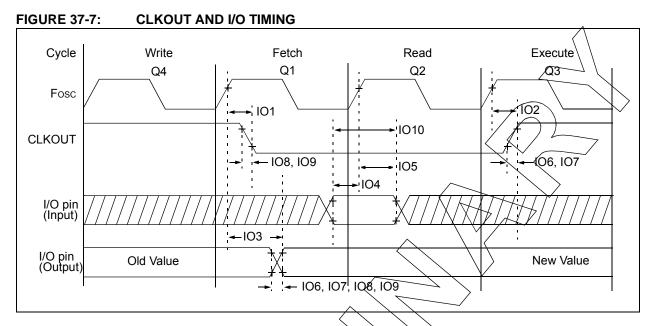

| TABLE 37-10: | I/O AND CLKOUT TIMING SPECIFICATIONS |

|--------------|--------------------------------------|

|--------------|--------------------------------------|

| Standar                                             | Standard Operating Conditions (unless otherwise stated) |                                                                                    |      |          |      |       |            |  |  |

|-----------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------|------|----------|------|-------|------------|--|--|

| Param.<br>No.                                       | Sym.                                                    | Characteristic                                                                     | Min. | Тур†     | Max. | Units | Conditions |  |  |

| IO1*                                                | T <sub>CLKOUTH</sub>                                    | CLKOUT rising edge delay (rising<br>edge Fosc (Q1 cycle) to falling edge<br>CLKOUT | > -  | —        | 70   | ns    |            |  |  |

| IO2*                                                | T <sub>CLKOUTL</sub>                                    | CLKOUT falling edge delay (rising<br>edge Fosc (Q3 cycle) to rising edge<br>CLKOUT | —    | _        | 72   | ns    |            |  |  |

| IO3*                                                | T <sub>IO_VALID</sub>                                   | Port output valid time (rising edge<br>Fose (Q1 cycle) to port valid)              | —    | 50       | 70   | ns    |            |  |  |

| 104*                                                | T <sub>IO_SETUP</sub>                                   | Port input setup time (Setup time<br>before rising edge Fosc – Q2 cycle)           | 20   | -        | —    | ns    |            |  |  |

| IO5*                                                | T <sub>IO_HOLD</sub>                                    | Port input hold time (Hold time after<br>rising edge Fosc – Q2 cycle)              | 50   | -        | —    | ns    |            |  |  |

| 106*                                                | TIOR_SLREN                                              | Port I/O rise time, slew rate enabled                                              | _    | 25       |      | ns    | VDD = 3.0V |  |  |

| 107*                                                | TIOR SLADIS                                             | Port I/O rise time, slew rate disabled                                             | _    | 5        |      | ns    | VDD = 3.0V |  |  |

| 108*                                                | FIOR SLREN                                              | Port I/O fall time, slew rate enabled                                              | _    | 25       |      | ns    | VDD = 3.0V |  |  |

| 109*/ /                                             | TIOF_SLRDIS                                             | Port I/O fall time, slew rate disabled                                             | _    | 5        |      | ns    | VDD = 3.0V |  |  |

|                                                     | FINT                                                    | INT pin high or low time to trigger an interrupt                                   | 25   | —        | —    | ns    |            |  |  |

| IO11*                                               | V.OC                                                    | Interrupt-on-Change minimum high or low time to trigger interrupt                  | 25   | <u> </u> |      | ns    |            |  |  |

| *These parameters are characterized but not tested. |                                                         |                                                                                    |      |          |      |       |            |  |  |