Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-UQFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15386t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

| I/O <sup>(2)</sup> | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO     | DAC | Timers | ССР  | MWM     | CWG            | ASSM                                           | ZCD | EUSART            | CLC     | CLKR | Interrupt | Pull-up | Basic |

|--------------------|------------------|------|-----------|------------|---------|-----|--------|------|---------|----------------|------------------------------------------------|-----|-------------------|---------|------|-----------|---------|-------|

| RF5                | 13               | ANF5 | —         |            | _       | _   |        | _    | _       | —              | _                                              |     | —                 | —       | —    | —         | Y       | —     |

| RF6                | 14               | ANF6 | —         | —          | —       | —   | -      | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | Y       | _     |

| RF7                | 15               | ANF7 | _         | _          | —       | _   |        | —    | —       | —              | -                                              | _   | —                 | —       | —    | —         | Y       | —     |

| VDD                | 30               | —    | —         | —          | —       | —   | -      | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | Y       | VDD   |

| VDD                | 7                | —    | —         | —          | —       | _   |        | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | —       | VDD   |

| Vss                | 6                | —    | _         |            | —       |     |        | _    | —       | —              |                                                |     | _                 | —       | —    | —         | —       | Vss   |

| Vss                | 31               | —    | —         | -          | —       | -   |        | —    | —       | —              | _                                              | -   | —                 | —       | —    | —         | —       | Vss   |

| OUT <sup>(2)</sup> | —                | —    | _         | C1OUT      | NCO10UT |     | TMR0   | CCP1 | PWM3OUT | CWG1A<br>CWG2A | SDO1<br>SDO2                                   |     | DT <sup>(3)</sup> | CLC1OUT | CLKR | —         | -       | —     |

|                    | —                | —    |           | C2OUT      | —       | _   |        | CCP2 | PWM4OUT | CWG1B<br>CWG2B | SCK1<br>SCK2                                   | -   | CK1<br>CK2        | CLC2OUT | -    | —         | -       | —     |

|                    | —                | -    | _         | _          | -       | _   | —      | _    | PWM5OUT | CWG1C<br>CWG2C | SCK1 <sup>(3,4)</sup><br>SCL2 <sup>(3,4)</sup> | _   | TX1<br>TX2        | CLC3OUT | _    | _         | -       | -     |

|                    | —                | _    | _         | _          | _       | —   | _      | _    | PWM6OUT | CWG1D<br>CWG2D | SDA1 <sup>(3,4)</sup><br>SDA2 <sup>(3,4)</sup> | _   | —                 | CLC4OUT | -    | _         | -       | -     |

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

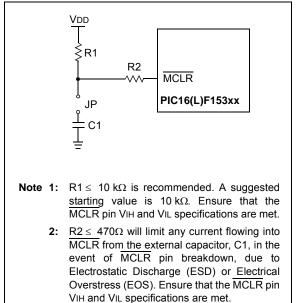

### 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

### 2.4 ICSP<sup>™</sup> Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 39.0 "Development Support"**.

| IADLE 4 | Bank 60               | ,     | Bank 61               |       | Bank 62               | - , - , | Bank 63 |

|---------|-----------------------|-------|-----------------------|-------|-----------------------|---------|---------|

| 1E0Ch   | _                     | 1E8Ch | RF7PPS <sup>(2)</sup> | 1F0Ch | _                     | 1F8Ch   | _       |

| 1E0Dh   | _                     | 1E8Dh | _                     | 1F0Dh | _                     | 1F8Dh   | _       |

| 1E0Eh   | _                     | 1E8Eh | _                     | 1F0Eh | _                     | 1F8Eh   | _       |

| 1E0Fh   | CLCDATA               | 1E8Fh | PPSLOCK               | 1F0Fh | _                     | 1F8Fh   | _       |

| 1E10h   | CLC1CON               | 1E90h | INTPPS                | 1F10h | RA0PPS                | 1F90h   | _       |

| 1E11h   | CLC1POL               | 1E91h | TOCKIPPS              | 1F11h | RA1PPS                | 1F91h   | _       |

| 1E12h   | CLC1SEL0              | 1E92h | T1CKIPPS              | 1F12h | RA2PPS                | 1F92h   | _       |

| 1E13h   | CLC1SEL1              | 1E93h | T1GPPS                | 1F13h | <b>RA3PPS</b>         | 1F93h   | _       |

| 1E14h   | CLC1SEL2              | 1E94h | _                     | 1F14h | RA4PPS                | 1F94h   | _       |

| 1E15h   | CLC1SEL3              | 1E95h |                       | 1F15h | RA5PPS                | 1F95h   |         |

| 1E16h   | CLC1GLS0              | 1E96h |                       | 1F16h | RA6PPS                | 1F96h   |         |

| 1E17h   | CLC1GLS1              | 1E97h |                       | 1F17h | RA7PPS                | 1F97h   | _       |

| 1E18h   | CLC1GLS2              | 1E98h |                       | 1F18h | RB0PPS                | 1F98h   | _       |

| 1E19h   | CLC1GLS3              | 1E99h | _                     | 1F19h | RB1PPS                | 1F99h   | _       |

| 1E1Ah   | CLC2CON               | 1E9Ah | _                     | 1F1Ah | RB2PPS                | 1F9Ah   | _       |

| 1E1Bh   | CLC2POL               | 1E9Bh | _                     | 1F1Bh | RB3PPS                | 1F9Bh   | —       |

| 1E1Ch   | CLC2SEL0              | 1E9Ch | T2INPPS               | 1F1Ch | RB4PPS                | 1F9Ch   | _       |

| 1E1Dh   | CLC2SEL1              | 1E9Dh | _                     | 1F1Dh | RB5PPS                | 1F9Dh   | _       |

| 1E1Eh   | CLC2SEL2              | 1E9Eh | _                     | 1F1Eh | RB6PPS                | 1F9Eh   | _       |

| 1E1Fh   | CLC2SEL3              | 1E9Fh | _                     | 1F1Fh | RB7PPS                | 1F9Fh   | _       |

| 1E20h   | CLC2GLS0              | 1EA0h | _                     | 1F20h | RC0PPS                | 1FA0h   | _       |

| 1E21h   | CLC2GLS1              | 1EA1h | CCP1PPS               | 1F21h | RC1PPS                | 1FA1h   | _       |

| 1E22h   | CLC2GLS2              | 1EA2h | CCP2PPS               | 1F22h | RC2PPS                | 1FA2h   | _       |

| 1E23h   | CLC2GLS3              | 1EA3h | _                     | 1F23h | RC3PPS                | 1FA3h   | _       |

| 1E24h   | CLC3CON               | 1EA4h | _                     | 1F24h | RC4PPS                | 1FA4h   | _       |

| 1E25h   | CLC3POL               | 1EA5h | —                     | 1F25h | RC5PPS                | 1FA5h   | —       |

| 1E26h   | CLC3SEL0              | 1EA6h | _                     | 1F26h | RC6PPS                | 1FA6h   | —       |

| 1E27h   | CLC3SEL1              | 1EA7h | _                     | 1F27h | RC7PPS                | 1FA7h   | —       |

| 1E28h   | CLC3SEL2              | 1EA8h | —                     | 1F28h | RD0PPS(1)             | 1FA8h   | —       |

| 1E29h   | CLC3SEL3              | 1EA9h | _                     | 1F29h | RD1PPS <sup>(1)</sup> | 1FA9h   | _       |

| 1E2Ah   | CLC3GLS0              | 1EAAh |                       | 1F2Ah | RD2PPS <sup>(1)</sup> | 1FAAh   | _       |

| 1E2Bh   | CLC3GLS1              | 1EABh |                       | 1F2Bh | RD3PPS <sup>(1)</sup> | 1FABh   | _       |

|         |                       |       |                       |       | RD4PPS <sup>(1)</sup> |         |         |

| 1E2Ch   | CLC3GLS2              | 1EACh |                       | 1F2Ch |                       | 1FACh   |         |

| 1E2Dh   | CLC3GLS3              | 1EADh | _                     | 1F2Dh | RD5PPS <sup>(1)</sup> | 1FADh   | _       |

| 1E2Eh   | CLC4CON               | 1EAEh | —                     | 1F2Eh | RD6PPS <sup>(1)</sup> | 1FAEh   | —       |

| 1E2Fh   | CLC4POL               | 1EAFh | _                     | 1F2Fh | RD7PPS <sup>(1)</sup> | 1FAFh   | _       |

| 1E30h   | CLC4SEL0              | 1EB0h |                       | 1F30h | RE0PPS <sup>(1)</sup> | 1FB0h   |         |

| 1E31h   | CLC4SEL1              | 1EB1h | CWG1PPS               | 1F31h | RE1PPS <sup>(1)</sup> | 1FB1h   | —       |

| 1E32h   | CLC4SEL2              | 1EB2h | _                     | 1F32h | RE2PPS <sup>(1)</sup> | 1FB2h   | _       |

| 1E33h   | CLC4SEL3              | 1EB3h | _                     | 1F33h | _                     | 1FB3h   | _       |

| 1E34h   | CLC4GLS0              | 1EB4h | _                     | 1F34h | _                     | 1FB4h   | _       |

| 1E35h   | CLC4GLS1              | 1EB5h |                       | 1F35h | _                     | 1FB5h   | _       |

| 1E36h   | CLC4GLS2              | 1EB6h |                       | 1F36h | _                     | 1FB6h   | _       |

| 1E37h   | CLC4GLS3              | 1EB7h |                       | 1F37h | _                     | 1FB7h   | _       |

| 1E38h   | RF0PPS(2)             | 1EB8h |                       | 1F38h | ANSELA                | 1FB8h   | _       |

| 1E39h   | RF1PPS <sup>(2)</sup> | 1EB9h |                       | 1F39h | WPUA                  | 1FB9h   | _       |

|         | RF2PPS <sup>(2)</sup> |       |                       |       |                       |         |         |

| 1E3Ah   |                       | 1EBAh |                       | 1F3Ah | ODCONA                | 1FBAh   |         |

| 1E3Bh   | RF3PPS <sup>(2)</sup> | 1EBBh | CLCIN0PPS             | 1F3Bh | SLRCONA               | 1FBBh   | _       |

| 1E3Ch   | RF4PPS <sup>(2)</sup> | 1EBCh | CLCIN1PPS             | 1F3Ch | INLVLA                | 1FBCh   | —       |

| 1E3Dh   | RF5PPS <sup>(2)</sup> | 1EBDh | CLCIN2PPS             | 1F3Dh | IOCAP                 | 1FBDh   | _       |

| 1E3Eh   | RF6PPS <sup>(2)</sup> | 1EBEh | <b>CLCIN3PPS</b>      | 1F3Eh | IOCAN                 | 1FBEh   | —       |

### TABLE 4-9: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANKS 60, 61, 62, AND 63

Legend: = Unimplemented data memory locations, read as '0'

Note 1: Present only on PIC16(L)F15375/76/85/86.

2: Present only on PIC16(L)F15385/86

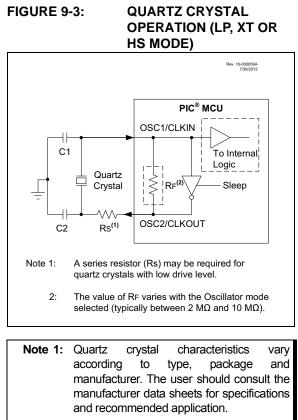

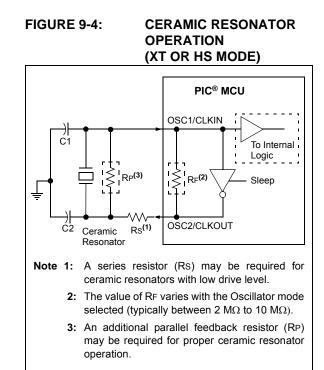

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

### 9.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR), Brown-out Reset (BOR) or a wake-up from Sleep. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

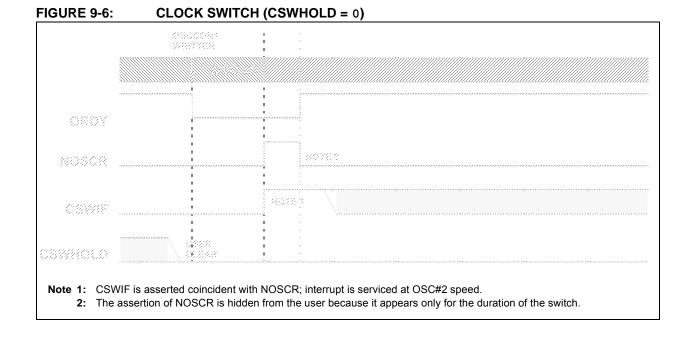

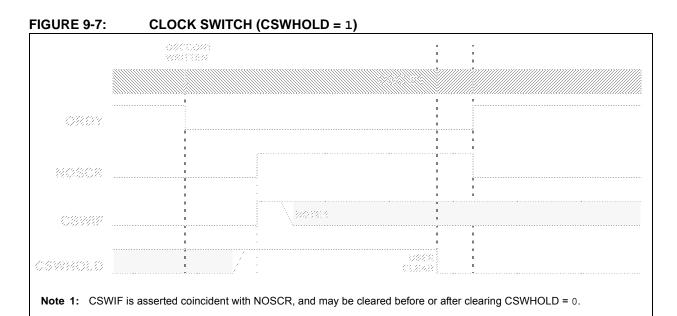

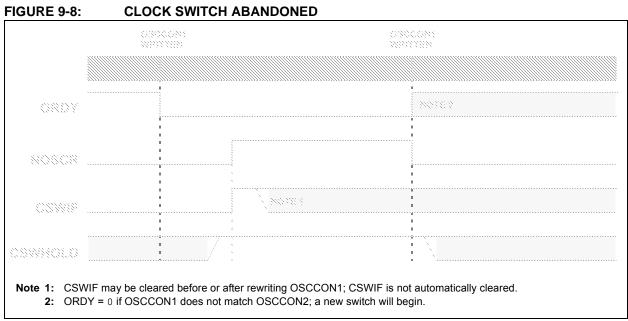

Changing the clock post-divider without changing the clock source (e.g., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

### 9.3.2 PLL INPUT SWITCH

Switching between the PLL and any non-PLL source is managed as described above. The input to the PLL is established when NOSC selects the PLL, and maintained by the COSC setting.

When NOSC and COSC select the PLL with different input sources, the system continues to run using the COSC setting, and the new source is enabled per NOSC. When the new oscillator is ready (and CSWHOLD = 0), system operation is suspended while the PLL input is switched and the PLL acquires lock.

Note: If the PLL fails to lock, the FSCM will trigger.

### 9.3.3 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

© 2016 Microchip Technology Inc.

DS40001866A-page 133

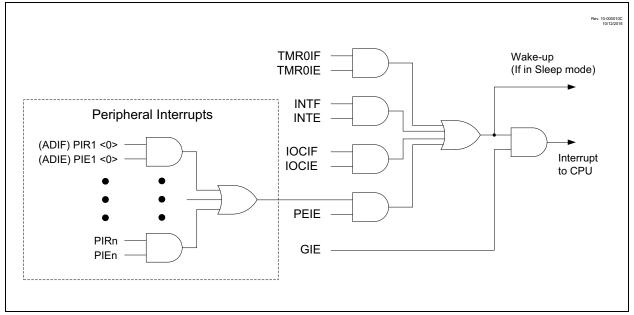

## **10.0 INTERRUPTS**

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 10-1.

### FIGURE 10-1: INTERRUPT LOGIC

### 12.1 Independent Clock Source

The WDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of either the WDTCCS<2:0> Configuration bits or the WDTCS<2:0> bits of WDTCON1. Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section 37.0 "Electrical Specifications"** for LFINTOSC and MFINTOSC tolerances.

### 12.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 12-1.

### 12.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

### 12.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### 12.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON0 register.

### 12.2.4 WDT IS OFF

When the WDTE bits of the Configuration Word are set to '00', the WDT is always OFF.

WDT protection is unchanged by Sleep. See Table 12-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 10        | 37     | Awake          | Active      |

| TO        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | Х              | Active      |

| 01        | 0      | Х              | Disabled    |

| 00        | х      | Х              | Disabled    |

### TABLE 12-1: WDT OPERATING MODES

### 12.3 Time-Out Period

The WDTPS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

### 12.4 Watchdog Window

The Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WDT Reset, similar to a WDT time out. See Figure 12-2 for an example.

The window size is controlled by the WDTCWS<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

In the event of a <u>window</u> violation, a Reset will be generated and the WDTWV bit of the PCON register will be cleared. This bit is set by a POR or can be set in firmware.

### 12.5 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1 registers

### 12.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation.

See Table 12-2 for more information.

### 12.6 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See Section 4.3.2.1 "STATUS Register" for more information.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 211                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 211                 |

| LATC    | LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 211                 |

| ANSELC  | ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 212                 |

| WPUC    | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 212                 |

| ODCONC  | ODCC7   | ODCC6   | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   | 213                 |

| SLRCONC | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 213                 |

| INLVLC  | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 213                 |

### TABLE 14-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

| REGISTER         | 16-2: PMD                                                                                       | 1: PMD CON                                                              | TROL REGI    | STER 1         |                                |                  |              |  |  |

|------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------|----------------|--------------------------------|------------------|--------------|--|--|

| R/W-0/0          | U-0                                                                                             | U-0                                                                     | U-0          | U-0            | R/W-0/0                        | R/W-0/0          | R/W-0/0      |  |  |

| NCO1MD           |                                                                                                 | —                                                                       |              | —              | TMR2MD                         | TMR1MD           | TMR0MD       |  |  |

| bit 7            |                                                                                                 |                                                                         |              |                |                                |                  | bit 0        |  |  |

| r                |                                                                                                 |                                                                         |              |                |                                |                  |              |  |  |

| Legend:          |                                                                                                 |                                                                         |              |                |                                |                  |              |  |  |

| R = Readab       | le bit                                                                                          | W = Writable                                                            | bit          | U = Unimplem   | nented bit, read               | l as '0'         |              |  |  |

| u = Bit is un    | changed                                                                                         | x = Bit is unkr                                                         | nown         | -n/n = Value a | t POR and BO                   | R/Value at all o | other Resets |  |  |

| '1' = Bit is se  | et                                                                                              | '0' = Bit is cle                                                        | ared         | q = Value dep  | q = Value depends on condition |                  |              |  |  |

| bit 7<br>bit 6-3 | 1 = NCO1 m<br>0 = NCO1 m                                                                        | isable Numerica<br>nodule disabled<br>nodule enabled<br>nted: Read as ' |              | scillator bit  |                                |                  |              |  |  |

| bit 2            | <b>TMR2MD:</b> D<br>1 = Timer2 r                                                                | isable Timer TM<br>nodule disablec<br>nodule enabled                    | 1R2 bit<br>I |                |                                |                  |              |  |  |

| bit 1            | bit 1 TMR1MD: Disable Timer TMR1 bit<br>1 = Timer1 module disabled<br>0 = Timer1 module enabled |                                                                         |              |                |                                |                  |              |  |  |

| bit 0            | 1 = Timer0 r                                                                                    | isable Timer TM<br>nodule disablec<br>nodule enabled                    | 1            |                |                                |                  |              |  |  |

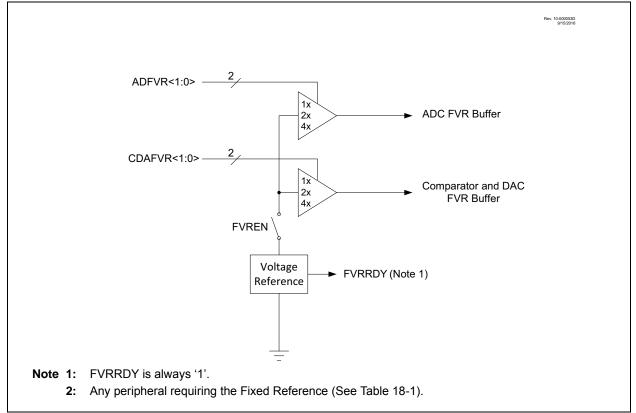

### 18.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · ADC positive reference

- · Comparator positive and negative input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

### 18.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 20.0 "Analog-to-Digital Converter (ADC) Module"** for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" and Section 23.0 "Comparator Module" for additional information.

### 18.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize.

FVRRDY is an indicator of the reference being ready. In the case of an LF device, or a device on which the BOR is enabled in the Configuration Word settings, then the FVRRDY bit will be high prior to setting FVREN as those module require the reference voltage.

FIGURE 18-1: VOLTAGE REFERENCE BLOCK DIAGRAM

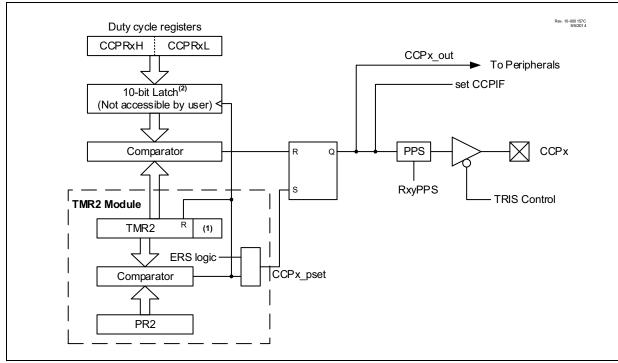

### FIGURE 28-4: SIMPLIFIED PWM BLOCK DIAGRAM

### 28.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the CCPxFMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note below.

- Configure the CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the Timer2 ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

- Note: In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

### 28.3.3 CCP/PWM CLOCK SELECTION

The PIC16(L)F15356/75/76/85/86 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

| R/W-x/u          | R/W-x/u     | R/W-x/u                               | R/W-x/u                                                                      | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |  |  |

|------------------|-------------|---------------------------------------|------------------------------------------------------------------------------|----------------|------------------|------------------|--------------|--|--|--|

| LCxG4D4T         | LCxG4D4N    | LCxG4D3T                              | LCxG4D3N                                                                     | LCxG4D2T       | LCxG4D2N         | LCxG4D1T         | LCxG4D1N     |  |  |  |

| bit 7            | ·           |                                       |                                                                              |                |                  |                  | bit 0        |  |  |  |

|                  |             |                                       |                                                                              |                |                  |                  |              |  |  |  |

| Legend:          |             |                                       |                                                                              |                |                  |                  |              |  |  |  |

| R = Readable     |             | W = Writable                          |                                                                              | •              | mented bit, read |                  |              |  |  |  |

| u = Bit is unch  | anged       | x = Bit is unki                       |                                                                              | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set |             | '0' = Bit is cle                      | ared                                                                         |                |                  |                  |              |  |  |  |

| hit 7            |             | Cata 2 Data 4 1                       | Frue (nen inve                                                               | rtad) bit      |                  |                  |              |  |  |  |

| bit 7            |             | Gate 3 Data 4 1<br>(true) is gated i  | •                                                                            | ,              |                  |                  |              |  |  |  |

|                  |             | (true) is gated<br>(true) is not ga   |                                                                              |                |                  |                  |              |  |  |  |

| bit 6            |             | Gate 3 Data 4                         |                                                                              |                |                  |                  |              |  |  |  |

|                  |             | (inverted) is ga                      | •                                                                            | ,              |                  |                  |              |  |  |  |

|                  |             | (inverted) is no                      |                                                                              |                |                  |                  |              |  |  |  |

| bit 5            | LCxG4D3T: ( | Gate 3 Data 3                         | True (non-inve                                                               | rted) bit      |                  |                  |              |  |  |  |

|                  |             | (true) is gated                       |                                                                              |                |                  |                  |              |  |  |  |

|                  | 0 = CLCIN2  | (true) is not ga                      | ted into CLCx                                                                | Gate 3         |                  |                  |              |  |  |  |

| bit 4            |             | Gate 3 Data 3                         | •                                                                            | ,              |                  |                  |              |  |  |  |

|                  |             |                                       | nverted) is gated into CLCx Gate 3<br>nverted) is not gated into CLCx Gate 3 |                |                  |                  |              |  |  |  |

|                  |             | ,                                     | 0                                                                            |                |                  |                  |              |  |  |  |

| bit 3            |             | Gate 3 Data 2                         | ,                                                                            |                |                  |                  |              |  |  |  |

|                  |             | (true) is gated i<br>(true) is not ga |                                                                              |                |                  |                  |              |  |  |  |

| bit 2            |             | Gate 3 Data 2                         |                                                                              |                |                  |                  |              |  |  |  |

| DIL Z            |             | (inverted) is ga                      | •                                                                            |                |                  |                  |              |  |  |  |

|                  |             | (inverted) is ga                      |                                                                              |                |                  |                  |              |  |  |  |

| bit 1            |             | Gate 4 Data 1 ∃                       | •                                                                            |                |                  |                  |              |  |  |  |

|                  |             | (true) is gated                       | ·                                                                            |                |                  |                  |              |  |  |  |

|                  | 0 = CLCIN0  | (true) is not ga                      | ted into CLCx                                                                | Gate 3         |                  |                  |              |  |  |  |

| bit 0            | LCxG4D1N:   | Gate 3 Data 1                         | Negated (inve                                                                | rted) bit      |                  |                  |              |  |  |  |

|                  |             | (inverted) is ga                      |                                                                              |                |                  |                  |              |  |  |  |

|                  | 0 = CLCIN0  | (inverted) is no                      | t gated into Cl                                                              | _Cx Gate 3     |                  |                  |              |  |  |  |

### REGISTER 31-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

### 33.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 33-3 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

### 33.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 33-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

### 33.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

### 33.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

### 33.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 33.4.1.2 "Clock Polarity"**.

### 33.1.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE3 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

### 33.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXxSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

### 33.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 33.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode.

If two words are written to the TXxREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXxREG register.

- 3. The TXxIF bit will not be set.

- After the first character has been shifted out of TSR, the TXxREG register will transfer the second character to the TSR and the TXxIF bit will now be set.

- 5. If the PEIE and TXxIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 33.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- 4. If interrupts are desired, set the TXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXxREG register.

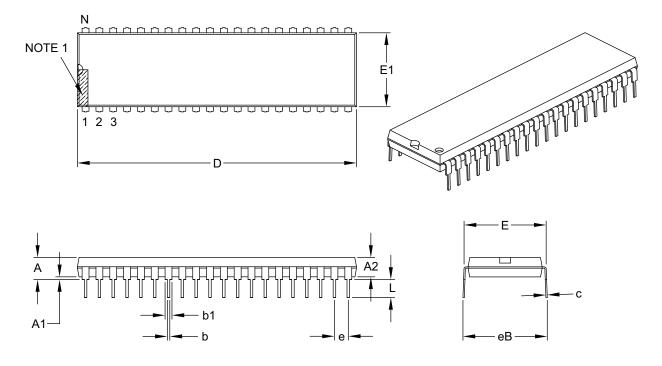

### 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES |          |       |  |

|----------------------------|----------|--------|----------|-------|--|

| Dimension                  | n Limits | MIN    | NOM      | MAX   |  |

| Number of Pins             | Ν        |        | 40       |       |  |

| Pitch                      | е        |        | .100 BSC |       |  |

| Top to Seating Plane       | А        | -      | -        | .250  |  |

| Molded Package Thickness   | A2       | .125   | -        | .195  |  |

| Base to Seating Plane      | A1       | .015   | -        | —     |  |

| Shoulder to Shoulder Width | Е        | .590   | -        | .625  |  |

| Molded Package Width       | E1       | .485   | -        | .580  |  |

| Overall Length             | D        | 1.980  | -        | 2.095 |  |

| Tip to Seating Plane       | L        | .115   | _        | .200  |  |

| Lead Thickness             | С        | .008   | _        | .015  |  |

| Upper Lead Width           | b1       | .030   | _        | .070  |  |

| Lower Lead Width           | b        | .014   | _        | .023  |  |

| Overall Row Spacing §      | eB       | -      | _        | .700  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

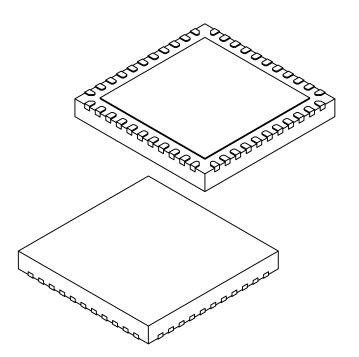

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS           |      |          |      |  |  |

|-------------------------|-----------------------|------|----------|------|--|--|

| Dimension               | Dimension Limits      |      |          |      |  |  |

| Number of Pins          | N                     |      | 44       |      |  |  |

| Pitch                   | е                     |      | 0.65 BSC |      |  |  |

| Overall Height          | Α                     | 0.80 | 0.90     | 1.00 |  |  |

| Standoff                | A1                    | 0.00 | 0.02     | 0.05 |  |  |

| Terminal Thickness      | Thickness A3 0.20 REF |      |          |      |  |  |

| Overall Width           | E                     |      | 8.00 BSC |      |  |  |

| Exposed Pad Width       | E2                    | 6.25 | 6.45     | 6.60 |  |  |

| Overall Length          | D                     |      | 8.00 BSC |      |  |  |

| Exposed Pad Length      | D2                    | 6.25 | 6.45     | 6.60 |  |  |

| Terminal Width          | b                     | 0.20 | 0.30     | 0.35 |  |  |

| Terminal Length         | L                     | 0.30 | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | К                     | 0.20 | -        | -    |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103D Sheet 2 of 2