Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-TQFP                                                                     |

| Supplier Device Package    | 48-TQFP (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15386t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                    | Function              | Input<br>Type | Output Type | Description                                       |

|---------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------|

| RA0/ANA0/C1IN0-/C2IN0-/CLCIN0 <sup>(1)</sup> /<br>IOCA0 | RA0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IUCAU                                                   | ANA0                  | AN            | _           | ADC Channel A0 input.                             |

|                                                         | C1IN0-                | AN            | _           | Comparator 1 negative input.                      |

|                                                         | C2IN0-                | AN            | _           | Comparator 2 negative input.                      |

|                                                         | CLCIN0 <sup>(1)</sup> | TTL/ST        |             | Configurable Logic Cell source input.             |

|                                                         | IOCA0                 | TTL/ST        | -           | Interrupt-on-change input.                        |

| RA1/ANA1/C1IN1-/C2IN1-/CLCIN1 <sup>(1)</sup> /<br>IOCA1 | RA1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IOCAT                                                   | ANA1                  | AN            |             | ADC Channel A1 input.                             |

|                                                         | C1IN1-                | AN            |             | Comparator 1 negative input.                      |

|                                                         | C2IN1-                | AN            |             | Comparator 2 negative input.                      |

|                                                         | CLCIN1 <sup>(1)</sup> | TTL/ST        |             | Configurable Logic Cell source input.             |

|                                                         | IOCA1                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA2/ANA2/C1IN0+/C2IN0+/<br>DAC1OUT1/IOCA2               | RA2                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| DACTOUTINOCAZ                                           | ANA2                  | AN            | _           | ADC Channel A2 input.                             |

|                                                         | C1IN0+                | AN            | -           | Comparator 2 positive input.                      |

|                                                         | C2IN0+                | AN            | _           | Comparator 2 positive input.                      |

|                                                         | DAC1OUT1              | _             | AN          | Digital-to-Analog Converter output.               |

|                                                         | IOCA2                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA3/ANA3/C1IN1+/VREF+/IOCA3/<br>DAC1REF+                | RA3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| DACIREFT                                                | ANA3                  | AN            | _           | ADC Channel A3 input.                             |

|                                                         | C1IN1+                | AN            | _           | Comparator 1 positive input.                      |

|                                                         | VREF+                 | AN            | _           | External ADC and/or DAC positive reference input. |

|                                                         | IOCA3                 | TTL/ST        | _           | Interrupt-on-change input.                        |

|                                                         | DAC1REF+              | TTL/ST        | AN          | DAC positive reference.                           |

| RA4/ANA4/T0CKI <sup>(1)</sup> /IOCA4                    | RA4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA4                  | AN            | -           | ADC Channel A4 input.                             |

|                                                         | T0CKI <sup>(1)</sup>  | TTL/ST        | _           | Timer0 clock input.                               |

|                                                         | IOCA4                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA5/ANA5/SS1 <sup>(1)</sup> /IOCA5                      | RA5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA5                  | AN            | _           | ADC Channel A5 input.                             |

|                                                         | SS1 <sup>(1)</sup>    | TTL/ST        | _           | MSSP1 SPI slave select input.                     |

|                                                         | IOCA5                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| <b>TABLE 1-2:</b> | PIC16(L)F15356 PINOUT DESCRIPTION |

|-------------------|-----------------------------------|

|-------------------|-----------------------------------|

CMOS = CMOS compatible input or output Legend: AN = Analog input or output OD = Open-Drain I<sup>2</sup>C TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx 1: pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for  $I^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the  $I^2C$  specific or SMBus input buffer thresholds. 4:

Note

| Name                                                   | Function              | Input<br>Type | Output Type | Description                                       |

|--------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------|

| RA0/ANA0/C1IN0-/C2IN0-/CLCIN0 <sup>(1)</sup> /         | RA0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IOCA0                                                  | ANA0                  | AN            | _           | ADC Channel A0 input.                             |

|                                                        | C1IN0-                | AN            | _           | Comparator negative input.                        |

|                                                        | C2IN0-                | AN            | _           | Comparator negative input.                        |

|                                                        | CLCIN0 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.             |

|                                                        | IOCA0                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA1/ANA1/C1IN1-/C2IN1-/CLCIN1 <sup>(1)</sup> /<br>OCA1 | RA1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| UCAT                                                   | ANA1                  | AN            | _           | ADC Channel A1 input.                             |

|                                                        | C1IN1-                | AN            | —           | Comparator negative input.                        |

|                                                        | C2IN1-                | AN            | _           | Comparator negative input.                        |

|                                                        | CLCIN1 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.             |

|                                                        | IOCA1                 | TTL/ST        | —           | Interrupt-on-change input.                        |

| RA2/ANA2/C1IN0+/C2IN0+/<br>DAC1OUT1/IOCA2              | RA2                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| JACTOUTINOCAZ                                          | ANA2                  | AN            | _           | ADC Channel A2 input.                             |

|                                                        | C1IN0+                | AN            | —           | Comparator positive input.                        |

|                                                        | C2IN0+                | AN            | —           | Comparator positive input.                        |

|                                                        | DAC10UT1              | —             | AN          | Digital-to-Analog Converter output.               |

|                                                        | IOCA2                 | TTL/ST        | —           | Interrupt-on-change input.                        |

| RA3/ANA3/C1IN1+/VREF+/DACREF+/<br>OCA3                 | RA3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| OCAS                                                   | ANA3                  | AN            | —           | ADC Channel A3 input.                             |

|                                                        | C1IN1+                | AN            | —           | Comparator positive input.                        |

|                                                        | VREF+                 | AN            | —           | External ADC and/or DAC positive reference input. |

|                                                        | IOCA3                 | TTL/ST        | —           | Interrupt-on-change input.                        |

| RA4/ANA4/C1IN1-/T0CKI <sup>(1)</sup> /IOCA4            | RA4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                        | ANA4                  | AN            | —           | ADC Channel A4 input.                             |

|                                                        | C1IN1-                | AN            | _           | Comparator negative input.                        |

|                                                        | T0CKI <sup>(1)</sup>  | TTL/ST        | _           | Timer0 clock input.                               |

|                                                        | IOCA4                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA5/ANA5/SS1 <sup>(1)</sup> /T1G <sup>(1)</sup> /IOCA5 | RA5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                        | ANA5                  | AN            | —           | ADC Channel A5 input.                             |

|                                                        | SS1 <sup>(1)</sup>    | TTL/ST        | —           | MSSP1 SPI slave select input.                     |

|                                                        | T1G <sup>(1)</sup>    | TTL/ST        | —           | Timer1 gate input.                                |

|                                                        | IOCA5                 | TTL/ST        | _           | Interrupt-on-change input.                        |

#### **TABLE 1-4:** PIC16(L)F15385/86 PINOUT DESCRIPTION

TTL = TTL compatible input HV = High Voltage

XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-7. 2:

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

#### 4.3.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains:

- the arithmetic status of the ALU

- the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

# For example, CLRF STATUS will clear bits <4:3> and <1:0>, and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, refer to **Section 36.0** "Instruction Set Summary".

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

## REGISTER 4-1: STATUS: STATUS REGISTER

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| —     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                                                                     |

|         | <ul> <li>1 = After power-up, CLRWDT instruction or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                                                                                                 |

| bit 3   | PD: Power-Down bit                                                                                                                                                                                                   |

|         | 1 = After power-up or by the CLRWDT instruction                                                                                                                                                                      |

|         | 0 = By execution of the SLEEP instruction                                                                                                                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | 1 = The result of an arithmetic or logic operation is zero                                                                                                                                                           |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                       |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                                                                                                                    |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                                                                                                                            |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                          |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                                                                                 |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

| TABLE 4          | ABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |         |                     |                    |          |        |           |           |           |                       |                            |

|------------------|---------------------------------------------------------------------|---------|---------------------|--------------------|----------|--------|-----------|-----------|-----------|-----------------------|----------------------------|

| Address          | Name                                                                | Bit 7   | Bit 6               | Bit 5              | Bit 4    | Bit 3  | Bit 2     | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 17          | ank 17                                                              |         |                     |                    |          |        |           |           |           |                       |                            |

|                  | CPU CORE REGISTERS; see Table 4-3 for specifics                     |         |                     |                    |          |        |           |           |           |                       |                            |

| 88Ch             | CPUDOZE                                                             | IDLEN   | DOZEN               | ROI                | DOE      | _      | DOZE2     | DOZE1     | DOZE0     | 0000 -000             | u000 -000                  |

| 88Dh             | OSCCON1                                                             | —       | NOSC<2:0> NDIV<3:0> |                    |          |        |           |           | -qqq 0000 | -qqq 0000             |                            |

| 88Eh             | OSCCON2                                                             | —       |                     | COSC<2:0>          |          |        | CDIV<3:0> |           |           |                       | -বর্বর বর্ববর              |

| 88Fh             | OSCCON3                                                             | CSWHOLD | SOSCPWR             | _                  | ORDY     | NOSCR  | —         | —         | —         | 00-0 0                | 00-0 0                     |

| 890h             | OSCSTAT                                                             | EXTOR   | HFOR                | MFOR               | LFOR     | SOR    | ADOR      | —         | PLLR      | d000 dd-0             | বর্ববুর বর-ব               |

| 891h             | OSCEN                                                               | EXTOEN  | HFOEN               | MFOEN              | LFOEN    | SOSCEN | ADOEN     | —         | —         | 0000 00               | 0000 00                    |

| 892h             | OSCTUNE                                                             | —       | -                   |                    |          | HFT    | UN<5:0>   |           |           | 10 0000               | 10 0000                    |

| 893h             | OSCFRQ                                                              | —       | -                   | _                  | _        | —      |           | HFFRQ<2:0 | >         | वेर्वेवे              | ddd                        |

| 894h             | —                                                                   |         |                     |                    | Unimpler | nented |           |           |           | —                     | —                          |

| 895h             | CLKRCON                                                             | CLKREN  | -                   | _                  |          |        |           |           |           | 0x xxxx               | 0u uuuu                    |

| 896h             | CLKRCLK                                                             | —       | _                   | — — — CLKRCLK<3:0> |          |        |           |           | 0000      | 0000                  |                            |

| 897h<br><br>89Fh |                                                                     |         |                     |                    |          |        | -         | _         |           |                       |                            |

## TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

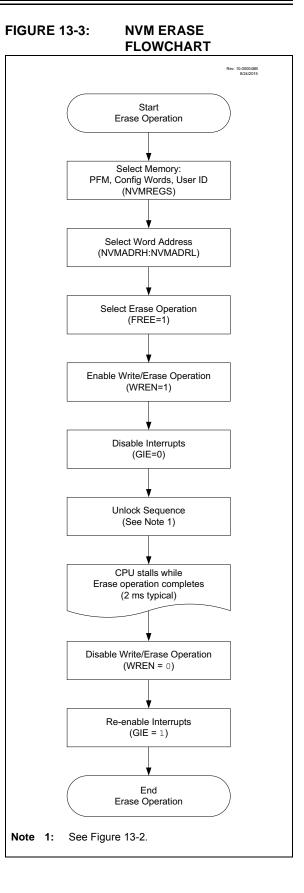

### 13.3.3 NVMREG ERASE OF PFM

Before writing to PFM, the word(s) to be written must be erased or previously unwritten. PFM can only be erased one row at a time. No automatic erase occurs upon the initiation of the write to PFM.

To erase a PFM row:

- Clear the NVMREGS bit of the NVMCON1 register to erase PFM locations, or set the NMVREGS bit to erase User ID locations.

- 2. Write the desired address into the NVMADRH:NVMADRL register pair (Table 13-2).

- 3. Set the FREE and WREN bits of the NVMCON1 register.

- 4. Perform the unlock sequence as described in Section 13.3.2 "NVM Unlock Sequence".

If the PFM address is write-protected, the WR bit will be cleared and the erase operation will not take place.

While erasing PFM, CPU operation is suspended, and resumes when the operation is complete. Upon completion, the NVMIF is set, and an interrupt will occur if the NVMIE bit is also set.

Write latch data is not affected by erase operations, and WREN will remain unchanged.

## 14.5 Register Definitions: PORTB

### **REGISTER 14-9: PORTB: PORTB REGISTER**

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     |

| bit 7   |         |         | •       |         |         | •       | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| •                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **RB<7:0>**: PORTB I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

## REGISTER 14-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISB<7:0>: PORTB Tri-State Control bit

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. The actual I/O pin values are read from the PORTB register.

|                      |                        | Default     | Reset Value<br>(xxxPPS<4:0>) | Remappable to Pins of PORTx<br>PIC16(L)F15375/76 |       |       |       |  |

|----------------------|------------------------|-------------|------------------------------|--------------------------------------------------|-------|-------|-------|--|

| INPUT SIGNAL<br>NAME | Input Register<br>Name | Location at |                              |                                                  |       |       |       |  |

|                      | Numo                   | POR         |                              | PORTA                                            | PORTB | PORTC | PORTD |  |

| INT                  | INTPPS                 | RB0         | 01000                        | ٠                                                | •     |       |       |  |

| TOCKI                | T0CKIPPS               | RA4         | 00100                        | ٠                                                | •     |       |       |  |

| T1CKI                | T1CKIPSS               | RC0         | 10000                        | ٠                                                |       | •     |       |  |

| T1G                  | T1GPPS                 | RB5         | 01101                        |                                                  | •     | •     |       |  |

| T2IN                 | T2INPPS                | RC3         | 10011                        | ٠                                                |       | •     |       |  |

| CCP1                 | CCP1PPS                | RC2         | 10010                        |                                                  | •     | •     |       |  |

| CCP2                 | CCP2PPS                | RC1         | 10001                        |                                                  | •     | •     |       |  |

| CWG1IN               | CWG1INPPS              | RB0         | 01000                        |                                                  | •     |       | •     |  |

| CLCIN0               | CLCIN0PPS              | RA0         | 00000                        | ٠                                                |       | •     |       |  |

| CLCIN1               | CLCIN1PPS              | RA1         | 00001                        | ٠                                                |       | •     |       |  |

| CLCIN2               | CLCIN2PPS              | RB6         | 01110                        |                                                  | •     |       | •     |  |

| CLCIN3               | CLCIN3PPS              | RB7         | 01111                        |                                                  | •     |       | •     |  |

| ADACT                | ADACTPPS               | RB4         | 01100                        |                                                  | •     |       | •     |  |

| SCK1/SCL1            | SSP1CLKPPS             | RC3         | 10011                        |                                                  | •     | •     |       |  |

| SDI1/SDA1            | SSP1DATPPS             | RC4         | 10100                        |                                                  | •     | •     |       |  |

| SS1                  | SSP1SS1PPS             | RA5         | 00101                        | ٠                                                |       |       | •     |  |

| SCK2/SCL2            | SSP2CLKPPS             | RB1         | 01001                        |                                                  | •     |       | •     |  |

| SDI2/SDA2            | SSP2DATPPS             | RB2         | 01010                        |                                                  | •     |       | •     |  |

| SS2                  | SSP2SSPPS              | RB0         | 01000                        |                                                  | •     |       | •     |  |

| RX1/DT1              | RX1PPS                 | RC7         | 10111                        |                                                  | •     | •     |       |  |

| CK1                  | TX1PPS                 | RC6         | 10110                        |                                                  | •     | •     |       |  |

| RX2/DT2              | RX2PPS                 | RB7         | 01111                        |                                                  | •     |       | •     |  |

| CK2                  | TX2PPS                 | RB6         | 01110                        |                                                  | •     |       | •     |  |

## TABLE 15-2: PPS INPUT SIGNAL ROUTING OPTIONS (PIC16(L)F15375/76)

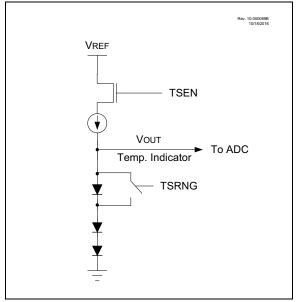

## 19.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The main purpose of the temperature indicator module is to provide a temperature-dependent voltage that can be measured by the Analog-to-Digital Converter.

The circuit's range of operating temperature falls between -40°C and +125°C. The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately.

## **19.1 Module Operation**

The temperature indicator module consists of a temperature-sensing circuit that provides a voltage to the device ADC. The analog voltage output, VTSENSE, varies inversely to the device temperature. The output of the temperature indicator is referred to as VOUT.

Figure 19-1 shows a simplified block diagram of the temperature indicator module.

#### FIGURE 19-1: TEMPERATURE INDICATOR BLOCK DIAGRAM

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 20.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

The ON/OFF bit for the module is located in the FVRCON register. See **Section 18.0** "**Fixed Voltage Reference (FVR)**" for more information. The circuit is enabled by setting the TSEN bit of the FVRCON register. When the module is disabled, the circuit draws no current.

The circuit operates in either High or Low range. Refer to **Section 19.5** "**Temperature Indicator Range**" for more details on the range settings.

## 19.2 Estimation of Temperature

This section describes how the sensor voltage can be used to estimate the temperature of the module. To use the sensor, the output voltage, VTSENSE, is measured and the corresponding temperature is determined. Equation 19-1 provides an estimate for the die temperature based on the VTSENSE value.

## EQUATION 19-1: SENSOR TEMPERATURE

$$T_{SENSE} = V_{TSENSE} \times (-Mt) + T_{OFFSET}$$

Where:

Mt = 1/Mv, where Mv = sensor voltage sensitivity (V/°C). TOFFSET is the temperature difference between the theoretical temperature and the actual temperature.

## 20.4 Register Definitions: ADC Control

#### REGISTER 20-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0    | R/W-0/0               | R/W-0/0         | R/W-0/0             | R/W-0/0                               | R/W-0/0 | R/W-0/0 |

|------------------|------------|-----------------------|-----------------|---------------------|---------------------------------------|---------|---------|

|                  |            | CHS<                  | 5:0>            |                     |                                       | GO/DONE | ADON    |

| bit 7            |            |                       |                 |                     |                                       |         | bit (   |

|                  |            |                       |                 |                     |                                       |         |         |

| Legend:          |            |                       |                 |                     |                                       |         |         |

| R = Readable b   | bit        | W = Writable bit      |                 | U = Unimplemer      | nted bit, read as                     | ʻ0'     |         |

| u = Bit is uncha | nged       | x = Bit is unknow     | vn              | -n/n = Value at F   | sets                                  |         |         |

| '1' = Bit is set |            | '0' = Bit is cleare   | d               |                     |                                       |         |         |

|                  |            |                       |                 |                     |                                       |         |         |

| bit 7-2          |            | Analog Channel Selec  |                 |                     |                                       |         |         |

|                  | 111111 =   | FVR Buffer 2 referen  | nce voltage (2) |                     |                                       |         |         |

|                  | 111110 =   | FVR 1Buffer 1 refere  | -(1)            |                     |                                       |         |         |

|                  | 111101 =   | DAC1 output voltage   |                 |                     |                                       |         |         |

|                  | 111100 =   | Temperature sensor    |                 |                     |                                       |         |         |

|                  | 111011 =   | AVss (Analog Grour    | ,               |                     |                                       |         |         |

|                  | 111010-100 | 0000 = Reserved. No   | channel conne   | cted                |                                       |         |         |

|                  | 101111 =   | RF7                   |                 |                     |                                       |         |         |

|                  | 101110 =   | RF6                   |                 |                     |                                       |         |         |

|                  | 101101 =   | RF5                   |                 |                     |                                       |         |         |

|                  | 101100 =   | RF4                   |                 |                     |                                       |         |         |

|                  | 101011 =   | RF3                   |                 |                     |                                       |         |         |

|                  | 101010 =   | RF2                   |                 |                     |                                       |         |         |

|                  | 101001 =   | RF1                   |                 |                     |                                       |         |         |

|                  | 101000 =   | RF0                   |                 |                     |                                       |         |         |

|                  | 100010 =   | RE2                   |                 |                     |                                       |         |         |

|                  | 100001 =   | RE1                   |                 |                     |                                       |         |         |

|                  |            |                       |                 |                     |                                       |         |         |

|                  | 100000 =   | RE0                   |                 |                     |                                       |         |         |

|                  | 011111 =   | RD7                   |                 |                     |                                       |         |         |

|                  | 011110 =   | RD6                   |                 |                     |                                       |         |         |

|                  | 011101 =   | RD5                   |                 |                     |                                       |         |         |

|                  | 011100 =   | RD4                   |                 |                     |                                       |         |         |

|                  | 011011 =   | RD3                   |                 |                     |                                       |         |         |

|                  | 011010 =   | RD2                   |                 |                     |                                       |         |         |

|                  | 011001 =   | RD1                   |                 |                     |                                       |         |         |

|                  | 011000 =   | RD0                   |                 |                     |                                       |         |         |

|                  | 010111 =   | RC7 <sup>(4)</sup>    |                 |                     |                                       |         |         |

|                  |            | RC6 <sup>(4)</sup>    |                 |                     |                                       |         |         |

|                  | 010110 =   |                       |                 |                     |                                       |         |         |

|                  | 010101 =   | RC5                   |                 |                     |                                       |         |         |

|                  | 010100 =   | RC4                   |                 |                     |                                       |         |         |

|                  | 010011 =   | RC3                   |                 |                     |                                       |         |         |

|                  | 010010 =   | RC2                   |                 |                     |                                       |         |         |

|                  | 010001 =   | RC1                   |                 |                     |                                       |         |         |

|                  | 010000 =   | RC0                   |                 |                     |                                       |         |         |

|                  | 001111 =   | RB7 <sup>(4)</sup>    |                 |                     |                                       |         |         |

|                  | 001110 =   | RB6 <sup>(4)</sup>    |                 |                     |                                       |         |         |

|                  | 001101 =   | RB5 <sup>(4)</sup>    |                 |                     |                                       |         |         |

|                  | 001100 =   | RB4 <sup>(4)</sup>    |                 |                     |                                       |         |         |

|                  |            | 0110 = Reserved       |                 |                     |                                       |         |         |

|                  |            |                       |                 |                     |                                       |         |         |

|                  | 000101 =   | RA5                   |                 |                     |                                       |         |         |

|                  | 000100 =   | RA4                   |                 |                     |                                       |         |         |

|                  | 000011 =   | RA3                   |                 |                     |                                       |         |         |

|                  | 000010 =   | RA2                   |                 |                     |                                       |         |         |

|                  | 000001 =   | RA1                   |                 |                     |                                       |         |         |

|                  | 000000 =   | RA0                   |                 |                     |                                       |         |         |

| bit 1            | GO/DONE: A | ADC Conversion Statu  | us bit          |                     |                                       |         |         |

|                  |            | version cycle in prog |                 | s bit starts an ADC | conversion cycle                      |         |         |

|                  |            | automatically cleare  |                 |                     |                                       |         |         |

|                  |            | version completed/no  |                 |                     | · · · · · · · · · · · · · · · · · · · |         |         |

0 = ADC conversion completed/not in progress

| Name     | Bit 7  | Bit 6 | Bit 5   | Bit 4        | Bit 3                | Bit 2 | Bit 1 | Bit 0   | Register<br>on page |

|----------|--------|-------|---------|--------------|----------------------|-------|-------|---------|---------------------|

| DAC1CON0 | DAC1EN | _     | DAC10E1 | DAC10E2      | DAC10E2 DAC1PSS<1:0> |       | _     | DAC1NSS | 287                 |

| DAC1CON1 | —      | _     | —       | DAC1R<4:0>   |                      |       |       |         | 287                 |

| CM1PSEL  | _      | _     | _       | — — PCH<2:0> |                      |       |       | 307     |                     |

| CM2PSEL  | _      | _     | _       | — — PCH<2:0> |                      |       |       | 307     |                     |

| TABLE 21-1: | SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE |

|-------------|------------------------------------------------------|

|             |                                                      |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

## PIC16(L)F15356/75/76/85/86

© 2016 Microchip Technology Inc.

## 25.0 TIMER0 MODULE

The Timer0 module is an 8/16-bit timer/counter with the following features:

- 16-bit timer/counter

- 8-bit timer/counter with programmable period

- Synchronous or asynchronous operation

- Selectable clock sources

- Programmable prescaler (independent of Watchdog Timer)

- Programmable postscaler

- Operation during Sleep mode

- · Interrupt on match or overflow

- Output on I/O pin (via PPS) or to other peripherals

## 25.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

## 25.1.1 16-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

## 25.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0, which is neither directly readable nor writable (see Figure 25-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

## 25.1.2 8-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

The value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh.

Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- <u>Any device Reset Power-on Reset (POR),</u> <u>MCLR Reset, Watchdog Timer Reset (WDTR) or</u>

- Brown-out Reset (BOR)

## 25.1.3 COUNTER MODE

In Counter mode, the prescaler is normally disabled by setting the T0CKPS bits of the T0CON1 register to '0000'. Each rising edge of the clock input (or the output of the prescaler if the prescaler is used) increments the counter by '1'.

## 25.1.4 TIMER MODE

In Timer mode, the Timer0 module will increment every instruction cycle as long as there is a valid clock signal and the T0CKPS bits of the T0CON1 register (Register 25-2) are set to '0000'. When a prescaler is added, the timer will increment at the rate based on the prescaler value.

## 25.1.5 ASYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is set (T0ASYNC = '1'), the counter increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows the counter to continue operation during Sleep mode provided that the clock also continues to operate during Sleep.

## 25.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system oscillator (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

## PIC16(L)F15356/75/76/85/86

| U-0                               | U-0                                  | U-0                                              | R/W-0/u | R/W-0/u        | R/W-0/u          | R/W-0/u        | R/W-0/u      |  |  |  |  |

|-----------------------------------|--------------------------------------|--------------------------------------------------|---------|----------------|------------------|----------------|--------------|--|--|--|--|

| _                                 | _                                    | _                                                |         |                | GSS<4:0>         |                |              |  |  |  |  |

| bit 7                             |                                      |                                                  |         |                |                  |                | bit C        |  |  |  |  |

|                                   |                                      |                                                  |         |                |                  |                |              |  |  |  |  |

| Legend:                           |                                      |                                                  |         |                |                  |                |              |  |  |  |  |

| R = Readable bit W = Writable bit |                                      |                                                  |         | U = Unimpler   | nented bit, read | d as '0'       |              |  |  |  |  |

| u = Bit is un                     | changed                              | x = Bit is unk                                   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is se                   | et                                   | '0' = Bit is cle                                 | ared    | HC = Bit is cl | eared by hardv   | vare           |              |  |  |  |  |

|                                   |                                      |                                                  |         |                |                  |                |              |  |  |  |  |

| bit 7-5                           | Unimpleme                            | nted: Read as '                                  | 0'      |                |                  |                |              |  |  |  |  |

| bit 4-0                           | GSS<4:0>: Timer1 Gate Select bits    |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 11111-10001 = Reserved               |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 10000 = LC4_out                      |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 01111 = LC3_out                      |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   |                                      | 01110 = LC2_out                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 01101 = LC1_out                      |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 00100 = ZCD1_output                  |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 01011 = C2OUT_sync                   |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 01010 = C1OUT_sync                   |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 01001 = NCO1_out                     |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 01000 = PWM6_out                     |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 00111 = PWM5_out<br>00110 = PWM4_out |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 0010 = PWM3  out                     |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 00100 = CCP2 out                     |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   | 00011 = CCP1_out                     |                                                  |         |                |                  |                |              |  |  |  |  |

|                                   |                                      | IR2 postscaled                                   |         |                |                  |                |              |  |  |  |  |

|                                   |                                      |                                                  | utput   |                |                  |                |              |  |  |  |  |

|                                   |                                      | 00001 = Timer0 overflow output<br>00000 = T1GPPS |         |                |                  |                |              |  |  |  |  |

## REGISTER 26-4: T1GATE TIMER1 GATE SELECT REGISTER

## 27.4 Timer2 Interrupt

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 27-3.

### FIGURE 27-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

|                 | Rev. 10-00<br>4                                          | 00205A<br>/7/2016 |

|-----------------|----------------------------------------------------------|-------------------|

| CKPS            | 0b010                                                    |                   |

| PRx             | 1                                                        |                   |

| OUTPS           | 0b0001                                                   |                   |

| TMRx_clk        |                                                          |                   |

| TMRx            |                                                          |                   |

| TMRx_postscaled |                                                          |                   |

| TMRxIF          | (1) (2) (1)                                              |                   |

| Note 1:<br>2:   | Synchronization may take as many as 2 instruction cycles |                   |

## 27.5.7 EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

In Edge-Triggered Hardware Limit One-Shot modes the timer starts on the first external signal edge after the ON bit is set and resets on all subsequent edges. Only the first edge after the ON bit is set is needed to start the timer. The counter will resume counting automatically two clocks after all subsequent external Reset edges. Edge triggers are as follows:

- Rising edge start and Reset (MODE<4:0> = 01100)

- Falling edge start and Reset (MODE<4:0> = 01101)

The timer resets and clears the ON bit when the timer value matches the PRx period value. External signal edges will have no effect until after software sets the ON bit. Figure 27-10 illustrates the rising edge hardware limit one-shot operation.

When this mode is used in conjunction with the CCP then the first starting edge trigger, and all subsequent Reset edges, will activate the PWM drive. The PWM drive will deactivate when the timer matches the CCPRx pulse-width value and stay deactivated until the timer halts at the PRx period match unless an external signal edge resets the timer before the match occurs.

## 27.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

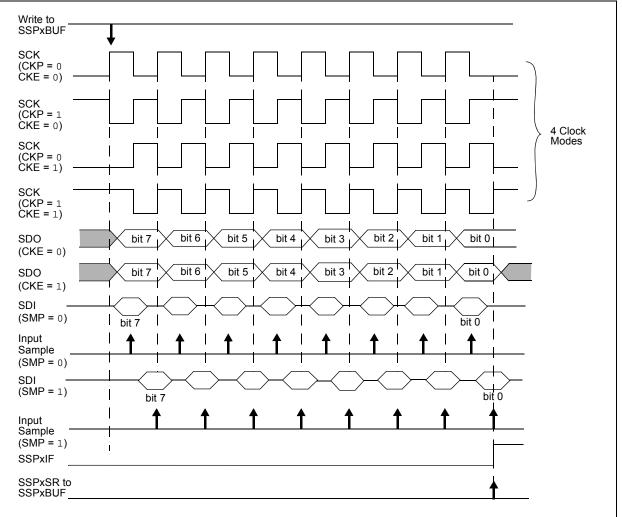

#### 32.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 32-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register. This then, would give waveforms for SPI communication as shown in Figure 32-6, Figure 32-8, Figure 32-9 and Figure 32-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 32-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

FIGURE 32-6: SPI MODE WAVEFORM (MASTER MODE)

## 32.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPxCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPxIF, to be set (SSP interrupt, if enabled):

- Start condition generated

- · Stop condition generated

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

#### 32.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 32.7** "**Baud Rate Generator**" for more detail.

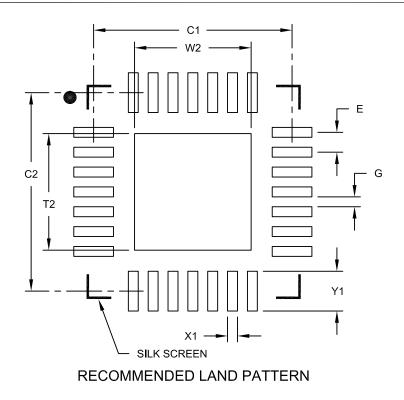

28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 4x4 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |  |

|----------------------------|-------------|----------|------|------|--|--|

| Dimensior                  | MIN         | NOM      | MAX  |      |  |  |

| Contact Pitch E            |             | 0.40 BSC |      |      |  |  |

| Optional Center Pad Width  | W2          |          |      | 2.35 |  |  |

| Optional Center Pad Length | T2          |          |      | 2.35 |  |  |

| Contact Pad Spacing        | C1          |          | 4.00 |      |  |  |

| Contact Pad Spacing        | C2          |          | 4.00 |      |  |  |

| Contact Pad Width (X28)    | X1          |          |      | 0.20 |  |  |

| Contact Pad Length (X28)   | Y1          |          |      | 0.80 |  |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2152A

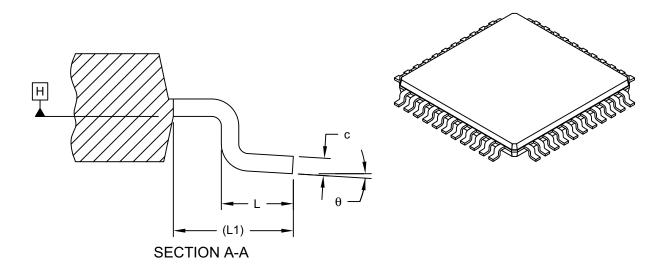

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Ν   | MILLIMETERS |                |      |  |  |  |

|--------------------------|-----|-------------|----------------|------|--|--|--|

| Dimension                | MIN | NOM         | MAX            |      |  |  |  |

| Number of Leads          | N   |             | 44             |      |  |  |  |

| Lead Pitch               | е   |             | 0.80 BSC       |      |  |  |  |

| Overall Height           | Α   | -           | -              | 1.20 |  |  |  |

| Standoff                 | A1  | 0.05        | -              | 0.15 |  |  |  |

| Molded Package Thickness | A2  | 0.95        | 1.00           | 1.05 |  |  |  |

| Overall Width            | E   |             | 12.00 BSC      |      |  |  |  |

| Molded Package Width     | E1  | 10.00 BSC   |                |      |  |  |  |

| Overall Length           | D   | 12.00 BSC   |                |      |  |  |  |

| Molded Package Length    | D1  |             | 10.00 BSC      |      |  |  |  |

| Lead Width               | b   | 0.30        | 0.37           | 0.45 |  |  |  |

| Lead Thickness           | С   | 0.09        | -              | 0.20 |  |  |  |

| Lead Length              | L   | 0.45        | 0.45 0.60 0.75 |      |  |  |  |

| Footprint L              |     |             | 1.00 REF       |      |  |  |  |

| Foot Angle               | θ   | 0°          | 3.5°           | 7°   |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2