Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15356-e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Digital Peripherals (Cont.)**

- I/O Pins:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

- Input level selection control (ST or TTL)

- Digital open-drain enable

- Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

#### **Analog Peripherals**

- Analog-to-Digital Converter (ADC):

- 10-bit with up to 43 external channels

- Operates in Sleep

- Two Comparators:

- FVR, DAC and external input pin available on inverting and noninverting input

- Software selectable hysteresis

- Outputs available internally to other modules, or externally through PPS

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- Voltage Reference:

- Fixed Voltage Reference with 1.024V, 2.048V and 4.096V output levels

- Zero-Cross Detect module:

- AC high voltage zero-crossing detection for simplifying TRIAC control

- Synchronized switching control and timing

#### **Flexible Oscillator Structure**

- High-Precision Internal Oscillator:

- Software selectable frequency range up to 32 MHz, ±1% typical

- x2/x4 PLL with Internal and External Sources

- Low-Power Internal 32 kHz Oscillator (LFINTOSC)

- External 32 kHz Crystal Oscillator (SOSC)

- External Oscillator Block with:

- Three crystal/resonator modes up to 20 MHz

- Three external clock modes up to 32 MHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if primary clock stops

- Oscillator Start-up Timer (OST):

- Ensures stability of crystal oscillator resources

| Name                                                                              | Function              | Input<br>Type    | Output Type | Description                                                                                        |

|-----------------------------------------------------------------------------------|-----------------------|------------------|-------------|----------------------------------------------------------------------------------------------------|

| RC2/ANC2/CCP1 <sup>(1)</sup> /IOCC2                                               | RC2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                               |

|                                                                                   | ANC2                  | AN               | —           | ADC Channel C2 input.                                                                              |

|                                                                                   | CCP1 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | Capture/compare/PWM1 (default input location for capture function).                                |

|                                                                                   | IOCC2                 | TTL/ST           | —           | Interrupt-on-change input.                                                                         |

| RC3/ANC3/SCL1 <sup>(1)</sup> /SDI1 <sup>(1)</sup> /T2IN <sup>(1)</sup> /<br>IOCC3 | RC3                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                               |

| 0000                                                                              | ANC3                  | AN               | —           | ADC Channel C3 input.                                                                              |

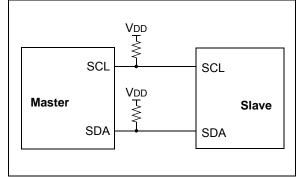

|                                                                                   | SCL1 <sup>(1)</sup>   | I <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C input/output.                                                               |

|                                                                                   | SDI1 <sup>(1)</sup>   | TTL/ST           | _           | MSSP1 SPI serial data input (default input location, SDI1 is a PPS remappable input and output).   |

|                                                                                   | T2IN <sup>(1)</sup>   | TTL/ST           | —           | Timer2 external input.                                                                             |

|                                                                                   | IOCC3                 | TTL/ST           | —           | Interrupt-on-change input.                                                                         |

| RC4/ANC4/SDA1 <sup>(1)</sup> /SDI1 <sup>(1)</sup> /IOCC4                          | RC4                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                               |

|                                                                                   | ANC4                  | AN               | _           | ADC Channel C4 input.                                                                              |

|                                                                                   | SDA1 <sup>(1)</sup>   | l <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                   |

|                                                                                   | SDI1 <sup>(1)</sup>   | TTL/ST           | _           | MSSP1 SPI serial data input (default input location, SDI1 is a PPS remappable input and output).   |

|                                                                                   | IOCC4                 | TTL/ST           | —           | Interrupt-on-change input.                                                                         |

| RC5/ANC5/IOCC5                                                                    | RC5                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                               |

|                                                                                   | ANC5                  | AN               | —           | ADC Channel C5 input.                                                                              |

|                                                                                   | IOCC5                 | TTL/ST           | —           | Interrupt-on-change input.                                                                         |

| RC6/ANC6/TX1/CK1 <sup>(1)</sup> /IOCC6                                            | RC6                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                               |

|                                                                                   | ANC6                  | AN               | —           | ADC Channel C6 input.                                                                              |

|                                                                                   | TX1                   | —                | CMOS        | EUSART1 asynchronous.                                                                              |

|                                                                                   | CK1 <sup>(1)</sup>    | TTL/ST           | CMOS/OD     | EUSART Synchronous mode clock input/output.                                                        |

|                                                                                   | IOCC6                 | TTL/ST           | _           | Interrupt-on-change input.                                                                         |

| RC7/ANC7/RX1/DT1 <sup>(1)</sup> /IOCC7                                            | RC7                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                               |

|                                                                                   | ANC7                  | AN               | _           | ADC Channel C7 input.                                                                              |

|                                                                                   | RX1                   | TTL/ST           | _           | EUSART1 Asynchronous mode receiver data input.                                                     |

|                                                                                   | DT1 <sup>(1)</sup>    | TTL/ST           | CMOS/OD     | EUSART1 Synchronous mode data input/output.                                                        |

|                                                                                   | IOCC7                 | TTL/ST           | _           | Interrupt-on-change input.                                                                         |

| RD0/AND0/SCL2 <sup>(1,4)</sup> /SCK2 <sup>(1)</sup> /                             | RD0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                               |

|                                                                                   | AND0                  | AN               | _           | ADC Channel D0 input.                                                                              |

|                                                                                   | SCL2 <sup>(1,4)</sup> | l <sup>2</sup> C | OD          | MSSP2 I <sup>2</sup> C input/output.                                                               |

|                                                                                   | SCK2 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | MSSP2 SPI clock input/output (default input location, SCK2 is<br>PPS remappable input and output). |

#### **TABLE 1-3:** PIC16(L)F15375/76 PINOUT DESCRIPTION (CONTINUED)

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx 1: pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options 2: as described in Table 15-5, Table 15-6 and Table 15-6. This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and

3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

Note

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                                         | Name | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0     Value on:<br>POR, BOR     Value on:<br>MCLR |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Bank 8-10                                       |      |                                                                                                                             |  |  |  |  |  |  |  |  |  |

| CPU CORE REGISTERS; see Table 4-3 for specifics |      |                                                                                                                             |  |  |  |  |  |  |  |  |  |

| x0Ch/<br>x8Ch<br>Unimplemented                  |      |                                                                                                                             |  |  |  |  |  |  |  |  |  |

## 5.2 Register Definitions: Configuration Words

| REGISTER          | 5-1: CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NFIGURATIO                                                                                        | N WORD 1:                                                                          | OSCILLATO                                                                 | RS                             |                                             |                   |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------|---------------------------------------------|-------------------|--|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/P-1                                                                                             | U-1                                                                                | R/P-1                                                                     | U-1                            | U-1                                         | R/P-1             |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FCMEN                                                                                             | _                                                                                  | CSWEN                                                                     | _                              | _                                           | CLKOUTEN          |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 13                                                                                            |                                                                                    |                                                                           |                                |                                             | bit 8             |  |

| 11.1              | R/P-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/P-1                                                                                             | R/P-1                                                                              | 11.1                                                                      | R/P-1                          | R/P-1                                       | R/P-1             |  |

| U-1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                   |                                                                                    | U-1                                                                       |                                |                                             |                   |  |

|                   | RSTOSC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RSTOSC1                                                                                           | RSTOSC0                                                                            | —                                                                         | FEXTOSC2                       | FEXTOSC1                                    | FEXTOSC0          |  |

| bit 7             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                   |                                                                                    |                                                                           |                                |                                             | bit (             |  |

| Legend:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| R = Readable      | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P = Programma                                                                                     | able bit                                                                           | x = Bit is unkno                                                          | own                            | U = Unimpleme<br>'1'                        | nted bit, read as |  |

| '0' = Bit is clea | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '1' = Bit is set                                                                                  |                                                                                    | W = Writable b                                                            | it                             | n = Value when blank or after Bulk<br>Erase |                   |  |

| bit 13            | FCMEN: Fail-<br>1 = FSCM tir<br>0 = FSCM tir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                   | or Enable bit                                                                      |                                                                           |                                |                                             |                   |  |

| bit 12            | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ed: Read as '1'                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| bit 11            | 1 = Writing to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | k Switch Enable<br>NOSC and NDI<br>C and NDIV bits                                                | / is allowed                                                                       | ged by user soft                                                          | ware                           |                                             |                   |  |

| bit 10-9          | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ed: Read as '1'                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| bit 8             | If FEXTOSC =<br>1 = CLKOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Clock Out Enable<br><u>EC (high, mid or</u><br>function is disable<br>function is enable<br>pred. | <u>low) or Not En</u><br>ed; I/O or oscill                                         | ator function on (                                                        |                                |                                             |                   |  |

| bit 7             | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ed: Read as '1'                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| bit 6-4           | This value is t           111 =         EXTC           110 =         HFIN           101 =         LFIN           100 =         SOSC           011 =         Reserved           010 =         EXTC           001 =         EXTC           001 =         EXTC                                                                                                                                                                                                                                                                                                                                                            | OSC operating per<br>TOSC with HFFR<br>TOSC                                                       | value for COSC<br>FEXTOSC bits<br>Q = 3 ' b010<br>with EXTOSC of<br>with EXTOSC of | and selects the<br>(device manufa<br>pperating per FE<br>pperating per FE | cturing default)<br>XTOSC bits | ed by user softwa                           | re.               |  |

| bit 3             | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ed: Read as '1'                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

| bit 2-0           | Unimplemented: Read as '1'<br>FEXTOSC<2:0>:FEXTOSC External Oscillator Mode Selection bits<br>111 = EC (External Clock) above 8 MHz; PFM set to high power (device manufacturing default)<br>10 = EC (External Clock) for 100 kHz to 8 MHz; PFM set to medium power<br>101 = EC (External Clock) below 100 kHz<br>100 = Oscillator not enabled<br>011 = Reserved (do not use)<br>010 = HS (Crystal oscillator) above 4 MHz; PFM set to high power<br>001 = XT (Crystal oscillator) above 100 kHz, below 4 MHz; PFM set to medium power<br>000 = LP (Crystal oscillator) optimized for 32.768 kHz; PFM set to low power |                                                                                                   |                                                                                    |                                                                           |                                |                                             |                   |  |

#### REGISTER 5-1: CONFIGURATION WORD 1: OSCILLATORS

#### REGISTER 5-3: CONFIGURATION WORD 3: WINDOWED WATCHDOG (CONTINUED)

bit 4-0 WDTCPS<4:0>: WDT Period Select bits

|                    |                    | WDTPS at   | POR             |                                    |                                 |

|--------------------|--------------------|------------|-----------------|------------------------------------|---------------------------------|

| WDTCPS             | Value              | Divider Ra | atio            | Typical Time Out<br>(FIN = 31 kHz) | - Software Control<br>of WDTPS? |

| 11111 <b>(1)</b>   | 01011              | 1:65536    | 2 <sup>16</sup> | 2 s                                | Yes                             |

| 11110<br><br>10011 | 11110<br><br>10011 | 1:32       | 2 <sup>5</sup>  | 1 ms                               | No                              |

| 10010              | 10010              | 1:8388608  | 2 <sup>23</sup> | 256 s                              |                                 |

| 10001              | 10001              | 1:4194304  | 2 <sup>22</sup> | 128 s                              |                                 |

| 10000              | 10000              | 1:2097152  | 2 <sup>21</sup> | 64 s                               |                                 |

| 01111              | 01111              | 1:1048576  | 2 <sup>20</sup> | 32 s                               |                                 |

| 01110              | 01110              | 1:524299   | 2 <sup>19</sup> | 16 s                               |                                 |

| 01101              | 01101              | 1:262144   | 2 <sup>18</sup> | 8 s                                |                                 |

| 01100              | 01100              | 1:131072   | 2 <sup>17</sup> | 4 s                                |                                 |

| 01011              | 01011              | 1:65536    | 2 <sup>16</sup> | 2 s                                |                                 |

| 01010              | 01010              | 1:32768    | 2 <sup>15</sup> | 1 s                                |                                 |

| 01001              | 01001              | 1:16384    | 2 <sup>14</sup> | 512 ms                             | No                              |

| 01000              | 01000              | 1:8192     | 2 <sup>13</sup> | 256 ms                             |                                 |

| 00111              | 00111              | 1:4096     | 2 <sup>12</sup> | 128 ms                             |                                 |

| 00110              | 00110              | 1:2048     | 2 <sup>11</sup> | 64 ms                              |                                 |

| 00101              | 00101              | 1:1024     | 2 <sup>10</sup> | 32 ms                              |                                 |

| 00100              | 00100              | 1:512      | 2 <sup>9</sup>  | 16 ms                              |                                 |

| 00011              | 00011              | 1:256      | 2 <sup>8</sup>  | 8 ms                               |                                 |

| 00010              | 00010              | 1:128      | 2 <sup>7</sup>  | 4 ms                               |                                 |

| 00001              | 00001              | 1:64       | 2 <sup>6</sup>  | 2 ms                               |                                 |

| 00000              | 00000              | 1:32       | 2 <sup>5</sup>  | 1 ms                               |                                 |

**Note 1:** 0b11111 is the default value of the WDTCPS bits.

© 2016 Microchip Technology Inc.

#### 5.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 5.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See **Section 5.4** "Write **Protection**" for more information.

#### 5.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRTAPP, WRTSAF, WRTB, WRTC bits in Configuration Words (Register 5-4) define whether the corresponding region of the program memory block is protected or not.

#### 5.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 13.3.6 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC16(L)F153xx Memory Programming Specification" (DS40001838).

#### 8.15 Register Definitions: Power Control

#### REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:          |                        |                                                                             |                                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| HC = Bit is clo  | eared by hardv         | vare                                                                        | HS = Bit is set by hardware                                                                                                                         |  |  |  |  |  |

| R = Readable     | e bit                  | W = Writable bit                                                            | U = Unimplemented bit, read as '0'                                                                                                                  |  |  |  |  |  |

| u = Bit is uncl  | hanged                 | x = Bit is unknown                                                          | -m/n = Value at POR/Value at all other Resets                                                                                                       |  |  |  |  |  |

| '1' = Bit is set |                        | '0' = Bit is cleared                                                        | q = Value depends on condition                                                                                                                      |  |  |  |  |  |

| bit 7            | 1 = A Stack            | tack Overflow Flag bit<br>Overflow occurred<br>Overflow has not occurre     | ed or cleared by firmware                                                                                                                           |  |  |  |  |  |

| bit 6            | 1 = A Stack            | tack Underflow Flag bit<br>Underflow occurred<br>Underflow has not occurr   | red or cleared by firmware                                                                                                                          |  |  |  |  |  |

| bit 5            | 1 = A WDT<br>0 = A WDT | Window Violation Reset h                                                    | g bit<br>as not occurred or set to '1' by firmware<br>as occurred (a CLRWDT instruction was executed either without<br>window (cleared by hardware) |  |  |  |  |  |

| bit 4            | 1 = A Watch            |                                                                             | it<br>occurred or set to '1' by firmware<br>urred (cleared by hardware)                                                                             |  |  |  |  |  |

| bit 3            | 1 = A MCLR             | CLR Reset Flag bit<br>Reset has not occurred of<br>Reset has occurred (clea |                                                                                                                                                     |  |  |  |  |  |

| bit 2            | 1 = A RESET            |                                                                             | executed or set to '1' by firmware<br>ecuted (cleared by hardware)                                                                                  |  |  |  |  |  |

| bit 1            | 1 = No Pow             | r-on Reset Status bit<br>er-on Reset occurred<br>r-on Reset occurred (must  | t be set in software after a Power-on Reset occurs)                                                                                                 |  |  |  |  |  |

| bit 0            | 1 = No Brow            | •                                                                           | t be set in software after a Power-on Reset or Brown-out Reset                                                                                      |  |  |  |  |  |

# PIC16(L)F15356/75/76/85/86

| REGISTER                                                                                                                              | 10-3: PIE1:                                  | PERIPHERAI                                                             |                                                      | PT ENABLE      | REGISTER 1       |                  |              |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|----------------|------------------|------------------|--------------|

| R/W-0/0                                                                                                                               | R/W-0/0                                      | U-0                                                                    | U-0                                                  | U-0            | U-0              | R/W-0/0          | R/W-0/0      |

| OSFIE                                                                                                                                 | CSWIE                                        | —                                                                      | —                                                    | —              | —                | —                | ADIE         |

| bit 7                                                                                                                                 |                                              |                                                                        |                                                      |                |                  |                  | bit 0        |

| Legend:                                                                                                                               |                                              |                                                                        |                                                      |                |                  |                  | ]            |

| R = Readab                                                                                                                            | la hit                                       | W = Writable                                                           | h:t                                                  |                | nantad hit raad  | aa 'O'           |              |

|                                                                                                                                       |                                              |                                                                        |                                                      |                | nented bit, read |                  |              |

| u = Bit is un                                                                                                                         | changed                                      | x = Bit is unkr                                                        | iown                                                 | -n/n = Value a | at POR and BOI   | R/Value at all c | other Resets |

| '1' = Bit is se                                                                                                                       | et                                           | '0' = Bit is clea                                                      | ared                                                 |                |                  |                  |              |

| bit 6                                                                                                                                 | 0 = Disables<br>CSWIE: Cloc<br>1 = The clock | he Oscillator Fa<br>the Oscillator F<br>k Switch Comp<br>switch module | ail Interrupt<br>lete Interrupt I<br>interrupt is er | nabled         |                  |                  |              |

| <b>h</b> :1 <b>F</b> 4                                                                                                                |                                              | switch module                                                          | •                                                    | sabled         |                  |                  |              |

| bit 5-1                                                                                                                               | -                                            | ted: Read as '                                                         |                                                      |                |                  |                  |              |

| bit 0 ADIE: Analog-to-Digital Converter (ADC) Interrupt Enable bit<br>1 = Enables the ADC interrupt<br>0 = Disables the ADC interrupt |                                              |                                                                        |                                                      |                |                  |                  |              |

| <b>Note:</b> Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE7         |                                              |                                                                        |                                                      |                |                  |                  |              |

#### EXAMPLE 13-1: PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELNVMADRL; Select Bank for NVMCON registersMOVLWPROG_ADDR_LO;MOVWFNVMADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWFNVMADRH; Store MSB of address

BCF

NVMCON1,NVMREGS ; Do not select Configuration Space

BSF

NVMCON1, RD

; Initiate read

MOVF

NVMDATL,W

; Get LSB of word

NVMDATL,W; Get LSB of wordPROG_DATA_LO; Store in user locationNVMDATH,W; Get MSB of wordPROG_DATA_HI; Store in user location

MOVWF

MOVF

MOVWF

```

## 14.10.8 PORTE FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

### 22.0 NUMERICALLY CONTROLLED OSCILLATOR (NCO) MODULE

The Numerically Controlled Oscillator (NCO) module is a timer that uses overflow from the addition of an increment value to divide the input frequency. The advantage of the addition method over simple counter driven timer is that the output frequency resolution does not vary with the divider value. The NCO is most useful for application that requires frequency accuracy and fine resolution at a fixed duty cycle.

Features of the NCO include:

- 20-bit Increment Function

- Fixed Duty Cycle mode (FDC) mode

- Pulse Frequency (PF) mode

- Output Pulse Width Control

- Multiple Clock Input Sources

- Output Polarity Control

- Interrupt Capability

Figure 22-1 is a simplified block diagram of the NCO module.

#### 23.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 23-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 23-2) contains Control bits for the following:

- · Interrupt on positive/negative edge enables

- The CMxNSEL and CMxPSEL (Register 23-3 and Register 23-4) contain control bits for the following:

- Positive input channel selection

- Negative input channel selection

#### 23.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 23.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 15-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 23.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 23-2 shows the output state versus input conditions, including polarity control.

#### TABLE 23-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 27.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

| R/W-0/0                                                                               | R/W-0/0                                                                                                                            | R/W-0/0                                                                | R/W-0/0                          | R/W-0/0               | R/W-0/0            | R/W-0/0           | R/W-0/0 |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------|-----------------------|--------------------|-------------------|---------|

| PSYNC <sup>(1,</sup>                                                                  | <sup>2)</sup> CKPOL <sup>(3)</sup>                                                                                                 | CKSYNC <sup>(4, 5)</sup>                                               |                                  |                       | MODE<4:0>(6, 7)    | 1                 |         |

| bit 7                                                                                 |                                                                                                                                    |                                                                        |                                  |                       |                    |                   | bit 0   |

|                                                                                       |                                                                                                                                    |                                                                        |                                  |                       |                    |                   |         |

| Legend:                                                                               |                                                                                                                                    |                                                                        |                                  |                       |                    |                   |         |

| R = Readab                                                                            | le bit                                                                                                                             | W = Writable bit                                                       |                                  | U = Unimpleme         | ented bit, read as | ʻ0'               |         |

| u = Bit is un                                                                         | changed                                                                                                                            | x = Bit is unknow                                                      | 'n                               | -n/n = Value at       | POR and BOR/V      | alue at all other | Resets  |

| '1' = Bit is se                                                                       | et                                                                                                                                 | '0' = Bit is cleare                                                    | d                                |                       |                    |                   |         |

| bit 7                                                                                 | 1 = TMRx Pr<br>0 = TMRx Pr                                                                                                         | erx Prescaler Synch<br>rescaler Output is s<br>rescaler Output is n    | ynchronized to<br>ot synchronize | Fosc/4                |                    |                   |         |

| bit 6                                                                                 | 1 = Falling e                                                                                                                      | erx Clock Polarity S<br>dge of input clock c<br>dge of input clock cl  | locks timer/pre                  |                       |                    |                   |         |

| bit 5                                                                                 | 1 = ON regis                                                                                                                       | nerx Clock Synchro<br>ster bit is synchroniz<br>ster bit is not synchr | ed to TMR2_c                     | clk input             |                    |                   |         |

| bit 4-0                                                                               | MODE<4:0>:<br>See Table 27-                                                                                                        | Timerx Control Mod                                                     | de Selection b                   | its <sup>(6, 7)</sup> |                    |                   |         |

| Note 1:                                                                               | Setting this bit ens                                                                                                               | sures that reading T                                                   | MRx will retur                   | n a valid value.      |                    |                   |         |

| 2:                                                                                    | When this bit is '1                                                                                                                | ', Timer2 cannot op                                                    | erate in Sleep                   | mode.                 |                    |                   |         |

| 3: CKPOL should not be changed while ON = 1.                                          |                                                                                                                                    |                                                                        |                                  |                       |                    |                   |         |

| 4: Setting this bit ensures glitch-free operation when the ON is enabled or disabled. |                                                                                                                                    |                                                                        |                                  |                       |                    |                   |         |

| 5:                                                                                    | When this bit is se                                                                                                                | et then the timer ope                                                  | eration will be                  | delayed by two Tl     | MRx input clocks   | after the ON bit  | is set. |

| 6:                                                                                    | 6: Unless otherwise indicated, all modes start upon ON = 1 and stop upon ON = 0 (stops occur without affecting the value of TMRx). |                                                                        |                                  |                       |                    |                   |         |

#### REGISTER 27-3: T2HLT: TIMERx HARDWARE LIMIT CONTROL REGISTER

7: When TMRx = PRx, the next clock clears TMRx, regardless of the operating mode.

# © 2016 Microchip Technology Inc.

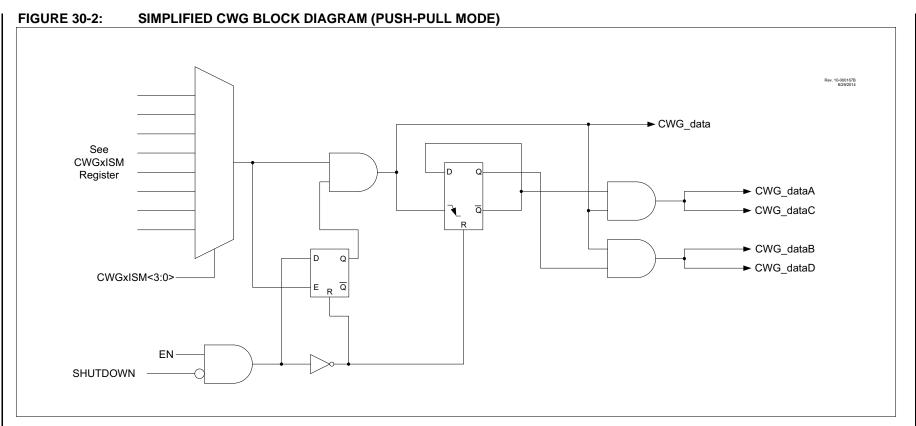

#### 30.12 Configuring the CWG

The following steps illustrate how to properly configure the CWG.

- 1. Ensure that the TRIS control bits corresponding to the desired CWG pins for your application are set so that the pins are configured as inputs.

- 2. Clear the EN bit, if not already cleared.

- 3. Set desired mode of operation with the MODE bits.

- Set desired dead-band times, if applicable to mode, with the CWG1DBR and CWG1DBF registers.

- 5. Setup the following controls in the CWG1AS0 and CWG1AS1 registers.

- a. Select the desired shutdown source.

- b. Select both output overrides to the desired levels (this is necessary even if not using autoshutdown because start-up will be from a shutdown state).

- c. Set which pins will be affected by auto-shutdown with the CWG1AS1 register.

- d. Set the SHUTDOWN bit and clear the REN bit.

- 6. Select the desired input source using the CWG1ISM register.

- 7. Configure the following controls.

- a. Select desired clock source using the CWG1CLKCON register.

- b. Select the desired output polarities using the CWG1CON1 register.

- c. Set the output enables for the desired outputs.

- 8. Set the EN bit.

- Clear TRIS control bits corresponding to the desired output pins to configure these pins as outputs.

- If auto-restart is to be used, set the REN bit and the SHUTDOWN bit will be cleared automatically. Otherwise, clear the SHUTDOWN bit to start the CWG.

#### 30.12.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the LSBD and LSAC bits of the CWG1AS0 register. LSBD<1:0> controls the CWG1B and D override levels and LSAC<1:0> controls the CWG1A and C override levels. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not affect the override level.

#### 30.12.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the REN bit of the CWG1CON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 30-13 and Figure 30-14.

#### 30.12.2.1 Software Controlled Restart

When the REN bit of the CWG1AS0 register is cleared, the CWG must be restarted after an auto-shutdown event by software. Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the SHUTDOWN bit will remain set. The overrides will remain in effect until the first rising edge event after the SHUTDOWN bit is cleared. The CWG will then resume operation.

#### 30.12.2.2 Auto-Restart

When the REN bit of the CWG1CON2 register is set, the CWG will restart from the auto-shutdown state automatically. The SHUTDOWN bit will clear automatically when all shutdown sources go low. The overrides will remain in effect until the first rising edge event after the SHUTDOWN bit is cleared. The CWG will then resume operation.

| R/W/HS-0/0                                                                                                                                             | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0/0                                              | R/W-1/1                    | R/W-0/0                                                                  | R/W-1/1                        | U-0                 | U-0           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|--------------------------------|---------------------|---------------|

| SHUTDOWN <sup>(1, 2)</sup>                                                                                                                             | REN                                                                                                                                                                                                                                                                                                                                                                                                   | LSBD<1:0> LSAC<1:0> — —                              |                            |                                                                          |                                |                     |               |

| bit 7                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                            |                                                                          |                                | ·                   | bit 0         |

|                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                            |                                                                          |                                |                     |               |

| Legend:                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                            |                                                                          |                                |                     |               |

| HC = Bit is cleared                                                                                                                                    | l by hardware                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |                            | HS = Bit is se                                                           | et by hardware                 | •                   |               |

| R = Readable bit                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       | W = Writable                                         | e bit                      | U = Unimpler                                                             | nented bit, rea                | ad as '0'           |               |

| u = Bit is unchange                                                                                                                                    | ed                                                                                                                                                                                                                                                                                                                                                                                                    | x = Bit is unk                                       | nown                       | -n/n = Value a                                                           | at POR and BO                  | DR/Value at all     | other Resets  |

| '1' = Bit is set                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       | '0' = Bit is cle                                     | eared                      | q = Value de                                                             | pends on cond                  | lition              |               |

| bit 7 SHUTDOWN: Auto-Shutdown Event Status bit <sup>(1, 2)</sup><br>1 = An Auto-Shutdown state is in effect<br>0 = No Auto-shutdown event has occurred |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                            |                                                                          |                                |                     |               |

| bit 6                                                                                                                                                  | REN: Auto-R<br>1 = Auto-res<br>0 = Auto-res                                                                                                                                                                                                                                                                                                                                                           |                                                      | bit                        |                                                                          |                                |                     |               |

| bit 5-4                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                            | -Shutdown Sta                                                            |                                |                     |               |

|                                                                                                                                                        | 10 =A logic '(<br>01 =Pin is tri-                                                                                                                                                                                                                                                                                                                                                                     | o' is placed or<br>-stated on CW<br>tive state of th | n CWG1B/D w<br>/G1B/D when | hen an auto-sh<br>hen an auto-sh<br>an auto-shutdo<br>g polarity, is pla | utdown event<br>wn event is pr | is present<br>esent | equired dead- |