Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Detaile                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Details                    |                                                                             |

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15356-e-sp |

TABLE 3: 28-PIN ALLOCATION TABLE (PIC16(L)F15356) (CONTINUED)

| I/O <sup>(2)</sup> | 28-Pin PDIP/SOIC/SSOP | 28-Pin UQFN | ADC  | Reference | Comparator | NCO     | DAC | Timers              | CCP                 | PWM     | CWG            | MSSP                                           | αɔz | EUSART                    | פרכ     | CLKR | Interrupt | Pull-up | Basic       |

|--------------------|-----------------------|-------------|------|-----------|------------|---------|-----|---------------------|---------------------|---------|----------------|------------------------------------------------|-----|---------------------------|---------|------|-----------|---------|-------------|

| RC0                | 11                    | 8           | ANC0 | -         | _          | _       | _   | SOSCO<br>T1CKI      | _                   | _       | _              | _                                              | -   | _                         | _       | _    | IOCC0     | Υ       | _           |

| RC1                | 12                    | 9           | ANC1 | _         | _          | _       | _   | SOSCI               | CCP2 <sup>(1)</sup> | _       | _              | _                                              | _   | _                         | -       | _    | IOCC1     | Υ       | _           |

| RC2                | 13                    | 10          | ANC2 | _         | _          | _       | _   | _                   | CCP1 <sup>(1)</sup> | _       | _              | _                                              | _   | _                         | _       | _    | IOCC2     | Υ       | _           |

| RC3                | 14                    | 11          | ANC3 | ı         | _          | _       | _   | T2IN <sup>(1)</sup> | _                   | _       | _              | SCL1,<br>SCK1 <sup>(1,4)</sup>                 | ı   | ı                         | ı       | _    | IOCC3     | Υ       | _           |

| RC4                | 15                    | 12          | ANC4 | -         | _          | _       | _   | _                   | _                   | _       | _              | SDA1,<br>SDI1 <sup>(1,4)</sup>                 | -   | -                         | -       | _    | IOCC4     | Υ       | _           |

| RC5                | 16                    | 13          | ANC5 | _         | _          | _       | _   | _                   | _                   | _       | _              | _                                              | _   | _                         | -       | _    | IOCC5     | Υ       | _           |

| RC6                | 17                    | 14          | ANC6 | 1         | _          | _       | _   |                     | _                   | _       | _              | _                                              | ı   | TX1<br>CK1 <sup>(1)</sup> | I       | ı    | IOCC6     | Υ       | _           |

| RC7                | 18                    | 15          | ANC7 | ı         | _          | _       | _   | _                   | _                   | _       | _              | _                                              | ı   | RX1<br>DT1 <sup>(1)</sup> | ı       | _    | IOCC7     | Υ       | _           |

| RE3                | 1                     | 26          | -    | _         | _          | -       | _   | _                   | _                   | -       | _              | _                                              | _   | _                         | _       | -    | IOCE3     | Υ       | MCLR<br>VPP |

| VDD                | 20                    | 17          | _    | _         | _          | _       | _   | _                   | _                   | _       | _              | _                                              | _   | _                         | -       | _    | _         | _       | VDD         |

| Vss                | 8                     | 16          | _    | -         | _          | _       | _   | _                   | _                   | _       | _              | _                                              | _   | _                         | _       | _    | _         | _       | Vss         |

| Vss                | 19                    | 5           | _    | _         | _          | _       | _   | _                   | _                   | _       | _              | _                                              | _   | _                         | _       | _    | _         | _       | Vss         |

| OUT <sup>(2)</sup> | _                     | _           | _    | ı         | C1OUT      | NCO10UT | _   | TMR0                | CCP1                | PWM3OUT | CWG1A<br>CWG2A | SDO1/2                                         | ı   | DT                        | CLC10UT | CLKR | _         | _       | _           |

|                    | -                     | -           | _    | -         | C2OUT      | _       | _   | _                   | CCP2                | PWM4OUT | CWG1B<br>CWG2B | SCK1/2                                         | -   | СК                        | CLC2OUT | _    | _         | _       | _           |

|                    | -                     | -           | _    | _         | _          | _       | _   | _                   | _                   | PWM5OUT | CWG1C<br>CWG2C | SCL1 <sup>(3,4)</sup><br>SCL2 <sup>(3,4)</sup> | _   | TX                        | CLC3OUT | _    | _         | _       | _           |

|                    | _                     | _           | _    |           | _          |         |     | _                   | _                   | PWM6OUT | CWG1D<br>CWG2D | SDA1 <sup>(3,4)</sup><br>SDA2 <sup>(3,4)</sup> | -   | -                         | CLC4OUT | _    | _         | _       | _           |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

PIC16(L)F15356/75/76/85/86

<sup>2:</sup> All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one or more PORTx pin options.

<sup>3:</sup> This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

<sup>4:</sup> These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

| 1/0(2) | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO | DAC | Timers              | CCP                 | MM | CWG | MSSP                          | ZCD | EUSART                    | CLC | CLKR | Interrupt | Pull-up | Basic       |

|--------|------------------|------|-----------|------------|-----|-----|---------------------|---------------------|----|-----|-------------------------------|-----|---------------------------|-----|------|-----------|---------|-------------|

| RC2    | 40               | ANC2 | _         | _          | _   | _   | _                   | CCP1 <sup>(1)</sup> | _  | _   | _                             | _   |                           |     | _    | IOCC2     | Υ       | _           |

| RC3    | 41               | ANC3 | _         | l          | _   | _   | T2IN <sup>(1)</sup> | _                   | ı  | _   | SCL1<br>SCL2 <sup>(1,4)</sup> | _   |                           | l   | _    | IOCC3     | Υ       | _           |

| RC4    | 46               | ANC4 | -         | -          | _   | _   | _                   | -                   | -  | _   | SDA1<br>SDI1 <sup>(1,4)</sup> | -   |                           | -   | _    | IOCC4     | Υ       | _           |

| RC5    | 47               | ANC5 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | IOCC5     | Υ       | _           |

| RC6    | 48               | ANC6 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | TX1<br>CK1 <sup>(1)</sup> | _   | _    | IOCC6     | Υ       | _           |

| RC7    | 1                | ANC7 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | RX1<br>DT1 <sup>(1)</sup> | _   | _    | IOCC7     | Υ       | _           |

| RD0    | 42               | AND0 | _         | _          | _   | _   | _                   | _                   | _  | _   | SCK2<br>SCL2 <sup>(1,4)</sup> | _   | _                         | _   | _    | _         | Υ       | _           |

| RD1    | 43               | AND1 | _         | _          | _   | _   | _                   | _                   | _  | _   | SDA2<br>SDI2 <sup>(1,4)</sup> | _   | _                         | _   | _    | _         | Υ       | _           |

| RD2    | 44               | AND2 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RD3    | 45               | AND3 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RD4    | 2                | AND4 | _         | ı          | _   | _   | _                   |                     | ı  | _   | _                             | _   | ı                         | I   | -    | _         | Υ       | _           |

| RD5    | 3                | AND5 |           | -          | _   | _   | _                   | _                   | I  | _   | _                             | _   | ı                         | I   | _    | _         | Υ       | _           |

| RD6    | 4                | AND6 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RD7    | 5                | AND7 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RE0    | 27               | ANE0 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RE1    | 28               | ANE1 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RE2    | 29               | ANE2 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RE3    | 20               | ı    | _         | ı          | _   | _   | _                   | _                   | ı  | _   | _                             | _   |                           | ı   | _    | IOCE3     | Y       | MCLR<br>VPP |

| RF0    | 36               | ANF0 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | -   | _    | _         | Υ       | _           |

| RF1    | 37               | ANF1 | _         |            | _   | _   | _                   | _                   | _  | _   | _                             |     |                           |     | _    | _         | Υ       | _           |

| RF2    | 38               | ANF2 | -         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RF3    | 39               | ANF3 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RF4    | 12               | ANF4 | _         | _          | _   | _   | _                   | _                   | _  | _   | _                             | _   | _                         | -   | _    | _         | Υ       | _           |

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

PIC16(L)F15356/75/76/85/86

<sup>2:</sup> All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

<sup>3:</sup> This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

<sup>4:</sup> These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

TABLE 4-7: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANK 24-31

|      | BANK 24                                                   |      | BANK 25                                                   |              | BANK 26                       |              | BANK 27                       |       | BANK 28                       |       | BANK 29                       |       | BANK 30                       |       | BANK 31                       |

|------|-----------------------------------------------------------|------|-----------------------------------------------------------|--------------|-------------------------------|--------------|-------------------------------|-------|-------------------------------|-------|-------------------------------|-------|-------------------------------|-------|-------------------------------|

| C00h | Core Registers<br>(Table 4-3)                             | C80h | Core Registers<br>(Table 4-3)                             | D00h<br>D0Bh | Core Registers<br>(Table 4-3) | D80h<br>D8Bh | Core Registers<br>(Table 4-3) | E00h  | Core Registers<br>(Table 4-3) | E80h  | Core Registers<br>(Table 4-3) | F00h  | Core Registers<br>(Table 4-3) | F80h  | Core Registers<br>(Table 4-3) |

|      |                                                           |      |                                                           |              |                               | DODII        |                               | EUDII |                               | CODII |                               | FUBII |                               | FODII |                               |

| C0Ch | Unimplemented<br>Read as '0'                              | C8Ch | Unimplemented<br>Read as '0'                              | D0Ch         | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |

| C20h |                                                           | CA0h |                                                           |              |                               |              |                               |       |                               |       |                               |       |                               |       |                               |

|      | General<br>Purpose<br>Register<br>80 Bytes <sup>(1)</sup> |      | General<br>Purpose<br>Register<br>80 Bytes <sup>(1)</sup> |              |                               |              |                               |       |                               |       |                               |       |                               |       |                               |

| C6Fh |                                                           | CEFh |                                                           | D6Fh         |                               | DEFh         |                               | E6Fh  |                               | EEFh  |                               | F6Fh  |                               | FEFh  |                               |

| C70h |                                                           | CF0h |                                                           | D70h         |                               | DF0h         |                               | E70h  |                               | EF0h  |                               | F70h  |                               | FF0h  |                               |

|      | Accesses<br>70h – 7Fh                                     |      | Accesses<br>70h – 7Fh                                     |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |       | Accesses<br>70h – 7Fh         |       | Accesses<br>70h – 7Fh         |       | Accesses<br>70h – 7Fh         |       | Accesses<br>70h – 7Fh         |

| CFFh |                                                           | CFFh |                                                           | D7Fh         |                               | DFFh         |                               | E7Fh  |                               | EFFh  |                               | F7Fh  |                               | FFFh  |                               |

**Legend:** = Unimplemented data memory locations, read as '0'.

**Note 1:** Present only in PIC16(L)F15356/76/86.

# 5.2 Register Definitions: Configuration Words

#### REGISTER 5-1: CONFIGURATION WORD 1: OSCILLATORS

| R/P-1  | U-1 | R/P-1 | U-1 | U-1 | R/P-1    |

|--------|-----|-------|-----|-----|----------|

| FCMEN  | _   | CSWEN | _   | _   | CLKOUTEN |

| bit 13 |     |       |     |     | bit 8    |

| U-1   | R/P-1   | R/P-1   | R/P-1   | U-1 | R/P-1    | R/P-1    | R/P-1    |

|-------|---------|---------|---------|-----|----------|----------|----------|

| _     | RSTOSC2 | RSTOSC1 | RSTOSC0 | 1   | FEXTOSC2 | FEXTOSC1 | FEXTOSC0 |

| bit 7 |         |         |         |     |          |          | bit 0    |

| Legend:              |                      |                    |                                             |

|----------------------|----------------------|--------------------|---------------------------------------------|

| R = Readable bit     | P = Programmable bit | x = Bit is unknown | U = Unimplemented bit, read as '1'          |

| '0' = Bit is cleared | '1' = Bit is set     | W = Writable bit   | n = Value when blank or after Bulk<br>Erase |

bit 13 FCMEN: Fail-Safe Clock Monitor Enable bit

1 = FSCM timer enabled0 = FSCM timer disabled

bit 12 Unimplemented: Read as '1'

bit 11 CSWEN: Clock Switch Enable bit

1 = Writing to NOSC and NDIV is allowed

0 = The NOSC and NDIV bits cannot be changed by user software

bit 10-9 Unimplemented: Read as '1'

bit 8 CLKOUTEN: Clock Out Enable bit

If FEXTOSC = EC (high, mid or low) or Not Enabled:

1 = CLKOUT function is disabled; I/O or oscillator function on OSC2

0 = CLKOUT function is enabled; FOSC/4 clock appears at OSC2

Otherwise:

This bit is ignored.

bit 7 Unimplemented: Read as '1'

bit 6-4 RSTOSC<2:0>: Power-up Default Value for COSC bits

This value is the Reset-default value for COSC and selects the oscillator first used by user software.

111 = EXTOSC operating per FEXTOSC bits (device manufacturing default)

110 = HFINTOSC with HFFRQ = 3'b010

101 = LFINTOSC

100 = SOSC

011 = Reserved

010 = EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC bits

001 = EXTOSC with 2x PLL, with EXTOSC operating per FEXTOSC bits

000 = HFINTOSC with CDIV = 1:1 and HFFRQ = 3'b110

bit 3 Unimplemented: Read as '1'

bit 2-0 FEXTOSC<2:0>:FEXTOSC External Oscillator Mode Selection bits

111 = EC (External Clock) above 8 MHz; PFM set to high power (device manufacturing default)

110 = EC (External Clock) for 100 kHz to 8 MHz; PFM set to medium power

101 = EC (External Clock) below 100 kHz

100 = Oscillator not enabled

011 = Reserved (do not use)

010 = HS (Crystal oscillator) above 4 MHz; PFM set to high power

001 = XT (Crystal oscillator) above 100 kHz, below 4 MHz; PFM set to medium power

000 = LP (Crystal oscillator) optimized for 32.768 kHz; PFM set to low power

# 7.0 DEVICE CONFIGURATION INFORMATION

The Device Configuration Information (DCI) is a dedicated region in the Program Flash Memory mapped from 8200h to 821Fh. The data stored in the DCI memory is hard-coded into the device during manufacturing.

Refer to Table 7-1 for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and bootloader applications. These locations are read-only and cannot be erased or modified.

TABLE 7-1: DEVICE CONFIGURATION INFORMATION FOR PIC16(L)F15356/75/76/85/86 DEVICES

| ADDRESS | Name  | DESCRIPTION             | VALUE                      | UNITS   |

|---------|-------|-------------------------|----------------------------|---------|

| ADDRESS | Name  | DESCRIPTION             | PIC16(L)F15356/75/76/85/86 | UNITS   |

| 8200h   | ERSIZ | Erase Row Size          | 32                         | Words   |

| 8201h   | WLSIZ | Number of write latches | 32                         | Latches |

| 8202h   | URSIZ | Number of User Rows     | See Table 7-2              | Rows    |

| 8203h   | EESIZ | EE Data memory size     | 0                          | Bytes   |

| 8204h   | PCNT  | Pin Count               | See Table 7-3              | Pins    |

#### TABLE 7-2: MEMORY SIZE AND NUMBER OF USER ROWS

| Part Name         | Memory size | Number of user rows |

|-------------------|-------------|---------------------|

| PIC16(L)F15356    | 16K         | 512                 |

| PIC16(L)F15375/85 | 8K          | 256                 |

| PIC16(L)F15376/86 | 16K         | 512                 |

## **TABLE 7-3: PIN COUNT**

| Part Number       | Pin Count |

|-------------------|-----------|

| PIC16(L)F15356    | 28        |

| PIC16(L)F15375/76 | 40/44     |

| PIC16(L)F15385/86 | 48        |

## 7.1 DIA and DCI Access

The DIA and DCI data are read-only and cannot be erased or modified. See 13.3.6 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the DIA and DCI regions, similar to the Device ID and Revision ID.

# REGISTER 10-2: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|---------|---------|-----|-----|-----|---------|

| _     | _   | TMR0IE  | IOCIE   | _   | _   |     | INTE    |

| bit 7 |     |         |         |     |     |     | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedHS = Hardware set

bit 7-6 Unimplemented: Read as '0' bit 5 TMR0IE: Timer0 Overflow Interrupt Enable bit 1 = Enables the Timer0 interrupt 0 = Disables the Timer0 interrupt bit 4 IOCIE: Interrupt-on-Change Interrupt Enable bit 1 = Enables the IOC change interrupt 0 = Disables the IOC change interrupt bit 3-1 Unimplemented: Read as '0' bit 0 **INTE:** INT External Interrupt Flag bit<sup>(1)</sup> 1 = Enables the INT external interrupt 0 = Disables the INT external interrupt

Note 1: The External Interrupt GPIO pin is selected by INTPPS (Register 15-1).

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by PIE1-PIE7. Interrupt sources controlled by the PIE0 register do not require PEIE to be set in order to allow interrupt vectoring (when GIE is set).

# 11.0 POWER-SAVING OPERATION MODES

The purpose of the Power-Down modes is to reduce power consumption. There are three Power-Down modes: DOZE mode, IDLE mode, and SLEEP mode.

## 11.1 DOZE Mode

DOZE mode allows for power saving by reducing CPU operation and program memory (PFM) access, without affecting peripheral operation. DOZE mode differs from Sleep mode because the system oscillators continue to

operate, while only the CPU and PFM are affected. The reduced execution saves power by eliminating unnecessary operations within the CPU and memory.

When the Doze Enable (DOZEN) bit is set (DOZEN = 1), the CPU executes only one instruction cycle out of every N cycles as defined by the DOZE<2:0> bits of the CPUDOZE register. For example, if DOZE<2:0> = 100, the instruction cycle ratio is 1:32. The CPU and memory execute for one instruction cycle and then lay idle for 31 instruction cycles. During the unused cycles, the peripherals continue to operate at the system clock speed.

11.1.1 DOZE OPERATION

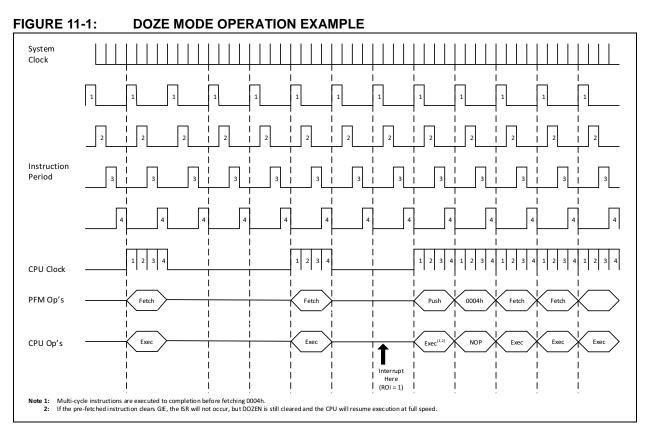

The Doze operation is illustrated in Figure 11-1. For this example:

- Doze enable (DOZEN) bit set (DOZEN = 1)

- DOZE<2:0> = 001 (1:4) ratio

- Recover-on-Interrupt (ROI) bit set (ROI = 1)

As with normal operation, the PFM fetches for the next instruction cycle. The Q-clocks to the peripherals continue throughout.

# PIC16(L)F15356/75/76/85/86

## 11.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- · Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- External interrupt pin/interrupt-on-change pins

- Timer1 (with external clock source)

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

Note:

The PIC16LF15356/75/76/85/86 does not have a configurable Low-Power Sleep mode. PIC16LF15356/75/76/85/86 is an unregulated device and is always in the lowest power state when in Sleep, with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC16F15356/75/76/85/86. See Section 37.0 "Electrical Specifications" for more information.

#### 11.3 IDLE Mode

When the Idle Enable (IDLEN) bit is clear (IDLEN = 0), the <code>SLEEP</code> instruction will put the device into full Sleep mode (see **Section 11.2 "Sleep Mode"**). When IDLEN is set (IDLEN = 1), the <code>SLEEP</code> instruction will put the device into IDLE mode. In IDLE mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to DOZE mode, except that in IDLE both the CPU and PFM are shut off.

Note:

Peripherals using Fosc will continue running while in Idle (but not in Sleep). Peripherals using HFINTOSC, LFINTOSC, or SOSC will continue running in both Idle and Sleep.

Note:

If CLKOUT is enabled (CLKOUT = 0, Configuration Word 1), the output will continue operating while in Idle.

#### 11.3.0.1 Idle and Interrupts

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can re-enter IDLE by executing the SLEEP instruction.

If Recover-on-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of Idle also restores full-speed CPU execution when doze is also enabled.

#### 11.3.0.2 Idle and WDT

When in IDLE, the WDT Reset is blocked and will instead wake the device. The WDT wake-up is not an interrupt, therefore ROI does not apply.

Note:

The WDT can bring the device out of IDLE, in the same way it brings the device out of Sleep. The DOZEN bit is not affected.

# 14.3 Register Definitions: PORTA

#### **REGISTER 14-1: PORTA: PORTA REGISTER**

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|---------|---------|-------|---------|---------|---------|

| RA7     | RA6     | RA5     | RA4     | RA3   | RA2     | RA1     | RA0     |

| bit 7   |         |         |         |       |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup>

1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register returns of actual I/O pin values.

#### **REGISTER 14-2: TRISA: PORTA TRI-STATE REGISTER**

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

# 21.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC1) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- · External VREF pins

- VDD supply voltage

- · FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- DAC1OUT pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DAC1EN bit of the DAC1CON0 register.

# 21.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DAC1R<4:0> bits of the DAC1CON1 register.

The DAC output voltage is determined by Equation 21-1:

#### **EQUATION 21-1: DAC OUTPUT VOLTAGE**

$$\begin{split} V_{OUT} &= \left( V_{SOURCE+} - V_{SOURCE-} \times \frac{DAC1R\langle 4:0 \rangle}{2^5} \right) + \left( V_{SOURCE-} \right) \\ V_{SOURCE+} &= V_{DD} \quad or \quad V_{REF+} \quad or \ FVR \\ V_{SOURCE-} &= V_{SS} \quad or \ V_{REF-} \end{split}$$

# 21.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 37-15.

#### 21.3 DAC Voltage Reference Output

The DAC voltage can be output to the DAC1OUT1/2 pins by setting the DAC1OE1/2 bits of the DAC1CON0 register, respectively. Selecting the DAC reference voltage for output on the DAC1OUT1/2 pins automatically overrides the digital output buffer and digital input threshold detector functions, disables the weak pull-up, and disables the current-controlled drive function of that pin. Reading the DAC1OUT1/2 pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to the DAC1OUT1/2 pins. Figure 21-2 shows an example buffering technique.

VPULLUP optional  $V_{DD}$ **RPULLUP ZCDxIN R**SERIES External **RPULLDOWN** Zcpinv voltage source optional ZCD Output for other modules ZCDxPOL ZCDxOUT pin Interrupt det Set ZCDxINTP ZCDxIF **ZCDxINTN** flag Interrupt det

**FIGURE 24-2:** SIMPLIFIED ZCD BLOCK DIAGRAM

# 27.5.8 LEVEL RESET, EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

In Level -Triggered One-Shot mode the timer count is reset on the external signal level and starts counting on the rising/falling edge of the transition from Reset level to the active level while the ON bit is set. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 01110)

- High Reset level (MODE<4:0> = 01111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control a new external signal edge is required after the ON bit is set to start the counter.

When Level-Triggered Reset One-Shot mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external signal edge that starts the timer. The PWM drive goes inactive when the timer count equals the CCPRx pulse width count. The PWM drive does not go active when the timer count clears at the PRx period count match.

# PIC16(L)F15356/75/76/85/86

## 31.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- · Data selection

- · Data gating

- · Logic function selection

- · Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

## 31.1.1 DATA SELECTION

There are 40 signals available as inputs to the configurable logic. Four 40-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 31-2. Data inputs in the figure are identified by a generic numbered input name.

Table 31-2 correlates the generic input name to the actual signal for each CLC module. The column labeled 'LCxDyS<4:0> Value' indicates the MUX selection code for the selected data input. LCxDyS is an abbreviation to identify specific multiplexers: LCxD1S<4:0> through LCxD4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 31-3 through Register 31-6).

TABLE 31-2: CLCx DATA INPUT SELECTION

| LCxDyS<4:0><br>Value   | CLCx Input Source      |

|------------------------|------------------------|

| 101000 to 111111 [40+] | Reserved               |

| 100111 [39]            | CWG1B output           |

| 100110 [38]            | CWG1A output           |

| 100101 [37]            | MSSP2 SCK output       |

| 100100 [36]            | MSSP2 SDO output       |

| 100011 [35]            | MSSP1 SCK output       |

| 100010 [34]            | MSSP1 SDO output       |

| 100001 [33]            | EUSART2 (TX/CK) output |

| 100000 [32]            | EUSART2 (DT) output    |

| 011111 [31]            | EUSART1 (TX/CK) output |

| 011110 [30]            | EUSART1 (DT) output    |

| 011101 [29]            | CLC4 output            |

| 011100 [28]            | CLC3 output            |

| 011011 [27]            | CLC2 output            |

| 011010 [26]            | CLC1 output            |

| 011001 [25]            | IOCIF                  |

| 011000 [24]            | ZCD output             |

| 010111 [23]            | C2OUT                  |

| 010110 [22]            | C1OUT                  |

| 010101 [21]            | NCO1 output            |

| 010100 [20]            | PWM6 output            |

| 010011 [19]            | PWM5 output            |

| 010010 [18]            | PWM4 output            |

| 010001 [17]            | PWM3 output            |

| 010000 [16]            | CCP2 output            |

| 001111 [15]            | CCP1 output            |

| 001110 [14]            | Timer2 overflow        |

| 001101 [13]            | Timer1 overflow        |

| 001100 [12]            | Timer0 overflow        |

| 001011 [11]            | CLKR                   |

| 001010 [10]            | ADCRC                  |

| 001001 [9]             | SOSC                   |

| 001000 [8]             | MFINTOSC (32 kHz)      |

| 000111 [7]             | MFINTOSC (500 kHz)     |

| 000110 [6]             | LFINTOSC               |

| 000101 [5]             | HFINTOSC               |

| 000100 [4]             | Fosc                   |

| 000011 [3]             | CLCIN3PPS              |

| 000010 [2]             | CLCIN2PPS              |

| 000001 [1]             | CLCIN1PPS              |

| 000000 [0]             | CLCIN0PPS              |

# **REGISTER 31-11: CLCDATA: CLC DATA OUTPUT**

| U-0   | U-0 | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | _   | _   | MLC4OUT | MLC3OUT | MLC2OUT | MLC1OUT |

| bit 7 |     |     |     | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'         |

|---------|------------------------------------|

| bit 3   | MLC4OUT: Mirror copy of LC4OUT bit |

| bit 2   | MLC3OUT: Mirror copy of LC3OUT bit |

| bit 1   | MLC2OUT: Mirror copy of LC2OUT bit |

| bit 0   | MLC10UT: Mirror copy of LC10UT bit |

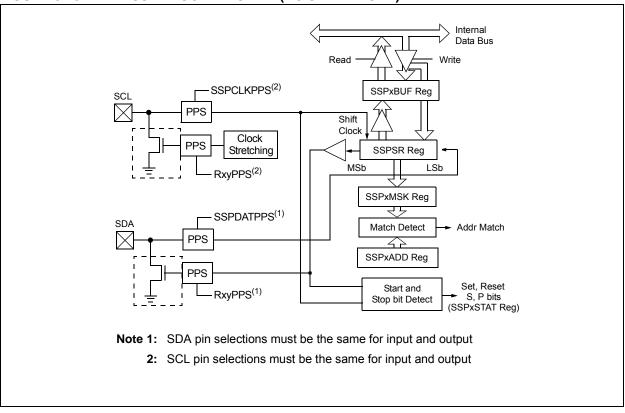

# FIGURE 32-3: MSSP BLOCK DIAGRAM (I<sup>2</sup>C SLAVE MODE)

# PIC16(L)F15356/75/76/85/86

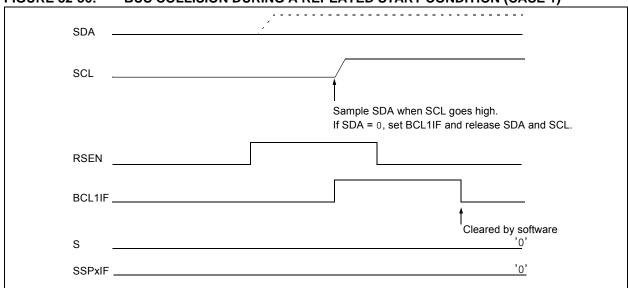

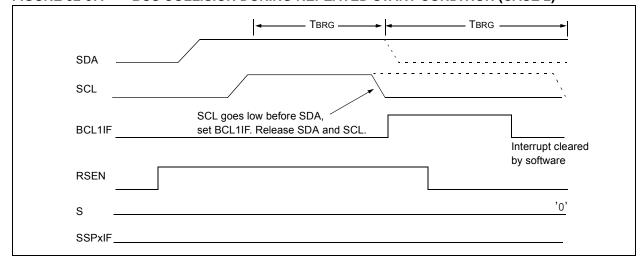

# 32.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 32-36). If SDA is sampled high, the BRG is reloaded and begins

counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 32-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

# FIGURE 32-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

| CALL             | Call Subroutine                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CALL k                                                                                                                                                                                                        |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Call Subroutine. First, return address (PC + 1) is pushed onto the stack. The 11-bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a 2-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow \underline{WDT} \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                               |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and PD are set.                            |

| CALLW            | Subroutine Call With W                                                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                     |

| Operation:       | $(PC) +1 \rightarrow TOS,$<br>$(W) \rightarrow PC<7:0>,$<br>$(PCLATH<6:0>) \rightarrow PC<14:8>$                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                     |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle |

| Complement f                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| [ label ] COMF f,d                                                                                                                                 |

| $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| $(\overline{f}) \rightarrow (destination)$                                                                                                         |

| Z                                                                                                                                                  |

| The contents of register 'f' are complemented. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'. |

|                                                                                                                                                    |

|                                                                                                                                                    |

| CLRF             | Clear f                                                        |

|------------------|----------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                 |

| Operands:        | $0 \leq f \leq 127$                                            |

| Operation:       | $00h \to (f)$ $1 \to Z$                                        |

| Status Affected: | Z                                                              |

| Description:     | The contents of register 'f' are cleared and the Z bit is set. |

instruction.

| DECF             | Decrement f                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                       |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                       |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                      |

| Status Affected: | Z                                                                                                                                        |

| Description:     | Decrement register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| CLRW             | Clear W                                    |

|------------------|--------------------------------------------|

| Syntax:          | [label] CLRW                               |

| Operands:        | None                                       |

| Operation:       | $00h \to (W)$ $1 \to Z$                    |

| Status Affected: | Z                                          |

| Description:     | W register is cleared. Zero bit (Z) is set |

# TABLE 37-3: POWER-DOWN CURRENT (IPD)(1,2)

| PIC16LF15356/75/76/85/86 |           |                                       |      | Standard Operating Conditions (unless otherwise stated)            |               |                |       |              |                       |

|--------------------------|-----------|---------------------------------------|------|--------------------------------------------------------------------|---------------|----------------|-------|--------------|-----------------------|

| PIC16F15356/75/76/85/86  |           |                                       |      | Standard Operating Conditions (unless otherwise stated) VREGPM = 1 |               |                |       |              |                       |

| Param.<br>No.            | Symbol    | Device Characteristics                | Min. | Тур.†                                                              | Max.<br>+85°C | Max.<br>+125°C | Units | VDD          | Conditions            |

| D200                     | IPD       | IPD Base                              | _    | 0.06                                                               | 2             | 9              | μΑ    | 3.0%         |                       |

| D200                     | IPD       | IPD Base                              | _    | 0.4                                                                | 4             | 12             | ~#A_  | 3.0V         |                       |

| D200A                    |           |                                       | _    | 18                                                                 | 22            | 27 \           | μA    | 3.04         | VREĞPM = 0            |

| D201                     | IPD_WDT   | Low-Frequency Internal Oscillator/WDT | 1    | 0.8                                                                | 4.0           | 11.5           | μĀ    | <b>73.0₩</b> |                       |

| D201                     | IPD_WDT   | Low-Frequency Internal Oscillator/WDT | _    | 0.9                                                                | 5.0 <         | 13             | μA    | 3.0V         |                       |

| D202                     | IPD_SOSC  | Secondary Oscillator (SOSC)           | _    | 0.6                                                                | /5_           | 13             | μA    | 3.0V         |                       |

| D202                     | IPD_SOSC  | Secondary Oscillator (SOSC)           | _    | 0.8                                                                | 8.5 ~         | 15             | μA    | 3.0V         |                       |

| D203                     | IPD_FVR   | FVR                                   | _    | 3/3                                                                | 47            | 47             | μΑ    | 3.0V         |                       |

| D203                     | IPD_FVR   | FVR                                   | -    | 28                                                                 | 44            | 44             | μΑ    | 3.0V         |                       |

| D204                     | IPD_BOR   | Brown-out Reset (BOR)                 | _^   | 10                                                                 | 17            | 19             | μΑ    | 3.0V         |                       |

| D204                     | IPD_BOR   | Brown-out Reset (BOR)                 | 7    | 14                                                                 | 18            | 20             | μΑ    | 3.0V         |                       |

| D205                     | IPD_LPBOR | Low-Power Brown-out Reset (LPBOR)     | _/   | 0.5                                                                | 4             | 10             | μΑ    | 3.0V         |                       |

| D207                     | IPD_ADCA  | ADC - Active                          | /-   | 250                                                                | $\nearrow$    | _              | μΑ    | 3.0V         | ADC is converting (4) |

| D207                     | IPD_ADCA  | ADC - Active                          | 7    | 280                                                                | _             | _              | μΑ    | 3.0V         | ADC is converting (4) |

| D208                     | IPD_CMP   | Comparator                            | 7    | 30                                                                 | 42            | 44             | μΑ    | 3.0V         |                       |

| D208                     | IPD_CMP   | Comparator                            |      | <b>3</b> 3                                                         | 44            | 45             | μΑ    | 3.0V         |                       |

Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not

The peripheral current is the sum of the base IDD and the additional current consumed when this peripheral is enabled. The Note 1: peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max. values should be used when calculating total current consumption.

The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode with all I/O pins in high-impedance state and tied to Vss.

All peripheral ourrents listed are on a per-peripheral basis if more than one instance of a peripheral is available.

ADC clock source is FRC,

**Preliminary** © 2016 Microchip Technology Inc. DS40001866A-page 524

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units | N        | <b>II</b> LLIMETER | S    |

|--------------------------|-------|----------|--------------------|------|

| Dimension Limits         |       | MIN      | NOM                | MAX  |

| Contact Pitch            | Е     | 1.27 BSC |                    |      |

| Contact Pad Spacing      | С     |          | 9.40               |      |

| Contact Pad Width (X28)  | Х     |          |                    | 0.60 |

| Contact Pad Length (X28) | Υ     |          |                    | 2.00 |

| Distance Between Pads    | Gx    | 0.67     |                    |      |

| Distance Between Pads    | G     | 7.40     |                    |      |

# Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

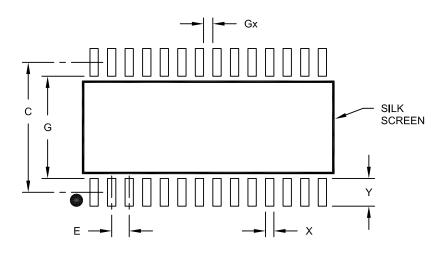

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

e: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS      |           |          |      |  |

|-------------------------|------------------|-----------|----------|------|--|

| Dimension               | MIN              | NOM       | MAX      |      |  |

| Number of Pins          | per of Pins N 44 |           |          |      |  |

| Pitch                   | е                | 0.65 BSC  |          |      |  |

| Overall Height          | Α                | 0.80 0.90 |          | 1.00 |  |

| Standoff                | A1               | 0.00      | 0.02     | 0.05 |  |

| Terminal Thickness      | A3               | 0.20 REF  |          |      |  |

| Overall Width           | Е                |           | 8.00 BSC |      |  |

| Exposed Pad Width       | E2               | 6.25      | 6.45     | 6.60 |  |

| Overall Length          | D                | 8.00 BSC  |          |      |  |

| Exposed Pad Length      | D2               | 6.25      | 6.45     | 6.60 |  |

| Terminal Width          | b                | 0.20      | 0.30     | 0.35 |  |

| Terminal Length         | L                | 0.30      | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | K                | 0.20      | -        | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103D Sheet 2 of 2