### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15356-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1: PIC16(L)F153XX FAMILY TYPES

| Device         | Data Sheet Index | Program Flash Memory (KW) | Program Flash Memory (KB) | Storage Area Flash (B) | Data SRAM<br>(bytes) | I/OPins | 10-bit ADC | 5-bit DAC | Comparator | 8-bit/ (with HLT) Timer | 16-bit Timer | Window Watchdog Timer | CCP/10-bit PWM | CWG | NCO | CLC | Zero-Cross Detect | Temperature Indicator | Memory Access Partition | <b>Device Information Area</b> | EUSART/ I <sup>2</sup> C-SPI | Peripheral Pin Select | Peripheral Module Disable | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------|---------------------------|------------------------|----------------------|---------|------------|-----------|------------|-------------------------|--------------|-----------------------|----------------|-----|-----|-----|-------------------|-----------------------|-------------------------|--------------------------------|------------------------------|-----------------------|---------------------------|----------------------|

| PIC16(L)F15313 | (C)              | 2                         | 3.5                       | 224                    | 256                  | 6       | 5          | 1         | 1          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Y                       | Y                              | 1/1                          | Y                     | Y                         | Ι                    |

| PIC16(L)F15323 | (C)              | 2                         | 3.5                       | 224                    | 256                  | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 1/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15324 | (D)              | 4                         | 7                         | 224                    | 512                  | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15325 | <b>(B)</b>       | 8                         | 14                        | 224                    | 1024                 | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15344 | (D)              | 4                         | 7                         | 224                    | 512                  | 18      | 17         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15345 | <b>(B)</b>       | 8                         | 14                        | 224                    | 1024                 | 18      | 17         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15354 | (A)              | 4                         | 7                         | 224                    | 512                  | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15355 | (A)              | 8                         | 14                        | 224                    | 1024                 | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15356 | (E)              | 16                        | 28                        | 224                    | 2048                 | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15375 | (E)              | 8                         | 14                        | 224                    | 1024                 | 36      | 35         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         |                      |

| PIC16(L)F15376 | (E)              | 16                        | 28                        | 224                    | 2048                 | 36      | 35         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15385 | (E)              | 8                         | 14                        | 224                    | 1024                 | 44      | 43         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15386 | (E)              | 16                        | 28                        | 224                    | 2048                 | 44      | 43         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Y                       | Y                              | 2/2                          | Υ                     | Y                         | Ι                    |

**Note 1:** I - Debugging integrated on chip.

### Data Sheet Index:

| ote: | For other small form | factor package availability and marking information, visit v |

|------|----------------------|--------------------------------------------------------------|

| E:   | DS40001866           | PIC16(L)F15356/75/76/85/86 Data Sheet, 28/40/48-Pin          |

| D:   | Future Release       | PIC16(L)F15324/44 Data Sheet, 14/20-Pin                      |

| C:   | Future Release       | PIC16(L)F15313/23 Data Sheet, 8/14-Pin                       |

| B:   | DS40001865           | PIC16(L)F15325/45 Data Sheet, 14/20-Pin                      |

| A:   | DS40001853           | PIC16(L)F15354/5 Data Sheet, 28-Pin                          |

|      |                      |                                                              |

**Note:** For other small form-factor package availability and marking information, visit www.microchip.com/packaging or contact your local sales office.

| Name                                                                                                  | Function            | Input<br>Type    | Output Type | Description                                                                                       |

|-------------------------------------------------------------------------------------------------------|---------------------|------------------|-------------|---------------------------------------------------------------------------------------------------|

| RA6/ANA6/CLKOUT/IOCA6/OSC1                                                                            | RA6                 | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                                       | ANA6                | AN               | —           | ADC Channel A6 input.                                                                             |

|                                                                                                       | CLKOUT              | _                | CMOS/OD     | Fosc/4 digital output (in non-crystal/resonator modes).                                           |

|                                                                                                       | IOCA6               | TTL/ST           | —           | Interrupt-on-change input.                                                                        |

|                                                                                                       | OSC1                | XTAL             | —           | External Crystal/Resonator (LP, XT, HS modes) driver input.                                       |

| RA7/ANA7/CLKIN/IOCA7/OSC2                                                                             | RA7                 | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                                       | ANA7                | AN               | _           | ADC Channel A7 input.                                                                             |

|                                                                                                       | CLKIN               | TTL/ST           | _           | External digital clock input.                                                                     |

|                                                                                                       | IOCA7               | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

|                                                                                                       | OSC2                | _                | XTAL        | External Crystal/Resonator (LP, XT, HS modes) driver output.                                      |

| RB0/ANB0/C2IN1+/ZCD1/ <del>SS2<sup>(1)</sup>/</del><br>CWG1 <sup>(1)</sup> /INT <sup>(1)</sup> /IOCB0 | RB0                 | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

| CWGTY/INTY/IOCB0                                                                                      | ANB0                | AN               | _           | ADC Channel B0 input.                                                                             |

|                                                                                                       | C2IN1+              | AN               | _           | Comparator positive input.                                                                        |

|                                                                                                       | ZCD1                | AN               | AN          | Zero-cross detect input pin (with constant current sink/source)                                   |

|                                                                                                       | SS2 <sup>(1)</sup>  | TTL/ST           | —           | MSSP2 SPI slave select input.                                                                     |

|                                                                                                       | CWG1 <sup>(1)</sup> | TTL/ST           | _           | Complementary Waveform Generator 1 input.                                                         |

|                                                                                                       | INT <sup>(1)</sup>  | TTL/ST           | _           | External interrupt request input.                                                                 |

|                                                                                                       | IOCB0               | TTL/ST           | —           | Interrupt-on-change input.                                                                        |

| RB1/ANB1/C1IN3-/C2IN3-/<br>SCL1 <sup>(1)</sup> /SCK1 <sup>(1)</sup> /IOCB1                            | RB1                 | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

| SCET ASCRT AUGBT                                                                                      | ANB1                | AN               | —           | ADC Channel B1 input.                                                                             |

|                                                                                                       | C1IN3-              | AN               | —           | Comparator negative input.                                                                        |

|                                                                                                       | C2IN3-              | AN               | —           | Comparator negative input.                                                                        |

|                                                                                                       | SCL1 <sup>(1)</sup> | I <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C input/output.                                                              |

|                                                                                                       | SCK1 <sup>(1)</sup> | TTL/ST           | CMOS/OD     | MSSP1 SPI clock input/output (default input location, SCK1 is a PPS remappable input and output). |

|                                                                                                       | IOCB1               | TTL/ST           | —           | Interrupt-on-change input.                                                                        |

| RB2/ANB2/SDA1 <sup>(1)</sup> /SDI1 <sup>(1)</sup> /IOCB2                                              | RB2                 | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                                       | ANB2                | AN               | —           | ADC Channel B2 input.                                                                             |

|                                                                                                       | SDA1 <sup>(1)</sup> | l <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                  |

|                                                                                                       | SDI1 <sup>(1)</sup> | TTL/ST           | _           | MSSP1 SPI serial data input (default input location, SDI1 is a PPS remappable input and output).  |

|                                                                                                       | IOCB2               | TTL/ST           | —           | Interrupt-on-change input.                                                                        |

| RB3/ANB3/C1IN2-/C2IN2-/IOCB3                                                                          | RB3                 | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                              |

|                                                                                                       | ANB3                | AN               | _           | ADC Channel B3 input.                                                                             |

|                                                                                                       | C1IN2-              | AN               | _           | Comparator negative input.                                                                        |

|                                                                                                       | C2IN2-              | AN               | _           | Comparator negative input.                                                                        |

|                                                                                                       | IOCB3               | TTL/ST           | _           | Interrupt-on-change input.                                                                        |

#### **TABLE 1-3:** PIC16(L)F15375/76 PINOUT DESCRIPTION (CONTINUED)

TTL = TTL compatible input HV = High Voltage

Note

= Crystal levels XTAL This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal. 1:

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options 2: as described in Table 15-5, Table 15-6 and Table 15-6.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

### REGISTER 5-3: CONFIGURATION WORD 3: WINDOWED WATCHDOG (CONTINUED)

bit 4-0 WDTCPS<4:0>: WDT Period Select bits

|                    |                    | WDTPS at      | POR             |                                    |                                 |

|--------------------|--------------------|---------------|-----------------|------------------------------------|---------------------------------|

| WDTCPS             | Value              | Divider Ratio |                 | Typical Time Out<br>(FIN = 31 kHz) | - Software Control<br>of WDTPS? |

| 11111 <b>(1)</b>   | 01011              | 1:65536       | 2 <sup>16</sup> | 2 s                                | Yes                             |

| 11110<br><br>10011 | 11110<br><br>10011 | 1:32          | 2 <sup>5</sup>  | 1 ms                               | No                              |

| 10010              | 10010              | 1:8388608     | 2 <sup>23</sup> | 256 s                              |                                 |

| 10001              | 10001              | 1:4194304     | 2 <sup>22</sup> | 128 s                              |                                 |

| 10000              | 10000              | 1:2097152     | 2 <sup>21</sup> | 64 s                               |                                 |

| 01111              | 01111              | 1:1048576     | 2 <sup>20</sup> | 32 s                               |                                 |

| 01110              | 01110              | 1:524299      | 2 <sup>19</sup> | 16 s                               |                                 |

| 01101              | 01101              | 1:262144      | 2 <sup>18</sup> | 8 s                                |                                 |

| 01100              | 01100              | 1:131072      | 2 <sup>17</sup> | 4 s                                |                                 |

| 01011              | 01011              | 1:65536       | 2 <sup>16</sup> | 2 s                                |                                 |

| 01010              | 01010              | 1:32768       | 2 <sup>15</sup> | 1 s                                |                                 |

| 01001              | 01001              | 1:16384       | 2 <sup>14</sup> | 512 ms                             | No                              |

| 01000              | 01000              | 1:8192        | 2 <sup>13</sup> | 256 ms                             |                                 |

| 00111              | 00111              | 1:4096        | 2 <sup>12</sup> | 128 ms                             |                                 |

| 00110              | 00110              | 1:2048        | 2 <sup>11</sup> | 64 ms                              |                                 |

| 00101              | 00101              | 1:1024        | 2 <sup>10</sup> | 32 ms                              |                                 |

| 00100              | 00100              | 1:512         | 2 <sup>9</sup>  | 16 ms                              |                                 |

| 00011              | 00011              | 1:256         | 2 <sup>8</sup>  | 8 ms                               |                                 |

| 00010              | 00010              | 1:128         | 2 <sup>7</sup>  | 4 ms                               |                                 |

| 00001              | 00001              | 1:64          | 2 <sup>6</sup>  | 2 ms                               |                                 |

| 00000              | 00000              | 1:32          | 2 <sup>5</sup>  | 1 ms                               |                                 |

**Note 1:** 0b11111 is the default value of the WDTCPS bits.

© 2016 Microchip Technology Inc.

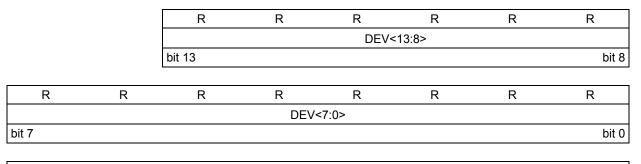

### 5.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. These locations can also be read from the NVMCON register.

### 5.7 Register Definitions: Device and Revision

### REGISTER 5-6: DEVID: DEVICE ID REGISTER

### Legend:

R = Readable bit

'1' = Bit is set

bit 13-0 **DEV<13:0>:** Device ID bits

| Device       | DEVID<13:0> Values                 |

|--------------|------------------------------------|

| PIC16F15356  | 11 0000 1011 0000 ( <b>30B0h</b> ) |

| PIC16LF15356 | 11 0000 1011 0001 ( <b>30B1h</b> ) |

| PIC16F15375  | 11 0000 1011 0010 ( <b>30B2h</b> ) |

| PIC16LF15375 | 11 0000 1011 0011 ( <b>30B3h</b> ) |

| PIC16F15376  | 11 0000 1011 0100 ( <b>30B4h</b> ) |

| PIC16LF15376 | 11 0000 1011 0101 ( <b>30B5h</b> ) |

| PIC16F15385  | 11 0000 1011 0110 ( <b>30B6h</b> ) |

| PIC16LF15385 | 11 0000 1011 0111 ( <b>30B7h</b> ) |

| PIC16F15386  | 11 0000 1011 1000 ( <b>30B8h</b> ) |

| PIC16LF15386 | 11 0000 1011 1001 ( <b>30B9h</b> ) |

'0' = Bit is cleared

### 8.3 Register Definitions: Brown-out Reset Control

### REGISTER 8-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u               | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-----------------------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN <sup>(1)</sup> | —   | —   | —   | _   | —   | —   | BORRDY |

| bit 7                 |     |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit <sup>(1)</sup> |

|---------|------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words $\neq 01$ :          |

|         | SBOREN is read/write, but has no effect on the BOR.        |

|         | If BOREN <1:0> in Configuration Words = 01:                |

|         | 1 = BOR Enabled                                            |

|         | 0 = BOR Disabled                                           |

| bit 6-1 | Unimplemented: Read as '0'                                 |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit           |

|         | 1 = The Brown-out Reset circuit is active                  |

|         |                                                            |

0 = The Brown-out Reset circuit is inactive

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

|       | . 1001 |     |     |     |     |            |       |

|-------|--------|-----|-----|-----|-----|------------|-------|

| U-0   | U-0    | U-0 | U-0 | U-0 | U-0 | R/W/HC-1/u | U-0   |

| —     | _      | -   | —   | —   | —   | MEMV       | —     |

| bit 7 |        |     |     |     |     |            | bit 0 |

|       |        |     |     |     |     |            |       |

### REGISTER 8-3: PCON1: POWER CONTROL REGISTER 0

| Legend:                         |                      |                                                       |  |  |  |  |  |  |  |

|---------------------------------|----------------------|-------------------------------------------------------|--|--|--|--|--|--|--|

| HC = Bit is cleared by hardware |                      |                                                       |  |  |  |  |  |  |  |

| R = Readable bit                | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |  |  |  |  |  |

| u = Bit is unchanged            | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |  |  |  |

| '1' = Bit is set                | '0' = Bit is cleared | q = Value depends on condition                        |  |  |  |  |  |  |  |

| bit 7-2 | Unimplemented: Read as '0'                                                                     |

|---------|------------------------------------------------------------------------------------------------|

| bit 1   | MEMV: Memory Violation Flag bit                                                                |

|         | 1 = No Memory Violation Reset occurred or set to '1' by firmware.                              |

|         | 0 = A Memory Violation Reset occurred (set to '0' in hardware when a Memory Violation occurs)) |

| bit 0   | Unimplemented: Read as '0'                                                                     |

### TABLE 8-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |

|---------|--------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| BORCON  | SBOREN | _      | _     |       | _     |        |       | BORRDY | 117                 |

| PCON0   | STKOVF | STKUNF | WDTWV | RWDT  | RMCLR | RI     | POR   | BOR    | 124                 |

| PCON1   | —      | _      | —     | —     | _     | _      | MEMV  | —      | 124                 |

| STATUS  | _      | _      | _     | TO    | PD    | Z      | DC    | С      | 54                  |

| WDTCON0 |        |        |       | V     |       | SWDTEN | 175   |        |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

### TABLE 12-2: WDT CLEARING CONDITIONS

| Conditions                                       | WDT        |

|--------------------------------------------------|------------|

| WDTE<1:0> = 00                                   |            |

| WDTE<1:0> = 01 and SWDTEN = 0                    |            |

| WDTE<1:0> = 10 and enter Sleep                   | Cleared    |

| CLRWDT Command                                   | Cleared    |

| Oscillator Fail Detected                         |            |

| Exit Sleep + System Clock = SOSC, EXTOSC, INTOSC |            |

| Change INTOSC divider (IRCF bits)                | Unaffected |

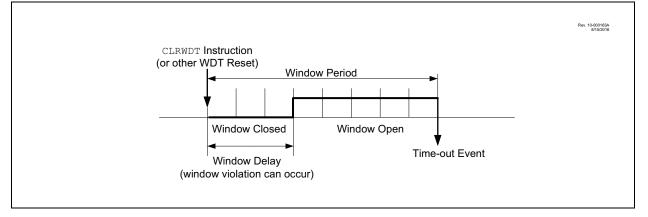

### FIGURE 12-2: WINDOW PERIOD AND DELAY

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2   | ODCD1   | ODCD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

ODCD<7:0>: PORTD Open-Drain Enable bits

For RD<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

### REGISTER 14-31: SLRCOND: PORTD SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRD<7:0>: PORTD Slew Rate Enable bits

For RD<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

### REGISTER 14-32: INLVLD: PORTD INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLD<7:0>: PORTD Input Level Select bits

For RD<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

### 14.10 PORTE Registers

### 14.10.1 DATA REGISTER

PORTE is a 4-bit wide port. The corresponding data direction register is TRISE (Register 14-33). Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize PORTE.

Reading the PORTE register (Register 14-33) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATE).

### 14.10.2 DIRECTION CONTROL

The TRISE register (Register 14-34) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

| Note: | The TRISE3 bit is a read-only bit and it |

|-------|------------------------------------------|

|       | always reads a '1'.                      |

### 14.10.3 OPEN-DRAIN CONTROL

The ODCONE register (Register 14-38) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONE bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONE bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for I <sup>2</sup> C; the I <sup>2</sup> C |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                                       |

### 14.10.4 SLEW RATE CONTROL

The SLRCONE register (Register 14-39) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONE bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONE bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

### 14.10.5 INPUT THRESHOLD CONTROL

The INLVLE register (Register 14-40) controls the input voltage threshold for each of the available PORTE input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTE register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 14.10.6 ANALOG CONTROL

The ANSELE register (Register 14-36) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELE bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELE bits has no effect on digital output functions. A pin with TRIS clear and ANSELE set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELE bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

### 14.10.7 WEAK PULL-UP CONTROL

The WPUE register (Register 14-37) controls the individual weak pull-ups for each port pin.

## 14.10.8 PORTE FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| Output Signal | RxyPPS                   |       | Re    | mappable to | Pins of POR | Tx    |       |

|---------------|--------------------------|-------|-------|-------------|-------------|-------|-------|

| Name          | RxyPP5<br>Register Value |       |       | PIC16(L)F   | 15385/86    |       |       |

|               | 5                        | PORTA | PORTB | PORTC       | PORTD       | PORTE | PORTF |

| CLKR          | 0x1B                     |       | •     |             |             | •     |       |

| NCO1OUT       | 0x1A                     | •     |       |             | •           |       |       |

| TMR0          | 0x19                     |       |       | •           |             |       | •     |

| SDO2/SDA2     | 0x18                     |       | •     |             | •           |       |       |

| SCK2/SCL2     | 0X17                     |       | •     |             | •           |       |       |

| SDO1/SDA1     | 0x16                     |       | •     | •           |             |       |       |

| SCK1/SCL1     | 0x15                     |       | •     | •           |             |       |       |

| C2OUT         | 0x14                     | ٠     |       |             |             | •     |       |

| C1OUT         | 0x13                     | ٠     |       |             | •           |       |       |

| DT2           | 0x12                     |       | •     | •           |             |       |       |

| TX2/CK2       | 0x11                     |       | •     |             | •           |       |       |

| DT1           | 0x10                     |       |       | •           |             |       | ٠     |

| TX1/CK1       | 0x0F                     |       |       | •           |             |       | ٠     |

| PWM6OUT       | 0x0E                     | ٠     |       |             | •           |       |       |

| PWM5OUT       | 0x0D                     | ٠     |       |             |             |       | •     |

| PWM4OUT       | 0x0C                     |       | •     |             | •           |       |       |

| PWM3OUT       | 0x0B                     |       | •     |             | •           |       |       |

| CCP2          | 0x0A                     |       |       | •           |             |       | •     |

| CCP1          | 0x09                     |       |       | •           |             |       | •     |

| CWG1D         | 0x08                     |       | •     |             | •           |       |       |

| CWG1C         | 0x07                     |       | •     |             | •           |       |       |

| CWG1B         | 0x06                     |       | •     |             | •           |       |       |

| CWG1A         | 0x05                     |       | •     | •           |             |       |       |

| CLC4OUT       | 0x04                     |       | •     |             | •           |       |       |

| CLC3OUT       | 0x03                     |       | •     |             | •           |       |       |

| CLC2OUT       | 0x02                     | •     |       |             |             |       | •     |

| CLC1OUT       | 0x01                     | •     |       |             |             |       | •     |

### TABLE 15-7: PPS OUTPUT SIGNAL ROUTING OPTIONS (PIC16(L)F15385/86)

| REGISTER        | 16-6: PMD5                     | 5 – PMD CON      | ITROL REGI | STER 5         |                  |                  |             |

|-----------------|--------------------------------|------------------|------------|----------------|------------------|------------------|-------------|

| U-0             | U-0                            | U-0              | R/W-0/0    | R/W-0/0        | R/W-0/0          | R/W-0/0          | U-0         |

| —               | —                              | —                | CLC4MD     | CLC3MD         | CLC2MD           | CLC1MD           | —           |

| bit 7           |                                |                  |            |                |                  |                  | bit 0       |

|                 |                                |                  |            |                |                  |                  |             |

| Legend:         |                                |                  |            |                |                  |                  |             |

| R = Readabl     | e bit                          | W = Writable     | bit        | U = Unimplem   | nented bit, read | l as '0'         |             |

| u = Bit is und  | changed                        | x = Bit is unkr  | nown       | -n/n = Value a | t POR and BO     | R/Value at all o | ther Resets |

| '1' = Bit is se | t                              | '0' = Bit is cle | ared       | q = Value dep  | ends on condit   | ion              |             |

|                 |                                |                  |            |                |                  |                  |             |

| bit 7-5         | Unimplemen                     | ted: Read as '   | D'         |                |                  |                  |             |

| bit 4           | CLC4MD: Dis                    | able CLC4 bit    |            |                |                  |                  |             |

|                 | 1 = CLC4 mc                    | dule disabled    |            |                |                  |                  |             |

|                 | 0 = CLC4 mc                    | dule enabled     |            |                |                  |                  |             |

| bit 3           | bit 3 CLC3MD: Disable CLC3 bit |                  |            |                |                  |                  |             |

|                 | 1 = CLC3 mc                    |                  |            |                |                  |                  |             |

|                 | 0 = CLC3 module enabled        |                  |            |                |                  |                  |             |

| bit 2           | CLC2MD: Dis                    | able CLC2 bit    |            |                |                  |                  |             |

|                 | 1 = CLC2 mc                    |                  |            |                |                  |                  |             |

|                 | 0 = CLC2 mc                    |                  |            |                |                  |                  |             |

| bit 1           | CLC1MD: Dis                    |                  |            |                |                  |                  |             |

|                 | 1 = CLC1 mc                    |                  |            |                |                  |                  |             |

|                 | 0 = CLC1 mc                    |                  | <u>.</u>   |                |                  |                  |             |

| bit 0           | Unimplemen                     | ted: Read as '   | J          |                |                  |                  |             |

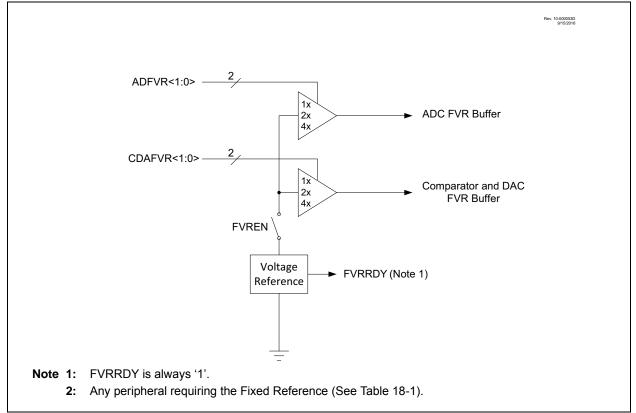

## 18.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · ADC positive reference

- · Comparator positive and negative input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

### 18.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 20.0 "Analog-to-Digital Converter (ADC) Module"** for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" and Section 23.0 "Comparator Module" for additional information.

### 18.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize.

FVRRDY is an indicator of the reference being ready. In the case of an LF device, or a device on which the BOR is enabled in the Configuration Word settings, then the FVRRDY bit will be high prior to setting FVREN as those module require the reference voltage.

FIGURE 18-1: VOLTAGE REFERENCE BLOCK DIAGRAM

### REGISTER 22-3: NCO1ACCL: NCO1 ACCUMULATOR REGISTER – LOW BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCO1A   | CC<7:0> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 NCO1ACC<7:0>: NCO1 Accumulator, Low Byte

### REGISTER 22-4: NCO1ACCH: NCO1 ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCO1ACC | C<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 NOC1ACC<15:8>: NCO1 Accumulator, High Byte

### REGISTER 22-5: NCO1ACCU: NCO1 ACCUMULATOR REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | —   | _   | —   |         | NCO1AC  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1ACC<19:16>: NCO1 Accumulator, Upper Byte

**Note 1:** The accumulator spans registers NCO1ACCU:NCO1ACCH: NCO1ACCL. The 24 bits are reserved but not all are used. This register updates in real-time, asynchronously to the CPU; there is no provision to guarantee atomic access to this 24-bit space using an 8-bit bus. Writing to this register while the module is operating will produce undefined results.

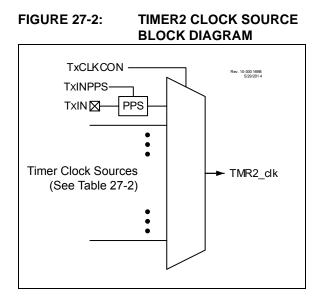

## 27.1 Timer2 Operation

Timer2 operates in three major modes:

- Free Running Period

- One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 27-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- · any device Reset

- External Reset Source event that resets the timer.

| Note: | TMR2 is  | s not | cleared | when | T2CON | is |

|-------|----------|-------|---------|------|-------|----|

|       | written. |       |         |      |       |    |

### 27.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each TMR2\_clk cycle. When the two values match, the comparator resets the value of TMR2 to 00h on the next rising TMR2\_clk edge and increments

the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register, a one TMR2\_clk period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

### 27.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

### 27.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

## 27.2 Timer2 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- The ADC module, as an Auto-conversion Trigger

- · COG, as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See **Section 28.0** "**Capture/Compare/PWM Modules**" for more details on setting up Timer2 for use with the CCP, as well as the timing diagrams in **Section 27.5** "**Operation Examples**" for examples of how the varying Timer2 modes affect CCP PWM output.

## 27.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2 with the T2RST register. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

## 28.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

The Capture/Compare/PWM modules available are shown in Table 28-1.

| TABLE 28-1: AVAILABLE CCP MODULE |

|----------------------------------|

|----------------------------------|

| Device                     | CCP1 | CCP2 |

|----------------------------|------|------|

| PIC16(L)F15356/75/76/85/86 | •    | •    |

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                               |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                     |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                          |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                            |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                          |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                          |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                         |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |  |

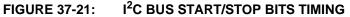

## TABLE 37-24: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Param.<br>No. | Symbol  | Charact         | eristic      | Min. | Тур          | Max. | Units | Conditions                                            |

|---------------|---------|-----------------|--------------|------|--------------|------|-------|-------------------------------------------------------|

| SP90*         | TSU:STA | Start condition | 100 kHz mode | 4700 | $\checkmark$ | _    | ns    | Only relevant for Repeated Start condition            |

|               |         | Setup time      | 400 kHz mode | 600  |              | _    |       |                                                       |

| SP91*         | THD:STA | Start condition | 100 kHzmode  | 4000 | _            | _    | ns    | After this period, the first clock pulse is generated |

|               |         | Hold time       | 400 kHz mode | 600  | _            | _    |       |                                                       |

| SP92*         | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _            | _    | ns    |                                                       |

|               |         | Setup time      | 400 kHz mode | 600  | _            | _    |       |                                                       |

| SP93          | THD:STO | Stop condition  | 100 kHz mode | 4000 | _            | _    | ns    |                                                       |

|               |         | Hold time       | 400 kHz mode | 600  | -            | —    |       |                                                       |

These parameters are characterized but not tested.

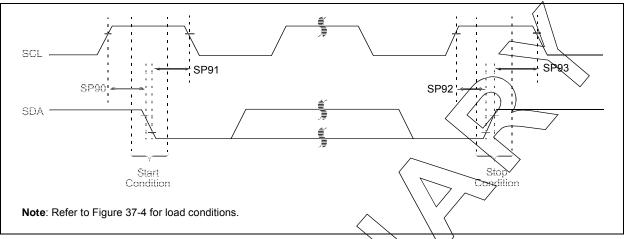

### 12C BUS DATA TIMING **FIGURE 37-22:**

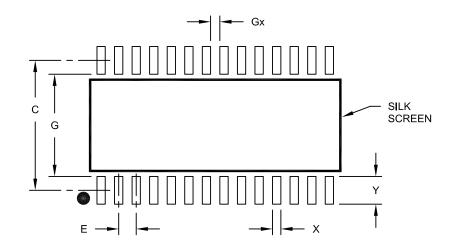

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units |          |      |      |  |  |

|--------------------------|-------|----------|------|------|--|--|

| Dimension                | MIN   | NOM      | MAX  |      |  |  |

| Contact Pitch            | Е     | 1.27 BSC |      |      |  |  |

| Contact Pad Spacing      | С     |          | 9.40 |      |  |  |

| Contact Pad Width (X28)  | Х     |          |      | 0.60 |  |  |

| Contact Pad Length (X28) | Y     |          |      | 2.00 |  |  |

| Distance Between Pads    | Gx    | 0.67     |      |      |  |  |

| Distance Between Pads    | G     | 7.40     |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A