### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

÷ХГ

| 2000                       |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 28KB (16K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15356t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# \_ \_ \_ CLKOUT/ OSC1 CLKIN/ OSC2 \_ \_ \_ \_ \_ \_ ICSPCLK ICSPDAT

Pull-up

Y

Y

Y

Y

Y

Y

Υ

Y

Υ

Y

Υ

Υ

Υ

Y

Y

\_

\_

Basic

\_

| 2<br>2<br>2<br>2<br>2<br>2<br>3<br>3<br>3 | 48-Pin UQFN/T | ADC                          | Reference | Comparato        | NCO | DAC      | Timers                        | ССР                 | MWA | CWG                 | dssm                          | ZCD  | EUSART                    | CLC                   | ССКК | Interrupt                   |

|-------------------------------------------|---------------|------------------------------|-----------|------------------|-----|----------|-------------------------------|---------------------|-----|---------------------|-------------------------------|------|---------------------------|-----------------------|------|-----------------------------|

| 2<br>2<br>2<br>2<br>2<br>3<br>3<br>3      | 21            | ANA0                         | -         | C1IN0-<br>C2IN0- |     | —        | -                             | -                   |     | -                   | -                             |      | —                         | CLCIN0 <sup>(1)</sup> |      | IOCA0                       |

| 2<br>2<br>2<br>2<br>3<br>3<br>3           | 22            | ANA1                         |           | C1IN1-<br>C2IN1- | _   | —        | _                             | _                   | _   | _                   | _                             | _    | —                         | CLCIN1 <sup>(1)</sup> | l    | IOCA1                       |

| 22                                        | 23            | ANA2                         | Ι         | C1IN0+<br>C2IN0+ | -   | DAC1OUT1 | -                             | -                   | -   | -                   | -                             | -    | —                         | -                     |      | IOCA2                       |

| 3                                         | 24            | ANA3                         | VREF+     | C1IN1+           | _   | DACREF+  | _                             | _                   | _   | _                   | _                             | _    | _                         | _                     | -    | IOCA3                       |

| 3                                         | 25            | ANA4                         | _         | C1IN1-           | _   | _        | T0CKI <sup>(1)</sup>          | _                   | _   | _                   | _                             | _    | —                         | _                     |      | IOCA4                       |

| 3                                         | 26            | ANA5<br>ADACT                |           |                  |     | _        | T1G <sup>(1)</sup>            |                     |     |                     | SS1 <sup>(1)</sup>            |      | —                         | —                     |      | IOCA5                       |

|                                           | 33            | ANA6                         | -         | _                | _   | —        | _                             | _                   | _   | _                   | _                             | _    | —                         | —                     |      | IOCA6                       |

|                                           | 32            | ANA7                         |           |                  | -   | _        |                               | -                   | -   | -                   | -                             | -    | —                         | -                     |      | IOCA7                       |

|                                           | 8             | ANB0                         |           | C2IN1+           | —   | _        | -                             | -                   | _   | CWG1 <sup>(1)</sup> | SS2 <sup>(1)</sup>            | ZCD1 | -                         | —                     |      | INT <sup>(1)</sup><br>IOCB0 |

| 9                                         | 9             | ANB1                         |           | C1IN3-<br>C2IN3- |     | _        |                               |                     |     |                     | SCL1<br>SCK1 <sup>(1,4)</sup> |      | —                         | —                     |      | IOCB1                       |

| 1                                         | 10            | ANB2                         | Ι         | -                | -   | _        | -                             | -                   | -   | -                   | SDA1<br>SDI1 <sup>(1,4)</sup> | -    | —                         | -                     |      | IOCB2                       |

| 1                                         | 11            | ANB3                         |           | C1IN2-<br>C2IN2- | _   | _        |                               | -                   | _   | -                   | -                             | -    | —                         | —                     |      | IOCB3                       |

| 1                                         | 16            | ANB4<br>ADACT <sup>(1)</sup> | I         |                  |     | _        |                               |                     |     |                     |                               |      | —                         | —                     |      | IOCB4                       |

| 1                                         | 17            | ANB5                         | -         | _                | _   | _        | _                             | _                   | -   | _                   | _                             |      | —                         | _                     | Ι    | IOCB5                       |

| 1                                         | 18            | ANB6                         | Ι         | -                | -   | _        | -                             | -                   | -   | -                   | -                             | -    | TX2<br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> |      | IOCB6                       |

| 1                                         | 19            | ANB7                         |           |                  | _   | DAC1OUT2 |                               | -                   | _   |                     |                               |      | RX2<br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> |      | IOCB7                       |

| 3                                         | 34            | ANC0                         | -         | —                | —   | _        | SOSCO<br>T1CKI <sup>(1)</sup> | -                   | -   |                     | —                             |      | -                         | —                     |      | IOCC0                       |

| 3                                         | 35            | ANC1                         | _         | _                | _   | _        | SOSCI                         | CCP2 <sup>(1)</sup> | _   | _                   | _                             | _    | _                         | _                     | _    | IOCC1                       |

### 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) TABLE 5:

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Note 1:

All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options. 2:

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

TQFP

I/O<sup>(2)</sup>

RA0 RA1

RA2

RA3

RA4

RA5

RA6

RA7

RB0

RB1

RB2

RB3

RB4

RB5

RB6

RB7

RC0

RC1

| Н |          |

|---|----------|

|   | _        |

|   |          |

|   |          |

|   |          |

|   |          |

|   | <b>O</b> |

|   |          |

|   |          |

|   | Ŧ        |

|   |          |

|   |          |

|   |          |

|   | 35       |

|   |          |

|   | 5        |

|   |          |

|   | UT I     |

|   |          |

|   |          |

|   | 6        |

| I |          |

| I | 85/      |

| I |          |

| I | 8        |

| I | ő        |

| н |          |

Preliminary

| I/O <sup>(2)</sup> | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO | DAC | Timers              | CCP                 | MWM | SWC | ASSM                          | ZCD | EUSART                    | CLC | CLKR | Interrupt | Pull-up | Basic       |

|--------------------|------------------|------|-----------|------------|-----|-----|---------------------|---------------------|-----|-----|-------------------------------|-----|---------------------------|-----|------|-----------|---------|-------------|

| RC2                | 40               | ANC2 | —         | —          | —   | _   | —                   | CCP1 <sup>(1)</sup> | -   | —   | —                             |     | —                         | -   | —    | IOCC2     | Y       | —           |

| RC3                | 41               | ANC3 | -         | -          | -   | _   | T2IN <sup>(1)</sup> | -                   | _   | _   | SCL1<br>SCL2 <sup>(1,4)</sup> | _   | —                         | _   | -    | IOCC3     | Y       | -           |

| RC4                | 46               | ANC4 | -         | _          | _   | _   | -                   | —                   | _   | -   | SDA1<br>SDI1 <sup>(1,4)</sup> | _   | —                         | _   | _    | IOCC4     | Y       | _           |

| RC5                | 47               | ANC5 | _         | —          | _   | _   | _                   | _                   | _   | _   | _                             | _   | —                         | _   | _    | IOCC5     | Υ       | _           |

| RC6                | 48               | ANC6 | -         | —          | —   | _   | —                   | —                   | _   | —   | —                             |     | TX1<br>CK1 <sup>(1)</sup> | _   | -    | IOCC6     | Y       | —           |

| RC7                | 1                | ANC7 | -         | —          | —   | _   | —                   | —                   | _   | —   | _                             |     | RX1<br>DT1 <sup>(1)</sup> | _   | -    | IOCC7     | Y       | —           |

| RD0                | 42               | AND0 | -         | —          | -   | -   | -                   | —                   | —   | -   | SCK2<br>SCL2 <sup>(1,4)</sup> | —   | -                         | —   | -    | -         | Y       | —           |

| RD1                | 43               | AND1 | —         | —          | —   |     | —                   | —                   | _   | —   | SDA2<br>SDI2 <sup>(1,4)</sup> |     | _                         | _   | -    | —         | Y       | —           |

| RD2                | 44               | AND2 | _         | _          | —   | _   | _                   | _                   | -   | _   | _                             | _   | —                         | -   | _    | _         | Y       | _           |

| RD3                | 45               | AND3 | _         | _          | _   | _   | _                   | _                   |     | _   | _                             |     | _                         |     | —    | _         | Y       | _           |

| RD4                | 2                | AND4 | _         | _          | —   | _   | _                   | —                   | _   | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RD5                | 3                | AND5 | _         | —          | —   | _   | _                   | —                   | -   | _   | _                             | -   | _                         | -   | _    | _         | Υ       | _           |

| RD6                | 4                | AND6 | _         | _          | —   | _   | _                   | _                   | _   | —   | _                             | _   | _                         | _   | _    | —         | Υ       | _           |

| RD7                | 5                | AND7 | —         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE0                | 27               | ANE0 | -         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE1                | 28               | ANE1 | _         | —          | —   | _   | -                   | —                   | _   | -   | _                             | _   | _                         | _   | —    | -         | Υ       | —           |

| RE2                | 29               | ANE2 | _         | —          | —   | —   | —                   | —                   | —   | —   | —                             | _   | —                         | —   | —    | —         | Y       | —           |

| RE3                | 20               | _    | -         | —          | —   |     | —                   | —                   | _   | —   | —                             | _   | —                         | _   | _    | IOCE3     | Y       | MCLR<br>VPP |

| RF0                | 36               | ANF0 | _         | _          | —   | _   | —                   | _                   | _   | —   | _                             |     | _                         | _   | _    | —         | Υ       | _           |

| RF1                | 37               | ANF1 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF2                | 38               | ANF2 | _         | —          | —   | _   | -                   | _                   | _   | —   | —                             | _   | —                         | _   | —    | —         | Υ       | _           |

| RF3                | 39               | ANF3 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF4                | 12               | ANF4 | —         | —          | —   |     | —                   | —                   |     | _   | _                             |     | _                         |     | —    | —         | Υ       | —           |

TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

### 9.2.1.4 4x PLL

The oscillator module contains a PLL that can be used with external clock sources and internal oscillator to provide a system clock source. The input frequency for the PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 37-9.

The PLL may be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to enable the EXTOSC with 4x PLL.

- 2. Write the NOSC bits in the OSCCON1 register to enable the EXTOSC with 4x PLL.

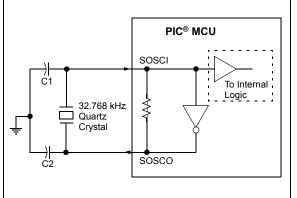

### 9.2.1.5 Secondary Oscillator

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 32.768 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. Refer to **Section 9.3 "Clock Switching"** for more information.

### FIGURE 9-5: QUARTZ CRYSTAL OPERATION (SECONDARY OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

| R/W-0/0                                                                                           | R/W-0/0                                                      | R/W-0/0                                                  | R/W-0/0        | U-0         | U-0              | U-0 | R/W-0/0 |  |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|----------------|-------------|------------------|-----|---------|--|

| CLC4IE                                                                                            | CLC3IE                                                       | CLC2IE                                                   | CLC1IE         | —           | —                | —   | TMR1GIE |  |

| bit 7                                                                                             |                                                              |                                                          |                |             |                  |     | bit 0   |  |

|                                                                                                   |                                                              |                                                          |                |             |                  |     |         |  |

| Legend:                                                                                           |                                                              |                                                          |                |             |                  |     |         |  |

| R = Readab                                                                                        |                                                              | W = Writable                                             |                | •           | mented bit, read |     |         |  |

| u = Bit is unchanged $x = Bit is unknown$ $-n/n = Value at POR and BOR/Value at all other Resets$ |                                                              |                                                          |                |             |                  |     |         |  |

| '1' = Bit is se                                                                                   | et                                                           | '0' = Bit is cle                                         | ared           | HS = Hardwa | are set          |     |         |  |

| bit 7                                                                                             | 1 = CLC4 i                                                   | C4 Interrupt Ena<br>nterrupt enabled<br>nterrupt disable | t              |             |                  |     |         |  |

| bit 6                                                                                             | 1 = CLC3 i                                                   | C3 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable | b              |             |                  |     |         |  |

| bit 5                                                                                             | 1 = CLC2 i                                                   | C2 Interrupt Ena<br>nterrupt enabled<br>nterrupt disable | t              |             |                  |     |         |  |

| bit 4                                                                                             | 1 = CLC1 i                                                   | C1 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable | b              |             |                  |     |         |  |

| bit 3-1                                                                                           | Unimpleme                                                    | nted: Read as '                                          | 0'             |             |                  |     |         |  |

| bit 0                                                                                             | 1 = Enable                                                   | imer1 Gate Inte<br>s the Timer1 ga<br>s the Timer1 ga    | te acquisition | interrupt   |                  |     |         |  |

| s                                                                                                 | Bit PEIE of the IN<br>set to enable a<br>controlled by regis | any peripheral                                           | interrupt      |             |                  |     |         |  |

### REGISTER 10-7: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

| R/W/HS-0       | 0/0 R/W/HS-0/0                           | R/W/HS-0/0                           | R/W/HS-0/0      | R/W/HS-0/0       | R/W/HS-0/0                          | R/W/HS-0/0       | R/W/HS-0/0     |

|----------------|------------------------------------------|--------------------------------------|-----------------|------------------|-------------------------------------|------------------|----------------|

| RC2IF          | TX2IF                                    | RC1IF                                | TX1IF           | BCL2IF           | SSP2IF                              | BCL1IF           | SSP1IF         |

| bit 7          |                                          |                                      |                 |                  |                                     |                  | bit (          |

|                |                                          |                                      |                 |                  |                                     |                  |                |

| Legend:        |                                          |                                      |                 |                  |                                     |                  |                |

| R = Reada      |                                          | W = Writable                         | bit             | •                | mented bit, read                    |                  |                |

| u = Bit is u   | •                                        | x = Bit is unkr                      |                 |                  | at POR and BO                       | R/Value at all c | other Resets   |

| '1' = Bit is s | set                                      | '0' = Bit is cle                     | ared            | HS = Hardwa      | re clearable                        |                  |                |

| bit 7          | BCOLE. EUS                               | ART2 Receive                         | ntorrunt Elog   | (Road Only) bi   | (1)                                 |                  |                |

|                |                                          |                                      |                 |                  | at least one by                     | te)              |                |

|                |                                          | SART2 receive                        |                 |                  | at least one by                     | ,                |                |

| bit 6          | TX2IF: EUSA                              | RT2 Transmit                         | Interrupt Flag  | (Read-Only) b    | it(2)                               |                  |                |

|                |                                          |                                      |                 |                  | unoccupied spa                      |                  |                |

|                | 0 = The EUS<br>TXxREG                    |                                      | it buffer is cu | rrently full. Th | ne application f                    | irmware should   | d not write to |

| bit 5          |                                          | ART1 Receive                         | nterrupt Flag   | (read-only) bit  | (1)                                 |                  |                |

|                |                                          |                                      |                 |                  | at least one by                     | te)              |                |

|                |                                          | SART1 receive                        |                 |                  | -                                   | ,                |                |

| bit 4          |                                          | RT1 Transmit                         |                 |                  |                                     |                  |                |

|                |                                          |                                      |                 |                  | unoccupied sp                       |                  | d wat unite t  |

|                |                                          |                                      |                 |                  | ne application f<br>in the transmit |                  |                |

| bit 3          |                                          | SP2 Bus Collisi                      |                 |                  |                                     |                  |                |

|                |                                          | lision was dete                      | -               | -                | ware)                               |                  |                |

|                |                                          | ollision was det                     |                 |                  |                                     |                  |                |

| bit 2          | -                                        | chronous Seria                       | -               |                  | -                                   |                  | `              |

|                |                                          | or the Transmi                       |                 |                  | lete (must be cl<br>on in progress  | eared in softwa  | are)           |

| bit 1          |                                          | SP1 Bus Collisi                      | •               | •                |                                     |                  |                |

|                |                                          | llision was dete<br>collision was de | •               | cleared in sof   | tware)                              |                  |                |

| bit 0          | SSP1IF: Syn                              | chronous Seria                       | I Port (MSSP1   | I) Interrupt Fla | g bit                               |                  |                |

|                |                                          |                                      |                 |                  | lete (must be cl                    | eared in softwa  | are)           |

|                | 0 = Waiting f                            | or the Transmi                       | ssion/Receptic  | on/Bus Conditi   | on in progress                      |                  |                |

|                | The RCxIF flag is times to remove al     |                                      |                 |                  | firmware must                       | read from RCx    | REG enough     |

|                | The TXxIF flag is a                      |                                      |                 |                  |                                     |                  |                |

|                | the firmware must<br>TXxIF flag does no  | •                                    |                 | •                | •                                   | •                | ouffer. The    |

|                |                                          |                                      |                 |                  |                                     |                  |                |

|                |                                          |                                      |                 |                  |                                     |                  |                |

|                | Interrupt flag bits a                    |                                      |                 |                  |                                     |                  |                |

|                | condition occurs, r<br>its corresponding |                                      |                 |                  |                                     |                  |                |

|                | Enable bit, GIE, c                       |                                      |                 |                  |                                     |                  |                |

|                | User software                            | should ensu                          | ure the         |                  |                                     |                  |                |

|                | appropriate interr                       |                                      | are clear       |                  |                                     |                  |                |

prior to enabling an interrupt.

© 2016 Microchip Technology Inc.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|---------|---------------------|

| INTCON | GIE    | PEIE   | _      |        | _      | _      | _      | INTEDG  | 146                 |

| PIE0   | _      | —      | TMR0IE | IOCIE  | _      | _      | —      | INTE    | 147                 |

| PIE1   | OSFIE  | CSWIE  | _      | _      | —      | _      | —      | ADIE    | 148                 |

| PIE2   | _      | ZCDIE  | _      | _      | _      | _      | C2IE   | C1IE    | 149                 |

| PIE3   | RC2IE  | TX2IE  | RC1IE  | TX1IE  | BCL2IE | SSP2IE | BCL1IE | SSP1IE  | 150                 |

| PIE4   | _      | —      | _      | _      | —      | _      | TMR2IE | TMR1IE  | 151                 |

| PIE5   | CLC4IE | CLC3IE | CLC2IE | CLC1IE | —      | _      | —      | TMR1GIE | 152                 |

| PIE6   | _      | —      | _      | _      | —      | _      | CCP2IE | CCP1IE  | 153                 |

| PIE7   | _      | —      | NVMIE  | NCO1IE | —      | _      | —      | CWG1IE  | 154                 |

| PIR0   |        | —      | TMR0IF | IOCIF  | —      |        | —      | INTF    | 155                 |

| PIR1   | OSFIF  | CSWIF  | -      |        | _      | _      | —      | ADIF    | 156                 |

| PIR2   | -      | ZCDIF  | _      | -      | —      | _      | C2IF   | C1IF    | 157                 |

| PIR3   | RC2IF  | TX2IF  | RC1IF  | TX1IF  | BCL2IF | SSP2IF | BCL1IF | SSP1IF  | 158                 |

| PIR4   | —      |        | —      | —      |        | —      | TMR2IF | TMR1IF  | 159                 |

| PIR5   | CLC4IF | CLC3IF | CLC2IF | CLC1IF | —      | _      | —      | TMR1GIF | 160                 |

| PIR6   | _      | —      | —      | —      | —      | _      | CCP2IF | CCP1IF  | 161                 |

| PIR7   |        | _      | NVMIF  | NCO1IF | _      |        | —      | CWG1IF  | 162                 |

### TABLE 10-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|---------|--------|--------|--------|--------|-----------|-----------------------|-----------------------|-----------------------|---------------------|

| INTCON  | GIE    | PEIE   | _      | _      | _         | —                     | _                     | INTEDG                | 146                 |

| PIE0    | —      |        | TMR0IE | IOCIE  | —         | _                     |                       | INTE                  | 147                 |

| PIE1    | OSFIE  | CSWIE  | _      |        | —         | —                     | _                     | ADIE                  | 148                 |

| PIE2    | _      | ZCDIE  | _      | _      | _         | _                     | C2IE                  | C1IE                  | 149                 |

| PIE3    | RC2IE  | TX2IE  | RC1IE  | TX1IE  | BCL2IE    | SSP2IE                | BCL1IE                | SSP1IE                | 150                 |

| PIE4    | —      | _      | _      | —      | —         | —                     | TMR2IE                | TMR1IE                | 151                 |

| PIR0    | —      | _      | TMR0IF | IOCIF  | —         | —                     |                       | INTF                  | 155                 |

| PIR1    | OSFIF  | CSWIF  | _      |        | _         | _                     | _                     | ADIF                  | 156                 |

| PIR2    | —      | ZCDIF  |        | _      | —         | —                     | C2IF                  | C1IF                  | 157                 |

| PIR3    | RC2IF  | TX2IF  | RC1IF  | TX1IF  | BCL2IF    | SSP2IF                | BCL1IF                | SSP1IF                | 158                 |

| PIR4    | _      |        | _      |        | —         | _                     | TMR2IF                | TMR1IF                | 159                 |

| IOCAP   | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3    | IOCAP2                | IOCAP1                | IOCAP0                | 255                 |

| IOCAN   | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3    | IOCAN2                | IOCAN1                | IOCAN0                | 255                 |

| IOCAF   | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3    | IOCAF2                | IOCAF1                | IOCAF0                | 256                 |

| IOCBP   | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3    | IOCBP2                | IOCBP1                | IOCBP0                | 257                 |

| IOCBN   | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3    | IOCBN2                | IOCBN1                | IOCBN0                | 257                 |

| IOCBF   | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3    | IOCBF2                | IOCBF1                | IOCBF0                | 258                 |

| IOCCP   | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3    | IOCCP2                | IOCCP1                | IOCCP0                | 259                 |

| IOCCN   | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3    | IOCCN2                | IOCCN1                | IOCCN0                | 259                 |

| IOCCF   | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3    | IOCCF2                | IOCCF1                | IOCCF0                | 259                 |

| IOCEP   | —      |        |        | _      | IOCEP3    | IOCEP2 <sup>(1)</sup> | IOCEP1 <sup>(1)</sup> | IOCEP0 <sup>(1)</sup> | 260                 |

| IOCEN   | —      | _      | _      | —      | IOCEN3    | IOCEN2 <sup>(1)</sup> | IOCEN1 <sup>(1)</sup> | IOCEN0 <sup>(1)</sup> | 260                 |

| IOCEF   | —      |        |        | _      | IOCEF3    | IOCEF2 <sup>(1)</sup> | IOCEF1 <sup>(1)</sup> | IOCEF0 <sup>(1)</sup> | 261                 |

| STATUS  | _      | _      | _      | TO     | PD        | Z                     | DC                    | С                     | 54                  |

| VREGCON | _      | _      | _      | _      | _         | —                     | VREGPM                | _                     | 168                 |

| CPUDOZE | IDLEN  | DOZEN  | ROI    | DOE    | _         |                       | 169                   |                       |                     |

| WDTCON0 | —      | —      |        | ١      | WDTPS<4:0 | >                     |                       | SWDTEN                | 175                 |

### TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

**Note 1:** Present only in PIC16(L)F15375/76/85/86.

### **REGISTER 14-35: LATE: PORTE DATA LATCH REGISTER<sup>(1)</sup>**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | _   | _   | —   | LATE2   | LATE1   | LATE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

|       |     |     |     |     |         |         |         |

# Legend:

bit 2-0

| •                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-3 Unimplemented: Read as '0'

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits

### **Note 1:** Present on PIC16(L)F15375/76/85/86 only.

2: Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of actual I/O pin values.

### REGISTER 14-36: ANSELE: PORTE ANALOG SELECT REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | _   | _   | _   | _   | ANSE2   | ANSE1   | ANSE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-3 Unimplemented: Read as '0'

**ANSE<2:0>**: Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively<sup>(2)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(2)</sup>. Digital input buffer disabled.

Note 1: Present on PIC16(L)F15375/76/85/86 only.

**2:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| VALC               | VALUES                     |  |  |  |  |

|--------------------|----------------------------|--|--|--|--|

| Desired Input Pin  | Value to Write to Register |  |  |  |  |

| RA0                | 0x00                       |  |  |  |  |

| RA1                | 0x01                       |  |  |  |  |

| RA2                | 0x02                       |  |  |  |  |

| RA3                | 0x03                       |  |  |  |  |

| RA4                | 0x04                       |  |  |  |  |

| RA5                | 0x05                       |  |  |  |  |

| RA6                | 0x06                       |  |  |  |  |

| RA7                | 0x07                       |  |  |  |  |

| RB0                | 0x08                       |  |  |  |  |

| RB1                | 0x09                       |  |  |  |  |

| RB2                | 0x0A                       |  |  |  |  |

| RB3                | 0x0B                       |  |  |  |  |

| RB4                | 0x0C                       |  |  |  |  |

| RB5                | 0x0D                       |  |  |  |  |

| RB6                | 0x0E                       |  |  |  |  |

| RB7                | 0x0F                       |  |  |  |  |

| RC0                | 0x10                       |  |  |  |  |

| RC1                | 0x11                       |  |  |  |  |

| RC2                | 0x12                       |  |  |  |  |

| RC3                | 0x13                       |  |  |  |  |

| RC4                | 0x14                       |  |  |  |  |

| RC5                | 0x15                       |  |  |  |  |

| RC6                | 0x16                       |  |  |  |  |

| RC7                | 0x17                       |  |  |  |  |

| RD0 <sup>(2)</sup> | 0x18                       |  |  |  |  |

| RD1 <sup>(2)</sup> | 0x19                       |  |  |  |  |

| RD2 <sup>(2)</sup> | 0x1A                       |  |  |  |  |

| RD3 <sup>(2)</sup> | 0x1B                       |  |  |  |  |

| RD4 <sup>(2)</sup> | 0x1C                       |  |  |  |  |

| RD5 <sup>(2)</sup> | 0x1D                       |  |  |  |  |

| RD6 <sup>(2)</sup> | 0x1E                       |  |  |  |  |

| RD7 <sup>(2)</sup> | 0x1F                       |  |  |  |  |

| RE0 <sup>(2)</sup> | 0x20                       |  |  |  |  |

| RE1 <sup>(2)</sup> | 0x21                       |  |  |  |  |

| RE2 <sup>(2)</sup> | 0x22                       |  |  |  |  |

| l                  | 1                          |  |  |  |  |

### TABLE 15-4: PPS INPUT REGISTER VALUES

Note 1: Only a few of the values in this column are valid for any given signal. For example, since the INT signal can only be mapped to PORTA or PORTB pins, only the register values 0x00-0x0F (corresponding to RA<7:0> and RB<7:0>) are valid values to write to the INTPPS register.

- 2: Present on PIC16(L)F15375/76/85/86 only.

- **3:** Present on PIC16(L)F15385/86 only.

### TABLE 15-4: PPS INPUT REGISTER VALUES

| Desired Input Pin  | Value to Write to Register |

|--------------------|----------------------------|

| RF0 <sup>(3)</sup> | 0x28                       |

| RF1 <sup>(3)</sup> | 0x29                       |

| RF2 <sup>(3)</sup> | 0x2A                       |

| RF3 <sup>(3)</sup> | 0x2B                       |

| RF4 <sup>(3)</sup> | 0x2C                       |

| RF5 <sup>(3)</sup> | 0x2D                       |

| RF6 <sup>(3)</sup> | 0x2E                       |

| RF7 <sup>(3)</sup> | 0x2F                       |

Note 1: Only a few of the values in this column are valid for any given signal. For example, since the INT signal can only be mapped to PORTA or PORTB pins, only the register values 0x00-0x0F (corresponding to RA<7:0> and RB<7:0>) are valid values to write to the INTPPS register.

- 2: Present on PIC16(L)F15375/76/85/86 only.

- **3:** Present on PIC16(L)F15385/86 only.

### REGISTER 17-10: IOCEP: INTERRUPT-ON-CHANGE PORTE POSITIVE EDGE REGISTER

| U-0     | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0            | R/W/HS-0/0            | R/W/HS-0/0            |

|---------|-----|-----|-----|------------|-----------------------|-----------------------|-----------------------|

|         | —   | _   | —   | IOCEP3     | IOCEP2 <sup>(1)</sup> | IOCEP1 <sup>(1)</sup> | IOCEP0 <sup>(1)</sup> |

| bit 7   |     |     |     |            |                       | •                     | bit 0                 |

|         |     |     |     |            |                       |                       |                       |

| Legend: |     |     |     |            |                       |                       |                       |

| •                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | <b>Unimplemented:</b> Read as '0' |

|---------|-----------------------------------|

|         |                                   |

bit 3-0 **IOCEP<3:0>:** Interrupt-on-Change PORTE Positive Edge Enable bit

- 1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

**Note 1:** Present only on PIC16(L)F15375/76/85/86.

### REGISTER 17-11: IOCEN: INTERRUPT-ON-CHANGE PORTE NEGATIVE EDGE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0            | R/W/HS-0/0            | R/W/HS-0/0            |

|-------|-----|-----|-----|------------|-----------------------|-----------------------|-----------------------|

| —     | _   |     |     | IOCEN3     | IOCEN2 <sup>(1)</sup> | IOCEN1 <sup>(1)</sup> | IOCEN0 <sup>(1)</sup> |

| bit 7 |     |     |     |            |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 IOCEN<3:0>: Interrupt-on-Change PORTE Negative Edge Enable bit

1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

**Note 1:** Present only on PIC16(L)F15375/76/85/86.

### **REGISTER 20-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u         R/W-x/u <t< th=""><th></th><th>,</th><th></th><th></th><th></th><th></th><th></th></t<> |                         | ,                                                |             |         |                |         |                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------|-------------|---------|----------------|---------|------------------|

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-x/u R/W-x/          | R/W-x/u R/W                                      | R/W-x/u     | R/W-x/u | R/W-x/u        | R/W-x/u | R/W-x/u          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |                                                  | S<9:2>      | ADRE    |                |         |                  |

| l egend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ł                       |                                                  |             |         |                |         | bit 7            |

| l agand:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |                                                  |             |         |                |         |                  |

| Legena.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         |                                                  |             |         |                |         | Legend:          |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | s 'O'                   | nented bit, read as '0'                          | U = Unimple |         | W = Writable I | bit     | R = Readable     |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all ot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | /alue at all other Rese | -n/n = Value at POR and BOR/Value at all other F |             |         |                | anged   | u = Bit is uncha |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

'1' = Bit is set

### **REGISTER 20-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

'0' = Bit is cleared

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | 6<1:0>  | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **ADRES<1:0>**: ADC Result Register bits Lower two bits of 10-bit conversion result

Lower two bits of 10-bit conversion

bit 5-0 Reserved: Do not use.

© 2016 Microchip Technology Inc.

### 23.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 37-14 for more details.

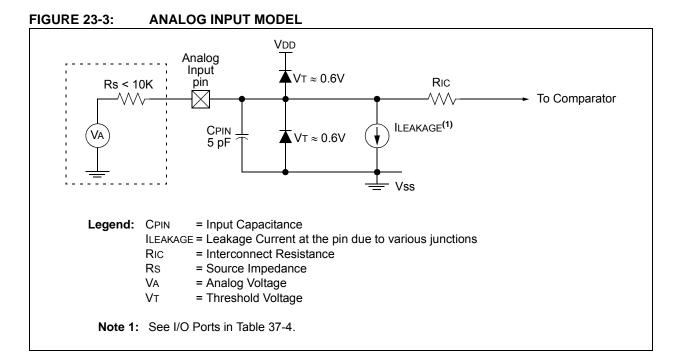

### 23.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 23-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

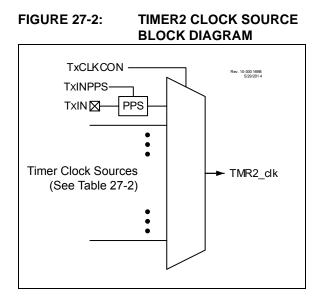

# 27.1 Timer2 Operation

Timer2 operates in three major modes:

- Free Running Period

- One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 27-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- · any device Reset

- External Reset Source event that resets the timer.

| Note: | TMR2 is  | s not | cleared | when | T2CON | is |

|-------|----------|-------|---------|------|-------|----|

|       | written. |       |         |      |       |    |

### 27.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each TMR2\_clk cycle. When the two values match, the comparator resets the value of TMR2 to 00h on the next rising TMR2\_clk edge and increments

the output postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register, a one TMR2\_clk period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

### 27.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

### 27.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

# 27.2 Timer2 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- The ADC module, as an Auto-conversion Trigger

- · COG, as an auto-shutdown source

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See **Section 28.0** "**Capture/Compare/PWM Modules**" for more details on setting up Timer2 for use with the CCP, as well as the timing diagrams in **Section 27.5** "**Operation Examples**" for examples of how the varying Timer2 modes affect CCP PWM output.

# 27.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2 with the T2RST register. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

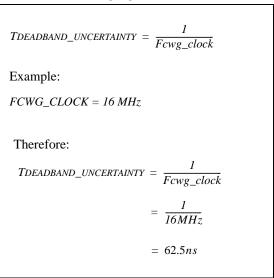

### 30.8 **Dead-Band Uncertainty**

When the rising and falling edges of the input source are asynchronous to the CWG clock, it creates uncertainty in the dead-band time delay. The maximum uncertainty is equal to one CWG clock period. Refer to Equation 30-1 for more details.

### EQUATION 30-1: **DEAD-BAND** UNCERTAINTY

# MODE0 CWG1A CWG1B CWG1C CWG1D No delay CWG1DBR 🕂 No delay CWG1DBF CWG1\_data Note 1: WGPOL{ABCD} = 0 2: The direction bit MODE<0> (Register 30-1) can be written any time during the PWM cycle, and takes effect at the next rising CWG1 data. 3: When changing directions, CWG1A and CWG1C switch at rising CWG1\_data; modulated CWG1B and CWG1D are held inactive for the dead band duration shown; dead band affects only the first pulse after the direction change.

### **FIGURE 30-8: EXAMPLE OF PWM DIRECTION CHANGE**

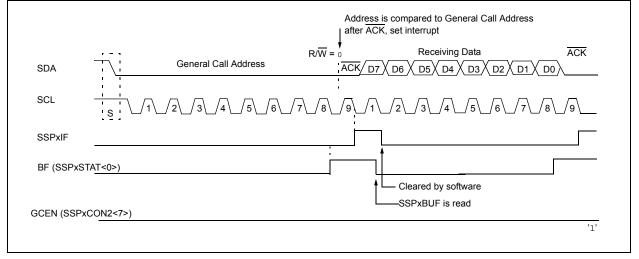

### 32.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address  $0 \ge 0.00$ . When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 32-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

32.5.9 SSP MASK REGISTER

An SSP Mask (SSPxMSK) register (Register 32-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care". This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<6:3>) \rightarrow PC<14:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                        |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                              |

| Operands:                      | None                                                                                                                                                                                        |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$<br>are set.                    |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                | COMF                                        |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       | Syntax:                                     |