Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 28KB (16K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15356t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

| I/O <sup>(2)</sup> | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO     | DAC | Timers | ССР  | MWM     | CWG            | MSSP                                           | ZCD | EUSART            | CLC     | CLKR | Interrupt | Pull-up | Basic |

|--------------------|------------------|------|-----------|------------|---------|-----|--------|------|---------|----------------|------------------------------------------------|-----|-------------------|---------|------|-----------|---------|-------|

| RF5                | 13               | ANF5 | —         |            | _       | _   |        | _    | _       | _              |                                                |     | —                 | —       | —    | —         | Y       | —     |

| RF6                | 14               | ANF6 | —         | —          | —       | —   | -      | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | Y       | _     |

| RF7                | 15               | ANF7 | _         | _          | —       | _   |        | —    | —       | _              | -                                              | _   | —                 | —       | —    | —         | Y       | —     |

| VDD                | 30               | —    | —         | —          | —       | —   | -      | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | Y       | VDD   |

| VDD                | 7                | —    | —         | —          | —       | _   |        | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | —       | VDD   |

| Vss                | 6                | —    | —         |            | _       |     |        | _    | —       |                |                                                |     | _                 | —       | —    | —         | —       | Vss   |

| Vss                | 31               | _    | _         | —          | —       | —   | _      | _    | _       | —              | —                                              | —   | —                 | _       | —    | _         | —       | Vss   |

| OUT <sup>(2)</sup> | —                | —    | —         | C1OUT      | NCO10UT |     | TMR0   | CCP1 | PWM3OUT | CWG1A<br>CWG2A | SDO1<br>SDO2                                   |     | DT <sup>(3)</sup> | CLC1OUT | CLKR | —         | -       | —     |

|                    | —                | —    |           | C2OUT      | —       | _   |        | CCP2 | PWM4OUT | CWG1B<br>CWG2B | SCK1<br>SCK2                                   | -   | CK1<br>CK2        | CLC2OUT | -    | —         | -       | —     |

|                    | —                | -    | _         | _          | -       | —   | —      | _    | PWM5OUT | CWG1C<br>CWG2C | SCK1 <sup>(3,4)</sup><br>SCL2 <sup>(3,4)</sup> | _   | TX1<br>TX2        | CLC3OUT | _    | _         | -       | -     |

|                    | —                | _    | _         | _          | _       | —   | _      | _    | PWM6OUT | CWG1D<br>CWG2D | SDA1 <sup>(3,4)</sup><br>SDA2 <sup>(3,4)</sup> | _   | —                 | CLC4OUT | -    | _         | -       | —     |

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

| Name                                                    | Function              | Input<br>Type | Output Type | Description                                       |

|---------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------|

| RA0/ANA0/C1IN0-/C2IN0-/CLCIN0 <sup>(1)</sup> /<br>IOCA0 | RA0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IOCAU                                                   | ANA0                  | AN            | —           | ADC Channel A0 input.                             |

|                                                         | C1IN0-                | AN            | —           | Comparator negative input.                        |

|                                                         | C2IN0-                | AN            | —           | Comparator negative input.                        |

|                                                         | CLCIN0 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.             |

|                                                         | IOCA0                 | TTL/ST        | —           | Interrupt-on-change input.                        |

| RA1/ANA1/C1IN1-/C2IN1-/CLCIN1 <sup>(1)</sup> /<br>IOCA1 | RA1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IUCAT                                                   | ANA1                  | AN            | _           | ADC Channel A1 input.                             |

|                                                         | C1IN1-                | AN            | —           | Comparator negative input.                        |

|                                                         | C2IN1-                | AN            | _           | Comparator negative input.                        |

|                                                         | CLCIN1 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.             |

|                                                         | IOCA1                 | TTL/ST        | —           | Interrupt-on-change input.                        |

| RA2/ANA2/C1IN0+/C2IN0+/<br>DAC1OUT1/IOCA2               | RA2                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| DACTOUTI/IOCAZ                                          | ANA2                  | AN            | _           | ADC Channel A2 input.                             |

|                                                         | C1IN0+                | AN            | _           | Comparator positive input.                        |

|                                                         | C2IN0+                | AN            | _           | Comparator positive input.                        |

|                                                         | DAC1OUT1              | _             | AN          | Digital-to-Analog Converter output.               |

|                                                         | IOCA2                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA3/ANA3/C1IN1+/VREF+/DACREF+/                          | RA3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IOCA3                                                   | ANA3                  | AN            | _           | ADC Channel A3 input.                             |

|                                                         | C1IN1+                | AN            | _           | Comparator positive input.                        |

|                                                         | VREF+                 | AN            | _           | External ADC and/or DAC positive reference input. |

|                                                         | IOCA3                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA4/ANA4/T0CKI <sup>(1)</sup> /IOCA4                    | RA4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA4                  | AN            | _           | ADC Channel A4 input.                             |

|                                                         | T0CKI <sup>(1)</sup>  | TTL/ST        | —           | Timer0 clock input.                               |

|                                                         | IOCA4                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA5/ANA5/SS1 <sup>(1)</sup> /T1G <sup>(1)</sup> /IOCA5  | RA5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA5                  | AN            | —           | ADC Channel A5 input.                             |

|                                                         | SS1 <sup>(1)</sup>    | TTL/ST        | _           | MSSP1 SPI slave select input.                     |

|                                                         | T1G <sup>(1)</sup>    | TTL/ST        | _           | Timer1 gate input.                                |

|                                                         | IOCA5                 | TTL/ST        | _           | Interrupt-on-change input.                        |

#### **TABLE 1-3:** PIC16(L)F15375/76 PINOUT DESCRIPTION

CMOS = CMOS compatible input or output Legend: AN = Analog input or output TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels XTAL

HV = High Voltage

Note

= Crystal levels This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx 1: pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-6.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for  $I^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, 4: instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

<sup>=</sup> Open-Drain 1<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

# 4.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Program Flash Memory

- Device Information Area (DIA)

- Device Configuration Information (DCI)

- Revision ID

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

- NVMREG access

#### TABLE 4-1: DEVICE SIZES AND ADDRESSES

| Device         | Program Memory Size (Words) | Last Program Memory Address |

|----------------|-----------------------------|-----------------------------|

| PIC16(L)F15356 | 16384                       | 3FFFh                       |

| PIC16(L)F15375 | 8192                        | 1FFFh                       |

| PIC16(L)F15376 | 16384                       | 3FFFh                       |

| PIC16(L)F15385 | 8192                        | 1FFFh                       |

| PIC16(L)F15386 | 16384                       | 3FFFh                       |

# 4.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing  $32K \times 14$  program memory space. Table 4-1 shows the memory sizes implemented. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 4-1).

| Address            | Name             | Bit 7          | Bit 6         | Bit 5   | Bit 4          | Bit 3               | Bit 2     | Bit 1 | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|--------------------|------------------|----------------|---------------|---------|----------------|---------------------|-----------|-------|-----------|-----------------------|----------------------------|

| Bank 61            |                  |                |               |         |                |                     |           |       |           |                       |                            |

|                    |                  |                |               | CPU COP | RE REGISTERS   | ; see Table 4-3 for | specifics |       |           |                       |                            |

| 1E8Ch              | _                |                |               |         | Unimple        | mented              |           |       |           |                       | _                          |

| 1E8Dh              | —                |                |               |         | Unimple        | mented              |           |       |           | —                     | _                          |

| 1E8Eh              | _                |                |               |         | Unimple        | mented              |           |       |           | —                     |                            |

| 1E8Fh              | PPSLOCK          | —              | —             | —       | —              | —                   | -         | —     | PPSLOCKED | 0                     | 0                          |

| 1E90h              | INTPPS           | —              | —             |         |                | INTP                | PS<5:0>   |       |           | 00 1000               | uu uuuu                    |

| 1E91h              | TOCKIPPS         | _              | _             |         |                | TOCKI               | PPS<5:0>  |       |           | 00 0100               | uu uuuu                    |

| 1E92h              | T1CKIPPS         | —              | —             |         |                | T1CKI               | PPS<5:0>  |       |           | 01 0000               | uu uuuu                    |

| 1E93h              | T1GPPS           | —              | _             |         |                | T1GF                | PS<5:0>   |       |           | 00 1101               | uu uuuu                    |

| 1E94h<br><br>1E9Bh | —                |                | Unimplemented |         |                |                     |           |       | _         | -                     |                            |

| 1E9Ch              | T2INPPS          | _              | _             |         |                | T2INF               | PPS<5:0>  |       |           | 01 0011               | uu uuuu                    |

| 1E9Dh<br><br>1EA0h | _                | Unimplemented  |               |         |                |                     |           |       | -         | _                     |                            |

| 1EA1h              | CCP1PPS          | _              | _             |         |                | CCP1                | PPS<5:0>  |       |           | 01 0010               | uu uuuu                    |

| 1EA2h              | CCP2PPS          | _              | _             |         |                | CCP2                | PPS<5:0>  |       |           | 01 0001               | uu uuuu                    |

| 1EA3h<br><br>1EB0h | _                |                |               |         | Unimple        | mented              |           |       |           | _                     | _                          |

| 1EB1h              | CWG1PPS          | _              | _             |         |                | CWG1                | PPS<5:0>  |       |           | 00 1000               | uu uuuu                    |

| 1EB2h<br>1EBAh     | _                |                |               |         | Unimple        | mented              |           |       |           | _                     | _                          |

| 1EBBh              | <b>CLCIN0PPS</b> | _              | _             |         |                | CLCIN               | )PPS<5:0> |       |           | 00 0000               | uu uuuu                    |

| 1EBCh              | CLCIN1PPS        | _              | _             |         |                | CLCIN               | 1PPS<5:0> |       |           | 00 0001               | uu uuuu                    |

| 1EBDh              | CLCIN2PPS        | —              | —             |         | CLCIN2PPS<5:0> |                     |           |       |           |                       | uu uuuu                    |

| 1EBEh              | CLCIN3PPS        | CLCIN3PPS<5:0> |               |         |                |                     |           |       | 00 1111   | uu uuuu               |                            |

| 1EBFh<br>1EC2h     | _                | Unimplemented  |               |         |                |                     |           |       | _         | _                     |                            |

| 1EC3h              | ADACTPPS         | _              | _             |         |                | CLCIN               | 3PPS<5:0> |       |           | 001100                | uuuuuu                     |

| 1EC4h              | _                |                | ·             |         | Unimple        | mented              |           |       |           | _                     | -                          |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

$Legend: \quad x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.$

# 4.4 PCL and PCLATH

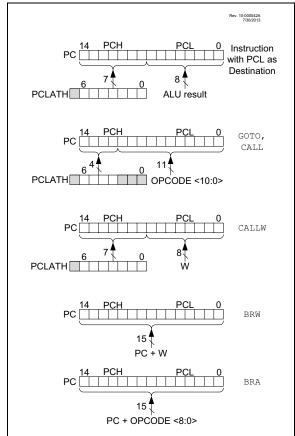

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 4-4 shows the five situations for the loading of the PC.

FIGURE 4-4: LOADING OF PC IN DIFFERENT SITUATIONS

# 4.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

# 4.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

# 4.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

# 4.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 + the signed value of the operand of the BRA instruction.

| REGISTER                                                                                                                              | 10-3: PIE1:                                  | PERIPHERAI                                                             |                                                      | PT ENABLE      | REGISTER 1       |                  |              |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|----------------|------------------|------------------|--------------|

| R/W-0/0                                                                                                                               | R/W-0/0                                      | U-0                                                                    | U-0                                                  | U-0            | U-0              | R/W-0/0          | R/W-0/0      |

| OSFIE                                                                                                                                 | CSWIE                                        | —                                                                      | —                                                    | —              | —                | —                | ADIE         |

| bit 7                                                                                                                                 |                                              |                                                                        |                                                      |                |                  |                  | bit 0        |

| Legend:                                                                                                                               |                                              |                                                                        |                                                      |                |                  |                  | ]            |

| R = Readab                                                                                                                            | la hit                                       | W = Writable                                                           | h:t                                                  |                | nantad hit raad  | aa 'O'           |              |

|                                                                                                                                       |                                              |                                                                        |                                                      |                | nented bit, read |                  |              |

| u = Bit is un                                                                                                                         | changed                                      | x = Bit is unkr                                                        | iown                                                 | -n/n = Value a | at POR and BOI   | R/Value at all c | other Resets |

| '1' = Bit is se                                                                                                                       | et                                           | '0' = Bit is clea                                                      | ared                                                 |                |                  |                  |              |

| bit 6                                                                                                                                 | 0 = Disables<br>CSWIE: Cloc<br>1 = The clock | he Oscillator Fa<br>the Oscillator F<br>k Switch Comp<br>switch module | ail Interrupt<br>lete Interrupt I<br>interrupt is er | nabled         |                  |                  |              |

| <b>h</b> :1 <b>F</b> 4                                                                                                                |                                              | switch module                                                          | •                                                    | sabled         |                  |                  |              |

| bit 5-1                                                                                                                               | -                                            | ted: Read as '                                                         |                                                      |                |                  |                  |              |

| bit 0 ADIE: Analog-to-Digital Converter (ADC) Interrupt Enable bit<br>1 = Enables the ADC interrupt<br>0 = Disables the ADC interrupt |                                              |                                                                        |                                                      |                |                  |                  |              |

| Note: Bit PEIE of the INTCON register must be<br>set to enable any peripheral interrupt<br>controlled by registers PIE1-PIE7          |                                              |                                                                        |                                                      |                |                  |                  |              |

# 12.0 WINDOWED WATCHDOG TIMER (WWDT)

The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WDT has the following features:

- Selectable clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Configurable window size from 12.5 to 100 percent of the time-out period

- Multiple Reset conditions

- Operation during Sleep

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATB<7:0>: RB<7:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register returns actual I/O pin values.

#### REGISTER 14-12: ANSELB: PORTB ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSB<7:0>: Analog Select between Analog or Digital Function on pins RB<7:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# 14.6 PORTC Registers

#### 14.6.1 DATA REGISTER

PORTC is an 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 14-18). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 14-17) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The PORT data latch LATC (Register 14-19) holds the output port data, and contains the latest value of a LATC or PORTC write.

#### 14.6.2 DIRECTION CONTROL

The TRISC register (Register 14-18) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

# 14.6.3 OPEN-DRAIN CONTROL

The ODCONC register (Register 14-22) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONC bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONC bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for $I^2C$ ; the $I^2C$ |

|-------|------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                    |

#### 14.6.4 SLEW RATE CONTROL

The SLRCONC register (Register 14-23) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONC bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONC bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

# 14.6.5 INPUT THRESHOLD CONTROL

The INLVLC register (Register 14-24) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

# 14.6.6 ANALOG CONTROL

The ANSELC register (Register 14-20) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |  |

# 14.6.7 WEAK PULL-UP CONTROL

The WPUC register (Register 14-21) controls the individual weak pull-ups for each port pin.

#### 14.6.8 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

# TABLE 14-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Register<br>on Page |

|-----------------------|-------|-------|-------|-------|---------|------------------------|------------------------|------------------------|---------------------|

| PORTE                 | —     |       |       |       | RE3     | RE2 <sup>(1)</sup>     | RE1 <sup>(1)</sup>     | RE0 <sup>(1)</sup>     | 222                 |

| TRISE                 | —     | —     | _     | _     | (2)     | TRISE2 <sup>(1)</sup>  | TRISE2 <sup>(1)</sup>  | TRISE2 <sup>(1)</sup>  | 222                 |

| LATE <sup>(1)</sup>   | —     | —     |       |       |         | LATE2                  | LATE2                  | LATE2                  | 223                 |

| ANSELE <sup>(1)</sup> | —     | —     | -     | -     | -       | ANSE2                  | ANSE1                  | ANSE0                  | 217                 |

| WPUE                  | —     | —     |       |       | WPUE3   | WPUE2 <sup>(1)</sup>   | WPUE1 <sup>(1)</sup>   | WPUE0 <sup>(1)</sup>   | 224                 |

| ODCONE <sup>(1)</sup> | —     | —     | -     | -     | -       | ODCE2                  | ODCE1                  | ODCE0                  | 224                 |

| SLRCONE               | _     | _     | _     | _     | SLRE3   | SLRE2 <sup>(1)</sup>   | SLRE1 <sup>(1)</sup>   | SLRE0 <sup>(1)</sup>   | 225                 |

| INLVLE                | —     |       |       |       | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> | 225                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Present only in PIC16(L)F15375/76/85/86.

2: Unimplemented, read as '1'

#### TABLE 14-7: SUMMARY OF CONFIGURATION WORD WITH PORTE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         | _       | DEBUG    | STVREN   | PPS1WAY  | ZCDDIS   | BORV    |         | 102                 |

| CONFIG2 | 7:0  | BOREN   | l <1:0> | LPBOREN  |          |          | _        | PWRTE   | MCLRE   | 103                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTE.

| R/W-0/0                                                                                         | R/W-0/0                                                                                   | R/W-0/0                                                       | R/W-0/0 | U-0            | U-0               | U-0            | R/W-0/0      |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------|----------------|-------------------|----------------|--------------|--|

| UART2MD                                                                                         | UART1MD                                                                                   | MSSP2MD                                                       | MSSP1MD | <u> </u>       |                   |                | CWG1MD       |  |

| bit 7                                                                                           |                                                                                           |                                                               |         |                |                   |                | bit 0        |  |

|                                                                                                 |                                                                                           |                                                               |         |                |                   |                |              |  |

| Legend:                                                                                         |                                                                                           |                                                               |         |                |                   |                |              |  |

| R = Readable                                                                                    | bit                                                                                       | W = Writable I                                                | oit     | U = Unimplem   | ented bit, read   | as '0'         |              |  |

| u = Bit is unch                                                                                 | nanged                                                                                    | x = Bit is unkn                                               | own     | -n/n = Value a | t POR and BOF     | R/Value at all | other Resets |  |

| '1' = Bit is set                                                                                |                                                                                           | '0' = Bit is clea                                             | ared    | q = Value dep  | ends on condition | on             |              |  |

| bit 7 UART2MD: Disable EUSART2 bit<br>1 = EUSART2 module disabled<br>0 = EUSART2 module enabled |                                                                                           |                                                               |         |                |                   |                |              |  |

| bit 6                                                                                           | 1 = EUSART                                                                                | visable EUSAR <sup>-</sup><br>1 module disab<br>1 module enab | led     |                |                   |                |              |  |

| bit 5                                                                                           | 1 = MSSP2 n                                                                               | isable MSSP2<br>nodule disablec<br>nodule enabled             | 1       |                |                   |                |              |  |

| bit 4                                                                                           | bit 4 MSSP1MD: Disable MSSP1 bit<br>1 = MSSP1 module disabled<br>0 = MSSP1 module enabled |                                                               |         |                |                   |                |              |  |

| bit 3-1                                                                                         | Unimplement                                                                               | ted: Read as '0                                               | )'      |                |                   |                |              |  |

| bit 0 <b>CWG1MD:</b> Disable CWG1 bit<br>1 = CWG1 module disabled<br>0 = CWG1 module enabled    |                                                                                           |                                                               |         |                |                   |                |              |  |

#### REGISTER 16-5: PMD4: PMD CONTROL REGISTER 4

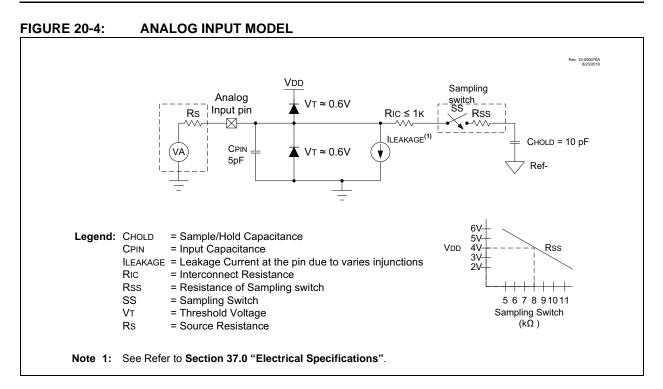

# FIGURE 20-5: ADC TRANSFER FUNCTION

© 2016 Microchip Technology Inc.

DS40001866A-page 276

| R/W-0/0         | U-0                        | R-0                                                          | R/W-0/0    | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|-----------------|----------------------------|--------------------------------------------------------------|------------|----------------|------------------|------------------|--------------|--|--|--|

| T0EN            | _                          | TOOUT                                                        | T016BIT    |                | TOOUTI           | PS<3:0>          |              |  |  |  |

| bit 7           |                            |                                                              |            |                |                  |                  | bit          |  |  |  |

|                 |                            |                                                              |            |                |                  |                  |              |  |  |  |

| Legend:         |                            |                                                              |            |                |                  |                  |              |  |  |  |

| R = Readable    | e bit                      | W = Writable                                                 | bit        | U = Unimplen   | nented bit, read | l as '0'         |              |  |  |  |

| u = Bit is unc  | changed                    | x = Bit is unk                                               | nown       | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is se | t                          | '0' = Bit is cle                                             | ared       |                |                  |                  |              |  |  |  |

|                 |                            |                                                              |            |                |                  |                  |              |  |  |  |

| bit 7           | TOEN: Time                 | r0 Enable bit                                                |            |                |                  |                  |              |  |  |  |

|                 |                            | dule is enabled                                              |            |                |                  |                  |              |  |  |  |

|                 |                            | dule is disabled                                             |            | vest power mod | de               |                  |              |  |  |  |

| bit 6           | Unimpleme                  | nted: Read as                                                | 0'         |                |                  |                  |              |  |  |  |

| bit 5           | T0OUT: Tim<br>Timer0 outp  | er0 Output bit (ı<br>ut bit                                  | read-only) |                |                  |                  |              |  |  |  |

| bit 4           | T016BIT: Tir               | T016BIT: Timer0 Operating as 16-bit Timer Select bit         |            |                |                  |                  |              |  |  |  |

| -               |                            | 1 = Timer0 is a 16-bit timer                                 |            |                |                  |                  |              |  |  |  |

|                 | 0 = Timer0 i               | s an 8-bit timer                                             |            |                |                  |                  |              |  |  |  |

| bit 3-0         | T0OUTPS<                   | TOOUTPS<3:0>: Timer0 output postscaler (divider) select bits |            |                |                  |                  |              |  |  |  |

|                 |                            | 1111 = 1:16 Postscaler                                       |            |                |                  |                  |              |  |  |  |

|                 | 1110 = 1:15<br>1101 = 1:14 |                                                              |            |                |                  |                  |              |  |  |  |

|                 | 1101 - 1.14<br>1100 = 1:13 |                                                              |            |                |                  |                  |              |  |  |  |

|                 | 1011 = 1:12                |                                                              |            |                |                  |                  |              |  |  |  |

|                 | 1010 = 1:11                |                                                              |            |                |                  |                  |              |  |  |  |

|                 | 1001 = 1:10                | Postscaler                                                   |            |                |                  |                  |              |  |  |  |

|                 | 1000 <b>= 1:9</b>          | Postscaler                                                   |            |                |                  |                  |              |  |  |  |

|                 | 0111 <b>= 1:8  </b>        |                                                              |            |                |                  |                  |              |  |  |  |

|                 |                            | 0110 = 1:7 Postscaler                                        |            |                |                  |                  |              |  |  |  |

|                 |                            | 0101 = 1:6 Postscaler<br>0100 = 1:5 Postscaler               |            |                |                  |                  |              |  |  |  |

|                 | 0100 = 1:5<br>0011 = 1:4   |                                                              |            |                |                  |                  |              |  |  |  |

|                 | 0011 = 1.41<br>0010 = 1:31 |                                                              |            |                |                  |                  |              |  |  |  |

|                 | 0001 = 1:2                 |                                                              |            |                |                  |                  |              |  |  |  |

|                 | 0000 = 1:1                 |                                                              |            |                |                  |                  |              |  |  |  |

| M - 1-            | MODE  | <4:0>     | Output                                         | Onenetien                                                 |                            | Timer Control            |                                    |                            |

|-------------------|-------|-----------|------------------------------------------------|-----------------------------------------------------------|----------------------------|--------------------------|------------------------------------|----------------------------|

| Mode              | <4:3> | <2:0>     | Operation                                      | Operation                                                 | Start                      | Reset                    | Stop                               |                            |

|                   |       | 000       |                                                | Software gate (Figure 27-4)                               | <b>ON =</b> 1              | _                        | ON = 0                             |                            |

|                   |       | 001       | Period<br>Pulse                                | Hardware gate, active-high<br>(Figure 27-5)               | ON = 1 and<br>TMRx_ers = 1 | _                        | ON = 0 or<br>TMRx_ers = 0          |                            |

|                   |       | 010       | Fuise                                          | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0 | _                        | ON = 0 or<br>TMRx_ers = 1          |                            |

| Free              | 0.0   | 011       |                                                | Rising or falling edge Reset                              |                            | TMRx_ers                 |                                    |                            |

| Running<br>Period | 00    | 100       | Period                                         | Rising edge Reset (Figure 27-6)                           | -                          | TMRx_ers ↑               | <b>ON =</b> 0                      |                            |

|                   |       | 101       | Pulse                                          | Falling edge Reset                                        | -                          | TMRx_ers ↓               |                                    |                            |

|                   |       | 110       | with<br>Hardware                               | Low level Reset                                           | ON = 1                     | TMRx_ers = 0             | ON = 0 or<br>TMRx_ers = 0          |                            |

|                   |       | 111 Reset | Reset                                          | High level Reset (Figure 27-7)                            |                            | TMRx_ers = 1             | ON = 0 or<br>TMRx_ers = 1          |                            |

|                   |       | 000       | One-shot                                       | Software start (Figure 27-8)                              | ON = 1                     | _                        |                                    |                            |

|                   |       | 001       | Edge                                           | Rising edge start (Figure 27-9)                           | ON = 1 and<br>TMRx_ers ↑   | _                        |                                    |                            |

|                   |       | 010 s     | start                                          |                                                           | Falling edge start         | ON = 1 and<br>TMRx_ers ↓ | —                                  | ON = 0<br>or<br>Next clock |

|                   |       | 011       | (Note 1)                                       | Any edge start                                            | ON = 1 and<br>TMRx_ers     |                          |                                    |                            |

| One-shot          | 01    | 100       | Edge                                           | Rising edge start and<br>Rising edge Reset (Figure 27-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑               | after<br>TMRx = PRx                |                            |

|                   |       | 101       | triggered<br>start<br>and<br>hardware<br>Reset | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers ↓               | (Note 2)                           |                            |

|                   |       | 110       |                                                | Rising edge start and<br>Low level Reset (Figure 27-11)   | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers = 0             |                                    |                            |

|                   |       | 111       | (Note 1)                                       | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1             |                                    |                            |

|                   |       | 000       |                                                | Rese                                                      | rved                       |                          |                                    |                            |

|                   |       | 001       | Edge                                           | Rising edge start<br>(Figure 27-12)                       | ON = 1 and<br>TMRx_ers ↑   | _                        | ON = 0<br>or                       |                            |

| Mono-stable       |       | 010       | triggered<br>start                             | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                        | Next clock<br>after                |                            |

|                   |       | 011       | (Note 1)                                       | Any edge start                                            | ON = 1 and<br>TMRx_ers     | -                        | TMRx = PRx<br>( <b>Note 3</b> )    |                            |

| Reserved          | 10    | 100       |                                                | Rese                                                      | rved                       |                          |                                    |                            |

| Reserved          |       | 101       |                                                | Rese                                                      | rved                       |                          |                                    |                            |

|                   |       | 110       | Level<br>triggered                             | High level start and<br>Low level Reset (Figure 27-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0             | ON = 0 or                          |                            |

| One-shot          |       | 111       | start<br>and<br>hardware<br>Reset              | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0 | TMRx_ers = 1             | Held in Reset<br>( <b>Note 2</b> ) |                            |

| Reserved          | 11    | xxx       |                                                | Rese                                                      | rved                       |                          |                                    |                            |

# TABLE 27-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

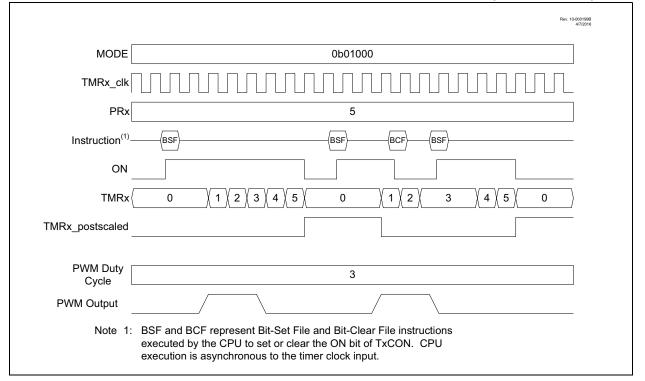

# 27.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal gates the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 27-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

|                                 | Rev. 10.0011988<br>530/2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE                            | 0b00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| TMRx_dk                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| TMRx_ers_                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PRx                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| TMRx                            | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 1 \\ 1$ |  |

| TMRx_postscaled                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PWM Duty<br>Cycle<br>PWM Output | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

#### 27.5.5 SOFTWARE START ONE-SHOT MODE

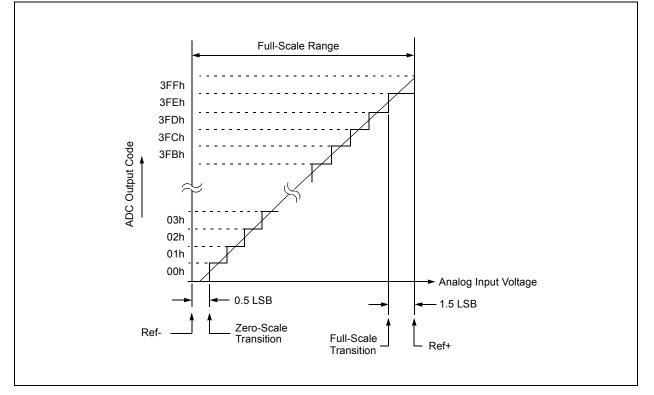

In One-Shot mode the timer resets and the ON bit is cleared when the timer value matches the PRx period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 27-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the PRx match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a PRx period count match.

FIGURE 27-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

# REGISTER 33-4: RCxREG<sup>(1)</sup>: RECEIVE DATA REGISTER

| R-0         | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-------|--|--|

| RCxREG<7:0> |     |     |     |     |     |     |       |  |  |

| bit 7       |     |     |     |     |     |     | bit 0 |  |  |

|             |     |     |     |     |     |     |       |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **RCxREG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 33-2)

**Note 1:** RCxREG (including the 9<sup>th</sup> bit) is double buffered, and data is available while new data is being received.

# REGISTER 33-5: TXxREG<sup>(1)</sup>: TRANSMIT DATA REGISTER

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | TXxREG<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 | bit 7 bit 0 |       |       |       |       |       |       |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TXxREG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 33-1)

**Note 1:** TXxREG (including the 9th bit) is double buffered, and can be written when previous data has started shifting.

# **REGISTER 33-6:** SPxBRGL<sup>(1)</sup>: BAUD RATE GENERATOR REGISTER

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | SPxBRG<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 | bit 7 bit 0 |       |       |       |       |       |       |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SPxBRG<7:0>: Lower eight bits of the Baud Rate Generator

**Note 1:** Writing to SP1BRG resets the BRG counter.

# TABLE 37-17: ZERO CROSS DETECT (ZCD) SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |          |                                |      |      |      |       |          |

|----------------------------------------------------------------------------------|----------|--------------------------------|------|------|------|-------|----------|

| Param.<br>No.                                                                    | Sym.     | Characteristics                | Min. | Тур† | Max. | Units | Comments |

| ZC01                                                                             | VPINZC   | Voltage on Zero Cross Pin      | —    | 0.75 | —    | V     | $\sim$   |

| ZC02                                                                             | IZCD_MAX | Maximum source or sink current | _    | _    | 600  | μΑ)   |          |

| ZC03                                                                             | TRESPH   | Response Time, Rising Edge     | —    | 1    |      | /us   |          |

|                                                                                  | TRESPL   | Response Time, Falling Edge    | _    | 1    | _    | μs    |          |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

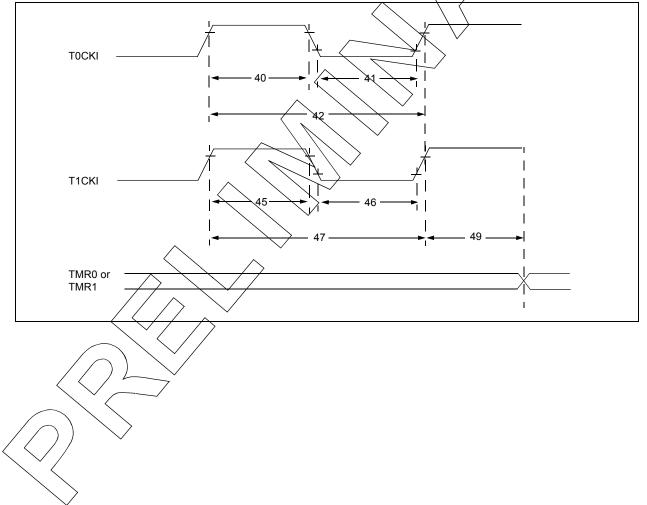

#### FIGURE 37-12: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

# 39.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

# 39.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 39.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 39.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility