#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 28KB (16K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15356t-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE 4  | 4-11: SPECI                                     | AL FUNCTION | REGISTER | SUMMARY                                      | BANKS 0- | 63 (CONTIN          | IUED)  |           |       |                       |                            |

|----------|-------------------------------------------------|-------------|----------|----------------------------------------------|----------|---------------------|--------|-----------|-------|-----------------------|----------------------------|

| Address  | Name                                            | Bit 7       | Bit 6    | Bit 5                                        | Bit 4    | Bit 3               | Bit 2  | Bit 1     | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 12  |                                                 |             |          |                                              |          |                     |        |           |       |                       |                            |

|          | CPU CORE REGISTERS; see Table 4-3 for specifics |             |          |                                              |          |                     |        |           |       |                       |                            |

| 60Ch     | CWG1CLKCON                                      | —           | _        | —                                            | _        | —                   | —      | _         | CS    | 0                     | 0                          |

| 60Dh     | CWG1DAT                                         | _           | _        | _                                            | _        |                     | DA     | T<3:0>    |       | 0000                  | 0000                       |

| 60Eh     | CWG1DBR                                         | _           | —        |                                              |          | DB                  | R<5:0> |           |       | 00 0000               | 00 0000                    |

| 60Fh     | CWG1DBF                                         | _           | —        |                                              |          | DB                  | F<5:0> |           |       | 00 0000               | 00 0000                    |

| 610h     | CWG1CON0                                        | EN          | LD       | —                                            | —        | —                   |        | MODE<2:0> | •     | 00000                 | 00000                      |

| 611h     | CWG1CON1                                        | _           | —        | IN                                           | —        | POLD                | POLC   | POLB      | POLA  | x- 0000               | u- 0000                    |

| 612h     | CWG1AS0                                         | SHUTDOWN    | REN      | LSBD                                         | <2:0>    | LSAC                | <2:0>  | —         | _     | 0001 01               | 0001 01                    |

| 613h     | CWG1AS1                                         | _           | —        | _                                            | AS4E     | AS3E AS2E AS1E AS0E |        |           |       | 0 0000                | u 0000                     |

| 614h     | CWG1STR                                         | OVRD        | OVRC     | OVRB OVRA STRD STRC STRB STRA 0000 0000 0000 |          |                     |        |           |       |                       | 0000 0000                  |

| 615h     |                                                 |             |          |                                              |          |                     |        |           |       |                       |                            |

| <br>61Fh | _                                               |             |          |                                              | Unimpler | nenteu              |        |           |       | _                     |                            |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

PIC16(L)F15356/75/76/85/86

# 6.1 Microchip Unique identifier (MUI)

The PIC16(L)F15356/75/76/85/86 devices are individually encoded during final manufacturing with a Microchip Unique Identifier, or MUI. The MUI cannot be erased by a Bulk Erase command or any other useraccessible means. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is a required. It may also be used by the application manufacturer for a number of functions that require unverified unique identification, such as:

- · Tracking the device

- Unique serial number

The MUI consists of nine program words. When taken together, these fields form a unique identifier. The MUI is stored in nine read-only locations, located between 8100h to 8109h in the DIA space. Table 6-1 lists the addresses of the identifier words.

| Note: | For applications that require verified unique |

|-------|-----------------------------------------------|

|       | identification, contact your Microchip Tech-  |

|       | nology sales office to create a Serialized    |

|       | Quick Turn Programming option.                |

# 6.2 External Unique Identifier (EUI)

The EUI data is stored at locations 810Ah to 8111h in the program memory region. This region is an optional space for placing application specific information. The data is coded per customer requirements during manufacturing. The EUI cannot be erased by a Bulk Erase command.

Note: Data is stored in this address range on receiving a request from the customer. The customer may contact the local sales representative or Field Applications Engineer, and provide them the unique identifier information that is required to be stored in this region.

# 6.3 Analog-to-Digital Conversion Data of the Temperature Sensor

The purpose of the temperature indicator module is to provide a temperature-dependent voltage that can be measured by an analog module. **Section 19.0 "Temperature Indicator Module**" explains the operation of the Temperature Indicator module and defines terms such as the low range and high range settings of the sensor.

The DIA table contains the internal ADC measurement values of the temperature sensor for low and high range at fixed points of reference. The values are measured during test and are unique to each device. The right-justified ADC readings are stored in the DIA memory region. The calibration data can be used to plot the approximate sensor output voltage, VTSENSE vs. Temperature curve.

- **TSLR<3:1>**: Address 8112h to 8114h store the measurements for the low range setting of the temperature sensor at VDD = 3V.

- TSHR<3:1>: Address 8115h to 8117h store the measurements for the high range setting of the temperature sensor at VDD = 3V.

The stored measurements are made by the device ADC using the internal VREF = 2.048V.

# 6.4 Fixed Voltage Reference Data

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- ADC positive reference

- Comparator positive input

- Digital-to-Analog Converter

For more information on the FVR, refer to **Section 18.0 "Fixed Voltage Reference (FVR)"**.

The DIA stores measured FVR voltages for this device in mV for the different buffer settings of 1x, 2x or 4x at program memory locations 8118h to 811Dh.

- FVRA1X stores the value of ADC FVR1 Output voltage for 1x setting (in mV)

- FVRA2X stores the value of ADC FVR1 Output Voltage for 2x setting (in mV)

- FVRA4X stores the value of ADC FVR1 Output Voltage for 4x setting (in mV)

- FVRC1X stores the value of Comparator FVR2 output voltage for 1x setting (in mV)

- FVRC2X stores the value of Comparator FVR2 output voltage for 2x setting (in mV)

- FVRC4X stores the value of Comparator FVR2 output voltage for 4x setting (in mV)

## 8.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

# 8.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 8-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 8-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |  |  |  |  |  |  |

|------------|--------|-------------|----------|---------------------------------------------------------------------|--|--|--|--|--|--|

| 11         | Х      | Х           | Active   | Wait for release of BOR <sup>(1)</sup> (BORRDY = 1)                 |  |  |  |  |  |  |

| 1.0        | 37     | Awake       | Active   | Waits for release of BOR (BORRDY = 1)                               |  |  |  |  |  |  |

| 10         | Х      | Sleep       | Disabled | Waits for BOR Reset release                                         |  |  |  |  |  |  |

| 0.1        | 1      | x           | Active   | Waits for BOR Reset release (BORRDY = 1)                            |  |  |  |  |  |  |

| 01         | 0      | х           | Disabled | Paging immediately (POPPDY =)                                       |  |  |  |  |  |  |

| 00         | Х      | Х           | Disabled | Begins immediately (BORRDY = x)                                     |  |  |  |  |  |  |

## TABLE 8-1: BOR OPERATING MODES

**Note 1:** In this specific case, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 8.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 8.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

## 8.4 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) is an important part of the Reset subsystem. Refer to Figure 8-1 to see how the BOR and LPBOR interact with other modules.

The LPBOR is used to monitor the external VDD pin. When too low of a voltage is detected, the device is held in Reset.

# 8.4.1 ENABLING LPBOR

The LPBOR is controlled by the  $\overrightarrow{LPBOR}$  bit of the Configuration Word (Register 5-1). When the device is erased, the LPBOR module defaults to disabled.

## 8.4.2 LPBOR MODULE OUTPUT

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The same bit is set for either the BOR or the LPBOR (refer to Register 8-3). This signal is OR'd with the output of the BOR module to provide the generic BOR signal, which goes to the PCON register and to the power control block. Refer to Figure 8-1 for the OR gate connections of the BOR and LPBOR Reset signals, which eventually generates one common BOR Reset.

# 8.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 8-2).

TABLE 8-2:

MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

# 8.5.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up. Refer to **Section 2.3 "Master Clear (MCLR) Pin"** for recommended MCLR connections.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

**Note:** A Reset does not drive the MCLR pin low.

# 8.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 14.1 "I/O Priorities"** for more information.

# 8.6 Windowed Watchdog Timer (WWDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period and the window is open. The TO and PD bits in the STATUS register and the WDT bit in PCON are changed to indicate a WDT Reset caused by the timer overflowing, and WDTWV bit in the PCON register is changed to indicate a WDT Reset caused by a window violation. See **Section 12.0 "Windowed Watchdog Timer (WWDT)"** for more information.

# 8.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 8-4 for default conditions after a RESET instruction has occurred.

# 8.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 4.5.2** "**Overflow/Underflow Reset**" for more information.

# 8.9 Programming Mode Exit

Upon exit of In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) mode, the device will behave as if a POR had just occurred (the device does not reset upon run time self-programming/erase operations).

# 8.10 Power-up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\mathsf{PWRTE}}$  bit of the Configuration Words.

The Power-up Timer provides a nominal 64 ms time out on POR or Brown-out Reset. The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in the Configuration Words. The Power-up Timer starts after the release of the POR and BOR. For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*" (DS00607).

PIC16(L)F15356/75/76/85/86

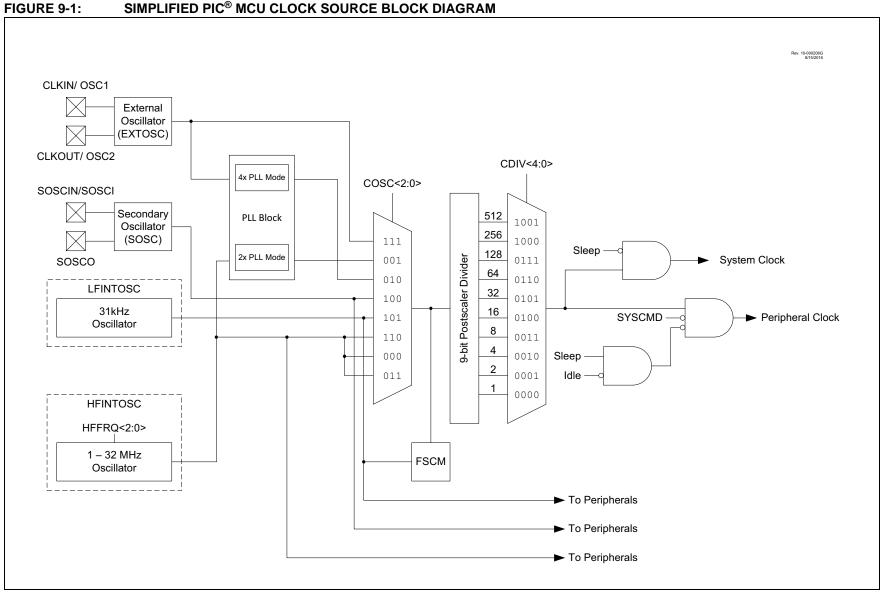

# SIMPLIFIED PIC® MCU CLOCK SOURCE BLOCK DIAGRAM

© 2016 Microchip Technology Inc

Preliminary

# **10.0 INTERRUPTS**

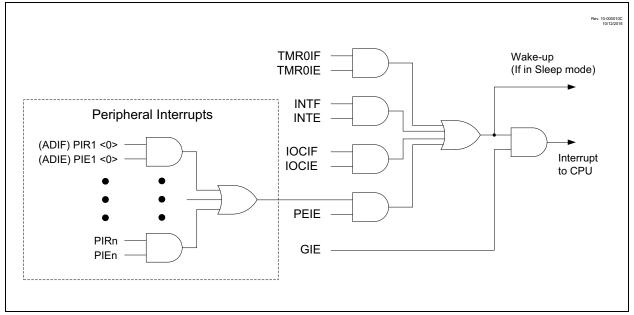

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 10-1.

#### FIGURE 10-1: INTERRUPT LOGIC

# PIC16(L)F15356/75/76/85/86

© 2016 Microchip Technology Inc.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSD<7:0>**: Analog Select between Analog or Digital Function on Pins RD<7:0>, respectively<sup>(1)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### REGISTER 14-29: WPUD: WEAK PULL-UP PORTD REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2   | WPUD1   | WPUD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUD<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# 21.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC1) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DAC1OUT pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DAC1EN bit of the DAC1CON0 register.

# EQUATION 21-1: DAC OUTPUT VOLTAGE

# 21.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DAC1R<4:0> bits of the DAC1CON1 register.

The DAC output voltage is determined by Equation 21-1:

$V_{OUT} = \left( V_{SOURCE+} - V_{SOURCE-} \times \frac{DAC1R\langle 4:0 \rangle}{2^5} \right) + (V_{SOURCE-})$  $V_{SOURCE+} = V_{DD} \quad or \quad V_{REF+} \quad or \; FVR$  $V_{SOURCE-} = V_{SS} \quad or \; V_{REF-}$

# 21.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 37-15.

# 21.3 DAC Voltage Reference Output

The DAC voltage can be output to the DAC1OUT1/2 pins by setting the DAC1OE1/2 bits of the DAC1CON0 register, respectively. Selecting the DAC reference voltage for output on the DAC1OUT1/2 pins automatically overrides the digital output buffer and digital input threshold detector functions, disables the weak pull-up, and disables the current-controlled drive function of that pin. Reading the DAC1OUT1/2 pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to the DAC1OUT1/2 pins. Figure 21-2 shows an example buffering technique.

© 2016 Microchip Technology Inc.

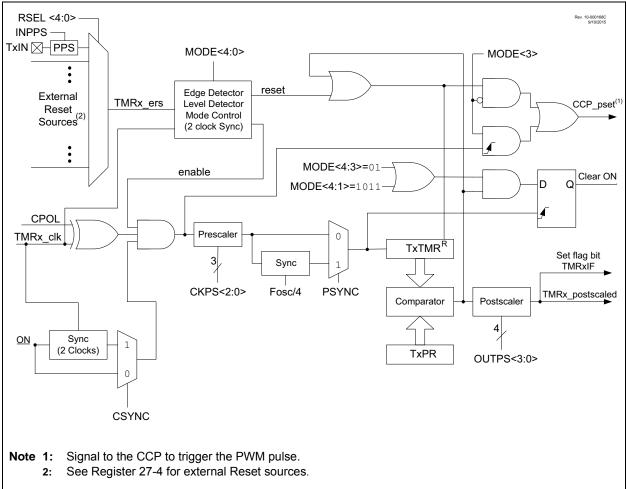

# 27.0 TIMER2 MODULE WITH HARDWARE LIMIT TIMER (HLT)

The Timer2 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- 8-bit period register

- · Selectable external hardware timer Resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- · Selectable synchronous/asynchronous operation

- Alternate clock sources

- Interrupt-on-period

- · Three modes of operation:

- Free Running Period

- One-shot

- Monostable

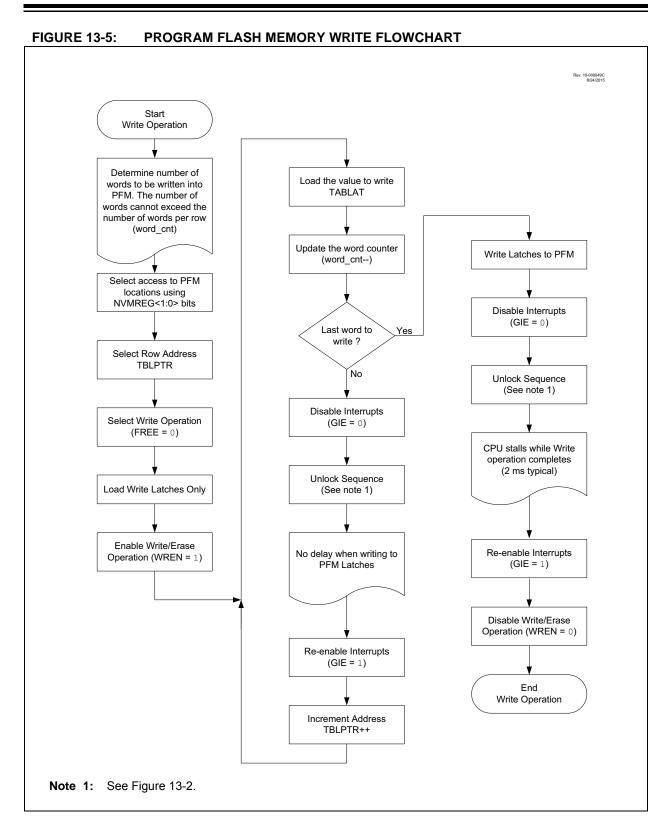

See Figure 27-1 for a block diagram of Timer2. See Figure 27-2 for the clock source block diagram.

# FIGURE 27-1: TIMER2 BLOCK DIAGRAM

# © 2016 Microchip Technology Inc.

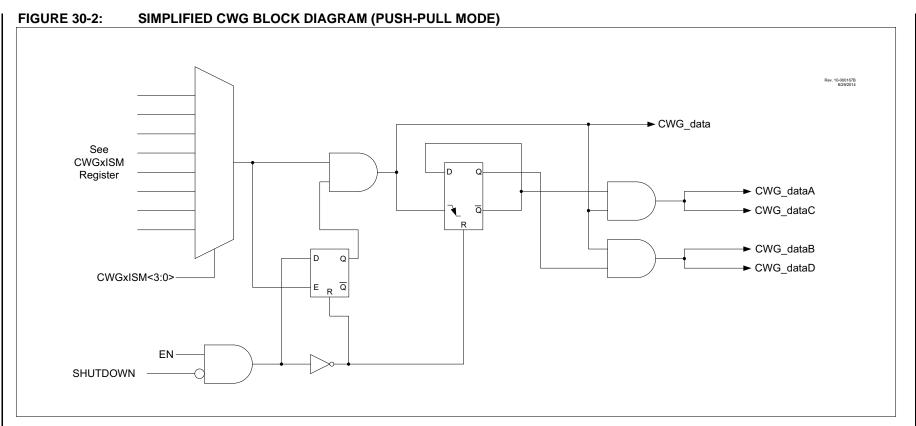

## 30.10 Auto-Shutdown

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software. The auto-shutdown circuit is illustrated in Figure 30-12.

#### 30.10.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External Input

#### 30.10.1.1 Software Generated Shutdown

Setting the SHUTDOWN bit of the CWG1AS0 register will force the CWG into the shutdown state.

When the auto-restart is disabled, the shutdown state will persist as long as the SHUTDOWN bit is set.

When auto-restart is enabled, the SHUTDOWN bit will clear automatically and resume operation on the next rising edge event.

#### 30.10.2 EXTERNAL INPUT SOURCE

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Several input sources can be selected to cause a shutdown condition. All input sources are active-low. The sources are:

- Comparator C1OUT\_sync

- Comparator C2OUT\_sync

- · Timer2 TMR2\_postscaled

- CWG1IN input pin

Shutdown inputs are selected using the CWG1AS1 register (Register 30-6).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

#### 30.11 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep when all the following conditions are met:

- CWG module is enabled

- · Input source is active

- HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, then the CPU will go idle during Sleep, but the HFINTOSC will remain active and the CWG will continue to operate. This will have a direct effect on the Sleep mode current.

| TABLE 31-4: | SUMMARY OF REGISTERS ASSOCIATED WITH CLCx (continued) |

|-------------|-------------------------------------------------------|

|-------------|-------------------------------------------------------|

| Name      | Bit 7 | Bit 6 | Bit 5    | Bit 4          | Bit 3    | Bit 2    | Bit 1    | Bit 0    |     |  |

|-----------|-------|-------|----------|----------------|----------|----------|----------|----------|-----|--|

| CLC4GLS1  | —     |       | LC4G2D3T | LC4G2D3N       | LC4G2D2T | LC4G2D2N | LC4G2D1T | LC4G2D1N | 414 |  |

| CLC4GLS2  | —     |       | LC4G3D3T | LC4G3D3N       | LC4G3D2T | LC4G3D2N | LC4G3D1T | LC4G3D1N | 415 |  |

| CLC4GLS3  | _     | _     | LC4G4D3T | LC4G4D3N       | LC4G4D2T | LC4G4D2N | LC4G4D1T | LC4G4D1N | 416 |  |

| CLCIN0PPS | _     | _     |          | CLCIN0PPS<5:0> |          |          |          |          |     |  |

| CLCIN1PPS | _     | _     |          | CLCIN1PPS<5:0> |          |          |          |          |     |  |

| CLCIN2PPS | _     | _     |          | CLCIN2PPS<5:0> |          |          |          |          |     |  |

| CLCIN3PPS | _     | _     |          |                | CLCIN3   | PPS<5:0> |          |          | 241 |  |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

|  | REGISTER 32-4: | SSPxCON3: SSPx CONTROL REGISTER 3 |

|--|----------------|-----------------------------------|

|--|----------------|-----------------------------------|

| R-0/0          | R/W-0/0                     | R/W-0/0                                          | R/W-0/0                       | R/W-0/0                         | R/W-0/0                                         | R/W-0/0             | R/W-0/0          |

|----------------|-----------------------------|--------------------------------------------------|-------------------------------|---------------------------------|-------------------------------------------------|---------------------|------------------|

| ACKTIM         | <sup>3)</sup> PCIE          | SCIE                                             | BOEN                          | SDAHT                           | SBCDE                                           | AHEN                | DHEN             |

| bit 7          | <u>.</u>                    |                                                  |                               |                                 | •                                               |                     | bit              |

|                |                             |                                                  |                               |                                 |                                                 |                     |                  |

| Legend:        |                             |                                                  |                               |                                 |                                                 |                     |                  |

| R = Readab     | ole bit                     | W = Writable b                                   | bit                           | U = Unimplem                    | ented bit, read as                              | ʻ0'                 |                  |

| u = Bit is ur  | changed                     | x = Bit is unkn                                  | own                           | -n/n = Value at                 | POR and BOR/V                                   | alue at all other l | Resets           |

| '1' = Bit is s | et                          | '0' = Bit is clea                                | red                           |                                 |                                                 |                     |                  |

|                |                             |                                                  | 0                             | (2)                             |                                                 |                     |                  |

| bit 7          |                             | nowledge Time S                                  |                               |                                 | oth curr                                        |                     |                  |

|                |                             | the I <sup>2</sup> C bus is in a knowledge seque |                               |                                 | on 8 <sup>th</sup> falling edge<br>of SCL clock | of SCL clock        |                  |

| bit 6          |                             | ondition Interrupt                               |                               |                                 |                                                 |                     |                  |

|                |                             | errupt on detection                              |                               |                                 |                                                 |                     |                  |

|                |                             | ction interrupts ar                              |                               |                                 |                                                 |                     |                  |

| bit 5          |                             | ondition Interrupt                               | •                             | • ·                             |                                                 |                     |                  |

|                |                             | errupt on detection ction interrupts ar          |                               | start conditions                |                                                 |                     |                  |

| oit 4          |                             | Overwrite Enabl                                  |                               |                                 |                                                 |                     |                  |

| 511 4          | In SPI Slave n              |                                                  |                               |                                 |                                                 |                     |                  |

|                |                             |                                                  |                               |                                 | shifted in ignoring                             |                     |                  |

|                |                             | •                                                |                               |                                 | egister already se                              | et, SSPOV bit of    | the SSPxCON      |

|                | · · ·                       | ster is set, and the<br>mode and SPI M           | •                             | dated                           |                                                 |                     |                  |

|                | In I <sup>2</sup> C Slave m |                                                  |                               |                                 |                                                 |                     |                  |

|                |                             |                                                  |                               | nerated for a rec               | eived address/da                                | ita byte, ignoring  | the state of th  |

|                |                             | OV bit only if the<br>xBUF is only upda          |                               | )V is clear                     |                                                 |                     |                  |

| oit 3          |                             | Hold Time Selec                                  |                               |                                 |                                                 |                     |                  |

|                |                             | of 300 ns hold tin                               | •                             | • ·                             | of SCL                                          |                     |                  |

|                |                             | of 100 ns hold tin                               |                               |                                 |                                                 |                     |                  |

| oit 2          | SBCDE: Slave                | e Mode Bus Colli                                 | sion Detect Ena               | ble bit (I <sup>2</sup> C Slave | e mode only)                                    |                     |                  |

|                |                             | g edge of SCL, SI<br>is set, and bus go          |                               | w when the moo                  | lule is outputting a                            | a high state, the E | 3CL1IF bit of th |

|                |                             | ave bus collision i collision i                  | •                             |                                 |                                                 |                     |                  |

| oit 1          | AHEN: Addres                | ss Hold Enable b                                 | it (I <sup>2</sup> C Slave mo | de only)                        |                                                 |                     |                  |

|                |                             | the eighth falling will be cleared an            |                               |                                 | eceived address                                 | byte; CKP bit of    | the SSPxCON      |

|                |                             | olding is disabled                               |                               |                                 |                                                 |                     |                  |

| bit 0          |                             | Hold Enable bit (I                               |                               |                                 | 4a budau alawa 1                                |                     |                  |

|                |                             | N1 register and S                                |                               | or a received da                | ta byte; slave ha                               | rdware clears the   | e CKP bit of tr  |

| Note 1:        | For daisy-chained S         | SPI operation; allo                              | ws the user to ic             | nore all but the                | ast received byte                               | . SSPOV is still s  | et when a new    |

|                | byte is received and        |                                                  |                               |                                 |                                                 |                     |                  |

| 2:             | This bit has no effect      | ct in Slave modes                                | s that Start and S            | Stop condition de               | tection is explicit                             | y listed as enable  | ed.              |

- 2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

- 3: The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

# PIC16(L)F15356/75/76/85/86

# **REGISTER 33-7:** SPxBRGH<sup>(1, 2)</sup>: BAUD RATE GENERATOR HIGH REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| SPxBRG<15:8> |       |       |       |       |       |       |       |  |  |  |

| bit 7        |       |       |       |       |       |       | bit 0 |  |  |  |

|              |       |       |       |       |       |       |       |  |  |  |

| Legend:      |       |       |       |       |       |       |       |  |  |  |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 SPxBRG<15:8>: Upper eight bits of the Baud Rate Generator

**Note 1:** SPxBRGH value is ignored for all modes unless BAUDxCON<BRG16> is active.

2: Writing to SPxBRGH resets the BRG counter.

| Name     | Bit 7       | Bit 6           | Bit 5  | Bit 4      | Bit 3   | Bit 2       | Bit 1  | Bit 0  | Register<br>on Page |  |  |

|----------|-------------|-----------------|--------|------------|---------|-------------|--------|--------|---------------------|--|--|

| INTCON   | GIE         | PEIE            | -      | _          | _       | —           | _      | INTEDG | 146                 |  |  |

| PIR3     | RC2IF       | TX2IF           | RC1IF  | TX1IF      | BCL2IF  | SSP2IF      | BCL1IF | SSP1IF | 158                 |  |  |

| PIE3     | RC2IE       | TX2IE           | RC1IE  | TX1IE      | BCL2IE  | SSP2IE      | BCL1IE | SSP1IE | 150                 |  |  |

| RCxSTA   | SPEN        | RX9             | SREN   | CREN       | ADDEN   | FERR        | OERR   | RX9D   | 491                 |  |  |

| TXxSTA   | CSRC        | TX9             | TXEN   | SYNC       | SENDB   | BRGH        | TRMT   | TX9D   | 490                 |  |  |

| BAUDxCON | ABDOVF      | RCIDL           | _      | SCKP       | BRG16   | —           | WUE    | ABDEN  | 492                 |  |  |

| RCxREG   | EUSART Rec  | eive Data Regis | ter    |            |         |             |        |        | 493*                |  |  |

| TXxREG   | EUSART Trar | nsmit Data Reg  | lister |            |         |             |        |        | 493*                |  |  |

| SPxBRGL  |             |                 |        | SPxBR      | G<7:0>  |             |        |        | 493*                |  |  |

| SPxBRGH  |             |                 |        | SPxBR      | G<15:8> |             |        |        | 494*                |  |  |

| RXPPS    | _           | —               |        |            | RXPP    | S<5:0>      |        |        | 241                 |  |  |

| CKPPS    | _           | _               |        | CXPPS<5:0> |         |             |        |        |                     |  |  |

| RxyPPS   | _           | —               | _      |            | F       | RxyPPS<4:0> |        |        | 242                 |  |  |

| CLCxSELy | _           |                 |        |            | LCxDy   | S<5:0>      |        |        | 412                 |  |  |

#### SUMMARY OF REGISTERS ASSOCIATED WITH EUSART TABLE 33-2:

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the EUSART module. \*

Page with register information.

# TABLE 37-11: RESET, WDT, OSCILLATOR START-UP TIMER, POWER-UP TIMER, BROWN-OUT RESET AND LOW-POWER BROWN-OUT RESET SPECIFICATIONS

| Standard      | Standard Operating Conditions (unless otherwise stated) |                                                   |                      |                      |                           |                     |                                                           |  |  |  |

|---------------|---------------------------------------------------------|---------------------------------------------------|----------------------|----------------------|---------------------------|---------------------|-----------------------------------------------------------|--|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                                    | Min.                 | Тур†                 | Max.                      | Units               | Conditions                                                |  |  |  |

| RST01*        | TMCLR                                                   | MCLR Pulse Width Low to ensure Reset              | 2                    | _                    | _                         | μS                  |                                                           |  |  |  |

| RST02*        | Tioz                                                    | I/O high-impedance from Reset detection           |                      |                      | 2                         | μS                  |                                                           |  |  |  |

| RST03         | Twdt                                                    | Watchdog Timer Time-out Period                    |                      | 16                   | _                         | ms                  | 16 ms Nominal Reset Time                                  |  |  |  |

| RST04*        | TPWRT                                                   | Power-up Timer Period                             | _                    | 65                   | _                         | ms                  |                                                           |  |  |  |

| RST05         | Tost                                                    | Oscillator Start-up Timer Period <sup>(1,2)</sup> |                      | 1024                 | — /                       | ∕~ <del>T</del> osc |                                                           |  |  |  |

| RST06         | VBOR                                                    | Brown-out Reset Voltage <sup>(4)</sup>            | 2.55<br>2.30<br>1.80 | 2.70<br>2.45<br>1.90 | 2.85<br>2.60<br>2.05      |                     | BORV = 0<br>BORV = 1 (F devices)<br>BORV = 1 (LF devices) |  |  |  |

| RST07         | VBORHYS                                                 | Brown-out Reset Hysteresis                        |                      | 40 🧹                 | $\overline{)}$            | m∖V ′               |                                                           |  |  |  |

| RST08         | TBORDC                                                  | Brown-out Reset Response Time                     | —                    | 3                    | $\backslash - \backslash$ | μs                  | $\rangle$                                                 |  |  |  |

| RST09         | VLPBOR                                                  | Low-Power Brown-out Reset Voltage                 | 1.8                  | / 1.9-               | 22                        | V V                 | LF Devices Only                                           |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 37-12: ANALOG-TO-DIGITAL CONVERTER (ADC) ACCURACY SPECIFICATIONS<sup>(1,2)</sup>:

|               | Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |                                                |          |      |        |       |                             |  |  |  |

|---------------|----------------------------------------------------------------------------------|------------------------------------------------|----------|------|--------|-------|-----------------------------|--|--|--|

| Param.<br>No. | Sym.                                                                             | Characteristic                                 | Min.     | Typt | Max.   | Units | Conditions                  |  |  |  |

| AD01          | NR                                                                               | Resolution                                     | $\sim$   | _    | 10     | bit   |                             |  |  |  |

| AD02          | EIL                                                                              | Integral Error                                 | $\geq -$ | ±0.1 | ±1.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |  |

| AD03          | Edl                                                                              | Differential Error                             |          | ±0.1 | ±1.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |  |

| AD04          | EOFF                                                                             | Offset Error                                   | _        | 0.5  | 2.0    | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |  |

| AD05          | Egn                                                                              | Gain Error 🗸 🖊 🔨                               | —        | ±0.2 | ±1.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |  |

| AD06          | VADREF                                                                           | ADC Reference Voltage<br>(ADREF+ - ADREF-)     | 1.8      |      | Vdd    | V     |                             |  |  |  |

| AD07          | Vain                                                                             | Fulf-Scale Range                               | ADREF-   | _    | ADREF+ | V     |                             |  |  |  |

| AD08          | ZAIN                                                                             | Recommended Impedance of Analog Voltage Source | _        | 10   | —      | kΩ    |                             |  |  |  |

| AD09          | RVREF                                                                            | ADC Voltage Reference Ladder<br>Impedance      | —        | 50   | —      | kΩ    | Note 3                      |  |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error is the sum of the offset, gain and integral non-linearity (INL) errors.

2: The ABC conversion result never decreases with an increase in the input and has no missing codes.

3: This is the impedance seen by the VREF pads when the external reference pads are selected.

<sup>Note 1: By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

2: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible.</sup> 0.1 μF and 0.01 μF values in parallel are recommended.

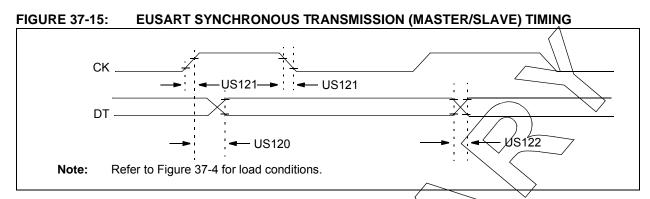

# TABLE 37-21: EUSART SYNCHRONOUS TRANSMISSION CHARACTERISTICS

| Param.<br>No.                | Symbol                       | Characteristic                    | Min.                | Max. | Units                            | Conditions                       |

|------------------------------|------------------------------|-----------------------------------|---------------------|------|----------------------------------|----------------------------------|

| JS120                        | TCKH2DTV                     | SYNC XMIT (Master and Slave)      |                     | 80   | ns                               | $3.0V \le V\text{DD} \le 5.5V$   |

| Clock high to data-out valid | Clock high to data-out valid | $\langle - \rangle$               | 100                 | ns   | $1.8V \leq V\text{DD} \leq 5.5V$ |                                  |

| US121                        | TCKRF                        | Clock out rise time and fall time | $\langle - \rangle$ | 45   | ns                               | $3.0V \leq V\text{DD} \leq 5.5V$ |

|                              |                              | (Master mode)                     |                     | ✓ 50 | ns                               | $1.8V \leq V\text{DD} \leq 5.5V$ |

| US122                        | TDTRF                        | Data-out rise time and fall time  | $\langle \rangle$   | 45   | ns                               | $3.0V \leq V\text{DD} \leq 5.5V$ |

|                              |                              |                                   | $\overline{)}$      | 50   | ns                               | $1.8V \le V\text{DD} \le 5.5V$   |

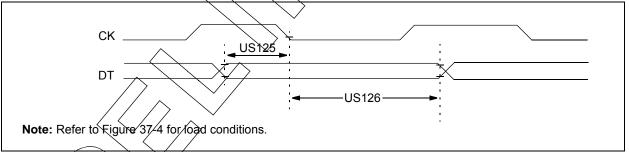

# FIGURE 37-16: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

# TABLE 37-22: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating C | Standard Operating Conditions (unless otherwise stated)                         |      |      |       |            |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------|------|------|-------|------------|--|--|--|--|--|

| Param.<br>No. Symbol | > Characteristic                                                                | Min. | Max. | Units | Conditions |  |  |  |  |  |

|                      | SYNC RCV (Master and Slave)<br>Data-setup before CK $\downarrow$ (DT hold time) | 10   | _    | ns    |            |  |  |  |  |  |

| US126 TCKL2DTL       | Data-hold after CK $\downarrow$ (DT hold time)                                  | 15   |      | ns    |            |  |  |  |  |  |

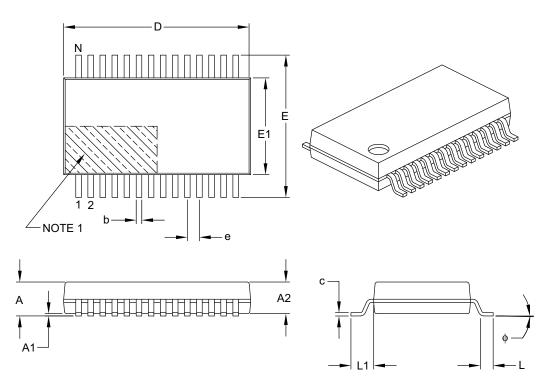

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |       |  |

|--------------------------|------------------|-------------|----------|-------|--|

|                          | Dimension Limits | MIN         | NOM      | MAX   |  |

| Number of Pins           | N                |             | 28       |       |  |

| Pitch                    | е                |             | 0.65 BSC |       |  |

| Overall Height           | А                | _           | -        | 2.00  |  |

| Molded Package Thickness | A2               | 1.65        | 1.75     | 1.85  |  |

| Standoff                 | A1               | 0.05        | -        | -     |  |

| Overall Width            | E                | 7.40        | 7.80     | 8.20  |  |

| Molded Package Width     | E1               | 5.00        | 5.30     | 5.60  |  |

| Overall Length           | D                | 9.90        | 10.20    | 10.50 |  |

| Foot Length              | L                | 0.55        | 0.75     | 0.95  |  |

| Footprint                | L1               | 1.25 REF    |          |       |  |

| Lead Thickness           | С                | 0.09        | -        | 0.25  |  |

| Foot Angle               | φ                | 0°          | 4°       | 8°    |  |

| Lead Width               | b                | 0.22        | -        | 0.38  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

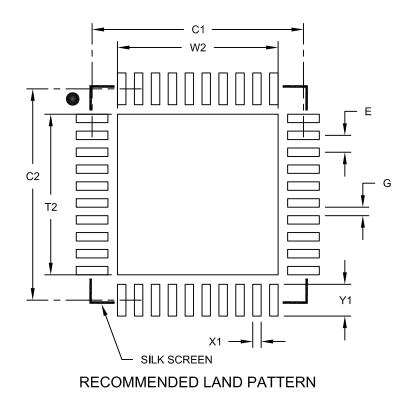

## 40-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 5x5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |                  | <b>ILLIMETER</b> |      |      |

|----------------------------|------------------|------------------|------|------|

|                            | Units            |                  |      |      |

| Dimensio                   | Dimension Limits |                  |      | MAX  |

| Contact Pitch              | E                | 0.40 BSC         |      |      |

| Optional Center Pad Width  | W2               |                  |      | 3.80 |

| Optional Center Pad Length | T2               |                  |      | 3.80 |

| Contact Pad Spacing        | C1               | 5.00             |      |      |

| Contact Pad Spacing        | C2               |                  | 5.00 |      |

| Contact Pad Width (X40)    | X1               |                  |      | 0.20 |

| Contact Pad Length (X40)   | Y1               | 0.75             |      |      |

| Distance Between Pads      | G                | 0.20             |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2156B