Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15375-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **PIN DIAGRAMS**

| 28-PIN PDIP, SOIC, SSOP |                                                                                                                                                                | $\bigcirc$                       | 28 RB7/ICSPDAT                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         | RA0 2                                                                                                                                                          |                                  | 27 RB6/ICSPCLK                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                         | RA1 3                                                                                                                                                          |                                  | 26 RB5                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | RA2 4                                                                                                                                                          |                                  | 25 RB4                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | RA3 5                                                                                                                                                          |                                  | 24 П RB3                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                         | RA4 🗌 6                                                                                                                                                        | 356                              | 23 RB2                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | RA5 7                                                                                                                                                          | F15                              | 22 RB1                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | Vss 🗌 8                                                                                                                                                        | 6(L)                             | 21 RB0                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | RA7 🗌 9                                                                                                                                                        | PIC16(L)F15356                   |                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                         | RA6 🗌 10                                                                                                                                                       | <u>م</u>                         | 19 Vss                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | RC0 🗌 11                                                                                                                                                       |                                  | 18 RC7                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | RC1 🗌 12                                                                                                                                                       |                                  | 17 RC6                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | RC2 🗌 13                                                                                                                                                       |                                  | 16 RC5                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | RC3 🗌 14                                                                                                                                                       |                                  | 15 RC4                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Note 1 See Table        | e 2 for location of all peripheral fun                                                                                                                         | nctions                          |                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                         | nd all Vss pins must be connected                                                                                                                              |                                  | ircuit board level                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                         |                                                                                                                                                                |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                         |                                                                                                                                                                |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                         |                                                                                                                                                                |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 40-PIN PDIP             |                                                                                                                                                                | $\bigcirc$                       |                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 40-PIN PDIP             |                                                                                                                                                                | $\bigcirc$                       |                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 40-PIN PDIP             | RA0 2                                                                                                                                                          | $\bigcirc$                       | 39 RB6/ICSPCLK                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3                                                                                                                                                 | $\bigcirc$                       | 39 RB6/ICSPCLK<br>38 RB5                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 40-PIN PDIP             | RA0 [] 2<br>RA1 [] 3<br>RA2 [] 4                                                                                                                               |                                  | 39 RB6/ICSPCLK<br>38 RB5<br>37 RB4                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5                                                                                                                               |                                  | 39 RB6/ICSPCLK<br>38 RB5<br>37 RB4<br>36 RB3                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6                                                                                                                      |                                  | 39 RB6/ICSPCLK<br>38 RB5<br>37 RB4<br>36 RB3<br>35 RB2                                                                                                                                                                                                                                                                                                                                                                             |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7                                                                                                             |                                  | 39 RB6/ICSPCLK<br>38 RB5<br>37 RB4<br>36 RB3<br>35 RB2<br>34 RB1                                                                                                                                                                                                                                                                                                                                                                   |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8                                                                                                    | 75                               | 39 RB6/ICSPCLK<br>38 RB5<br>37 RB4<br>36 RB3<br>35 RB2                                                                                                                                                                                                                                                                                                                                                                             |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7                                                                                                             | 15375                            | 39 RB6/ICSPCLK<br>38 RB5<br>37 RB4<br>36 RB3<br>35 RB2<br>34 RB1<br>33 RB0                                                                                                                                                                                                                                                                                                                                                         |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9                                                                                           | (L)F15375<br>(L)F15376           | 39 RB6/ICSPCLK<br>38 RB5<br>37 RB4<br>36 RB3<br>35 RB2<br>34 RB1<br>33 RB0<br>32 VDD                                                                                                                                                                                                                                                                                                                                               |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9<br>RE2 10                                                                                 | C16(L)F15375<br>C16(L)F15376     | <ul> <li>39 RB6/ICSPCLK</li> <li>38 RB5</li> <li>37 RB4</li> <li>36 RB3</li> <li>35 RB2</li> <li>34 RB1</li> <li>33 RB0</li> <li>32 VDD</li> <li>31 VSS</li> </ul>                                                                                                                                                                                                                                                                 |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9<br>RE2 10<br>VDD 11<br>VSS 12                                                             | PIC16(L)F15375<br>PIC16(L)F15376 | <ul> <li>39</li> <li>RB6/ICSPCLK</li> <li>38</li> <li>RB5</li> <li>37</li> <li>RB4</li> <li>36</li> <li>RB3</li> <li>35</li> <li>RB2</li> <li>34</li> <li>RB1</li> <li>33</li> <li>RB0</li> <li>32</li> <li>VDD</li> <li>31</li> <li>VSS</li> <li>30</li> <li>RD7</li> </ul>                                                                                                                                                       |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9<br>RE2 10<br>VDD 11<br>VSS 12                                                             | PIC16(L)F15375<br>PIC16(L)F15376 | <ul> <li>39 RB6/ICSPCLK</li> <li>38 RB5</li> <li>37 RB4</li> <li>36 RB3</li> <li>35 RB2</li> <li>34 RB1</li> <li>33 RB0</li> <li>32 VDD</li> <li>31 VSS</li> <li>30 RD7</li> <li>29 RD6</li> </ul>                                                                                                                                                                                                                                 |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9<br>RE2 10<br>VDD 11<br>VSS 12<br>RA7 13                                                   | PIC16(L)F15375<br>PIC16(L)F15376 | <ul> <li>39 RB6/ICSPCLK</li> <li>38 RB5</li> <li>37 RB4</li> <li>36 RB3</li> <li>35 RB2</li> <li>34 RB1</li> <li>33 RB0</li> <li>32 VDD</li> <li>31 VSS</li> <li>30 RD7</li> <li>29 RD6</li> <li>28 RD5</li> </ul>                                                                                                                                                                                                                 |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9<br>RE2 10<br>VDD 11<br>VSS 12<br>RA7 13<br>RA6 14                                         | PIC16(L)F15375<br>PIC16(L)F15376 | <ul> <li>39 RB6/ICSPCLK</li> <li>38 RB5</li> <li>37 RB4</li> <li>36 RB3</li> <li>35 RB2</li> <li>34 RB1</li> <li>33 RB0</li> <li>32 VDD</li> <li>31 VSS</li> <li>30 RD7</li> <li>29 RD6</li> <li>28 RD5</li> <li>27 RD4</li> </ul>                                                                                                                                                                                                 |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9<br>RE2 10<br>VDD 11<br>VSS 12<br>RA7 13<br>RA6 14<br>RC0 15                               | PIC16(L)F15375<br>PIC16(L)F15376 | <ul> <li>39 RB6/ICSPCLK</li> <li>38 RB5</li> <li>37 RB4</li> <li>36 RB3</li> <li>35 RB2</li> <li>34 RB1</li> <li>33 RB0</li> <li>32 VDD</li> <li>31 VSS</li> <li>30 RD7</li> <li>29 RD6</li> <li>28 RD5</li> <li>27 RD4</li> <li>26 RC7</li> </ul>                                                                                                                                                                                 |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9<br>RE2 10<br>VDD 11<br>VSS 12<br>RA7 13<br>RA6 14<br>RC0 15<br>RC1 16<br>RC2 17<br>RC3 18 | PIC16(L)F15375<br>PIC16(L)F15376 | <ul> <li>39 RB6/ICSPCLK</li> <li>38 RB5</li> <li>37 RB4</li> <li>36 RB3</li> <li>35 RB2</li> <li>34 RB1</li> <li>33 RB0</li> <li>32 VDD</li> <li>31 VSS</li> <li>30 RD7</li> <li>29 RD6</li> <li>28 RD5</li> <li>27 RD4</li> <li>26 RC7</li> <li>25 RC6</li> </ul>                                                                                                                                                                 |  |

| 40-PIN PDIP             | RA0 2<br>RA1 3<br>RA2 4<br>RA3 5<br>RA4 6<br>RA5 7<br>RE0 8<br>RE1 9<br>RE2 10<br>VDD 11<br>VSS 12<br>RA7 13<br>RA6 14<br>RC0 15<br>RC1 16<br>RC2 17           | PIC16(L)F15375<br>PIC16(L)F15376 | <ul> <li>39</li> <li>RB6/ICSPCLK</li> <li>38</li> <li>RB5</li> <li>37</li> <li>RB4</li> <li>36</li> <li>RB3</li> <li>35</li> <li>RB2</li> <li>34</li> <li>RB1</li> <li>33</li> <li>RB0</li> <li>32</li> <li>VDD</li> <li>31</li> <li>VSS</li> <li>30</li> <li>RD7</li> <li>29</li> <li>RD6</li> <li>28</li> <li>RD5</li> <li>27</li> <li>RD4</li> <li>26</li> <li>RC7</li> <li>25</li> <li>RC6</li> <li>24</li> <li>RC5</li> </ul> |  |

|       | Bank 60                |       | Bank 61    |       | Bank 62                |       | Bank 63     |

|-------|------------------------|-------|------------|-------|------------------------|-------|-------------|

| 1E3Fh | RE7PPS <sup>(2)</sup>  | 1EBFh | _          | 1F3Fh | IOCAF                  | 1FBFh | _           |

| 1E40h | _                      | 1EC0h | _          | 1F40h | _                      | 1FC0h | _           |

| 1E41h | _                      | 1EC1h | _          | 1F41h | _                      | 1FC1h | _           |

| 1E42h |                        | 1EC2h | _          | 1F42h | _                      | 1FC2h | _           |

| 1E43h |                        | 1EC3h | ADACTPPS   | 1F43h | ANSELB                 | 1FC3h | _           |

| 1E44h | _                      | 1EC4h | _          | 1F44h | WPUB                   | 1FC4h | _           |

| 1E45h | —                      | 1EC5h | SSP1CLKPPS | 1F45h | ODCONB                 | 1FC5h | _           |

| 1E46h | —                      | 1EC6h | SSP1DATPPS | 1F46h | SLRCONB                | 1FC6h | —           |

| 1E47h |                        | 1EC7h | SSP1SSPPS  | 1F47h | INLVLB                 | 1FC7h | —           |

| 1E48h | —                      | 1EC8h | SSP2CLKPPS | 1F48h | IOCBP                  | 1FC8h | —           |

| 1E49h | —                      | 1EC9h | SSP2DATPPS | 1F49h | IOCBN                  | 1FC9h | —           |

| 1E4Ah | _                      | 1ECAh | SSP2SSPPS  | 1F4Ah | IOCBF                  | 1FCAh | —           |

| 1E4Bh | —                      | 1ECBh | RXDT1PPS   | 1F4Bh | _                      | 1FCBh | —           |

| 1E4Ch | —                      | 1ECCh | TXCK1PPS   | 1F4Ch | _                      | 1FCCh | —           |

| 1E4Dh | —                      | 1ECDh | RXD2TPPS   | 1F4Dh | _                      | 1FCDh | —           |

| 1E4Eh | —                      | 1ECEh | TXCK2PPS   | 1F4Eh | ANSELC                 | 1FCEh | —           |

| 1E4Fh | —                      | 1ECFh | _          | 1F4Fh | WPUC                   | 1FCFh | _           |

| 1E50h | ANSELF <sup>(2)</sup>  | 1ED0h | —          | 1F50h | ODCONC                 | 1FD0h | —           |

| 1E51h | WPUF <sup>(2)</sup>    | 1ED1h | _          | 1F51h | SLRCONC                | 1FD1h | _           |

| 1E52h | ODCONF <sup>(2)</sup>  | 1ED2h | _          | 1F52h | INLVLC                 | 1FD2h | _           |

| 1E53h | SLRCONF <sup>(2)</sup> | 1ED3h | _          | 1F53h | IOCCP                  | 1FD3h | _           |

| 1E54h | INLVLF <sup>(2)</sup>  | 1ED4h | _          | 1F54h | IOCCN                  | 1FD4h | _           |

| 1E55h |                        | 1ED5h | _          | 1F55h | IOCCF                  | 1FD5h | _           |

| 1E56h |                        | 1ED6h | _          | 1F56h | _                      | 1FD6h | _           |

| 1E57h | _                      | 1ED7h | _          | 1F57h | _                      | 1FD7h | _           |

| 1E58h | _                      | 1ED8h | _          | 1F58h | _                      | 1FD8h | _           |

| 1E59h | —                      | 1ED9h | _          | 1F59h | ANSELD <sup>(1)</sup>  | 1FD9h | _           |

| 1E5Ah | _                      | 1EDAh | _          | 1F5Ah | WPUD <sup>(1)</sup>    | 1FDAh | _           |

| 1E5Bh | _                      | 1EDBh | _          | 1F5Bh | ODCOND <sup>(1)</sup>  | 1FDBh | _           |

| 1E5Ch | _                      | 1EDCh | _          | 1F5Ch | SLRCOND <sup>(1)</sup> | 1FDCh | _           |

| 1E5Dh | _                      | 1EDDh | _          | 1F5Dh | INLVLD <sup>(1)</sup>  | 1FDDh | _           |

| 1E5Eh | _                      | 1EDEh | _          | 1F5Eh | _                      | 1FDEh | _           |

| 1E5Fh |                        | 1EDFh | _          | 1F5Fh |                        | 1FDFh | _           |

| 1E60h | _                      | 1EE0h | _          | 1F60h |                        | 1FE0h | _           |

| 1E61h | _                      | 1EE1h | _          | 1F61h |                        | 1FE1h | _           |

| 1E62h | _                      | 1EE2h | _          | 1F62h | _                      | 1FE2h | _           |

| 1E63h | _                      | 1EE3h | _          | 1F63h | _                      | 1FE3h | BSR ICDSHAD |

| 1E64h | _                      | 1EE4h | _          | 1F64h | ANSELE <sup>(1)</sup>  | 1FE4h | STATUS SHAD |

| 1E65h | _                      | 1EE5h | _          | 1F65h | WPUE                   | 1FE5h | WREG_SHAD   |

| 1E66h | _                      | 1EE6h | _          | 1F66h | ODCONE <sup>(1)</sup>  | 1FE6h | BSR_SHAD    |

| 1E67h | _                      | 1EE7h | _          | 1F67h | SLRCONE <sup>(1)</sup> | 1FE7h | PCLATH SHAD |

| 1E68h | _                      | 1EE8h | _          | 1F68h | INLVLE                 | 1FE8h | FSR0L SHAD  |

| 1E69h | _                      | 1EE9h | _          | 1F69h | IOCEP                  | 1FE9h | FSR0H SHAD  |

| 1E6Ah |                        | 1EEAh | _          | 1F6Ah | IOCEN                  | 1FEAh | FSR1L SHAD  |

| 1E6Bh | _                      | 1EEBh | _          | 1F6Bh | IOCEF                  | 1FEBh | FSR1H_SHAD  |

| 1E6Ch |                        | 1EECh | _          | 1F6Ch |                        | 1FECh |             |

| 1E6Dh |                        | 1EEDh | _          | 1F6Dh | _                      | 1FEDh | STKPTR      |

| 1E6Eh |                        | 1EEEh | _          | 1F6Eh | _                      | 1FEEh | TOSL        |

| 1E6Fh |                        | 1EEFh | _          | 1F6Fh | _                      | 1FEFh | TOSH        |

# TABLE 4-9: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANKS 60, 61, 62, AND 63

Legend:

= Unimplemented data memory locations, read as '0'

**Note 1:** Present only on PIC16(L)F15375/76/85/86.

2: Present only on PIC16(L)F15385/86

### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address            |                                                                                                                                                         |  |  |  |  |  |  |   |  |  | V <u>alue o</u> n:<br>MCLR |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|---|--|--|----------------------------|

| Bank 13            |                                                                                                                                                         |  |  |  |  |  |  |   |  |  |                            |

|                    | CPU CORE REGISTERS; see Table 4-3 for specifics                                                                                                         |  |  |  |  |  |  |   |  |  |                            |

| 68Ch Unimplemented |                                                                                                                                                         |  |  |  |  |  |  | _ |  |  |                            |

| Legend:            | egend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. |  |  |  |  |  |  |   |  |  |                            |

|                       |                                                 | R/W-1                        | U-1                  | R/W-1                            | U-1            | R/W-1                           | R/W-1               |  |  |  |

|-----------------------|-------------------------------------------------|------------------------------|----------------------|----------------------------------|----------------|---------------------------------|---------------------|--|--|--|

|                       |                                                 | LVP                          | —                    | WRTSAF <sup>(1)</sup>            | —              | WRTC <sup>(1)</sup>             | WRTB <sup>(1)</sup> |  |  |  |

|                       |                                                 | bit 13                       | 12                   | 11                               | 10             | 9                               | bit 8               |  |  |  |

| R/W-1                 | U-1                                             | U-1                          | R/W-1                | R/W-1                            | R/W-1          | R/W-1                           | R/W-1               |  |  |  |

| WRTAPP <sup>(1)</sup> | 0-1                                             | 0-1                          | SAFEN <sup>(1)</sup> | BBEN <sup>(1)</sup>              | BBSIZE2        | BBSIZE1                         |                     |  |  |  |

|                       |                                                 |                              |                      |                                  |                | _                               | BBSIZE0             |  |  |  |

| bit 7                 | 6                                               | 5                            | 4                    | 3                                | 2              | 1                               | bit                 |  |  |  |

| Legend:               |                                                 |                              |                      |                                  |                |                                 |                     |  |  |  |

| R = Readable          | e bit                                           | P = Programı                 | nable bit            | x = Bit is unkn                  | own            | U = Unimplem<br>read as '1'     | nented bit,         |  |  |  |

| '0' = Bit is cleared  |                                                 | '1' = Bit is set             |                      | W = Writable t                   | bit            | n = Value whe<br>after Bulk Era |                     |  |  |  |

| bit 13                |                                                 | oltage Programr              | ning Enable bit      |                                  |                |                                 |                     |  |  |  |

|                       |                                                 |                              |                      | ICLR/VPP pin fu                  | nction is MCL  | R. MCLRE Cont                   | iguration bit i     |  |  |  |

|                       | ignored                                         |                              | 4 h a a a d fa a a   |                                  |                |                                 |                     |  |  |  |

|                       |                                                 | MCLR/VPP mus                 |                      | rogramming.<br>le operating fror | n tha LVD ara  | aromming intorf                 | ann Tha             |  |  |  |

|                       |                                                 |                              |                      | om dropping out                  |                |                                 |                     |  |  |  |

|                       |                                                 |                              |                      | e from the config                |                |                                 |                     |  |  |  |

|                       |                                                 | litioned (erased)            | •                    |                                  | garation state |                                 |                     |  |  |  |

| bit 12                | -                                               | nted: Read as '              |                      |                                  |                |                                 |                     |  |  |  |

| bit 11                | WRTSAF: Storage Area Flash Write Protection bit |                              |                      |                                  |                |                                 |                     |  |  |  |

|                       |                                                 | DT write-protect             |                      |                                  |                |                                 |                     |  |  |  |

|                       |                                                 | ite-protected                | cu                   |                                  |                |                                 |                     |  |  |  |

|                       |                                                 |                              | ot supported in      | the device famil                 | ly and only ap | plicable if SAFE                | <b>N</b> = 0.       |  |  |  |

| bit 10                |                                                 | nted: Read as '              |                      |                                  |                |                                 |                     |  |  |  |

| bit 9                 |                                                 | figuration Regis             |                      | ction bit                        |                |                                 |                     |  |  |  |

|                       |                                                 | uration Register             |                      |                                  |                |                                 |                     |  |  |  |

|                       |                                                 | uration Register             |                      |                                  |                |                                 |                     |  |  |  |

| bit 8                 | Ŭ                                               | t Block Write Pr             | •                    |                                  |                |                                 |                     |  |  |  |

|                       |                                                 | lock NOT write-              |                      |                                  |                |                                 |                     |  |  |  |

|                       |                                                 | lock write-prote             |                      |                                  |                |                                 |                     |  |  |  |

|                       |                                                 | ble if $\overline{BBEN} = 0$ |                      |                                  |                |                                 |                     |  |  |  |

| bit 7                 |                                                 | pplication Block             |                      | on bit                           |                |                                 |                     |  |  |  |

|                       |                                                 | ation Block NOT              |                      |                                  |                |                                 |                     |  |  |  |

|                       |                                                 | ation Block write            |                      |                                  |                |                                 |                     |  |  |  |

| bit 6-5               | Unimpleme                                       | nted: Read as '              | 1'                   |                                  |                |                                 |                     |  |  |  |

| bit 4                 | SAFEN: SAF                                      | Enable bit                   |                      |                                  |                |                                 |                     |  |  |  |

|                       | 1 = SAF dis                                     | sabled                       |                      |                                  |                |                                 |                     |  |  |  |

|                       | 0 = SAF en                                      | abled                        |                      |                                  |                |                                 |                     |  |  |  |

| bit 3                 | BBEN: Boot                                      | Block Enable b               | it                   |                                  |                |                                 |                     |  |  |  |

|                       | 1 = Boot Bl                                     |                              |                      |                                  |                |                                 |                     |  |  |  |

|                       | 0 = Boot Bl                                     | ock enabled                  |                      |                                  |                |                                 |                     |  |  |  |

| bit 2-0               | BBSIZE[2:0]                                     | · Boot Block Size            | Soloction hite       |                                  |                |                                 |                     |  |  |  |

| DIL 2-0               |                                                 |                              |                      |                                  |                |                                 |                     |  |  |  |

| DIL 2-0               | BBSIZE is us                                    | sed only when E              | BBEN = 0             | = 1; after BBEN                  |                |                                 |                     |  |  |  |

**Note 1:** Bits are implemented as sticky bits. Once protection is enabled, it can only be reset through a Bulk Erase.

# 8.15 Register Definitions: Power Control

#### REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:          |                                                                                                                                                                                                                                                                                                                      |                                                                             |                                                                         |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|

| HC = Bit is clo  | eared by hardv                                                                                                                                                                                                                                                                                                       | vare                                                                        | HS = Bit is set by hardware                                             |  |  |  |  |  |

| R = Readable     | e bit                                                                                                                                                                                                                                                                                                                | W = Writable bit                                                            | U = Unimplemented bit, read as '0'                                      |  |  |  |  |  |

| u = Bit is uncl  | hanged                                                                                                                                                                                                                                                                                                               | x = Bit is unknown                                                          | -m/n = Value at POR/Value at all other Resets                           |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                      | '0' = Bit is cleared                                                        | q = Value depends on condition                                          |  |  |  |  |  |

| bit 7            | 1 = A Stack                                                                                                                                                                                                                                                                                                          | tack Overflow Flag bit<br>Overflow occurred<br>Overflow has not occurre     | ed or cleared by firmware                                               |  |  |  |  |  |

| bit 6            | 1 = A Stack                                                                                                                                                                                                                                                                                                          | tack Underflow Flag bit<br>Underflow occurred<br>Underflow has not occurr   | red or cleared by firmware                                              |  |  |  |  |  |

| bit 5            | <ul> <li>WDTWV: WDT Window Violation Flag bit</li> <li>1 = A WDT Window Violation Reset has not occurred or set to '1' by firmware</li> <li>0 = A WDT Window Violation Reset has occurred (a CLRWDT instruction was executed either without arming the window or outside the window (cleared by hardware)</li> </ul> |                                                                             |                                                                         |  |  |  |  |  |

| bit 4            | 1 = A Watch                                                                                                                                                                                                                                                                                                          |                                                                             | it<br>occurred or set to '1' by firmware<br>urred (cleared by hardware) |  |  |  |  |  |

| bit 3            | 1 = A MCLR                                                                                                                                                                                                                                                                                                           | CLR Reset Flag bit<br>Reset has not occurred of<br>Reset has occurred (clea |                                                                         |  |  |  |  |  |

| bit 2            | 1 = A RESET                                                                                                                                                                                                                                                                                                          |                                                                             | executed or set to '1' by firmware<br>ecuted (cleared by hardware)      |  |  |  |  |  |

| bit 1            | 1 = No Pow                                                                                                                                                                                                                                                                                                           | r-on Reset Status bit<br>er-on Reset occurred<br>r-on Reset occurred (must  | t be set in software after a Power-on Reset occurs)                     |  |  |  |  |  |

| bit 0            | 1 = No Brow                                                                                                                                                                                                                                                                                                          | •                                                                           | t be set in software after a Power-on Reset or Brown-out Reset          |  |  |  |  |  |

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|---------|--------|--------|--------|--------|-----------|-----------------------|-----------------------|-----------------------|---------------------|

| INTCON  | GIE    | PEIE   | _      | _      | _         | —                     | _                     | INTEDG                | 146                 |

| PIE0    | —      |        | TMR0IE | IOCIE  | —         | _                     |                       | INTE                  | 147                 |

| PIE1    | OSFIE  | CSWIE  | _      |        | —         | —                     |                       | ADIE                  | 148                 |

| PIE2    | _      | ZCDIE  | _      | _      | _         | _                     | C2IE                  | C1IE                  | 149                 |

| PIE3    | RC2IE  | TX2IE  | RC1IE  | TX1IE  | BCL2IE    | SSP2IE                | BCL1IE                | SSP1IE                | 150                 |

| PIE4    | —      | _      | _      | —      | —         | —                     | TMR2IE                | TMR1IE                | 151                 |

| PIR0    | —      | _      | TMR0IF | IOCIF  | —         | —                     |                       | INTF                  | 155                 |

| PIR1    | OSFIF  | CSWIF  | _      |        | _         | _                     | _                     | ADIF                  | 156                 |

| PIR2    | —      | ZCDIF  |        | _      | —         | —                     | C2IF                  | C1IF                  | 157                 |

| PIR3    | RC2IF  | TX2IF  | RC1IF  | TX1IF  | BCL2IF    | SSP2IF                | BCL1IF                | SSP1IF                | 158                 |

| PIR4    | _      |        | _      | _      | —         | _                     | TMR2IF                | TMR1IF                | 159                 |

| IOCAP   | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3    | IOCAP2                | IOCAP1                | IOCAP0                | 255                 |

| IOCAN   | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3    | IOCAN2                | IOCAN1                | IOCAN0                | 255                 |

| IOCAF   | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3    | IOCAF2                | IOCAF1                | IOCAF0                | 256                 |

| IOCBP   | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3    | IOCBP2                | IOCBP1                | IOCBP0                | 257                 |

| IOCBN   | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3    | IOCBN2                | IOCBN1                | IOCBN0                | 257                 |

| IOCBF   | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3    | IOCBF2                | IOCBF1                | IOCBF0                | 258                 |

| IOCCP   | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3    | IOCCP2                | IOCCP1                | IOCCP0                | 259                 |

| IOCCN   | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3    | IOCCN2                | IOCCN1                | IOCCN0                | 259                 |

| IOCCF   | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3    | IOCCF2                | IOCCF1                | IOCCF0                | 259                 |

| IOCEP   | —      |        |        | _      | IOCEP3    | IOCEP2 <sup>(1)</sup> | IOCEP1 <sup>(1)</sup> | IOCEP0 <sup>(1)</sup> | 260                 |

| IOCEN   | —      | _      | _      | —      | IOCEN3    | IOCEN2 <sup>(1)</sup> | IOCEN1 <sup>(1)</sup> | IOCEN0 <sup>(1)</sup> | 260                 |

| IOCEF   | —      |        |        | _      | IOCEF3    | IOCEF2 <sup>(1)</sup> | IOCEF1 <sup>(1)</sup> | IOCEF0 <sup>(1)</sup> | 261                 |

| STATUS  | _      | _      | _      | TO     | PD        | Z                     | DC                    | С                     | 54                  |

| VREGCON | _      | _      | _      | _      | _         | —                     | VREGPM                | _                     | 168                 |

| CPUDOZE | IDLEN  | DOZEN  | ROI    | DOE    | _         |                       | DOZE<2:0>             |                       | 169                 |

| WDTCON0 | —      | —      |        | ١      | NDTPS<4:0 | >                     |                       | SWDTEN                | 175                 |

### TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

**Note 1:** Present only in PIC16(L)F15375/76/85/86.

#### 14.12 PORTF Registers

Note: Present only on PIC16(L)F15385/86.

#### 14.12.1 DATA REGISTER

PORTF is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISF (Register 14-42). Setting a TRISF bit (= 1) will make the corresponding PORTF pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISF bit (= 0) will make the corresponding PORTF pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize an I/O port.

Reading the PORTF register (Register 14-41) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATF).

The PORT data latch LATF (Register 14-43) holds the output port data, and contains the latest value of a LATF or PORTF write.

#### 14.12.2 DIRECTION CONTROL

The TRISF register (Register 14-42) controls the PORTF pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISF register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.12.3 INPUT THRESHOLD CONTROL

The INLVLF register (Register 14-48) controls the input voltage threshold for each of the available PORTF input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTF register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 14.12.4 OPEN-DRAIN CONTROL

The ODCONF register (Register 14-46) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONF bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONF bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

#### 14.12.5 SLEW RATE CONTROL

The SLRCONF register (Register 14-47) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONF bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONF bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.12.6 ANALOG CONTROL

The ANSELF register (Register 14-44) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELF bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELF bits has no effect on digital output functions. A pin with TRIS clear and ANSELF set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELF bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 14.12.7 WEAK PULL-UP CONTROL

The WPUF register (Register 14-45) controls the individual weak pull-ups for each port pin.

#### 14.12.8 PORTF FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

|                      |                        | Default     | 5                            | Rem               | nappable to | Pins of PC | RTx   |  |

|----------------------|------------------------|-------------|------------------------------|-------------------|-------------|------------|-------|--|

| INPUT SIGNAL<br>NAME | Input Register<br>Name | Location at | Reset Value<br>(xxxPPS<4:0>) | PIC16(L)F15375/76 |             |            |       |  |

|                      | ituito                 | POR         |                              | PORTA             | PORTB       | PORTC      | PORTD |  |

| INT                  | INTPPS                 | RB0         | 01000                        | ٠                 | •           |            |       |  |

| TOCKI                | T0CKIPPS               | RA4         | 00100                        | ٠                 | •           |            |       |  |

| T1CKI                | T1CKIPSS               | RC0         | 10000                        | ٠                 |             | •          |       |  |

| T1G                  | T1GPPS                 | RB5         | 01101                        |                   | •           | •          |       |  |

| T2IN                 | T2INPPS                | RC3         | 10011                        | ٠                 |             | •          |       |  |

| CCP1                 | CCP1PPS                | RC2         | 10010                        |                   | •           | •          |       |  |

| CCP2                 | CCP2PPS                | RC1         | 10001                        |                   | •           | •          |       |  |

| CWG1IN               | CWG1INPPS              | RB0         | 01000                        |                   | •           |            | •     |  |

| CLCIN0               | CLCIN0PPS              | RA0         | 00000                        | ٠                 |             | •          |       |  |

| CLCIN1               | CLCIN1PPS              | RA1         | 00001                        | ٠                 |             | •          |       |  |

| CLCIN2               | CLCIN2PPS              | RB6         | 01110                        |                   | •           |            | •     |  |

| CLCIN3               | CLCIN3PPS              | RB7         | 01111                        |                   | •           |            | •     |  |

| ADACT                | ADACTPPS               | RB4         | 01100                        |                   | •           |            | •     |  |

| SCK1/SCL1            | SSP1CLKPPS             | RC3         | 10011                        |                   | •           | •          |       |  |

| SDI1/SDA1            | SSP1DATPPS             | RC4         | 10100                        |                   | •           | •          |       |  |

| SS1                  | SSP1SS1PPS             | RA5         | 00101                        | ٠                 |             |            | •     |  |

| SCK2/SCL2            | SSP2CLKPPS             | RB1         | 01001                        |                   | •           |            | •     |  |

| SDI2/SDA2            | SSP2DATPPS             | RB2         | 01010                        |                   | •           |            | •     |  |

| SS2                  | SSP2SSPPS              | RB0         | 01000                        |                   | •           |            | •     |  |

| RX1/DT1              | RX1PPS                 | RC7         | 10111                        |                   | •           | •          |       |  |

| CK1                  | TX1PPS                 | RC6         | 10110                        |                   | •           | •          |       |  |

| RX2/DT2              | RX2PPS                 | RB7         | 01111                        |                   | •           |            | •     |  |

| CK2                  | TX2PPS                 | RB6         | 01110                        |                   | •           |            | •     |  |

#### TABLE 15-2: PPS INPUT SIGNAL ROUTING OPTIONS (PIC16(L)F15375/76)

| REGISTER                                                             | 16-2: PMD                                                                                        | 1: PMD CON                                                               | TROL REGI | STER 1         |                |                  |              |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------|----------------|----------------|------------------|--------------|

| R/W-0/0                                                              | U-0                                                                                              | U-0                                                                      | U-0       | U-0            | R/W-0/0        | R/W-0/0          | R/W-0/0      |

| NCO1MD                                                               |                                                                                                  |                                                                          | _         | —              | TMR2MD         | TMR1MD           | TMR0MD       |

| bit 7                                                                |                                                                                                  |                                                                          |           |                |                |                  | bit 0        |

| r                                                                    |                                                                                                  |                                                                          |           |                |                |                  |              |

| Legend:                                                              |                                                                                                  |                                                                          |           |                |                |                  |              |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                  |                                                                          |           |                |                |                  |              |

| u = Bit is un                                                        | changed                                                                                          | x = Bit is unkr                                                          | nown      | -n/n = Value a | t POR and BO   | R/Value at all c | other Resets |

| '1' = Bit is se                                                      | et                                                                                               | '0' = Bit is cle                                                         | ared      | q = Value dep  | ends on condit | ion              |              |

| bit 7<br>bit 6-3                                                     | 1 = NCO1 m<br>0 = NCO1 m                                                                         | isable Numerica<br>iodule disabled<br>iodule enabled<br>inted: Read as ' |           | scillator bit  |                |                  |              |

| bit 2                                                                | 1 = Timer2 n                                                                                     | sable Timer TM<br>nodule disablec<br>nodule enabled                      | 1         |                |                |                  |              |

| bit 1                                                                | <b>TMR1MD:</b> Disable Timer TMR1 bit<br>1 = Timer1 module disabled<br>0 = Timer1 module enabled |                                                                          |           |                |                |                  |              |

| bit 0                                                                | 1 = Timer0 n                                                                                     | sable Timer TM<br>nodule disableo<br>nodule enabled                      | 1         |                |                |                  |              |

#### REGISTER 17-12: IOCEF: INTERRUPT-ON-CHANGE PORTE FLAG REGISTER

| U-0                                     | U-0   | U-0             | U-0  | R/W/HS-0/0                                            | R/W/HS-0/0                         | R/W/HS-0/0            | R/W/HS-0/0            |  |  |

|-----------------------------------------|-------|-----------------|------|-------------------------------------------------------|------------------------------------|-----------------------|-----------------------|--|--|

| —                                       | _     | —               | _    | IOCEF3                                                | IOCEF2 <sup>(1)</sup>              | IOCEF1 <sup>(1)</sup> | IOCEF0 <sup>(1)</sup> |  |  |

| bit 7 bit 0                             |       |                 |      |                                                       |                                    |                       |                       |  |  |

|                                         |       |                 |      |                                                       |                                    |                       |                       |  |  |

| Legend:                                 |       |                 |      |                                                       |                                    |                       |                       |  |  |

| R = Readable bit W = Writable bit U = U |       |                 |      | U = Unimplen                                          | U = Unimplemented bit, read as '0' |                       |                       |  |  |

| u = Bit is uncha                        | anged | x = Bit is unkn | iown | -n/n = Value at POR and BOR/Value at all other Resets |                                    |                       |                       |  |  |

'1' = Bit is set

bit 3

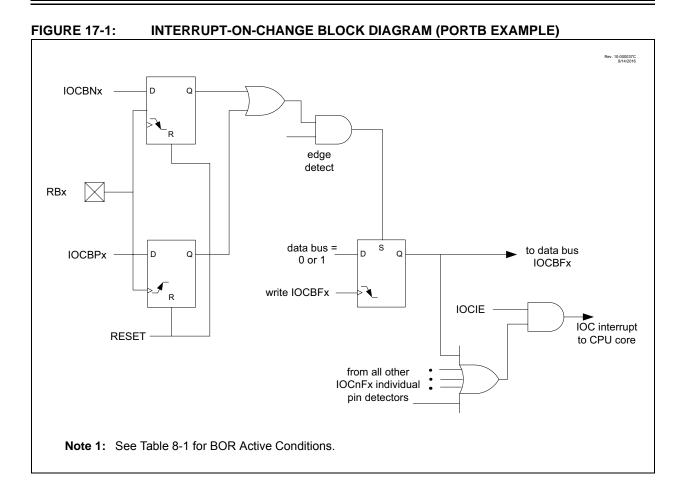

IOCEF<3:0>: Interrupt-on-Change PORTE Flag bit

'0' = Bit is cleared

1 = An enabled change was detected on the associated pin

Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.

HS - Bit is set in hardware

0 = No change was detected, or the user cleared the detected change

Note 1: Present only on PIC16(L)F15375/76/85/86.

© 2016 Microchip Technology Inc.

| Name     | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1 | Bit 0   | Register<br>on page |

|----------|--------|-------|---------|---------|--------|---------|-------|---------|---------------------|

| DAC1CON0 | DAC1EN | _     | DAC10E1 | DAC10E2 | DAC1PS | SS<1:0> | _     | DAC1NSS | 287                 |

| DAC1CON1 | —      | _     | —       |         | 287    |         |       |         |                     |

| CM1PSEL  | _      | _     | _       | _       | _      | 307     |       |         |                     |

| CM2PSEL  | _      | _     | _       |         |        | 307     |       |         |                     |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

#### 27.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

#### 28.3.4 TIMER2 TIMER RESOURCE

This device has a newer version of the Timer2 module that has many new modes, which allow for greater customization and control of the PWM signals than on older parts. Refer to **Section 27.5** "**Operation Examples**" for examples of PWM signal generation using the different modes of Timer2. The CCP operation requires that the timer used as the PWM time base has the FOSC/4 clock source selected

#### 28.3.5 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 28-1.

#### EQUATION 28-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

| Note: | The Timer postscaler (see Section 27.4 |

|-------|----------------------------------------|

|       | "Timer2 Interrupt") is not used in the |

|       | determination of the PWM frequency.    |

#### 28.3.6 PWM DUTY CYCLE

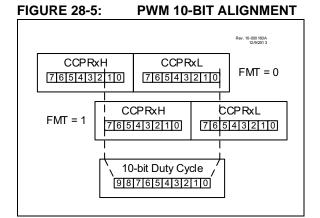

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the CCPRxFMT bit of the CCPxCON register (see Figure 28-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between PR2 and TMR2.

Equation 28-2 is used to calculate the PWM pulse width.

Equation 28-3 is used to calculate the PWM duty cycle ratio.

### EQUATION 28-2: PULSE WIDTH