#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15375-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

© 2016 Microchip Technology Inc.

|                       |                                                                                  | R/W-1                                                                                       | U-1                  | R/W-1                            | U-1            | R/W-1                           | R/W-1               |  |  |

|-----------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|----------------------------------|----------------|---------------------------------|---------------------|--|--|

|                       |                                                                                  | LVP                                                                                         | —                    | WRTSAF <sup>(1)</sup>            | —              | WRTC <sup>(1)</sup>             | WRTB <sup>(1)</sup> |  |  |

|                       |                                                                                  | bit 13                                                                                      | 12                   | 11                               | 10             | 9                               | bit 8               |  |  |

| R/W-1                 | U-1                                                                              | U-1                                                                                         | R/W-1                | R/W-1                            | R/W-1          | R/W-1                           | R/W-1               |  |  |

| WRTAPP <sup>(1)</sup> | 0-1                                                                              | 0-1                                                                                         | SAFEN <sup>(1)</sup> | BBEN <sup>(1)</sup>              | BBSIZE2        | BBSIZE1                         |                     |  |  |

|                       |                                                                                  |                                                                                             |                      |                                  |                | _                               | BBSIZE0             |  |  |

| bit 7                 | 6                                                                                | 5                                                                                           | 4                    | 3                                | 2              | 1                               | bit                 |  |  |

| Legend:               |                                                                                  |                                                                                             |                      |                                  |                |                                 |                     |  |  |

| R = Readable          | e bit                                                                            | P = Programı                                                                                | nable bit            | x = Bit is unkn                  | own            | U = Unimplem<br>read as '1'     | nented bit,         |  |  |

| '0' = Bit is clea     | ared                                                                             | '1' = Bit is set                                                                            |                      | W = Writable t                   | bit            | n = Value whe<br>after Bulk Era |                     |  |  |

| bit 13                |                                                                                  | oltage Programr                                                                             | ning Enable bit      |                                  |                |                                 |                     |  |  |

|                       |                                                                                  |                                                                                             |                      | ICLR/VPP pin fu                  | nction is MCL  | R. MCLRE Cont                   | iguration bit i     |  |  |

|                       | ignored                                                                          |                                                                                             | 4 h a a a d fa a a   |                                  |                |                                 |                     |  |  |

|                       |                                                                                  | MCLR/VPP mus                                                                                |                      | rogramming.<br>le operating fror | n tha LVD ara  | aromming intorf                 | ann Tha             |  |  |

|                       |                                                                                  |                                                                                             |                      | om dropping out                  |                |                                 |                     |  |  |

|                       |                                                                                  |                                                                                             |                      | e from the config                |                |                                 |                     |  |  |

|                       |                                                                                  | litioned (erased)                                                                           | •                    |                                  | garation state |                                 |                     |  |  |

| bit 12                | -                                                                                |                                                                                             |                      |                                  |                |                                 |                     |  |  |

| bit 11                | Unimplemented: Read as '1'<br>WRTSAF: Storage Area Flash Write Protection bit    |                                                                                             |                      |                                  |                |                                 |                     |  |  |

|                       |                                                                                  | DT write-protect                                                                            |                      |                                  |                |                                 |                     |  |  |

|                       |                                                                                  | ite-protected                                                                               | cu                   |                                  |                |                                 |                     |  |  |

|                       |                                                                                  |                                                                                             | ot supported in      | the device famil                 | ly and only ap | plicable if SAFE                | <b>N</b> = 0.       |  |  |

| bit 10                |                                                                                  | nted: Read as '                                                                             |                      |                                  |                |                                 |                     |  |  |

| bit 9                 |                                                                                  | figuration Regis                                                                            |                      | ction bit                        |                |                                 |                     |  |  |

|                       |                                                                                  | uration Register                                                                            |                      |                                  |                |                                 |                     |  |  |

|                       |                                                                                  | uration Register                                                                            |                      |                                  |                |                                 |                     |  |  |

| bit 8                 | Ŭ                                                                                | t Block Write Pr                                                                            | •                    |                                  |                |                                 |                     |  |  |

|                       |                                                                                  | lock NOT write-                                                                             |                      |                                  |                |                                 |                     |  |  |

|                       |                                                                                  | lock write-prote                                                                            |                      |                                  |                |                                 |                     |  |  |

|                       |                                                                                  | ble if $\overline{BBEN} = 0$                                                                |                      |                                  |                |                                 |                     |  |  |

| bit 7                 |                                                                                  |                                                                                             |                      | on bit                           |                |                                 |                     |  |  |

|                       |                                                                                  | WRTAPP: Application Block Write Protection bit<br>1 = Application Block NOT write-protected |                      |                                  |                |                                 |                     |  |  |

|                       |                                                                                  | ation Block write                                                                           |                      |                                  |                |                                 |                     |  |  |

| bit 6-5               | Unimpleme                                                                        | nted: Read as '                                                                             | 1'                   |                                  |                |                                 |                     |  |  |

| bit 4                 | SAFEN: SAF Enable bit                                                            |                                                                                             |                      |                                  |                |                                 |                     |  |  |

|                       | 1 = SAF dis                                                                      | sabled                                                                                      |                      |                                  |                |                                 |                     |  |  |

|                       | 0 = SAF en                                                                       | abled                                                                                       |                      |                                  |                |                                 |                     |  |  |

| bit 3                 | BBEN: Boot                                                                       | Block Enable b                                                                              | it                   |                                  |                |                                 |                     |  |  |

|                       | 1 = Boot Bl                                                                      |                                                                                             |                      |                                  |                |                                 |                     |  |  |

|                       | 0 = Boot Bl                                                                      | ock enabled                                                                                 |                      |                                  |                |                                 |                     |  |  |

| bit 2-0               | BBSIZE[2:0]                                                                      | · Boot Block Size                                                                           | Soloction hite       |                                  |                |                                 |                     |  |  |

| DIL 2-0               | BBSIZE[2:0]: Boot Block Size Selection bits<br>BBSIZE is used only when BBEN = 0 |                                                                                             |                      |                                  |                |                                 |                     |  |  |

| DIL 2-0               | BBSIZE is us                                                                     | sed only when E                                                                             | BBEN = 0             | = 1; after BBEN                  |                |                                 |                     |  |  |

**Note 1:** Bits are implemented as sticky bits. Once protection is enabled, it can only be reset through a Bulk Erase.

## 9.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

## 9.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 9-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 determine the type of oscillator that will be used when the device reset, including when it is first powered up.

The internal clock modes, LFINTOSC, HFINTOSC (set at 1 MHz), or HFINTOSC (set at 32 MHz) can be set through the RSTOSC bits.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used to select the external clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode ECL<= 500 kHz

- 2. ECM External Clock Medium Power mode ECM <= 8 MHz

- 3. ECH External Clock High-Power mode ECH <= 32 MHz

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 4 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The INTOSC internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 9-1). A wide selection of device clock frequencies may be derived from these clock sources.

| R/W-0/0                                                                                                                                                           | R/W-0/0                                                      | R/W-0/0                                                         | R/W-0/0   | U-0         | U-0              | U-0              | R/W-0/0      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|-----------|-------------|------------------|------------------|--------------|

| CLC4IE                                                                                                                                                            | CLC3IE                                                       | CLC2IE                                                          | CLC1IE    | —           | —                | —                | TMR1GIE      |

| bit 7                                                                                                                                                             |                                                              |                                                                 |           |             |                  |                  | bit 0        |

|                                                                                                                                                                   |                                                              |                                                                 |           |             |                  |                  |              |

| Legend:                                                                                                                                                           |                                                              |                                                                 |           |             |                  |                  |              |

| R = Readab                                                                                                                                                        |                                                              | W = Writable                                                    |           | •           | mented bit, read |                  |              |

| u = Bit is un                                                                                                                                                     | 0                                                            | x = Bit is unkr                                                 |           |             | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se                                                                                                                                                   | et                                                           | '0' = Bit is cle                                                | ared      | HS = Hardwa | are set          |                  |              |

| bit 7                                                                                                                                                             | 1 = CLC4 i                                                   | C4 Interrupt Ena<br>nterrupt enabled<br>nterrupt disable        | t         |             |                  |                  |              |

| bit 6                                                                                                                                                             | 1 = CLC3 i                                                   | C3 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable        | b         |             |                  |                  |              |

| bit 5                                                                                                                                                             | 1 = CLC2 i                                                   | C2 Interrupt Ena<br>nterrupt enabled<br>nterrupt disable        | t         |             |                  |                  |              |

| bit 4                                                                                                                                                             | 1 = CLC1 i                                                   | CLC1IE: CLC1 Interrupt Enable bit<br>1 = CLC1 interrupt enabled |           |             |                  |                  |              |

| bit 3-1                                                                                                                                                           | Unimpleme                                                    | nted: Read as '                                                 | 0'        |             |                  |                  |              |

| bit 0 <b>TMR1GIE:</b> Timer1 Gate Interrupt Enable bit<br>1 = Enables the Timer1 gate acquisition interrupt<br>0 = Disables the Timer1 gate acquisition interrupt |                                                              |                                                                 |           |             |                  |                  |              |

| s                                                                                                                                                                 | Bit PEIE of the IN<br>set to enable a<br>controlled by regis | any peripheral                                                  | interrupt |             |                  |                  |              |

## REGISTER 10-7: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

## REGISTER 10-16: PIR6: PERIPHERAL INTERRUPT REQUEST REGISTER 6

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| —     | —   | -   | -   | -   | —   | CCP2IF     | CCP1IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

|       |     |     |     |     |     |            |            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

#### bit 7-2 Unimplemented: Read as '0'

bit 1

## CCP2IF: CCP2 Interrupt Flag bit

| Value | CCPM Mode                                         |                                                      |                                                                |  |  |  |  |

|-------|---------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| value | Capture                                           | Compare                                              | PWM                                                            |  |  |  |  |

| 1     | Capture occurred<br>(must be cleared in software) | Compare match occurred (must be cleared in software) | Output trailing edge occurred<br>(must be cleared in software) |  |  |  |  |

| 0     | Capture did not occur                             | Compare match did not occur                          | Output trailing edge did not occur                             |  |  |  |  |

#### bit 0 CCP1IF: CCP1 Interrupt Flag bit

| Value |                                                   | CCPM Mode                                               |                                                                |

|-------|---------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------|

| value | Capture                                           | Compare                                                 | PWM                                                            |

| 1     | Capture occurred<br>(must be cleared in software) | Compare match occurred<br>(must be cleared in software) | Output trailing edge occurred<br>(must be cleared in software) |

| 0     | Capture did not occur                             | Compare match did not occur                             | Output trailing edge did not occur                             |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

© 2016 Microchip Technology Inc.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTF   | RF7     | RF6     | RF5     | RF4     | RF3     | RF2     | RF1     | RF0     | 216                 |

| TRISF   | TRISF7  | TRISF6  | TRISF5  | TRISF4  | TRISF3  | TRISF2  | TRISF1  | TRISF0  | 216                 |

| LATF    | LATF7   | LATF6   | LATF5   | LATF4   | LATF3   | LATF2   | LATF1   | LATF0   | 216                 |

| ANSELF  | ANSF7   | ANSF6   | ANSF5   | ANSF4   | ANSF3   | ANSF2   | ANSF1   | ANSF0   | 217                 |

| WPUF    | WPUF7   | WPUF6   | WPUF5   | WPUF4   | WPUF3   | WPUF2   | WPUF1   | WPUF0   | 217                 |

| ODCONF  | ODCF7   | ODCF6   | ODCF5   | ODCF4   | ODCF3   | ODCF2   | ODCF1   | ODCF0   | 218                 |

| SLRCONF | SLRF7   | SLRF6   | SLRF5   | SLRF4   | SLRF3   | SLRF2   | SLRF1   | SLRF0   | 218                 |

| INLVLF  | INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4 | INLVLF3 | INLVLF2 | INLVLF1 | INLVLF0 | 218                 |

## TABLE 14-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

Legend: - = unimplemented locations read as '0'. Shaded cells are not used by PORTF.

## 15.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- The I<sup>2</sup>C SCLx and SDAx functions can be Note: remapped through PPS. However, only the RB1, RB2, RC3 and RC4 pins have the I<sup>2</sup>C and SMBus specific input buffers implemented (I<sup>2</sup>C mode disables INLVL and sets thresholds that are specific for  $I^2C$ ). If the SCLx or SDAx functions are mapped to some other pin (other than RB1, RB2, RC3 or RC4), the general purpose TTL or ST input buffers (as configured based on INLVL register setting) will be used instead. In most applications, it is therefore recommended only to map the SCLx and SDAx pin functions to the RB1, RB2, RC3 or RC4 pins.

## 15.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 15-1.

#### EXAMPLE 15-1: PPS LOCK/UNLOCK SEQUENCE

| ; | suspend interrupts                     |

|---|----------------------------------------|

|   | BCF INTCON, GIE                        |

| ; | BANKSEL PPSLOCK ; set bank             |

| ; | required sequence, next 5 instructions |

|   | MOVLW 0x55                             |

|   | MOVWF PPSLOCK                          |

|   | MOVLW 0xAA                             |

|   | MOVWF PPSLOCK                          |

| ; | Set PPSLOCKED bit to disable writes or |

| ; | Clear PPSLOCKED bit to enable writes   |

|   | BSF PPSLOCK, PPSLOCKED                 |

| ; | restore interrupts                     |

|   | BSF INTCON, GIE                        |

## 15.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

## 15.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

## 15.7 Effects of a Reset

A device Power-on-Reset (POR) clears all PPS input and output selections to their default values (Permanent Lock Removed). All other Resets leave the selections unchanged. Default input selections are shown in Table 15-1 through Table 15-3.

| U-0                                                                  | U-0                                 | R/W/HS-0/0 | R/W/HS-0/0                                            | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0            | R/W/HS-0/0            |

|----------------------------------------------------------------------|-------------------------------------|------------|-------------------------------------------------------|------------|------------|-----------------------|-----------------------|

| _                                                                    | —                                   | IOCAF5     | IOCAF4                                                | IOCAF3     | IOCAF2     | IOCAF1 <sup>(1)</sup> | IOCAF0 <sup>(1)</sup> |

| bit 7                                                                | ib                                  |            |                                                       |            |            | bit 0                 |                       |

|                                                                      |                                     |            |                                                       |            |            |                       |                       |

| Legend:                                                              |                                     |            |                                                       |            |            |                       |                       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                     |            |                                                       |            |            |                       |                       |

| u = Bit is unch                                                      | Bit is unchanged x = Bit is unknown |            | -n/n = Value at POR and BOR/Value at all other Resets |            |            |                       |                       |

## REGISTER 17-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

bit 7-6 Unimplemented: read as '0'

'1' = Bit is set

bit 5-0

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

'0' = Bit is cleared

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

HS - Bit is set in hardware

0 = No change was detected, or the user cleared the detected change.

**Note 1:** If the debugger is enabled, these bits are not available for use.

## 20.4 Register Definitions: ADC Control

### REGISTER 20-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0           | R/W-0/0    | R/W-0/0                | R/W-0/0                    | R/W-0/0             | R/W-0/0           | R/W-0/0              | R/W-0/0 |

|-------------------|------------|------------------------|----------------------------|---------------------|-------------------|----------------------|---------|

|                   |            | CHS<                   | 5:0>                       |                     |                   | GO/DONE              | ADON    |

| bit 7             |            |                        |                            |                     |                   |                      | bit (   |

|                   |            |                        |                            |                     |                   |                      |         |

| Legend:           |            |                        |                            |                     |                   |                      |         |

| R = Readable bit  | t          | W = Writable bit       |                            | U = Unimplemer      | nted bit, read as | 0'                   |         |

| u = Bit is unchan | ged        | x = Bit is unknow      | vn                         | -n/n = Value at F   | OR and BOR/Va     | alue at all other Re | sets    |

| '1' = Bit is set  |            | '0' = Bit is cleare    | d                          |                     |                   |                      |         |

|                   |            |                        |                            |                     |                   |                      |         |

| bit 7-2           |            | Analog Channel Selec   |                            |                     |                   |                      |         |

|                   | 111111 =   | FVR Buffer 2 referen   | nce voltage <sup>(2)</sup> |                     |                   |                      |         |

|                   | 111110 =   | FVR 1Buffer 1 refer    | ence voltage               |                     |                   |                      |         |

|                   | 111101 =   | DAC1 output voltage    |                            |                     |                   |                      |         |

|                   | 111100 =   | Temperature sensor     |                            |                     |                   |                      |         |

|                   | 111011 =   | AVss (Analog Grour     | ,                          |                     |                   |                      |         |

|                   | 111010-10  | 0000 = Reserved. No    | channel conne              | cted                |                   |                      |         |

|                   | 101111 =   | RF7                    |                            |                     |                   |                      |         |

|                   | 101110 =   | RF6                    |                            |                     |                   |                      |         |

|                   | 101101 =   | RF5                    |                            |                     |                   |                      |         |

|                   | 101100 =   | RF4                    |                            |                     |                   |                      |         |

|                   | 101011 =   | RF3                    |                            |                     |                   |                      |         |

|                   | 101010 =   | RF2                    |                            |                     |                   |                      |         |

|                   | 101001 =   | RF1                    |                            |                     |                   |                      |         |

|                   | 101000 =   | RF0                    |                            |                     |                   |                      |         |

|                   | 100010 =   | RE2                    |                            |                     |                   |                      |         |

|                   | 100001 =   | RE1                    |                            |                     |                   |                      |         |

|                   | 100000 =   | RE0                    |                            |                     |                   |                      |         |

|                   | 011111 =   | RD7                    |                            |                     |                   |                      |         |

|                   | 011111 =   | RD6                    |                            |                     |                   |                      |         |

|                   |            |                        |                            |                     |                   |                      |         |

|                   | 011101 =   | RD5                    |                            |                     |                   |                      |         |

|                   | 011100 =   | RD4                    |                            |                     |                   |                      |         |

|                   | 011011 =   | RD3                    |                            |                     |                   |                      |         |

|                   | 011010 =   | RD2                    |                            |                     |                   |                      |         |

|                   | 011001 =   | RD1                    |                            |                     |                   |                      |         |

|                   | 011000 =   | RD0                    |                            |                     |                   |                      |         |

|                   | 010111 =   | RC7 <sup>(4)</sup>     |                            |                     |                   |                      |         |

|                   | 010110 =   | RC6 <sup>(4)</sup>     |                            |                     |                   |                      |         |

|                   | 010101 =   | RC5                    |                            |                     |                   |                      |         |

|                   | 010100 =   | RC4                    |                            |                     |                   |                      |         |

|                   | 010011 =   | RC3                    |                            |                     |                   |                      |         |

|                   | 010010 =   | RC2                    |                            |                     |                   |                      |         |

|                   | 010001 =   | RC1                    |                            |                     |                   |                      |         |

|                   | 010000 =   | RC0                    |                            |                     |                   |                      |         |

|                   | 001111 =   | RB7 <sup>(4)</sup>     |                            |                     |                   |                      |         |

|                   | 001110 =   | RB6 <sup>(4)</sup>     |                            |                     |                   |                      |         |

|                   | 001101 =   | RB5 <sup>(4)</sup>     |                            |                     |                   |                      |         |

|                   | 001100 =   | RB4 <sup>(4)</sup>     |                            |                     |                   |                      |         |

|                   |            | 0110 = Reserved        |                            |                     |                   |                      |         |

|                   |            |                        |                            |                     |                   |                      |         |

|                   | 000101 =   | RA5                    |                            |                     |                   |                      |         |

|                   | 000100 =   | RA4                    |                            |                     |                   |                      |         |

|                   | 000011 =   | RA3                    |                            |                     |                   |                      |         |

|                   | 000010 =   | RA2                    |                            |                     |                   |                      |         |

|                   | 000001 =   | RA1                    |                            |                     |                   |                      |         |

|                   | 000000 =   | RA0                    |                            |                     |                   |                      |         |

| bit 1             | GO/DONE: / | ADC Conversion State   | us bit                     |                     |                   |                      |         |

|                   |            | version cycle in prog  |                            | s bit starts an ADC | conversion cycle  |                      |         |

|                   |            | s automatically cleare |                            |                     |                   |                      |         |

|                   |            | version completed/no   |                            |                     |                   |                      |         |

0 = ADC conversion completed/not in progress

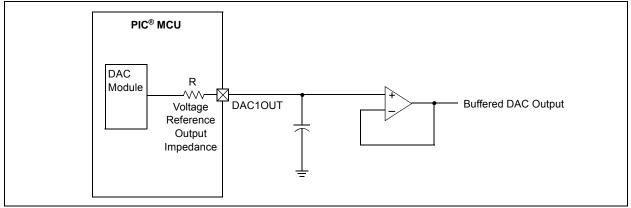

## FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

© 2016 Microchip Technology Inc.

## 26.7 Timer1 Interrupts

The timer register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When the timer rolls over, the respective timer interrupt flag bit of the PIR5 register is set. To enable the interrupt on rollover, you must set these bits:

- ON bit of the T1CON register

- TMR1IE bit of the PIE4 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

| Note: | To avoid immediate interrupt vectoring,     |

|-------|---------------------------------------------|

|       | the TMR1H:TMR1L register pair should        |

|       | be preloaded with a value that is not immi- |

|       | nently about to rollover, and the TMR1IF    |

|       | flag should be cleared prior to enabling    |

|       | the timer interrupts.                       |

## 26.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- ON bit of the T1CON register must be set

- TMR1IE bit of the PIE4 register must be set

- PEIE bit of the INTCON register must be set

- SYNC bit of the T1CON register must be set

- CS bits of the T1CLK register must be configured

- The timer clock source must be enabled and continue operation during sleep. When the SOSC is used for this purpose, the SOSCEN bit of the OSCEN register must be set.

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Secondary oscillator will continue to operate in Sleep regardless of the SYNC bit setting.

## 26.9 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value CCPRxH:CCPRxL register pair matches the value in the TMR1H:TMR1L register pair. This event can be an Auto-conversion Trigger.

For more information, see Section 28.0 "Capture/Compare/PWM Modules".

## 26.10 CCP Auto-Conversion Trigger

When any of the CCP's are configured to trigger an auto-conversion, the trigger will clear the TMR1H:TMR1L register pair. This auto-conversion does not cause a timer interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1.

The timer should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Auto-conversion Trigger. Asynchronous operation of the timer can cause an Auto-conversion Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with an Auto-conversion Trigger from the CCP, the write will take precedence.

For more information, see Section 28.2.4 "Compare During Sleep".

## **30.0 COMPLEMENTARY WAVEFORM** GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces half-bridge, full-bridge, and steering of PWM waveforms. It is backwards compatible with previous ECCP functions.

The CWG has the following features:

- · Six operating modes:

- Synchronous Steering mode

- Asynchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

- Half-Bridge mode

- Push-Pull mode

- Output polarity control

- Output steering

- Synchronized to rising event

- Immediate effect

- Independent 6-bit rising and falling event deadband timers

- Clocked dead band

- Independent rising and falling dead-band enables

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

The CWG modules available are shown in Table 30-1.

### TABLE 30-1: AVAILABLE CWG MODULES

| Device                     | CWG1 |

|----------------------------|------|

| PIC16(L)F15356/75/76/85/86 | •    |

## 30.1 Fundamental Operation

The CWG module can operate in six different modes, as specified by MODE of the CWG1CON0 register:

- Half-Bridge mode (Figure 30-9)

- Push-Pull mode (Figure 30-2)

- Full-Bridge mode, Forward (Figure 30-3)

- Full-Bridge mode, Reverse (Figure 30-3)

- Steering mode (Figure 30-10)

- Synchronous Steering mode (Figure 30-11)

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. Thus, all output modes support auto-shutdown, which is covered in **30.10** "Auto-Shutdown".

#### 30.1.1 HALF-BRIDGE MODE

In Half-Bridge mode, two output signals are generated as true and inverted versions of the input as illustrated in Figure 30-9. A non-overlap (dead-band) time is inserted between the two outputs as described in **Section 30.5 "Dead-Band Control"**.

The unused outputs CWG1C and CWG1D drive similar signals, with polarity independently controlled by the POLC and POLD bits of the CWG1CON1 register, respectively.

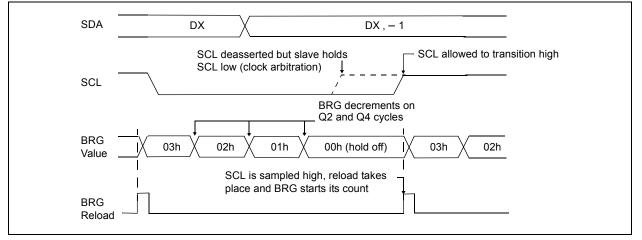

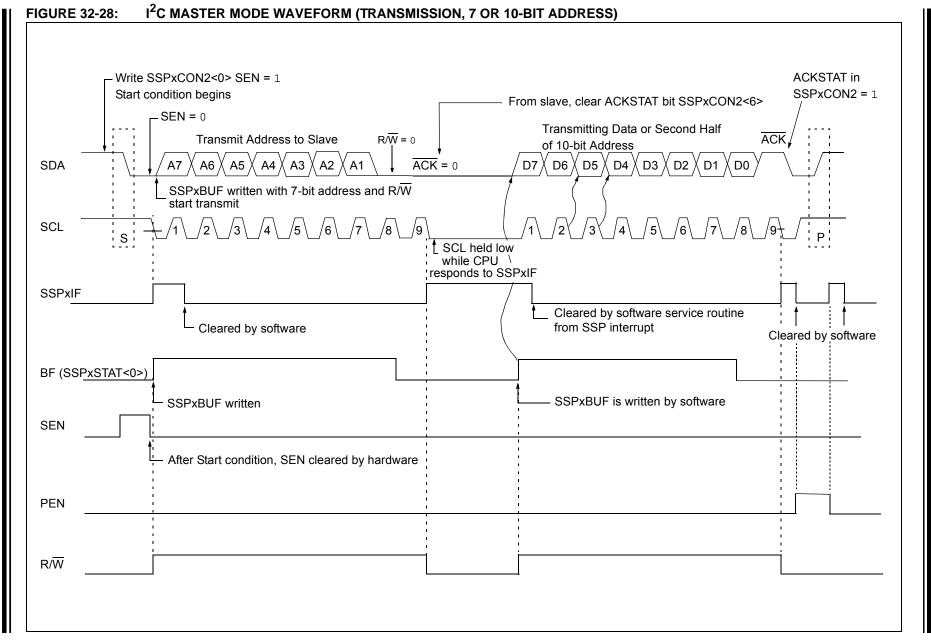

#### 32.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 32-25).

#### FIGURE 32-25: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

#### 32.6.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | writing to the lower five bits of SSPxCON2 |  |  |  |  |  |  |  |

|       | is disabled until the Start condition is   |  |  |  |  |  |  |  |

|       | complete.                                  |  |  |  |  |  |  |  |

|  | REGISTER 32-4: | SSPxCON3: SSPx CONTROL REGISTER 3 |

|--|----------------|-----------------------------------|

|--|----------------|-----------------------------------|

| R-0/0          | R/W-0/0                     | R/W-0/0                                          | R/W-0/0                       | R/W-0/0                         | R/W-0/0                                         | R/W-0/0             | R/W-0/0          |

|----------------|-----------------------------|--------------------------------------------------|-------------------------------|---------------------------------|-------------------------------------------------|---------------------|------------------|

| ACKTIM         | <sup>3)</sup> PCIE          | SCIE                                             | BOEN                          | SDAHT                           | SBCDE                                           | AHEN                | DHEN             |

| bit 7          | <u>.</u>                    |                                                  |                               |                                 | •                                               |                     | bit              |

|                |                             |                                                  |                               |                                 |                                                 |                     |                  |

| Legend:        |                             |                                                  |                               |                                 |                                                 |                     |                  |

| R = Readab     | ole bit                     | W = Writable b                                   | bit                           | U = Unimplem                    | ented bit, read as                              | ʻ0'                 |                  |

| u = Bit is ur  | changed                     | x = Bit is unkn                                  | own                           | -n/n = Value at                 | POR and BOR/V                                   | alue at all other l | Resets           |

| '1' = Bit is s | et                          | '0' = Bit is clea                                | red                           |                                 |                                                 |                     |                  |

|                |                             |                                                  | 0                             | (2)                             |                                                 |                     |                  |

| bit 7          |                             | nowledge Time S                                  |                               |                                 | oth curr                                        |                     |                  |

|                |                             | the I <sup>2</sup> C bus is in a knowledge seque |                               |                                 | on 8 <sup>th</sup> falling edge<br>of SCL clock | of SCL clock        |                  |

| bit 6          |                             | ondition Interrupt                               |                               |                                 |                                                 |                     |                  |

|                |                             | errupt on detection                              |                               |                                 |                                                 |                     |                  |

|                |                             | ction interrupts ar                              |                               |                                 |                                                 |                     |                  |

| bit 5          |                             | ondition Interrupt                               | •                             | • ·                             |                                                 |                     |                  |

|                |                             | errupt on detection ction interrupts ar          |                               | start conditions                |                                                 |                     |                  |

| oit 4          |                             | Overwrite Enabl                                  |                               |                                 |                                                 |                     |                  |

| 511 4          | In SPI Slave n              |                                                  |                               |                                 |                                                 |                     |                  |

|                |                             |                                                  |                               |                                 | shifted in ignoring                             |                     |                  |

|                |                             | •                                                |                               |                                 | egister already se                              | et, SSPOV bit of    | the SSPxCON      |

|                | · · ·                       | ster is set, and the<br>mode and SPI M           | •                             | dated                           |                                                 |                     |                  |

|                | In I <sup>2</sup> C Slave m |                                                  |                               |                                 |                                                 |                     |                  |

|                |                             |                                                  |                               | nerated for a rec               | eived address/da                                | ita byte, ignoring  | the state of th  |

|                |                             | OV bit only if the<br>xBUF is only upda          |                               | )V is clear                     |                                                 |                     |                  |

| oit 3          |                             | Hold Time Selec                                  |                               |                                 |                                                 |                     |                  |

|                |                             | of 300 ns hold tin                               | •                             | • ·                             | of SCL                                          |                     |                  |

|                |                             | of 100 ns hold tin                               |                               |                                 |                                                 |                     |                  |

| oit 2          | SBCDE: Slave                | e Mode Bus Colli                                 | sion Detect Ena               | ble bit (I <sup>2</sup> C Slave | e mode only)                                    |                     |                  |

|                |                             | g edge of SCL, SI<br>is set, and bus go          |                               | w when the moo                  | lule is outputting a                            | a high state, the E | 3CL1IF bit of th |

|                |                             | ave bus collision i collision i                  | •                             |                                 |                                                 |                     |                  |

| oit 1          | AHEN: Addres                | ss Hold Enable b                                 | it (I <sup>2</sup> C Slave mo | de only)                        |                                                 |                     |                  |

|                |                             | the eighth falling will be cleared an            |                               |                                 | eceived address                                 | byte; CKP bit of    | the SSPxCON      |

|                |                             | olding is disabled                               |                               |                                 |                                                 |                     |                  |

| bit 0          |                             | Hold Enable bit (I                               |                               |                                 | 4a budau alawa 1                                |                     |                  |

|                |                             | N1 register and S                                |                               | or a received da                | ta byte; slave ha                               | rdware clears the   | e CKP bit of tr  |

| Note 1:        | For daisy-chained S         | SPI operation; allo                              | ws the user to ic             | nore all but the                | ast received byte                               | . SSPOV is still s  | et when a new    |

|                | byte is received and        |                                                  |                               |                                 |                                                 |                     |                  |

| 2:             | This bit has no effect      | ct in Slave modes                                | s that Start and S            | Stop condition de               | tection is explicit                             | y listed as enable  | ed.              |

- 2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

- 3: The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

## REGISTER 32-7: SSPxBUF: MSSPx BUFFER REGISTER

| R/W-x   | R/W-x | R/W-x | R/W-x  | R/W-x   | R/W-x | R/W-x | R/W-x |

|---------|-------|-------|--------|---------|-------|-------|-------|

|         |       |       | SSPxBl | JF<7:0> |       |       |       |

| bit 7   |       |       |        |         |       |       | bit 0 |

|         |       |       |        |         |       |       |       |

| Legend: |       |       |        |         |       |       |       |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SSPxBUF<7:0>: MSSP Buffer bits

#### TABLE 32-3: SUMMARY OF REGISTERS ASSOCIATED WITH MSSPx

| Name       | Bit 7       | Bit 6            | Bit 5 | Bit 4           | Bit 3     | Bit 2    | Bit 1 | Bit 0  | Register<br>on Page |  |

|------------|-------------|------------------|-------|-----------------|-----------|----------|-------|--------|---------------------|--|

| INTCON     | GIE         | PEIE             | _     | —               | _         | —        |       | INTEDG | 146                 |  |

| PIR1       | OSFIF       | CSWIF            | -     | —               | -         | —        | -     | ADIF   | 156                 |  |

| PIE1       | OSFIE       | CSWIE            | _     | —               | _         | —        | -     | ADIE   | 148                 |  |

| SSP1STAT   | SMP         | CKE              | D/A   | Р               | S         | R/W      | UA    | BF     | 465                 |  |

| SSP1CON1   | WCOL        | SSPOV            | SSPEN | CKP             |           | SSPM     | <3:0> |        | 466                 |  |

| SSP1CON2   | GCEN        | ACKSTAT          | ACKDT | ACKEN           | RCEN      | PEN      | RSEN  | SEN    | 467                 |  |

| SSP1CON3   | ACKTIM      | PCIE             | SCIE  | BOEN            | SDAHT     | SBCDE    | AHEN  | DHEN   | 465                 |  |

| SSP1MSK    | SSPMSK<7:0> |                  |       |                 |           |          |       |        | 469                 |  |

| SSP1ADD    | SSPADD<7:0> |                  |       |                 |           |          |       |        | 469                 |  |

| SSP1BUF    |             |                  |       | SSPBUF<7:0>     |           |          |       |        |                     |  |

| SSP2STAT   | SMP         | CKE              | D/A   | Р               | S         | R/W      | UA    | BF     | 465                 |  |

| SSP2CON1   | WCOL        | SSPOV            | SSPEN | CKP             | SSPM<3:0> |          |       |        | 466                 |  |

| SSP2CON2   | GCEN        | ACKSTAT          | ACKDT | ACKEN           | RCEN      | PEN      | RSEN  | SEN    | 467                 |  |

| SSP2CON3   | ACKTIM      | PCIE             | SCIE  | BOEN            | SDAHT     | SBCDE    | AHEN  | DHEN   | 465                 |  |

| SSP2MSK    |             |                  |       | SSPMS           | K<7:0>    |          |       |        | 469                 |  |

| SSP2ADD    |             |                  |       | SSPAD           | D<7:0>    |          |       |        | 469                 |  |

| SSP2BUF    |             |                  |       | SSPBU           | F<7:0>    |          |       |        | 470                 |  |

| SSP1CLKPPS | -           | —                |       | SSP1CLKPPS<5:0> |           |          |       |        |                     |  |

| SSP1DATPPS | _           | _                |       | SSP1DATPPS<5:0> |           |          |       |        |                     |  |

| SSP1SSPPS  | _           | — SSP1SSPPS<5:0> |       |                 |           |          |       |        | 241                 |  |

| SSP2CLKPPS |             | SSP2CLKPPS<5:0>  |       |                 |           |          |       |        | 241                 |  |

| SSP2DATPPS |             | _                |       |                 | SSP2DATE  | PPS<5:0> |       |        | 241                 |  |

| SSP2SSPPS  | _           | —                |       | 1               | SSP2SSP   | PS<5:0>  |       |        | 241                 |  |

| RxyPPS     | —           | —                | —     | RxyPPS<4:0>     |           |          |       |        |                     |  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSPx module

**Note 1:** When using designated I<sup>2</sup>C pins, the associated pin values in INLVLx will be ignored.

### 33.1.2.3 Receive Interrupts

The RXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RXxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RXxIF interrupts are enabled by setting all of the following bits:

- RXxIE, Interrupt Enable bit of the PIE3 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RXxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

## 33.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCxSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCxREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCxSTA register which resets the EUSART. Clearing the CREN bit of the RCxSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note: If all receive characters in the receive FIFO have framing errors, repeated reads of the RCxREG will not clear the FERR bit.

## 33.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCxSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCxSTA register or by resetting the EUSART by clearing the SPEN bit of the RCxSTA register.

## 33.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

## 33.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RXxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

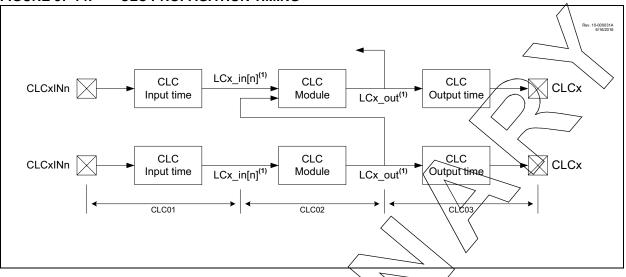

## TABLE 37-20: CONFIGURABLE LOGIC CELL (CLC) CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)   Operating temperature -40°C ≤ TA ≤ +125°C |         |                                             |            |          |      |          |                          |  |

|-----------------------------------------------------------------------------------------------------|---------|---------------------------------------------|------------|----------|------|----------|--------------------------|--|

| Param.<br>No.                                                                                       | Sym.    | Characteristic                              | Min.       | Typt     | Max. | Units    | Conditions               |  |

| CLC01*                                                                                              | TCLCIN  | CLC input time                              | $\searrow$ | 7        | 105  | ns       | (Note 1)                 |  |

| CLC02*                                                                                              | TCLC    | CLC module input to output propagation time | $\searrow$ | 24<br>12 | _    | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |  |

| CLC03*                                                                                              | TCLCOUT | CLC output time Rise Time                   | —          | 107      | _    | _        | (Note 1)                 |  |

|                                                                                                     |         | Fall Time                                   | —          | IO8      | _    | —        | (Note 1)                 |  |

| CLC04*                                                                                              | FCLCMAX | CLC maximum switching frequency             | —          | 32       | Fosc | MHz      |                          |  |

- \* These parameters are characterized but not/tested.

- † Data in "Typ" column is at 3.0%, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: See Table 37-10 for IØ5, IØ7 and IO8 rise and fall times.

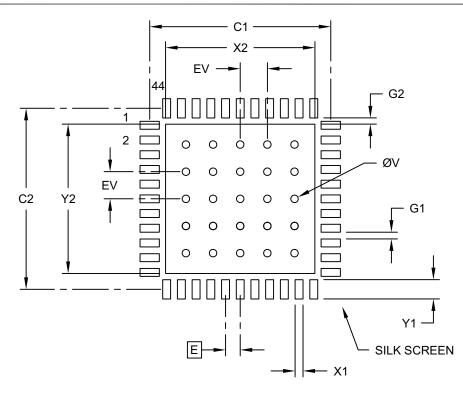

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                  | Ν                | AILLIMETER: | S    |      |  |

|----------------------------------|------------------|-------------|------|------|--|

| Dimension                        | Dimension Limits |             |      |      |  |

| Contact Pitch                    | E                | 0.65 BSC    |      |      |  |

| Optional Center Pad Width        | X2               |             |      | 6.60 |  |

| Optional Center Pad Length       | Y2               |             |      | 6.60 |  |

| Contact Pad Spacing              | C1               |             | 8.00 |      |  |

| Contact Pad Spacing              | C2               |             | 8.00 |      |  |

| Contact Pad Width (X44)          | X1               |             |      | 0.35 |  |

| Contact Pad Length (X44)         | Y1               |             |      | 0.85 |  |

| Contact Pad to Contact Pad (X40) | G1               | 0.30        |      |      |  |

| Contact Pad to Center Pad (X44)  | G2               | 0.28        |      |      |  |

| Thermal Via Diameter             | V                |             | 0.33 |      |  |

| Thermal Via Pitch                |                  | 1.20        |      |      |  |

#### Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510