Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 40-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 40-UQFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15375t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| PIC16(   |

|----------|

| L)F1535  |

| 56/75/76 |

| 6/85/86  |

#### 40/44-PIN ALLOCATION TABLE (PIC16(L)F15375, PIC16(L)F15376) (CONTINUED) TABLE 4:

|                    |             |             |            |             |      |           |            |     | ( ) |                     |     | ,   | <i>,</i> , | -                              |     |                           |     |      |           |         |             |

|--------------------|-------------|-------------|------------|-------------|------|-----------|------------|-----|-----|---------------------|-----|-----|------------|--------------------------------|-----|---------------------------|-----|------|-----------|---------|-------------|

| I/O <sup>(2)</sup> | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC  | Reference | Comparator | NCO | DAC | Timers              | ССР | MWA | CWG        | ASSM                           | ZCD | EUSART                    | CLC | CLKR | Interrupt | Bull-up | Basic       |

| RC3                | 18          | 33          | 37         | 37          | ANC3 | —         | —          | _   | -   | T2IN <sup>(1)</sup> |     | _   | -          | SCL1<br>SCK1 <sup>(1,4)</sup>  | _   | -                         | _   | —    | IOCC3     | Y       |             |

| RC4                | 23          | 38          | 42         | 42          | ANC4 | —         | —          | _   | _   | —                   | _   | _   | —          | SDA1<br>SDI1 <sup>(1,4)</sup>  | —   | -                         | _   | _    | IOCC4     | Y       | _           |

| RC5                | 24          | 39          | 43         | 43          | ANC5 | _         | _          | _   | _   | _                   | _   | _   | _          | _                              | _   | _                         | _   | _    | IOCC5     | Υ       | —           |

| RC6                | 25          | 40          | 44         | 44          | ANC6 | —         | —          | _   | -   | _                   | _   | _   | —          | —                              | _   | TX1<br>CK1 <sup>(1)</sup> | —   | _    | IOCC6     | Y       | _           |

| RC7                | 26          | 1           | 1          | 1           | ANC7 | —         | —          |     |     | _                   |     | _   | —          | —                              | _   | RX1<br>DT1 <sup>(1)</sup> | —   | —    | IOCC7     | Y       |             |

| RD0                | 19          | 34          | 38         | 38          | AND0 | —         | —          | _   | -   | —                   |     | —   | —          | SCK2,<br>SCL2 <sup>(1,4)</sup> | —   | -                         | —   | —    | —         | -       | —           |

| RD1                | 20          | 35          | 39         | 39          | AND1 | _         | —          | _   | -   | _                   | _   | _   | _          | SDA2,<br>SDI2 <sup>(1,4)</sup> | _   | -                         | _   | _    | _         | -       |             |

| RD2                | 21          | 36          | 40         | 40          | AND2 | _         | _          | _   | _   | _                   | _   | _   | _          | _                              | _   |                           | —   | _    | _         | —       | —           |

| RD3                | 22          | 37          | 41         | 41          | AND3 | _         | —          | _   | _   | _                   | _   | —   | _          | _                              | _   | _                         | _   | _    | _         | —       | - 1         |

| RD4                | 27          | 2           | 2          | 2           | AND4 | -         | —          | -   |     | _                   |     | —   | —          | _                              | —   | —                         | —   | -    | _         | _       | —           |

| RD5                | 28          | 3           | 3          | 3           | AND5 | _         | —          |     |     | —                   |     | —   | —          | —                              | —   | —                         | —   | _    | —         | -       | —           |

| RD6                | 29          | 4           | 4          | 4           | AND6 | _         | —          |     |     | —                   |     | —   | —          | _                              | —   | —                         | —   | _    | —         | _       | —           |

| RD7                | 30          | 5           | 5          | 5           | AND7 | -         | —          |     |     | —                   |     | —   | _          | —                              | —   | —                         | _   | _    | —         | —       | —           |

| RE0                | 8           | 23          | 25         | 25          | ANE0 | _         | —          | _   | _   | _                   | _   | —   | —          | _                              | —   | —                         | _   | _    | —         | —       |             |

| RE1                | 9           | 24          | 26         | 26          | ANE1 | _         | —          | _   | —   | _                   | _   | —   | —          | _                              | —   | _                         | _   | _    | —         | —       | —           |

| RE2                | 10          | 25          | 27         | 27          | ANE2 | —         | —          | -   | —   | —                   | _   | —   | —          | —                              | —   | —                         | —   | —    | —         | —       | —           |

| RE3                | 1           | 16          | 18         | 18          | —    | -         | —          | —   | —   | —                   | —   | —   | —          | —                              | —   | _                         | —   | -    | IOCE3     | Y       | MCLR<br>VPP |

| VDD                | 11          | 26          | 7          | 7           | _    |           | —          | _   | -   | _                   | -   | —   | _          | _                              | _   | —                         | _   |      | _         | —       | Vdd         |

| VDD                | 32          | 7           | 28         | 28          | —    | -         | —          | _   | -   | —                   | _   | —   | —          | —                              | _   | —                         | —   | _    | —         | -       | Vdd         |

| Vss                | 12          | 27          | 6          | 6           | _    | —         | —          | _   | _   | _                   | _   | _   | _          | _                              | —   | _                         | _   | _    | _         | —       | Vss         |

| Vss                | 31          | 6           | 30         | 29          | —    | _         | —          | —   | —   | —                   | —   | —   | —          | —                              | —   | —                         | —   | _    | —         | -       | Vss         |

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. 1: Note

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or 4: SMBUS input buffer thresholds.

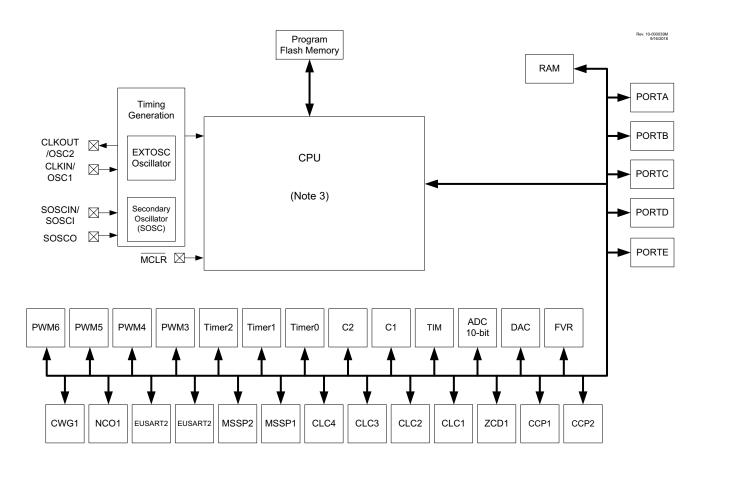

### FIGURE 1-2: PIC16(L)F15375/76 BLOCK DIAGRAM

Note 1: See applicable chapters for more information on peripherals.

- 2: See Table 1-1 for peripherals available on specific devices.

- 3: See Figure 3-1.

#### **TABLE 1-4:** PIC16(L)F15385/86 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                                                                                                                                                                                                                                                                                                               | Function | Input<br>Type | Output Type | Description                    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|-------------|--------------------------------|--|--|

| RF5/ANF5                                                                                                                                                                                                                                                                                                                                                                           | RF5      | TTL/ST        | CMOS/OD     | General purpose I/O.           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                    | ANF5     | AN            | _           | ADC Channel D0 input.          |  |  |

| RF6/ANF6                                                                                                                                                                                                                                                                                                                                                                           | RF6      | TTL/ST        | CMOS/OD     | General purpose I/O.           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                    | ANF6     | AN            | —           | ADC Channel D0 input.          |  |  |

| RF7/ANF7                                                                                                                                                                                                                                                                                                                                                                           | RF5      | TTL/ST        | CMOS/OD     | General purpose I/O.           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                    | ANF5     | AN            | _           | ADC Channel D0 input.          |  |  |

| VDD                                                                                                                                                                                                                                                                                                                                                                                | Vdd      | Power         | _           | Positive supply voltage input. |  |  |

| Vss                                                                                                                                                                                                                                                                                                                                                                                | Vss      | Power         | _           | Ground reference.              |  |  |

| Legend:         AN         =         Analog input or output         CMOS         =         CMOS compatible input or output         OD         =         Open-Drain           TTL         =         TTL compatible input         ST         =         Schmitt Trigger input with CMOS levels         I <sup>2</sup> C         =         Schmitt Trigger input with I <sup>2</sup> C |          |               |             |                                |  |  |

TTL = TTL compatible input

HV = High Voltage

XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-7.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for  $l^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the  $l^2C$  specific or SMBus input buffer thresholds. 4:

#### **BANK 16 BANK 17 BANK 18 BANK 19 BANK 20 BANK 21** BANK 22 **BANK 23** 800h 880h 900h 980h A00h A80h B00h B80h Core Register (Table 4-3) 90Bh 98Bh A0Bh B0Bh B8Bh 80Bh 88Bh A8Bh 80Ch WDTCON0 88Ch CPUDOZE 90Ch FVRCON 98Ch A0Ch A8Ch B0Ch B8Ch \_\_\_\_ \_\_\_\_ \_ \_ \_ 80Dh WDTCON1 88Dh OSCCON1 90Dh 98Dh \_ A0Dh \_ A8Dh \_\_\_\_ B0Dh \_ B8Dh \_ 80Eh WDTL 88Eh OSCCON2 90Eh DAC1CON0 98Eh \_ A0Eh \_ A8Eh B0Eh \_ B8Eh \_ \_ 80Fh WDTH 88Fh OSCCON3 90Fh DAC1CON1 98Fh CMOUT A0Fh \_ A8Fh B0Fh \_ B8Fh \_ \_ 810h WDTU 890h OSCSTAT1 910h 990h CM1CON0 A10h A90h B10h B90h \_ \_ \_ \_ \_ BORCON 811h 891h OSCEN 911h 991h CM1CON1 A11h A91h B11h B91h \_ \_ \_ \_ \_ VREGCON<sup>(2)</sup> OSCTUNE 992h B12h B92h 812h 892h 912h \_ CM1NCH A12h \_ A92h \_ \_\_\_\_ \_ PCON0 893h OSCFRQ 913h 993h A13h A93h B13h B93h 813h CM1PCH \_ \_ \_ \_ \_ 814h PCON1 894h \_ 914h 994h CM2CON0 A14h \_ A94h B14h B94h \_\_\_\_ 895h CLKRCON 915h 995h A95h B15h B95h 815h \_ \_ CM2CON1 A15h \_ \_\_\_\_ \_ \_ CLKCLK B16h 816h \_ 896h 916h 996h A16h \_ A96h B96h \_ CM2NCH \_ \_\_\_\_ \_ 817h 897h 917h 997h CM2PCH A17h A97h B17h B97h \_ \_ \_ — \_ \_ \_ 818h 898h 918h 998h A18h A98h B18h B98h \_ \_ \_ \_ \_ \_ \_\_\_\_ 919h 999h RC2REG B99h 819h \_ 899h A19h A99h B19h \_ \_ \_ \_ \_ \_ 81Ah NVMADRL 89Ah \_ 91Ah \_ 99Ah \_ A1Ah TX2REG A9Ah \_ B1Ah \_ B9Ah \_ 81Bh NVMADRH 89Bh 91Bh 99Bh A1Bh SP2BRGL A9Bh B1Bh B9Bh \_ \_ \_ \_ \_ 81Ch 89Ch 91Ch 99Ch A1Ch A9Ch B1Ch B9Ch NVMDATL SP2BRGH \_ \_ \_ \_ \_ \_ 81Dh 89Dh 91Dh 99Dh A1Dh RC2STA A9Dh B1Dh B9Dh **NVMDATH** \_ \_ \_ \_ \_ \_ 91Eh 99Eh TX2STA A9Eh B1Eh B9Eh 81Eh NVMCON1 89Eh A1Eh \_ — \_ \_ 81Fh NVMCON2 89Fh \_ 91Fh ZCDCON 99Fh A1Fh BAUD2CON A9Fh \_ B1Fh \_ B9Fh \_ 820h General 8A0h General 920h General 9A0h General A20h General AA0h General B20h General BA0h General Purpose Purpose Purpose Purpose Purpose Purpose Purpose Purpose Register Register Register Register Register Register Register Register 80 Bytes(3) 80 Bytes<sup>(3)</sup> 80 Bytes(3) 80 Bytes(3) 80 Bytes<sup>(3)</sup> 80 Bytes(3) 80 Bytes<sup>(3)</sup> 80 Bytes<sup>(3)</sup> 86Fh 8EFh 96Fh 9EFh A6Fh AEFh B6Fh BEFh 8F0h 970h 9F0h A70h AF0h Common RAM B70h BF0h 870h Common RAM Accesses Accesses Accesses Accesses Accesses Accesses Accesses Accesses 87Fh 8FFh 97Fh 70h-7Fh 9FFh 70h-7Fh A7Fh AFFh B7Fh 70h-7Fh BFFh 70h-7Fh 70h-7Fh 70h-7Fh 70h-7Fh 70h-7Fh

#### TABLE 4-6: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANKS 16-23

Note 1: Unimplemented locations read as '0'.

2: Register not implemented on LF devices.

3: Present only in PIC16(L)F15356/76/86.

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address  | Name                                            | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|----------|-------------------------------------------------|---------------|-------|-------|-------|-------|-------|-------|-------|-----------------------|----------------------------|

| Bank 7   | ank 7                                           |               |       |       |       |       |       |       |       |                       |                            |

|          | CPU CORE REGISTERS; see Table 4-3 for specifics |               |       |       |       |       |       |       |       |                       |                            |

| 38Ch     | PWM6DCL                                         | DC<1:0        | )>    | _     | —     | _     | _     | —     | _     | xx                    | uu                         |

| 38Dh     | PWM6DCH                                         |               |       |       | DC<9  | ):0>  |       |       |       | XXXX XXXX             | uuuu uuuu                  |

| 38Eh     | PWM6CON                                         | EN            | _     | OUT   | POL   | —     | —     | —     | _     | 0-00                  | 0-00                       |

| 38Fh<br> | —                                               | Unimplemented |       |       |       |       |       |       | -     | _                     |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| IABLE 4  | ABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |          |       |         |               |                   |           |           |       |                       |                            |

|----------|---------------------------------------------------------------------|----------|-------|---------|---------------|-------------------|-----------|-----------|-------|-----------------------|----------------------------|

| Address  | Name                                                                | Bit 7    | Bit 6 | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1     | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 12  |                                                                     |          |       |         |               |                   |           |           |       |                       |                            |

|          |                                                                     |          |       | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics |           |       |                       |                            |

| 60Ch     | CWG1CLKCON                                                          | —        | _     | —       | _             | —                 | —         | _         | CS    | 0                     | 0                          |

| 60Dh     | CWG1DAT                                                             | _        | _     | _       | — — DAT<3:0>  |                   |           |           | 0000  | 0000                  |                            |

| 60Eh     | CWG1DBR                                                             | _        | _     |         | DBR<5:0>      |                   |           |           |       |                       | 00 0000                    |

| 60Fh     | CWG1DBF                                                             | _        | _     |         |               | DB                | F<5:0>    |           |       | 00 0000               | 00 0000                    |

| 610h     | CWG1CON0                                                            | EN       | LD    | —       | —             | —                 |           | MODE<2:0> | •     | 00000                 | 00000                      |

| 611h     | CWG1CON1                                                            | _        | —     | IN      | —             | POLD              | POLC      | POLB      | POLA  | x- 0000               | u- 0000                    |

| 612h     | CWG1AS0                                                             | SHUTDOWN | REN   | LSBD    | <2:0>         | LSAC              | <2:0>     | —         | _     | 0001 01               | 0001 01                    |

| 613h     | CWG1AS1                                                             | _        | —     | _       | AS4E          | AS3E              | AS2E      | AS1E      | AS0E  | 0 0000                | u 0000                     |

| 614h     | CWG1STR                                                             | OVRD     | OVRC  | OVRB    | OVRA          | STRD              | STRC      | STRB      | STRA  | 0000 0000             | 0000 0000                  |

| 615h     |                                                                     |          |       |         |               |                   |           |           |       |                       |                            |

| <br>61Fh | - Unimplemented — — —                                               |          |       |         |               |                   |           |           |       |                       |                            |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

PIC16(L)F15356/75/76/85/86

| Address              | Name                                            | Bit 7         | Bit 6   | Bit 5   | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|----------------------|-------------------------------------------------|---------------|---------|---------|----------|--------|--------|--------|--------|-----------------------|----------------------------|

| Bank 15              |                                                 |               |         |         |          |        |        |        |        |                       |                            |

|                      | CPU CORE REGISTERS; see Table 4-3 for specifics |               |         |         |          |        |        |        |        |                       |                            |

| 78Ch<br>             | – Unimplemented                                 |               |         |         |          |        |        |        |        | —                     | —                          |

| 796h                 | PMD0                                            | SYSCMD        | FVRMD   | _       | _        | _      | NVMMD  | CLKRMD | IOCMD  | 00000                 | 00000                      |

| 797h                 | PMD1                                            | NCO1MD        | _       | _       | _        | _      | TMR2MD | TMR1MD | TMR0MD | 0000                  | 0000                       |

| 798h                 | PMD2                                            | _             | DAC1MD  | ADCMD   | _        | _      | CMP2MD | CMP1MD | ZCDMD  | -00000                | -00000                     |

| 799h                 | PMD3                                            | _             | _       | PWM6MD  | PWM5MD   | PWM4MD | PWM3MD | CCP2MD | CCP1MD | 00 0000               | 00 0000                    |

| 79Ah                 | PMD4                                            | UART2MD       | UART1MD | MSSP2MD | MSSP1MD  |        |        | _      | CWG1MD | 00000                 | 00000                      |

| 79Bh                 | PMD5                                            | _             | _       | —       | CLC4MD   | CLC3MD | CLC2MD | CLC1MD | _      | 0 000-                | 0 000-                     |

| 79Ch                 | _                                               | Unimplemented |         |         |          |        |        |        |        | —                     | _                          |

| 79Dh — Unimplemented |                                                 |               |         |         |          |        |        |        | —      | _                     |                            |

| 79Eh                 | _                                               | Unimplemented |         |         |          |        |        |        |        | —                     | _                          |

| 79Fh                 | _                                               |               |         |         | Unimpler | mented |        |        |        | _                     | _                          |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

# PIC16(L)F15356/75/76/85/86

#### REGISTER 10-14: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| _     | _   |     |     | _   | _   | TMR2IF     | TMR1IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7-2<br>bit 1 | Unimplemented: Read as '0'<br>TRM2IF: Timer2 Interrupt Flag bit<br>1 = The TMR2 postscaler overflowed, or in 1:1 mode, a TMR2 to PR2 match occurred (must be cleared<br>in software)<br>0 = No TMR2 event has occurred |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0            | <b>TRM1IF:</b> Timer1 Overflow Interrupt Flag bit<br>1 = Timer1 overflow occurred (must be cleared in software)<br>0 = No Timer1 overflow occurred                                                                     |

| Note:            | Interrupt flag bits are set when an interrupt                                                                                                                                                                          |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

© 2016 Microchip Technology Inc.

#### REGISTER 10-16: PIR6: PERIPHERAL INTERRUPT REQUEST REGISTER 6

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|-----|-----|-----|-----|------------|------------|

| —     | —   | -   | -   | -   | —   | CCP2IF     | CCP1IF     |

| bit 7 |     |     |     |     |     |            | bit 0      |

|       |     |     |     |     |     |            |            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

#### bit 7-2 Unimplemented: Read as '0'

bit 1

#### CCP2IF: CCP2 Interrupt Flag bit

| Value | CCPM Mode                                         |                                                      |                                                                |  |  |

|-------|---------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|--|--|

| value | Capture                                           | Compare                                              | PWM                                                            |  |  |

| 1     | Capture occurred<br>(must be cleared in software) | Compare match occurred (must be cleared in software) | Output trailing edge occurred<br>(must be cleared in software) |  |  |

| 0     | Capture did not occur                             | Compare match did not occur                          | Output trailing edge did not occur                             |  |  |

#### bit 0 CCP1IF: CCP1 Interrupt Flag bit

| Value | CCPM Mode                                         |                                                         |                                                                |  |  |

|-------|---------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------|--|--|

| value | Capture                                           | ture Compare PWM                                        |                                                                |  |  |

| 1     | Capture occurred<br>(must be cleared in software) | Compare match occurred<br>(must be cleared in software) | Output trailing edge occurred<br>(must be cleared in software) |  |  |

| 0     | Capture did not occur                             | Compare match did not occur                             | Output trailing edge did not occur                             |  |  |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

© 2016 Microchip Technology Inc.

### 13.0 NONVOLATILE MEMORY (NVM) CONTROL

NVM consists of the Program Flash Memory (PFM).

NVM is accessible by using both the FSR and INDF registers, or through the NVMREG register interface.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways; by either code protection or write protection.

Code protection (CP bit in Configuration Word 5) disables access, reading and writing, to the PFM via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be Reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits, and User IDs.

Write protection prohibits self-write and erase to a portion or all of the PFM, as defined by the WRT<1:0> bits of Configuration Word 4. Write protection does not affect a device programmer's ability to read, write, or erase the device.

#### 13.1 Program Flash Memory (PFM)

PFM consists of an array of 14-bit words as user memory, with additional words for User ID information, Configuration words, and interrupt vectors. PFM provides storage locations for:

- User program instructions

- User defined data

PFM data can be read and/or written to through:

- CPU instruction fetch (read-only)

- FSR/INDF indirect access (read-only) (Section 13.2 "FSR and INDF Access")

- NVMREG access (Section 13.3 "NVMREG Access"

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

Read operations return a single word of memory. When write and erase operations are done on a row basis, the row size is defined in Table 13-1. PFM will erase to a logic '1' and program to a logic '0'.

#### TABLE 13-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device            | Row<br>Erase<br>(words) | Write<br>Latches<br>(words) | Total<br>Program<br>Flash<br>(words) |

|-------------------|-------------------------|-----------------------------|--------------------------------------|

| PIC16(L)F15356    |                         |                             | 16K                                  |

| PIC16(L)F15375/85 | 32                      | 32                          | 8K                                   |

| PIC16(L)F15376/86 |                         |                             | 16K                                  |

It is important to understand the PFM memory structure for erase and programming operations. PFM is arranged in rows. A row consists of 32 14-bit program memory words. A row is the minimum size that can be erased by user software.

All or a portion of this row can be programmed. Data to be written into the program memory row is written to 14-bit wide data write latches. These latches are not directly accessible, but may be loaded via sequential writes to the NVMDATH:NVMDATL register pair.

#### 13.1.1 PROGRAM MEMORY VOLTAGES

The PFM is readable and writable during normal operation over the full VDD range.

#### 13.1.1.1 Programming Externally

The program memory cell and control logic support write and Bulk Erase operations down to the minimum device operating voltage. Special BOR operation is enabled during Bulk Erase (Section 8.2.4 "BOR is always OFF").

#### 13.1.1.2 Self-programming

The program memory cell and control logic will support write and row erase operations across the entire VDD range. Bulk Erase is not available when selfprogramming.

#### EXAMPLE 13-1: PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELNVMADRL; Select Bank for NVMCON registersMOVLWPROG_ADDR_LO;MOVWFNVMADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWFNVMADRH; Store MSB of address

BCF

NVMCON1,NVMREGS ; Do not select Configuration Space

BSF

NVMCON1, RD

; Initiate read

MOVF

NVMDATL,W

; Get LSB of word

NVMDATL,W; Get LSB of wordPROG_DATA_LO; Store in user locationNVMDATH,W; Get MSB of wordPROG_DATA_HI; Store in user location

MOVWF

MOVF

MOVWF

```

| U-0                  | R/W-0/0                                                                                                                                                                                                                                                                                               | R/W-0/0                                                                                                                                                                                                                                                                                                                                  | R/W/HC-0/0                           | R/W/HC-x/q                                     | R/W-0/0            | R/S/HC-0/0            | R/S/HC-0/0      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------|--------------------|-----------------------|-----------------|

| _                    | NVMREGS                                                                                                                                                                                                                                                                                               | LWLO                                                                                                                                                                                                                                                                                                                                     | FREE                                 | WRERR <sup>(1,2,3)</sup>                       | WREN               | WR <sup>(4,5,6)</sup> | RD              |

| bit 7                |                                                                                                                                                                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                        |                                      | -                                              |                    |                       | bit             |

|                      |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                      |                                                |                    |                       |                 |

| Legend:              |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                      |                                                |                    |                       |                 |

| R = Readable         | e bit                                                                                                                                                                                                                                                                                                 | W = Writable b                                                                                                                                                                                                                                                                                                                           | bit                                  | U = Unimplemer                                 | nted bit, read as  | s 'O'                 |                 |

| S = Bit can or       | nly be set                                                                                                                                                                                                                                                                                            | x = Bit is unkn                                                                                                                                                                                                                                                                                                                          | own                                  | -n/n = Value at F                              | OR and BOR/        | Value at all other I  | Resets          |

| '1' = Bit is set     | :                                                                                                                                                                                                                                                                                                     | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                        | red                                  | HC = Bit is cleared by hardware                |                    |                       |                 |

| bit 7                | Unimplemente                                                                                                                                                                                                                                                                                          | ed: Read as '0'                                                                                                                                                                                                                                                                                                                          |                                      |                                                |                    |                       |                 |

| bit 6                | NVMREGS: Co                                                                                                                                                                                                                                                                                           | onfiguration Sele<br>IA, DCI, Configu                                                                                                                                                                                                                                                                                                    |                                      | and Device ID Reg                              | jisters            |                       |                 |

| bit 5                | <ul> <li>LWLO: Load Write Latches Only bit</li> <li><u>When FREE = 0</u>:</li> <li>1 = The next WR command updates the write latch for this word within the row; no memory operation is init</li> <li>0 = The next WR command writes data or erases</li> <li>Otherwise: The bit is ignored</li> </ul> |                                                                                                                                                                                                                                                                                                                                          |                                      |                                                | ation is initiated |                       |                 |

| bit 4                | 1 = Performs<br>address is                                                                                                                                                                                                                                                                            | GS:NVMADR po<br>an erase operat<br>s erased (to all 1                                                                                                                                                                                                                                                                                    | ion with the nex<br>s) to prepare fo | t WR command; t<br>r writing.                  | he 32-word pse     | eudo-row containi     | ng the indicate |

| bit 3                | WRERR: Prog<br>This bit is norm<br>1 = A write op<br>NVMADR                                                                                                                                                                                                                                           | <ul> <li>0 = All erase operations have completed non</li> <li>WRERR: Program/Erase Error Flag bit<sup>(1,2,3)</sup></li> <li>This bit is normally set by hardware.</li> <li>1 = A write operation was interrupted by a R</li> <li>NVMADR points to a write-protected add</li> <li>0 = The program or erase operation complete</li> </ul> |                                      | eset, interrupted ur                           | nlock sequence     | e, or WR was writ     | ten to one whil |

| bit 2                | WREN: Progra<br>1 = Allows pro                                                                                                                                                                                                                                                                        | m/Erase Enable<br>ogram/erase cyc<br>ogramming/eras                                                                                                                                                                                                                                                                                      | bit<br>les                           |                                                |                    |                       |                 |

| bit 1                | 1 = Initiates th                                                                                                                                                                                                                                                                                      | ntrol bit <sup>(4,5,6)</sup><br><u>G:NVMADR poin</u><br>ne operation indi<br>gram/erase opera                                                                                                                                                                                                                                            | cated by Table                       | 13-4                                           |                    |                       |                 |

| bit 0                | <b>RD:</b> Read Con<br>1 = Initiates a<br>bit is clear                                                                                                                                                                                                                                                | trol bit <sup>(7)</sup><br>read at address                                                                                                                                                                                                                                                                                               | = NVMADR1, a<br>eration is compl     | nd loads data to N<br>ete. The bit can or      |                    |                       | •               |

| 2: B<br>3: B<br>4: T | Bit is undefined while<br>Bit must be cleared b<br>Bit may be written to<br>This bit can only be s<br>Operations are self-t                                                                                                                                                                           | by software; hard<br>o '1' by software<br>set by following t                                                                                                                                                                                                                                                                             | in order to imple<br>the unlock sequ | ement test sequend<br>ence of <b>Section 1</b> | 3.3.2 "NVM Un      | llock Sequence"       |                 |

#### REGISTER 13-5: NVMCON1: NONVOLATILE MEMORY CONTROL 1 REGISTER

6: Once a write operation is initiated, setting this bit to zero will have no effect.

#### 24.7 Operation During Sleep

The ZCD current sources and interrupts are unaffected by Sleep.

#### 24.8 Effects of a Reset

The ZCD circuit can be configured to default to the active or inactive state on Power-on-Reset (POR). When the ZCDDIS Configuration bit is cleared, the ZCD circuit will be active at POR. When the ZCD Configuration bit is set, the EN bit of the ZCDxCON register must be set to enable the ZCD module.

#### 26.1 Timer1 Operation

The Timer1 modules are 16-bit incrementing counters which are accessed through the TMR1H:TMR1L register pairs. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

The timer is enabled by configuring the TMR1ON and GE bits in the T1CON and T1GCON registers, respectively. Table 26-1 displays the Timer1 enable selections.

TABLE 26-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 1      | 1      | Count Enabled       |

| 1      | 0      | Always On           |

| 0      | 1      | Off                 |

| 0      | 0      | Off                 |

#### 26.2 Clock Source Selection

The T1CLK register is used to select the clock source for the timer. Register 26-3 shows the possible clock sources that may be selected to make the timer increment.

#### 26.2.1 INTERNAL CLOCK SOURCE

When the internal clock source Fosc is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the respective Timer1 prescaler.

When the Fosc internal clock source is selected, the timer register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the TMR1H:TMR1L value. To utilize the full resolution of the timer in this mode, an asynchronous input signal must be used to gate the timer clock input.

Out of the total timer gate signal sources, the following subset of sources can be asynchronous and may be useful for this purpose:

- CLC4 output

- CLC3 output

- CLC2 output

- CLC1 output

- · Zero-Cross Detect output

- · Comparator2 output

- Comparator1 output

- TxG PPS remappable input pin

#### 26.2.2 EXTERNAL CLOCK SOURCE

When the timer is enabled and the external clock input source (ex: T1CKI PPS remappable input) is selected as the clock source, the timer will increment on the rising edge of the external clock input.

When using an external clock source, the timer can be configured to run synchronously or asynchronously, as described in Section 26.5 "Timer Operation in Asynchronous Counter Mode".

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used connected to the SOSCI/SOSCO pins.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · The timer is first enabled after POR

- Firmware writes to TMR1H or TMR1L

- · The timer is disabled

- The timer is re-enabled (e.g., TMR1ON-->1) when the T1CKI signal is currently logic low.

#### 27.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

### PIC16(L)F15356/75/76/85/86

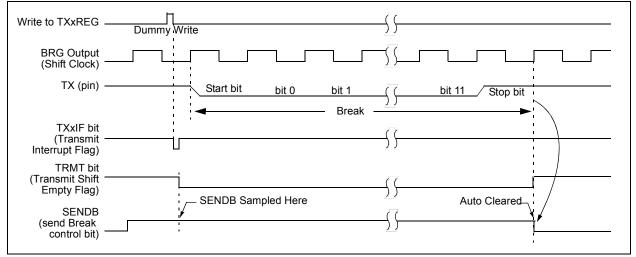

#### 33.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCxSTA register and the received data as indicated by RCxREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when:

- · RXxIF bit is set

- · FERR bit is set

- RCxREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 33.3.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RXxIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDxCON register before placing the EUSART in Sleep mode.

# PIC16(L)F15356/75/76/85/86

### **REGISTER 33-7:** SPxBRGH<sup>(1, 2)</sup>: BAUD RATE GENERATOR HIGH REGISTER

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|---------|-------|-------|-------|---------|-------|-------|-------|

|         |       |       | SPxBR | G<15:8> |       |       |       |

| bit 7   |       |       |       |         |       |       | bit 0 |

|         |       |       |       |         |       |       |       |

| Legend: |       |       |       |         |       |       |       |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 SPxBRG<15:8>: Upper eight bits of the Baud Rate Generator

**Note 1:** SPxBRGH value is ignored for all modes unless BAUDxCON<BRG16> is active.

2: Writing to SPxBRGH resets the BRG counter.

# PIC16(L)F15356/75/76/85/86

| SLEEP            | Enter Sleep mode                                                                                                                                                                                  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] SLEEP                                                                                                                                                                                     |  |

| Operands:        | None                                                                                                                                                                                              |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \mbox{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                        |  |

| Status Affected: | TO, PD                                                                                                                                                                                            |  |

| Description:     | The power-down Status bit, PD is<br>cleared. Time-out Status bit, TO is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>See <b>Section 11.2 "Sleep Mode"</b> for<br>more information. |  |

| SUBWF            | Subtract W from f                                                                                                                                                           |                 |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| Syntax:          | [ <i>label</i> ] SL                                                                                                                                                         | IBWF f,d        |  |  |

|                  | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                          |                 |  |  |

| Operation:       | $(f) - (W) \to (d$                                                                                                                                                          | estination)     |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                    |                 |  |  |

|                  | Subtract (2's complement methor<br>register from register 'f'. If 'd' is '<br>result is stored in the W<br>register. If 'd' is '1', the result is s<br>back in register 'f. |                 |  |  |

|                  | <b>C =</b> 0                                                                                                                                                                | W > f           |  |  |

|                  | <b>C =</b> 1                                                                                                                                                                | $W \leq f$      |  |  |

|                  | DC = 0                                                                                                                                                                      | W<3:0> > f<3:0> |  |  |

$W<3:0> \le f<3:0>$

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                     |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                     |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                 |  |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                     |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                          |  |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's<br>complement method). If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |

DC = 1

| SUBLW            | Subtract W from literal                                                                                                  |           |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|-----------|--|

| Syntax:          | [label] SU                                                                                                               | JBLW k    |  |

| Operands:        | $0 \le k \le 255$                                                                                                        |           |  |

| Operation:       | $k - (W) \to (W$                                                                                                         | /)        |  |

| Status Affected: | C, DC, Z                                                                                                                 |           |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |           |  |

|                  | <b>C</b> = 0                                                                                                             | W > k     |  |

|                  | <b>C =</b> 1                                                                                                             | $W \le k$ |  |

DC = 0

DC = 1

W<3:0> > k<3:0>

$W<3:0> \le k<3:0>$

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                      |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |  |  |  |

| Status Affected: | None                                                                                                                                                                   |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |  |  |  |

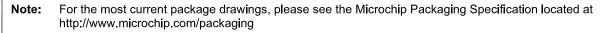

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.40 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 4.45 |

| Optional Center Pad Length | T2 |             |      | 4.45 |

| Contact Pad Spacing        | C1 |             | 6.00 |      |

| Contact Pad Spacing        | C2 |             | 6.00 |      |

| Contact Pad Width (X28)    | X1 |             |      | 0.20 |

| Contact Pad Length (X28)   | Y1 |             |      | 0.80 |

| Distance Between Pads      | G  | 0.20        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A