Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15375t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABL              | <b>= 4</b> : |             | 40/        | 44-r        |                      | LUCA      |                  | ADLE (P |          | 5375, 1                       |                     | L)F15576 | )                   |                               |      |                           |                       |      |                             |         |                 |

|-------------------|--------------|-------------|------------|-------------|----------------------|-----------|------------------|---------|----------|-------------------------------|---------------------|----------|---------------------|-------------------------------|------|---------------------------|-----------------------|------|-----------------------------|---------|-----------------|

| VO <sup>(2)</sup> | 40-Pin PDIP  | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC                  | Reference | Comparator       | NCO     | DAC      | Timers                        | ССР                 | WMd      | CWG                 | MSSP                          | ZCD  | EUSART                    | CLC                   | CLKR | Interrupt                   | Pull-up | Basic           |

| RA0               | 2            | 17          | 19         | 19          | ANA0                 | -         | C1IN0-<br>C2IN0- | _       | _        | —                             | _                   | _        | -                   | -                             | —    | —                         | CLCIN0 <sup>(1)</sup> | -    | IOCA0                       | Y       | _               |

| RA1               | 3            | 18          | 20         | 20          | ANA1                 | —         | C1IN1-<br>C2IN1- | _       | —        | —                             | _                   |          | _                   |                               | —    | _                         | CLCIN1 <sup>(1)</sup> |      | IOCA1                       | Y       | _               |

| RA2               | 4            | 19          | 21         | 21          | ANA2                 | —         | C1IN0+<br>C2IN0+ | —       | DAC1OUT1 | —                             | _                   |          | —                   | -                             | —    | -                         | -                     |      | IOCA2                       | Y       | —               |

| RA3               | 5            | 20          | 22         | 22          | ANA3                 | VREF+     | C1IN1+           | —       | DACREF+  | —                             | -                   | -        | -                   |                               | —    | -                         | -                     |      | IOCA3                       | Y       | Ι               |

| RA4               | 6            | 21          | 23         | 23          | ANA4                 | _         | _                | _       | _        | TOCKI(1)                      | _                   | _        | _                   | _                             | _    | _                         | _                     | -    | IOCA4                       | Y       | _               |

| RA5               | 7            | 22          | 24         | 24          | ANA5                 | _         | _                | _       | _        | T1G <sup>(1)</sup>            | _                   | _        | _                   | SS1 <sup>(1)</sup>            | _    | -                         | -                     | _    | IOCA5                       | Y       | _               |

| RA6               | 14           | 29          | 33         | 31          | ANA6                 | -         | —                | -       | -        | —                             | _                   | -        | -                   | -                             | —    | -                         | -                     | _    | IOCA6                       | Y       | CLKOUT/<br>OSC1 |

| RA7               | 13           | 28          | 32         | 30          | ANA7                 | -         | —                | -       | -        | —                             | _                   | _        | -                   | _                             | —    | _                         | -                     | _    | IOCA7                       | Y       | CLKIN/<br>OSC2  |

| RB0               | 33           | 8           | 9          | 8           | ANB0                 | -         | C2IN1+           | -       | -        | —                             | _                   | -        | CWG1 <sup>(1)</sup> | SS2 <sup>(1)</sup>            | ZCD1 | -                         | -                     | _    | INT <sup>(1)</sup><br>IOCB0 | Y       | Ι               |

| RB1               | 34           | 9           | 10         | 9           | ANB1                 | _         | C1IN3-<br>C2IN3- | _       | —        | —                             | _                   |          | _                   | SCL1<br>SCK1 <sup>(1,4)</sup> | —    | _                         | —                     |      | IOCB1                       | Y       | _               |

| RB2               | 34           | 10          | 11         | 10          | ANB2                 | _         | —                | —       | —        | —                             | —                   | _        | —                   | SDA1<br>SDI1 <sup>(1,4)</sup> | —    | _                         | —                     |      | IOCB2                       | Y       | —               |

| RB3               | 36           | 11          | 12         | 11          | ANB3                 | _         | C1IN2-<br>C2IN2- | _       | —        | —                             | _                   |          | _                   |                               | —    | _                         | —                     |      | IOCB3                       | Y       | _               |

| RB4               | 37           | 12          | 14         | 14          | ANB4<br>ADACT<br>(1) | -         | _                | —       | —        | _                             | _                   |          | _                   |                               | _    | _                         | -                     | _    | IOCB4                       | Y       | _               |

| RB5               | 38           | 13          | 15         | 15          | ANB5                 | —         | —                | —       | —        | —                             | -                   | -        | -                   |                               | —    | -                         | -                     |      | IOCB5                       | Y       | Ι               |

| RB6               | 39           | 14          | 16         | 16          | ANB6                 | -         | —                | -       | _        | —                             |                     | -        |                     | -                             | —    | TX2<br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> |      | IOCB6                       | Y       | ICSPCLK         |

| RB7               | 40           | 15          | 17         | 17          | ANB7                 | -         | —                | —       | DAC1OUT2 | —                             | —                   | -        | —                   | _                             | —    | RX2<br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> |      | IOCB7                       | Y       | ICSPDAT         |

| RC0               | 15           | 30          | 34         | 32          | ANC0                 | —         | —                | —       | —        | SOSCO<br>T1CKI <sup>(1)</sup> |                     |          | _                   | —                             | —    | -                         | -                     |      | IOCC0                       | Y       | —               |

| RC1               | 16           | 31          | 35         | 35          | ANC1                 | _         | —                | _       | _        | SOSCI                         | CCP2 <sup>(1)</sup> | _        | —                   | _                             | —    | -                         | —                     | -    | IOCC1                       | Υ       | _               |

| RC2               | 17           | 32          | 36         | 36          | ANC2                 | -         | —                | —       | _        | _                             | CCP1 <sup>(1)</sup> | —        | —                   | _                             | _    | _                         | —                     | _    | IOCC2                       | Υ       | _               |

TABLE 4: 40/44-PIN ALLOCATION TABLE (PIC16(L)F15375, PIC16(L)F15376)

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

## TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                                         | ress Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value on: Value on: MCLR |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Bank 8-10                                       |                                                                                    |  |  |  |  |  |  |  |  |  |  |

| CPU CORE REGISTERS; see Table 4-3 for specifics |                                                                                    |  |  |  |  |  |  |  |  |  |  |

| x0Ch/<br>x8Ch<br>Unimplemented                  |                                                                                    |  |  |  |  |  |  |  |  |  |  |

# 9.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

### 9.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 9-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 determine the type of oscillator that will be used when the device reset, including when it is first powered up.

The internal clock modes, LFINTOSC, HFINTOSC (set at 1 MHz), or HFINTOSC (set at 32 MHz) can be set through the RSTOSC bits.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used to select the external clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode ECL<= 500 kHz

- 2. ECM External Clock Medium Power mode ECM <= 8 MHz

- 3. ECH External Clock High-Power mode ECH <= 32 MHz

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 4 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The INTOSC internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 9-1). A wide selection of device clock frequencies may be derived from these clock sources.

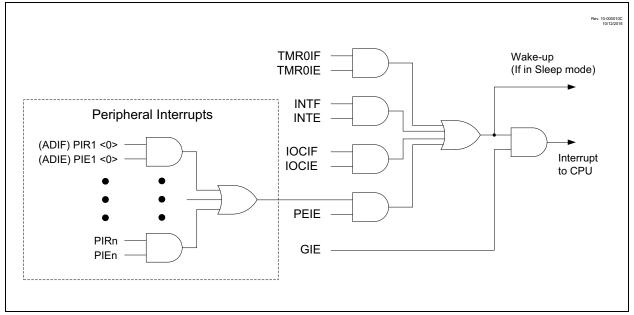

# **10.0 INTERRUPTS**

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 10-1.

### FIGURE 10-1: INTERRUPT LOGIC

| R/W-0/0                                                                                              | R/W-0/0                                                                                        | R/W-0/0                                                  | R/W-0/0        | U-0         | U-0              | U-0              | R/W-0/0      |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------|-------------|------------------|------------------|--------------|

| CLC4IE                                                                                               | CLC3IE                                                                                         | CLC2IE                                                   | CLC1IE         | —           | —                | —                | TMR1GIE      |

| bit 7                                                                                                |                                                                                                |                                                          |                |             |                  |                  | bit 0        |

|                                                                                                      |                                                                                                |                                                          |                |             |                  |                  |              |

| Legend:                                                                                              |                                                                                                |                                                          |                |             |                  |                  |              |

| R = Readab                                                                                           |                                                                                                | W = Writable                                             |                | •           | mented bit, read |                  |              |

| u = Bit is un                                                                                        | 0                                                                                              | x = Bit is unkr                                          |                |             | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se                                                                                      | et                                                                                             | '0' = Bit is cle                                         | ared           | HS = Hardwa | are set          |                  |              |

| bit 7 CLC4IE: CLC4 Interrupt Enable bit<br>1 = CLC4 interrupt enabled<br>0 = CLC4 interrupt disabled |                                                                                                |                                                          |                |             |                  |                  |              |

| bit 6                                                                                                | CLC3IE: CLC3 Interrupt Enable bit<br>1 = CLC3 interrupt enabled<br>0 = CLC3 interrupt disabled |                                                          |                |             |                  |                  |              |

| bit 5                                                                                                | 1 = CLC2 i                                                                                     | C2 Interrupt Ena<br>nterrupt enabled<br>nterrupt disable | t              |             |                  |                  |              |

| bit 4                                                                                                | 1 = CLC1 i                                                                                     | C1 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable | b              |             |                  |                  |              |

| bit 3-1                                                                                              | Unimpleme                                                                                      | nted: Read as '                                          | 0'             |             |                  |                  |              |

| bit 0                                                                                                | 1 = Enable                                                                                     | imer1 Gate Inte<br>s the Timer1 ga<br>s the Timer1 ga    | te acquisition | interrupt   |                  |                  |              |

| s                                                                                                    | Bit PEIE of the IN<br>set to enable a<br>controlled by regis                                   | any peripheral                                           | interrupt      |             |                  |                  |              |

### REGISTER 10-7: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

# REGISTER 10-11: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W/HS-0/0                                                                                                                                                                                                                                                                                                       | R/W/HS-0/0                                                                                                                                                                                                                                         | U-0                                                              | U-0                              | U-0             | U-0                      | U-0              | R/W/HS-0/0     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------|-----------------|--------------------------|------------------|----------------|

| OSFIF                                                                                                                                                                                                                                                                                                            | CSWIF                                                                                                                                                                                                                                              | —                                                                | _                                | _               | —                        | —                | ADIF           |

| bit 7                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                    |                                                                  |                                  |                 |                          |                  | bit 0          |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                    |                                                                  |                                  |                 |                          |                  |                |

| Legend:                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                    |                                                                  |                                  |                 |                          |                  |                |

| R = Readable                                                                                                                                                                                                                                                                                                     | bit                                                                                                                                                                                                                                                | W = Writable                                                     | bit                              | U = Unimpler    | mented bit, read         | as '0'           |                |

| u = Bit is unch                                                                                                                                                                                                                                                                                                  | anged                                                                                                                                                                                                                                              | x = Bit is unkr                                                  | nown                             | -n/n = Value a  | at POR and BOF           | R/Value at all c | other Resets   |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                    | '0' = Bit is clea                                                | ared                             | HS = Hardwa     | ire set                  |                  |                |

| bit 7 <b>OSFIF</b> : Oscillator Fail-Safe Interrupt Flag bit<br>1 = Oscillator fail-safe interrupt has occurred (must be cleared in software)<br>0 = No oscillator fail-safe interrupt                                                                                                                           |                                                                                                                                                                                                                                                    |                                                                  |                                  |                 |                          |                  |                |

| bit 6                                                                                                                                                                                                                                                                                                            | 1 = The clock<br>operation                                                                                                                                                                                                                         | Switch Comp<br>switch module<br>(must be clear<br>switch does no | indicates an i<br>ed in software | nterrupt condit | ion and is ready<br>tion | to complete th   | e clock switch |

| bit 5-1                                                                                                                                                                                                                                                                                                          | Unimplemen                                                                                                                                                                                                                                         | ted: Read as '                                                   | 0'                               |                 |                          |                  |                |

| bit 0                                                                                                                                                                                                                                                                                                            | <ul> <li>ADIF: Analog-to-Digital Converter (ADC) Interrupt Flag bit</li> <li>1 = An A/D conversion or complex operation has completed (must be cleared in software)</li> <li>0 = An A/D conversion or complex operation is not complete</li> </ul> |                                                                  |                                  |                 |                          |                  |                |

| Note: Interrupt flag bits are set when an interrupt<br>condition occurs, regardless of the state of<br>its corresponding enable bit or the Global<br>Enable bit, GIE, of the INTCON register.<br>User software should ensure the<br>appropriate interrupt flag bits are clear<br>prior to enabling an interrupt. |                                                                                                                                                                                                                                                    |                                                                  |                                  |                 |                          |                  |                |

| R/W/HS-0       | 0/0 R/W/HS-0/0                                                                                                                                                                 | R/W/HS-0/0                           | R/W/HS-0/0     | R/W/HS-0/0                                            | R/W/HS-0/0                          | R/W/HS-0/0      | R/W/HS-0/0    |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------------------------------------------|-------------------------------------|-----------------|---------------|--|--|

| RC2IF          | TX2IF                                                                                                                                                                          | RC1IF                                | TX1IF          | BCL2IF                                                | SSP2IF                              | BCL1IF          | SSP1IF        |  |  |

| bit 7          |                                                                                                                                                                                |                                      |                |                                                       |                                     |                 | bit (         |  |  |

|                |                                                                                                                                                                                |                                      |                |                                                       |                                     |                 |               |  |  |

| Legend:        |                                                                                                                                                                                |                                      |                |                                                       |                                     |                 |               |  |  |

| R = Reada      |                                                                                                                                                                                | W = Writable                         | bit            | •                                                     | mented bit, read                    |                 |               |  |  |

| u = Bit is u   | •                                                                                                                                                                              | x = Bit is unkr                      |                | -n/n = Value at POR and BOR/Value at all other Resets |                                     |                 |               |  |  |

| '1' = Bit is s | set                                                                                                                                                                            | '0' = Bit is cle                     | ared           | HS = Hardwa                                           | re clearable                        |                 |               |  |  |

| bit 7          | BCOLE. EUS                                                                                                                                                                     |                                      | ntorrunt Elog  | (Road Only) bi                                        | (1)                                 |                 |               |  |  |

|                | <b>RC2IF:</b> EUSART2 Receive Interrupt Flag (Read-Only) bit <sup>(1)</sup><br>1 = The EUSART2 receive buffer is not empty (contains at least one byte)                        |                                      |                |                                                       |                                     |                 |               |  |  |

|                | 0 = The EUSART2 receive buffer is empty                                                                                                                                        |                                      |                |                                                       |                                     |                 |               |  |  |

| bit 6          | TX2IF: EUSA                                                                                                                                                                    | RT2 Transmit                         | Interrupt Flag | (Read-Only) b                                         | it(2)                               |                 |               |  |  |

|                | 1 = The EUSART2 transmit buffer contains at least one unoccupied space                                                                                                         |                                      |                |                                                       |                                     |                 |               |  |  |

|                | <ul> <li>0 = The EUSART2 transmit buffer is currently full. The application firmware should not write to<br/>TXxREG</li> </ul>                                                 |                                      |                |                                                       |                                     |                 |               |  |  |

| bit 5          |                                                                                                                                                                                |                                      | nterrupt Flag  | (read-only) bit                                       | (1)                                 |                 |               |  |  |

|                | <b>RC1IF:</b> EUSART1 Receive Interrupt Flag (read-only) bit <sup>(1)</sup><br>1 = The EUSART1 receive buffer is not empty (contains at least one byte)                        |                                      |                |                                                       |                                     |                 |               |  |  |

|                |                                                                                                                                                                                | SART1 receive                        |                |                                                       | -                                   | ,               |               |  |  |

| bit 4          | <b>TX1IF:</b> EUSART1 Transmit Interrupt Flag (read-only) bit <sup>(2)</sup><br>1 = The EUSART1 transmit buffer contains at least one unoccupied space                         |                                      |                |                                                       |                                     |                 |               |  |  |

|                |                                                                                                                                                                                |                                      |                |                                                       |                                     |                 | d wat unite t |  |  |

|                |                                                                                                                                                                                |                                      |                |                                                       | ne application f<br>in the transmit |                 |               |  |  |

| bit 3          |                                                                                                                                                                                | SP2 Bus Collisi                      |                |                                                       |                                     |                 |               |  |  |

|                | 1 = A bus collision was detected (must be cleared in software)                                                                                                                 |                                      |                |                                                       |                                     |                 |               |  |  |

|                |                                                                                                                                                                                | ollision was det                     |                |                                                       |                                     |                 |               |  |  |

| bit 2          | <ul> <li>SSP2IF: Synchronous Serial Port (MSSP2) Interrupt Flag bit</li> <li>1 = The Transmission/Reception/Bus Condition is complete (must be cleared in software)</li> </ul> |                                      |                |                                                       |                                     |                 |               |  |  |

|                |                                                                                                                                                                                | or the Transmi                       |                |                                                       |                                     | eared in softwa | are)          |  |  |

| bit 1          | BCL1IF: MSSP1 Bus Collision Interrupt Flag bit                                                                                                                                 |                                      |                |                                                       |                                     |                 |               |  |  |

|                |                                                                                                                                                                                | llision was dete<br>collision was de | •              | cleared in sof                                        | tware)                              |                 |               |  |  |

| bit 0          | SSP1IF: Syn                                                                                                                                                                    | chronous Seria                       | I Port (MSSP1  | I) Interrupt Fla                                      | g bit                               |                 |               |  |  |

|                |                                                                                                                                                                                |                                      |                |                                                       | lete (must be cl                    | eared in softwa | are)          |  |  |

|                | 0 = Waiting f                                                                                                                                                                  | or the Transmi                       | ssion/Receptic | on/Bus Conditi                                        | on in progress                      |                 |               |  |  |

|                | The RCxIF flag is times to remove al                                                                                                                                           |                                      |                |                                                       | firmware must                       | read from RCx   | REG enough    |  |  |

|                | The TXxIF flag is a                                                                                                                                                            |                                      |                |                                                       |                                     |                 |               |  |  |

|                | the firmware must<br>TXxIF flag does no                                                                                                                                        | •                                    |                | •                                                     | •                                   | •               | ouffer. The   |  |  |

|                |                                                                                                                                                                                |                                      |                |                                                       |                                     |                 |               |  |  |

|                |                                                                                                                                                                                |                                      |                |                                                       |                                     |                 |               |  |  |

|                | Interrupt flag bits a                                                                                                                                                          |                                      |                |                                                       |                                     |                 |               |  |  |

|                | condition occurs, r<br>its corresponding                                                                                                                                       |                                      |                |                                                       |                                     |                 |               |  |  |

|                | Enable bit, GIE, c                                                                                                                                                             |                                      |                |                                                       |                                     |                 |               |  |  |

|                | User software                                                                                                                                                                  | should ensu                          | ure the        |                                                       |                                     |                 |               |  |  |

|                | appropriate interr                                                                                                                                                             |                                      | are clear      |                                                       |                                     |                 |               |  |  |

prior to enabling an interrupt.

© 2016 Microchip Technology Inc.

## TABLE 12-2: WDT CLEARING CONDITIONS

| Conditions                                       | WDT        |  |  |

|--------------------------------------------------|------------|--|--|

| WDTE<1:0> = 00                                   |            |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                    |            |  |  |

| WDTE<1:0> = 10 and enter Sleep                   | Cleared    |  |  |

| CLRWDT Command                                   | Cleared    |  |  |

| Oscillator Fail Detected                         |            |  |  |

| Exit Sleep + System Clock = SOSC, EXTOSC, INTOSC |            |  |  |

| Change INTOSC divider (IRCF bits)                | Unaffected |  |  |

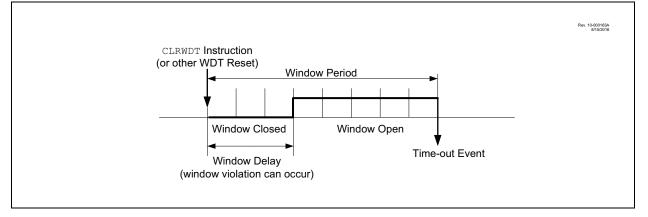

# FIGURE 12-2: WINDOW PERIOD AND DELAY

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRB<7:0>:** PORTB Slew Rate Enable bits For RB<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

### REGISTER 14-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLB<7:0>: PORTB Input Level Select bits For RB<7:0> pins, respectively

$\ensuremath{\mathtt{1}}$  = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

### TABLE 14-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTB   | RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     | 206                 |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  | 206                 |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   | 207                 |

| ANSELB  | ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 207                 |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 208                 |

| ODCONB  | ODCB7   | ODCB6   | ODCB5   | ODCB4   | ODCB3   | ODCB2   | ODCB1   | ODCB0   | 208                 |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 209                 |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 209                 |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

© 2016 Microchip Technology Inc.

# 15.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- The I<sup>2</sup>C SCLx and SDAx functions can be Note: remapped through PPS. However, only the RB1, RB2, RC3 and RC4 pins have the I<sup>2</sup>C and SMBus specific input buffers implemented (I<sup>2</sup>C mode disables INLVL and sets thresholds that are specific for  $I^2C$ ). If the SCLx or SDAx functions are mapped to some other pin (other than RB1, RB2, RC3 or RC4), the general purpose TTL or ST input buffers (as configured based on INLVL register setting) will be used instead. In most applications, it is therefore recommended only to map the SCLx and SDAx pin functions to the RB1, RB2, RC3 or RC4 pins.

# 15.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 15-1.

### EXAMPLE 15-1: PPS LOCK/UNLOCK SEQUENCE

| ; | suspend interrupts                     |

|---|----------------------------------------|

|   | BCF INTCON, GIE                        |

| ; | BANKSEL PPSLOCK ; set bank             |

| ; | required sequence, next 5 instructions |

|   | MOVLW 0x55                             |

|   | MOVWF PPSLOCK                          |

|   | MOVLW 0xAA                             |

|   | MOVWF PPSLOCK                          |

| ; | Set PPSLOCKED bit to disable writes or |

| ; | Clear PPSLOCKED bit to enable writes   |

|   | BSF PPSLOCK, PPSLOCKED                 |

| ; | restore interrupts                     |

|   | BSF INTCON, GIE                        |

# 15.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

# 15.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

# 15.7 Effects of a Reset

A device Power-on-Reset (POR) clears all PPS input and output selections to their default values (Permanent Lock Removed). All other Resets leave the selections unchanged. Default input selections are shown in Table 15-1 through Table 15-3.

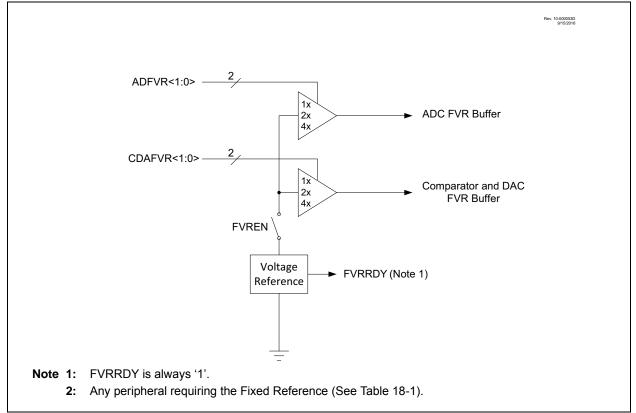

# 18.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · ADC positive reference

- · Comparator positive and negative input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

## 18.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 20.0 "Analog-to-Digital Converter (ADC) Module"** for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" and Section 23.0 "Comparator Module" for additional information.

# 18.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize.

FVRRDY is an indicator of the reference being ready. In the case of an LF device, or a device on which the BOR is enabled in the Configuration Word settings, then the FVRRDY bit will be high prior to setting FVREN as those module require the reference voltage.

FIGURE 18-1: VOLTAGE REFERENCE BLOCK DIAGRAM

# 24.7 Operation During Sleep

The ZCD current sources and interrupts are unaffected by Sleep.

# 24.8 Effects of a Reset

The ZCD circuit can be configured to default to the active or inactive state on Power-on-Reset (POR). When the ZCDDIS Configuration bit is cleared, the ZCD circuit will be active at POR. When the ZCD Configuration bit is set, the EN bit of the ZCDxCON register must be set to enable the ZCD module.

#### 29.1.1 PWM CLOCK SELECTION

The PIC16(L)F15356/75/76/85/86 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

#### 29.1.2 USING THE TMR2 WITH THE PWM MODULE

This device has a newer version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than on older parts. Refer to Section 27.5 "Operation Examples" for examples of PWM signal generation using the different modes of Timer2.

| Note: | PWM operation requires that the timer |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|

|       | used as the PWM time base has the     |  |  |  |  |

|       | FOSC/4 clock source selected.         |  |  |  |  |

#### 29.1.3 **PWM PERIOD**

Referring to Figure 29-1, the PWM output has a period and a pulse width. The frequency of the PWM is the inverse of the period (1/period).

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### EQUATION 29-1: **PWM PERIOD**

$$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC$$

$$\cdot (TMR2 Prescale Value)$$

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWMx pin is set (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM pulse width is latched from PWMxDC.

| Note: | If the p          | ulse v | width value | is grea | ter than | the  |

|-------|-------------------|--------|-------------|---------|----------|------|

|       | period            | the    | assigned    | PWM     | pin(s)   | will |

|       | remain unchanged. |        |             |         |          |      |

#### 29.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDC register. The PWMxDCH contains the eight MSbs and the PWMxDCL<7:6> bits contain the two LSbs.

The PWMDC register is double-buffered and can be updated at any time. This double buffering is essential for glitch-free PWM operation. New values take effect when TMR2 = PR2. Note that PWMDC is left-justified.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

Equation 29-2 is used to calculate the PWM pulse width.

Equation 29-3 is used to calculate the PWM duty cycle ratio.

### EQUATION 29-2: PULSE WIDTH

$Pulse Width = (PWMxDC) \cdot TOSC \cdot$ (TMR2 Prescale Value)

#### EQUATION 29-3: DUTY CYCLE RATIO

(PWMxDC) Duty Cycle Ratio =

```

4(PR2 + 1)

```

#### 29.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 29-4.

#### EQUATION 29-4: **PWM RESOLUTION**

Resolution =

$$\frac{\log[4(PR2+1)]}{\log(2)}$$

bits

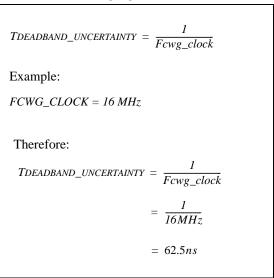

#### 30.8 **Dead-Band Uncertainty**

When the rising and falling edges of the input source are asynchronous to the CWG clock, it creates uncertainty in the dead-band time delay. The maximum uncertainty is equal to one CWG clock period. Refer to Equation 30-1 for more details.

#### EQUATION 30-1: **DEAD-BAND** UNCERTAINTY

# MODE0 CWG1A CWG1B CWG1C CWG1D No delay CWG1DBR 🕂 No delay CWG1DBF CWG1\_data Note 1: WGPOL{ABCD} = 0 2: The direction bit MODE<0> (Register 30-1) can be written any time during the PWM cycle, and takes effect at the next rising CWG1 data. 3: When changing directions, CWG1A and CWG1C switch at rising CWG1\_data; modulated CWG1B and CWG1D are held inactive for the dead band duration shown; dead band affects only the first pulse after the direction change.

#### **FIGURE 30-8: EXAMPLE OF PWM DIRECTION CHANGE**

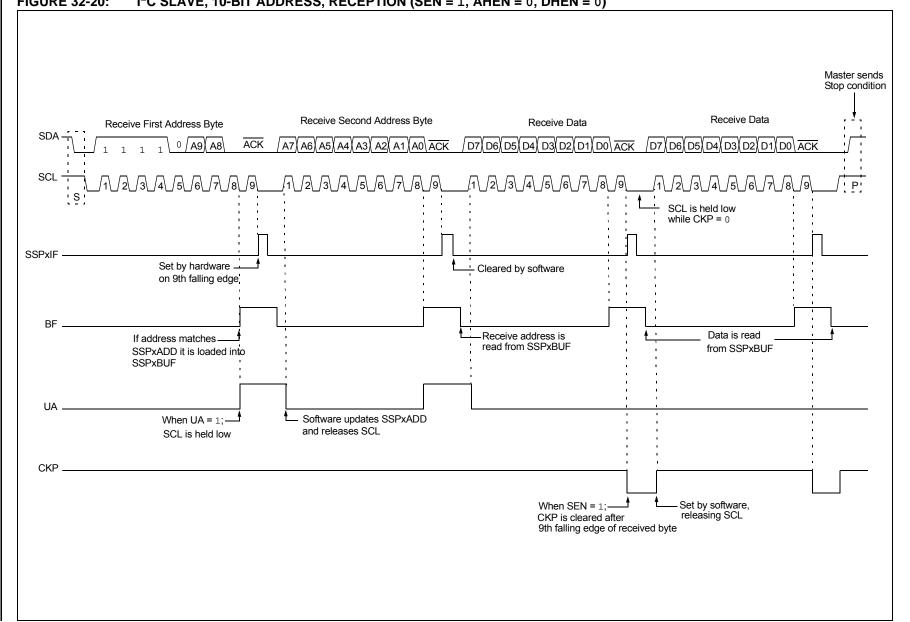

#### I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 0, DHEN = 0) **FIGURE 32-20:**

### 32.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

# 32.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 32.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

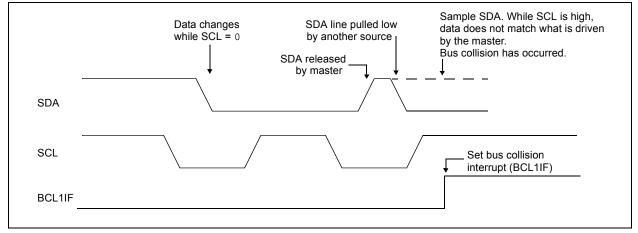

### 32.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF and reset the I<sup>2</sup>C port to its Idle state (Figure 32-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

### FIGURE 32-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

# 33.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 33-3 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

### 33.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 33-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

### 33.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

### 33.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

### 33.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 33.4.1.2 "Clock Polarity"**.

### 33.1.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE3 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

© 2016 Microchip Technology Inc.

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

Bit Test f, Skip if Set

instruction is executed.

If bit 'b' in register 'f' is '0', the next

If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2-cycle

$0 \le f \le 127$  $0 \le b < 7$ skip if (f<b>) = 1

instruction.

None

| BRA              | Relative Branch                                                    | BTFSS            |

|------------------|--------------------------------------------------------------------|------------------|

| Syntax:          | [ label ] BRA label                                                | Syntax:          |

|                  | [ <i>label</i> ] BRA \$+k                                          | Operands:        |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255                                        |                  |

|                  | $-256 \le k \le 255$                                               | Operation:       |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                      | Status Affected: |

| Status Affected: | None                                                               | Description:     |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have |                  |

|                  | incremented to fetch the next                                      |                  |

|                  | instruction, the new address will be                               |                  |

|                  | PC + 1 + k. This instruction is a                                  |                  |

|                  | 2-cycle instruction. This branch has a                             |                  |

|                  | limited range.                                                     |                  |

### BRW Relative Branch with W

| Syntax:          | [ <i>label</i> ] BRW                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                          |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

## **37.4** AC Characteristics