#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15376-e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

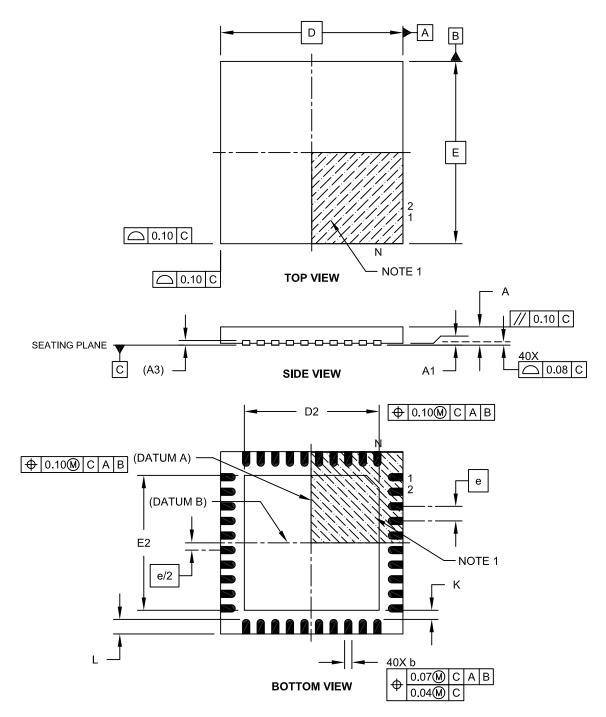

## 1.0 DEVICE OVERVIEW

The PIC16(L)F15356/75/76/85/86 are described within this data sheet. The PIC16(L)F15356/75/76/85/86 devices are available in 28/40/44/48-pin SPDIP, SSOP, SOIC, TQFP, QFN and UQFN packages. Figure 1-1 through Figure 1-3 shows the block diagrams of the PIC16(L)F15356/75/76/85/86 devices. Table 1-2 through Table 1-4 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| SUMMARY                                                                          |                |                            |

|----------------------------------------------------------------------------------|----------------|----------------------------|

| Peripheral                                                                       |                | PIC16(L)F15356/75/76/85/86 |

| Analog-to-Digital Converter                                                      |                | •                          |

| Digital-to-Analog Converter (DAC1)                                               |                | •                          |

| Fixed Voltage Reference (FVR)                                                    |                | ٠                          |

| Enhanced Universal Synchronous/Asynchronous<br>Transmitter (EUSART1 and EUSART2) | Receiver/      | •                          |

| Numerically Controlled Oscillator (NCO1)                                         |                | ٠                          |

| Temperature Indicator Module (TIM)                                               |                | ٠                          |

| Zero-Cross Detect (ZCD1)                                                         |                | •                          |

| Capture/Compare/PWM Modules (CCP)                                                |                |                            |

|                                                                                  | CCP1           | ٠                          |

|                                                                                  | CCP2           | ٠                          |

| Comparator Module (Cx)                                                           |                |                            |

|                                                                                  | C1             | ٠                          |

|                                                                                  | C2             | ٠                          |

| Configurable Logic Cell (CLC)                                                    |                |                            |

| -                                                                                | CLC1           | ٠                          |

| -                                                                                | CLC2           | ٠                          |

| -                                                                                | CLC3           | ٠                          |

|                                                                                  | CLC4           | •                          |

| Complementary Waveform Generator (CWG)                                           | CW/C1          | _                          |

| Master Synahranaua Sarial Parta (MSSP)                                           | CWG1           | ٠                          |

| Master Synchronous Serial Ports (MSSP)                                           | MSSP1          | -                          |

|                                                                                  | MSSP1<br>MSSP2 | •                          |

| Pulse-Width Modulator (PWM)                                                      | 111001 Z       | -                          |

|                                                                                  | PWM3           | •                          |

| -                                                                                | PWM4           | •                          |

|                                                                                  | PWM5           | •                          |

|                                                                                  | PWM6           | •                          |

| Timers                                                                           |                |                            |

|                                                                                  | Timer0         | ٠                          |

|                                                                                  | Timer1         | •                          |

|                                                                                  | Timer2         | ٠                          |

| Name                                                | Function              | Input<br>Type    | Output Type | Description                                                                                      |  |  |

|-----------------------------------------------------|-----------------------|------------------|-------------|--------------------------------------------------------------------------------------------------|--|--|

| RD1/AND1/SDA2 <sup>(1)</sup> /SDI2 <sup>(1,4)</sup> | RD1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND1                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

|                                                     | SDA2 <sup>(1)</sup>   | l <sup>2</sup> C | OD          | MSSP2 I <sup>2</sup> C serial data input/output.                                                 |  |  |

|                                                     | SDI2 <sup>(1,4)</sup> | TTL/ST           | _           | MSSP2 SPI serial data input (default input location, SDI2 is a PPS remappable input and output). |  |  |

| RD2/AND2                                            | RD2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND2                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD3/AND3                                            | RD3                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND3                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD4/AND4                                            | RD4                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND4                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD5/AND5                                            | RD5                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND5                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD6/AND6                                            | RD6                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND6                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RD7/AND7                                            | RD7                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | AND7                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RE0/ANE0                                            | RE0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANE0                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RE1/ANE1                                            | RE1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANE1                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RE2/ANE2                                            | RE2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANE2                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RE3/MCLR/IOCE3                                      | RE3                   | TTL/ST           | -           | General purpose input only (when $\overline{\text{MCLR}}$ is disabled by the Configuration bit). |  |  |

|                                                     | MCLR                  | ST               | _           | Master clear input with internal weak pull-up resistor.                                          |  |  |

|                                                     | IOCE3                 | TTL/ST           | _           | Interrupt-on-change input.                                                                       |  |  |

| RF0/ANF0                                            | RF0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF0                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RF1/ANF1                                            | RF1                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF1                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RF2/ANF2                                            | RF2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF2                  | AN               | —           | ADC Channel D0 input.                                                                            |  |  |

| RF3/ANF3                                            | RF3                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF3                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

| RF4/ANF4                                            | RF4                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                             |  |  |

|                                                     | ANF4                  | AN               | _           | ADC Channel D0 input.                                                                            |  |  |

#### **TABLE 1-4:** PIC16(L)F15385/86 PINOUT DESCRIPTION (CONTINUED)

HV = High Voltage

XTAL

Note

= Crystal levels This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal. 1:

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options 2: as described in Table 15-5, Table 15-6 and Table 15-7.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

#### 4.3.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains:

- the arithmetic status of the ALU

- the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

# For example, CLRF STATUS will clear bits <4:3> and <1:0>, and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, refer to **Section 36.0** "Instruction Set Summary".

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

### REGISTER 4-1: STATUS: STATUS REGISTER

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| —     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                                                                     |

|         | <ul> <li>1 = After power-up, CLRWDT instruction or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                                                                                                 |

| bit 3   | PD: Power-Down bit                                                                                                                                                                                                   |

|         | 1 = After power-up or by the CLRWDT instruction                                                                                                                                                                      |

|         | 0 = By execution of the SLEEP instruction                                                                                                                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | 1 = The result of an arithmetic or logic operation is zero                                                                                                                                                           |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                       |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                                                                                                                    |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                                                                                                                            |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                          |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                                                                                 |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

| IADLE 4          | ABLE 4-11. SPECIAL FUNCTION REGISTER SUMMART BANKS 0-03 (CONTINUED) |                       |                           |        |       |       |       |         |        |                       |                            |  |  |  |

|------------------|---------------------------------------------------------------------|-----------------------|---------------------------|--------|-------|-------|-------|---------|--------|-----------------------|----------------------------|--|--|--|

| Address          | Name                                                                | Bit 7                 | Bit 6                     | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |  |

| Bank 1           | nk 1                                                                |                       |                           |        |       |       |       |         |        |                       |                            |  |  |  |

|                  | CPU CORE REGISTERS; see Table 4-3 for specifics                     |                       |                           |        |       |       |       |         |        |                       |                            |  |  |  |

| 08Ch<br><br>09Ah | - Unimplemented                                                     |                       |                           |        |       |       |       |         |        |                       | -                          |  |  |  |

| 09Bh             | ADRESL                                                              | ADC Result Register L | _OW                       |        |       |       |       |         |        | xxxx xxxx             | uuuu uuuu                  |  |  |  |

| 09Ch             | ADRESH                                                              | ADC Result Register H | High                      |        |       |       |       |         |        | xxxx xxxx             | uuuu uuuu                  |  |  |  |

| 09Dh             | ADCON0                                                              |                       |                           | CHS<5: | 0>    |       |       | GO/DONE | ADON   | 0000 0000             | 0000 0000                  |  |  |  |

| 09Eh             | ADCON1                                                              | ADFM                  | ADCS<2:0> — — ADPREF<1:0> |        |       |       |       |         | 000000 | 000000                |                            |  |  |  |

| 09Fh             | ADACT                                                               | —                     | _                         | —      | _     |       | ADA   | CT<3:0> |        | 0000                  | 0000                       |  |  |  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address | Name | Bit 7  | Bit 6  | Bit 5   | Bit 4         | Bit 3             | Bit 2       | Bit 1  | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|------|--------|--------|---------|---------------|-------------------|-------------|--------|---------|-----------------------|----------------------------|

| Bank 14 |      |        | 1      |         |               |                   |             |        |         |                       |                            |

|         |      |        |        | CPU COP | RE REGISTERS; | see Table 4-3 for | r specifics |        |         |                       |                            |

| 70Ch    | PIR0 | _      | —      | TMR0IF  | IOCIF         | —                 | _           | —      | INTF    | 000                   | 000                        |

| 70Dh    | PIR1 | OSFIF  | CSWIF  | —       | -             | _                 | -           | —      | ADIF    | 0000                  | 0000                       |

| 70Eh    | PIR2 | _      | ZCDIF  | _       | -             | _                 | _           | C2IF   | C1IF    | -000                  | -000                       |

| 70Fh    | PIR3 | RC2IF  | TX2IF  | RC1IF   | TX1IF         | BCL2IF            | SSP2IF      | BCL1IF | SSP1IF  | 0000 0000             | 0000 0000                  |

| 710h    | PIR4 | _      | _      | _       | _             | _                 | _           | TMR2IF | TMR1IF  | 00                    | 00                         |

| 711h    | PIR5 | CLC4IF | CLC3IF | CLC2IF  | CLC1IF        | _                 | _           | _      | TMR1GIF | 00000                 | 00000                      |

| 712h    | PIR6 | _      | _      | _       | _             | _                 | _           | CCP2IF | CCP1IF  | 00                    | 00                         |

| 713h    | PIR7 | _      | _      | NVMIF   | NCO1IF        | _                 | _           | _      | CWG1IF  | 000                   | 000                        |

| 714h    | _    |        |        | •       | Unimple       | mented            |             |        |         | _                     | _                          |

| 715h    | _    |        |        |         | Unimple       | mented            |             |        |         | _                     | _                          |

| 716h    | PIE0 | —      | —      | TMR0IE  | IOCIE         | —                 | —           | —      | INTE    | 000                   | 000                        |

| 717h    | PIE1 | OSFIE  | CSWIE  | _       | _             | _                 | _           | _      | ADIE    | 0000                  | 0000                       |

| 718h    | PIE2 | _      | ZCDIE  | —       | -             | _                 | -           | C2IE   | C1IE    | -000                  | -000                       |

| 719h    | PIE3 | RC2IE  | TX2IE  | RC1IE   | TX1IE         | BCL2IE            | SSP2IE      | BCL1IE | SSP1IE  | 0000 0000             | 0000 000                   |

| 71Ah    | PIE4 | _      | _      | _       | _             | _                 | —           | TMR2IE | TMR1IE  | 00                    | 0                          |

| 71Bh    | PIE5 | CLC4IE | CLC3IE | CLC2IE  | CLC1IE        | _                 | _           |        | TMR1GIE | 00000                 | 0000                       |

| 71Ch    | PIE6 | _      | _      | —       | _             | _                 | _           | CCP2IE | CCP1IE  | 00                    | 0                          |

| 71Dh    | PIE7 |        | —      | NVMIE   | NCO1IE        | _                 | —           | —      | CWG1IE  | 000                   | 00                         |

| 71Eh    | —    |        |        |         | Unimple       | mented            |             |        |         | —                     | _                          |

| 71Fh    | _    |        |        |         | Unimple       | mented            |             |        |         | _                     | _                          |

### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

# PIC16(L)F15356/75/76/85/86

**REGISTER 5-2:**

#### **CONFIGURATION WORD 2: SUPERVISORS**

| REGISTER                | 5-2:                                                                                                | CONFIGUR                                                                     | ATION WOR                                                                        | D 2: SUPER                           | VISORS                                 |                                |                     |

|-------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|--------------------------------|---------------------|

|                         |                                                                                                     | R/P-1                                                                        | R/P-1                                                                            | R/P-1                                | R/P-1                                  | R/P-1                          | U-1                 |

|                         |                                                                                                     | DEBUG                                                                        | STVREN                                                                           | PPS1WAY                              | ZCDDIS                                 | BORV                           |                     |

|                         |                                                                                                     | bit 13                                                                       |                                                                                  |                                      |                                        |                                | bit 8               |

| <b></b>                 |                                                                                                     |                                                                              |                                                                                  |                                      |                                        |                                |                     |

| R/P-1                   | R/P-1                                                                                               | R/P-1                                                                        | U-1                                                                              | U-1                                  | U-1                                    | R/P-1                          | R/P-1               |

| BOREN1                  | BOREN0                                                                                              | LPBOREN                                                                      | —                                                                                |                                      |                                        | PWRTE                          | MCLRE               |

| bit 7                   |                                                                                                     |                                                                              |                                                                                  |                                      |                                        |                                | bit 0               |

| Lonondi                 |                                                                                                     |                                                                              |                                                                                  |                                      |                                        |                                |                     |

| Legend:<br>R = Readable | a bit                                                                                               | P = Programma                                                                | ahle hit                                                                         | x = Bit is unkno                     |                                        | U = Unimpleme                  | nted hit read as    |

|                         | , Dit                                                                                               | i – i logramma                                                               |                                                                                  |                                      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | '1'                            | ited bit, read as   |

| '0' = Bit is cle        | ared                                                                                                | '1' = Bit is set                                                             |                                                                                  | W = Writable bi                      | t                                      | n = Value when l<br>Erase      | olank or after Bulk |

| bit 13                  | 1 = Backgrour                                                                                       | ugger Enable bit<br>nd debugger disa<br>nd debugger ena                      |                                                                                  |                                      |                                        |                                |                     |

| bit 12                  | 1 = Stack Ove                                                                                       | ck Overflow/Unde<br>erflow or Underflo<br>erflow or Underflo                 | w will cause a F                                                                 | Reset                                |                                        |                                |                     |

| bit 11                  | 1 = The PPSL                                                                                        |                                                                              | cleared and set                                                                  | only once; PPS i                     | egisters remain l                      | ocked after one c<br>sequence) | lear/set cycle      |

| bit 10                  | 1 = ZCD disab                                                                                       | -Cross Detect Di<br>bled. ZCD can be<br>ys enabled (ZCD                      | enabled by sett                                                                  |                                      | I bit of the ZCDC                      | ON register                    |                     |

| bit 9                   | 1 = Brown-out                                                                                       | -out Reset Voltag<br>t Reset voltage (\<br>t Reset voltage (\                | /BOR) set to low                                                                 | er trip point leve                   |                                        |                                |                     |

| bit 8                   | Unimplement                                                                                         | ed: Read as '1'                                                              |                                                                                  |                                      |                                        |                                |                     |

| bit 7-6                 | When enabled<br>11 = Brown-o<br>10 = Brown-o<br>01 = Brown-o<br>00 = Brown-o                        | out Reset is enab<br>out Reset is disat                                      | et Voltage (VBO<br>led; SBOREN b<br>led while runnir<br>led according to<br>oled | oit is ignored<br>ng, disabled in SI | ORV bit<br>eep; SBOREN bi              | t is ignored                   |                     |

| bit 5                   | 1 = ULPBOR<br>0 = ULPBOR                                                                            |                                                                              | nable bit                                                                        |                                      |                                        |                                |                     |

| bit 4-2                 | Unimplement                                                                                         | ed: Read as '1'                                                              |                                                                                  |                                      |                                        |                                |                     |

| bit 1                   | <b>PWRTE</b> : Powe<br>1 = PWRT is 0<br>0 = PWRT is 6                                               |                                                                              | le bit                                                                           |                                      |                                        |                                |                     |

| bit 0                   | $\frac{\text{If LVP} = 1}{\text{RE3 pin function}}$ $\frac{\text{If LVP} = 0}{1 = \text{MCLR pin}}$ | er Clear (MCLR)<br>on is MCLR (it wi<br>is MCLR (it will r<br>may be used as | Il reset the device                                                              | when driven low                      | ,                                      |                                |                     |

|                         | see <u>Vbor pa</u> rame                                                                             | eter for specific tri                                                        | p point voltages                                                                 | s.                                   | by device develo                       | pment tools includ             | lina debuaaers      |

2: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

## 12.0 WINDOWED WATCHDOG TIMER (WWDT)

The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WDT has the following features:

- Selectable clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Configurable window size from 12.5 to 100 percent of the time-out period

- Multiple Reset conditions

- Operation during Sleep

#### 13.4 Register Definitions: Flash Program Memory Control

#### REGISTER 13-1: NVMDATL: NONVOLATILE MEMORY DATA LOW BYTE REGISTER

| R/W-x/u                                                            | R/W-x/u | R/W-x/u              | R/W-x/u                                                | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|--------------------------------------------------------------------|---------|----------------------|--------------------------------------------------------|---------|---------|---------|---------|

|                                                                    |         |                      | NVMD                                                   | AT<7:0> |         |         |         |

| bit 7                                                              |         |                      |                                                        |         |         |         | bit 0   |

|                                                                    |         |                      |                                                        |         |         |         |         |

| Legend:                                                            |         |                      |                                                        |         |         |         |         |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |         |                      |                                                        |         |         |         |         |

| u = Bit is unchan                                                  | ged     | x = Bit is unknow    | n -n/n = Value at POR and BOR/Value at all other Reser |         |         |         |         |

| '1' = Bit is set                                                   |         | '0' = Bit is cleared | 1                                                      |         |         |         |         |

bit 7-0 NVMDAT<7:0>: Read/write value for Least Significant bits of program memory

#### REGISTER 13-2: NVMDATH: NONVOLATILE MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u      | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|-------|-----|---------|--------------|---------|---------|---------|---------|--|--|--|

| —     | _   |         | NVMDAT<13:8> |         |         |         |         |  |  |  |

| bit 7 |     |         |              |         |         |         | bit 0   |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 NVMDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 13-3: NVMADRL: NONVOLATILE MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0     | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--|

| NVMADR<7:0> |             |         |         |         |         |         |         |  |

| bit 7       | bit 7 bit 0 |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NVMADR<7:0>: Specifies the Least Significant bits for program memory address

#### REGISTER 13-4: NVMADRH: NONVOLATILE MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | NVMADR<14:8 | }>      |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 NVMADR<14:8>: Specifies the Most Significant bits for program memory address

**Note 1:** Bit is undefined while WR = 1

| R/W-x/u              | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-1/1                                              | R/W-x/u | R/W-x/u | R/W-x/u     |

|----------------------|---------|--------------------|---------|------------------------------------------------------|---------|---------|-------------|

| LATA7                | LATA6   | LATA5              | LATA4   | LATA3                                                | LATA2   | LATA1   | LATA0       |

| bit 7                |         |                    | •       |                                                      |         | •       | bit 0       |

|                      |         |                    |         |                                                      |         |         |             |

| Legend:              |         |                    |         |                                                      |         |         |             |

| R = Readable         | bit     | W = Writable       | bit     | U = Unimplemented bit, read as '0'                   |         |         |             |

| u = Bit is unchanged |         | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Reset |         |         | thar Pacata |

#### REGISTER 14-3: LATA: PORTA DATA LATCH REGISTER

#### bit 7-0 LATA<7:0>: RA<7:0> Output Latch Value bits<sup>(1)</sup>

'1' = Bit is set

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register returns actual I/O pin values.

#### REGISTER 14-4: ANSELA: PORTA ANALOG SELECT REGISTER

'0' = Bit is cleared

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSA7   | ANSA6   | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSA<7:0>: Analog Select between Analog or Digital Function on pins RA<7:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# PIC16(L)F15356/75/76/85/86

## **REGISTER 14-35: LATE: PORTE DATA LATCH REGISTER<sup>(1)</sup>**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | _   | —   | —   | LATE2   | LATE1   | LATE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

|       |     |     |     |     |         |         |         |

## Legend:

bit 2-0

| •                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits

#### **Note 1:** Present on PIC16(L)F15375/76/85/86 only.

2: Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of actual I/O pin values.

### REGISTER 14-36: ANSELE: PORTE ANALOG SELECT REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | _   | _   | _   | _   | ANSE2   | ANSE1   | ANSE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-3 Unimplemented: Read as '0'

**ANSE<2:0>**: Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively<sup>(2)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(2)</sup>. Digital input buffer disabled.

Note 1: Present on PIC16(L)F15375/76/85/86 only.

**2:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTF   | RF7     | RF6     | RF5     | RF4     | RF3     | RF2     | RF1     | RF0     | 216                 |

| TRISF   | TRISF7  | TRISF6  | TRISF5  | TRISF4  | TRISF3  | TRISF2  | TRISF1  | TRISF0  | 216                 |

| LATF    | LATF7   | LATF6   | LATF5   | LATF4   | LATF3   | LATF2   | LATF1   | LATF0   | 216                 |

| ANSELF  | ANSF7   | ANSF6   | ANSF5   | ANSF4   | ANSF3   | ANSF2   | ANSF1   | ANSF0   | 217                 |

| WPUF    | WPUF7   | WPUF6   | WPUF5   | WPUF4   | WPUF3   | WPUF2   | WPUF1   | WPUF0   | 217                 |

| ODCONF  | ODCF7   | ODCF6   | ODCF5   | ODCF4   | ODCF3   | ODCF2   | ODCF1   | ODCF0   | 218                 |

| SLRCONF | SLRF7   | SLRF6   | SLRF5   | SLRF4   | SLRF3   | SLRF2   | SLRF1   | SLRF0   | 218                 |

| INLVLF  | INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4 | INLVLF3 | INLVLF2 | INLVLF1 | INLVLF0 | 218                 |

#### TABLE 14-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

Legend: - = unimplemented locations read as '0'. Shaded cells are not used by PORTF.

## 20.3 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 20-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 20-4. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 20-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 20-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$TC = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 2\mu s + 1.37 + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

**Note 1:** The VAPPLIED has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

© 2016 Microchip Technology Inc.

| Name     | Bit 7                                        | Bit 6         | Bit 5                | Bit 4     | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|----------|----------------------------------------------|---------------|----------------------|-----------|-------|-------|--------|--------|---------------------|

| CCP1CON  | EN                                           | _             | OUT                  | FMT       |       | MODE  | =<3:0> |        | 366                 |

| CCP2CON  | EN                                           | _             | OUT                  | FMT       |       | MODE  | <3:0>  |        | 366                 |

| INTCON   | GIE                                          | PEIE          | _                    | _         | —     | —     | —      | INTEDG | 146                 |

| PIE1     | OSFIE                                        | CSWIE         | _                    | _         | —     | —     | _      | ADIE   | 148                 |

| PIR1     | OSFIF                                        | CSWIF         | _                    | _         | —     | _     | _      | ADIF   | 156                 |

| PR2      | Timer2 Module Period Register                |               |                      |           |       |       |        |        |                     |

| TMR2     | Holding Register for the 8-bit TMR2 Register |               |                      |           |       |       |        |        |                     |

| T2CON    | ON                                           |               | CKPS<2:0> OUTPS<3:0> |           |       |       |        |        | 355                 |

| T2CLKCON | _                                            | — — — CS<3:0> |                      |           |       | 354   |        |        |                     |

| T2RST    | —                                            |               | — — RSEL<3:0>        |           |       |       | 357    |        |                     |

| T2HLT    | PSYNC                                        | CKPOL         | CKSYNC               | MODE<4:0> |       |       |        |        | 356                 |

### TABLE 27-2: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

| R/W-x/u          | R/W-x/u                                                                                                                  | R/W-x/u                                                                                                                          | R/W-x/u         | R/W-x/u                                               | R/W-x/u  | R/W-x/u  | R/W-x/u  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------|----------|----------|----------|--|--|--|

| LCxG4D4T         | LCxG4D4N                                                                                                                 | LCxG4D3T                                                                                                                         | LCxG4D3N        | LCxG4D2T                                              | LCxG4D2N | LCxG4D1T | LCxG4D1N |  |  |  |

| bit 7            | ·                                                                                                                        |                                                                                                                                  |                 |                                                       |          |          | bit 0    |  |  |  |

|                  |                                                                                                                          |                                                                                                                                  |                 |                                                       |          |          |          |  |  |  |

| Legend:          |                                                                                                                          |                                                                                                                                  |                 |                                                       |          |          |          |  |  |  |

| R = Readable     |                                                                                                                          | W = Writable                                                                                                                     |                 | U = Unimplemented bit, read as '0'                    |          |          |          |  |  |  |

| u = Bit is unch  | anged                                                                                                                    | x = Bit is unki                                                                                                                  |                 | -n/n = Value at POR and BOR/Value at all other Resets |          |          |          |  |  |  |

| '1' = Bit is set |                                                                                                                          | '0' = Bit is cle                                                                                                                 | ared            |                                                       |          |          |          |  |  |  |

| hit 7            |                                                                                                                          | Cata 2 Data 4 1                                                                                                                  | Frue (nen inve  | rtad) bit                                             |          |          |          |  |  |  |

| bit 7            |                                                                                                                          | Gate 3 Data 4 1<br>(true) is gated i                                                                                             | •               | ,                                                     |          |          |          |  |  |  |

|                  |                                                                                                                          | (true) is gated<br>(true) is not ga                                                                                              |                 |                                                       |          |          |          |  |  |  |

| bit 6            |                                                                                                                          | Gate 3 Data 4                                                                                                                    |                 |                                                       |          |          |          |  |  |  |

|                  |                                                                                                                          | (inverted) is ga                                                                                                                 | •               | ,                                                     |          |          |          |  |  |  |

|                  |                                                                                                                          | (inverted) is no                                                                                                                 |                 |                                                       |          |          |          |  |  |  |

| bit 5            | LCxG4D3T: (                                                                                                              | Gate 3 Data 3                                                                                                                    | True (non-inve  | rted) bit                                             |          |          |          |  |  |  |

|                  | 1 = CLCIN2 (true) is gated into CLCx Gate 3                                                                              |                                                                                                                                  |                 |                                                       |          |          |          |  |  |  |

|                  | 0 = CLCIN2                                                                                                               | (true) is not ga                                                                                                                 | ted into CLCx   | Gate 3                                                |          |          |          |  |  |  |

| bit 4            |                                                                                                                          | Gate 3 Data 3                                                                                                                    | •               | ,                                                     |          |          |          |  |  |  |

|                  |                                                                                                                          | <ul> <li>1 = CLCIN2 (inverted) is gated into CLCx Gate 3</li> <li>0 = CLCIN2 (inverted) is not gated into CLCx Gate 3</li> </ul> |                 |                                                       |          |          |          |  |  |  |

|                  |                                                                                                                          | ,                                                                                                                                | 0               |                                                       |          |          |          |  |  |  |

| bit 3            |                                                                                                                          | Gate 3 Data 2                                                                                                                    | ·               |                                                       |          |          |          |  |  |  |

|                  | <ul> <li>1 = CLCIN1 (true) is gated into CLCx Gate 3</li> <li>0 = CLCIN1 (true) is not gated into CLCx Gate 3</li> </ul> |                                                                                                                                  |                 |                                                       |          |          |          |  |  |  |

| bit 2            |                                                                                                                          |                                                                                                                                  |                 |                                                       |          |          |          |  |  |  |

| Dit 2            | LCxG4D2N: Gate 3 Data 2 Negated (inverted) bit<br>1 = CLCIN1 (inverted) is gated into CLCx Gate 3                        |                                                                                                                                  |                 |                                                       |          |          |          |  |  |  |

|                  | 0 = CLCIN1 (inverted) is not gated into CLCx Gate 3                                                                      |                                                                                                                                  |                 |                                                       |          |          |          |  |  |  |

| bit 1            |                                                                                                                          | Gate 4 Data 1 ∃                                                                                                                  | •               |                                                       |          |          |          |  |  |  |

|                  | 1 = CLCIN0 (true) is gated into CLCx Gate 3                                                                              |                                                                                                                                  |                 |                                                       |          |          |          |  |  |  |

|                  | 0 = CLCIN0                                                                                                               | (true) is not ga                                                                                                                 | ted into CLCx   | Gate 3                                                |          |          |          |  |  |  |

| bit 0            | LCxG4D1N:                                                                                                                | Gate 3 Data 1                                                                                                                    | Negated (inve   | rted) bit                                             |          |          |          |  |  |  |

|                  |                                                                                                                          | (inverted) is ga                                                                                                                 |                 |                                                       |          |          |          |  |  |  |

|                  | 0 = CLCIN0                                                                                                               | (inverted) is no                                                                                                                 | t gated into Cl | _Cx Gate 3                                            |          |          |          |  |  |  |

## REGISTER 31-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

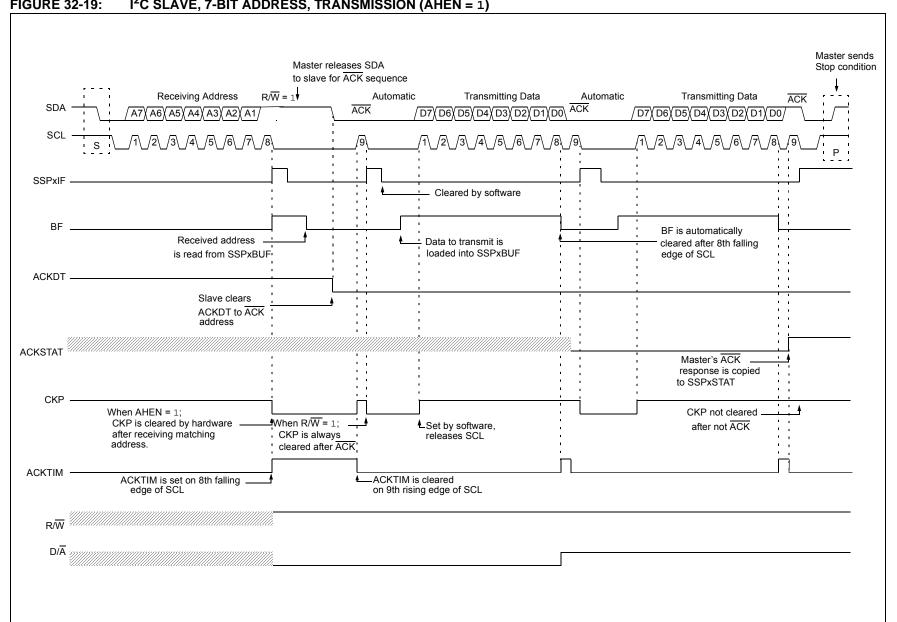

## 32.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 32.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 32-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 32-5) affects the address matching process. See **Section 32.5.9** "**SSP Mask Register**" for more information.

32.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

32.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 32.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 32-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register.

32.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 7-bit Addressing mode. Figure 32-14 and Figure 32-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDA low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes idle.

PIC16(L)F15356/75/76/85/86

#### I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, TRANSMISSION (AHEN = 1) **FIGURE 32-19:**

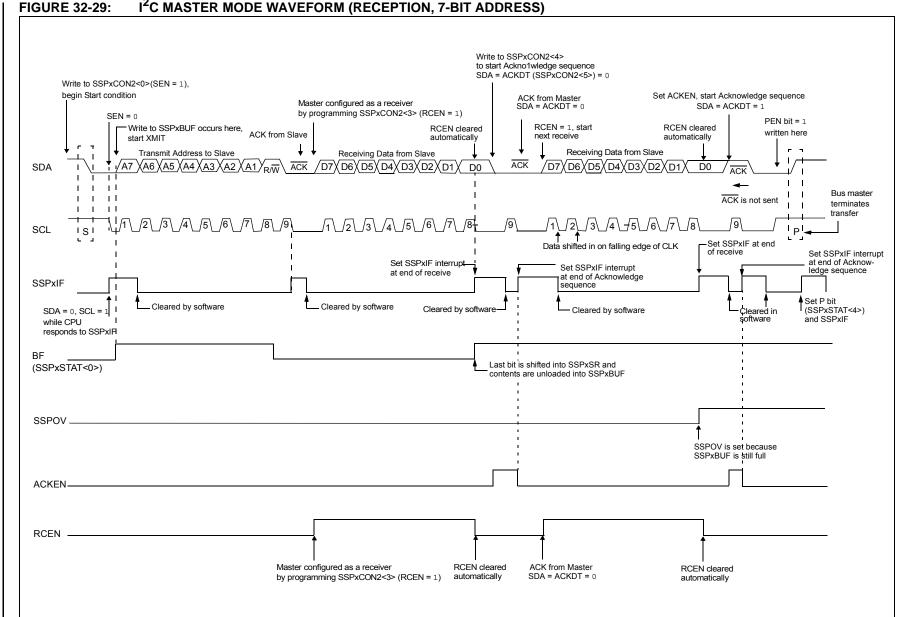

#### 32.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION