#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15376-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Н |          |

|---|----------|

|   | _        |

|   |          |

|   |          |

|   |          |

|   |          |

|   | <b>O</b> |

|   |          |

|   |          |

|   | Ŧ        |

|   |          |

|   |          |

|   |          |

|   | 35       |

|   |          |

|   | 5        |

|   |          |

|   | UT I     |

|   |          |

|   |          |

|   | 6        |

| I |          |

| I | 85/      |

| I |          |

| I | 8        |

| I | ő        |

| н |          |

Preliminary

| I/O <sup>(2)</sup> | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO | DAC | Timers              | CCP                 | MWM | SWC | ASSM                          | ZCD | EUSART                    | CLC | CLKR | Interrupt | Pull-up | Basic       |

|--------------------|------------------|------|-----------|------------|-----|-----|---------------------|---------------------|-----|-----|-------------------------------|-----|---------------------------|-----|------|-----------|---------|-------------|

| RC2                | 40               | ANC2 | —         | —          | —   | _   | —                   | CCP1 <sup>(1)</sup> | -   | —   | —                             |     | —                         | -   | —    | IOCC2     | Y       | —           |

| RC3                | 41               | ANC3 | -         | -          | -   | _   | T2IN <sup>(1)</sup> | -                   | _   | _   | SCL1<br>SCL2 <sup>(1,4)</sup> | _   | —                         | _   | -    | IOCC3     | Y       | -           |

| RC4                | 46               | ANC4 | -         | _          | _   | _   | -                   | —                   | _   | -   | SDA1<br>SDI1 <sup>(1,4)</sup> | _   | —                         | _   | _    | IOCC4     | Y       | _           |

| RC5                | 47               | ANC5 | _         | —          | _   | _   | _                   | _                   | _   | _   | _                             | _   | —                         | _   | _    | IOCC5     | Υ       | _           |

| RC6                | 48               | ANC6 | -         | —          | —   | _   | _                   | —                   | _   | —   | —                             |     | TX1<br>CK1 <sup>(1)</sup> | _   | -    | IOCC6     | Y       | —           |

| RC7                | 1                | ANC7 | -         | —          | —   | _   | —                   | —                   | _   | —   | _                             |     | RX1<br>DT1 <sup>(1)</sup> | _   | -    | IOCC7     | Y       | —           |

| RD0                | 42               | AND0 | -         | —          | -   | -   | -                   | —                   | —   | -   | SCK2<br>SCL2 <sup>(1,4)</sup> | —   | -                         | —   | -    | -         | Y       | —           |

| RD1                | 43               | AND1 | —         | —          | —   |     | —                   | —                   | _   | —   | SDA2<br>SDI2 <sup>(1,4)</sup> |     | _                         | _   | -    | —         | Y       | —           |

| RD2                | 44               | AND2 | _         | _          | —   | _   | _                   | _                   | -   | _   | _                             | _   | —                         | -   | _    | _         | Y       | _           |

| RD3                | 45               | AND3 | _         | _          | _   | _   | _                   | _                   |     | _   | _                             |     | _                         |     | —    | _         | Y       | _           |

| RD4                | 2                | AND4 | _         | _          | —   | _   | _                   | —                   | _   | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RD5                | 3                | AND5 | _         | _          | —   | _   | _                   | —                   | -   | _   | _                             | -   | _                         | -   | _    | _         | Υ       | _           |

| RD6                | 4                | AND6 | _         | _          | —   | _   | _                   | _                   | _   | —   | _                             | _   | _                         | _   | _    | —         | Υ       | _           |

| RD7                | 5                | AND7 | —         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE0                | 27               | ANE0 | -         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE1                | 28               | ANE1 | _         | —          | —   | _   | -                   | —                   |     | -   | _                             | _   | _                         |     | —    | -         | Υ       | —           |

| RE2                | 29               | ANE2 | _         | —          | —   | —   | —                   | —                   | —   | —   | —                             | _   | —                         | —   | —    | —         | Y       | —           |

| RE3                | 20               | _    | -         | —          | —   |     | —                   | —                   | _   | —   | —                             | _   | —                         | _   | _    | IOCE3     | Y       | MCLR<br>VPP |

| RF0                | 36               | ANF0 | _         | _          | —   | _   | —                   | _                   | _   | —   | _                             |     | _                         | _   | _    | —         | Y       | _           |

| RF1                | 37               | ANF1 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF2                | 38               | ANF2 | _         | —          | —   | _   | -                   | _                   | _   | —   | —                             | _   | —                         | _   | —    | —         | Υ       | _           |

| RF3                | 39               | ANF3 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF4                | 12               | ANF4 | —         | —          | —   |     | —                   | —                   |     | _   | _                             |     | _                         |     | —    | —         | Υ       | —           |

TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

|       | Bank 60                |       | Bank 61    |       | Bank 62                |       | Bank 63     |

|-------|------------------------|-------|------------|-------|------------------------|-------|-------------|

| 1E3Fh | RE7PPS <sup>(2)</sup>  | 1EBFh | _          | 1F3Fh | IOCAF                  | 1FBFh | _           |

| 1E40h | _                      | 1EC0h | _          | 1F40h | _                      | 1FC0h | _           |

| 1E41h | _                      | 1EC1h | _          | 1F41h | _                      | 1FC1h | _           |

| 1E42h |                        | 1EC2h | _          | 1F42h | _                      | 1FC2h | _           |

| 1E43h |                        | 1EC3h | ADACTPPS   | 1F43h | ANSELB                 | 1FC3h | _           |

| 1E44h | _                      | 1EC4h | _          | 1F44h | WPUB                   | 1FC4h | _           |

| 1E45h | —                      | 1EC5h | SSP1CLKPPS | 1F45h | ODCONB                 | 1FC5h | _           |

| 1E46h | —                      | 1EC6h | SSP1DATPPS | 1F46h | SLRCONB                | 1FC6h | —           |

| 1E47h |                        | 1EC7h | SSP1SSPPS  | 1F47h | INLVLB                 | 1FC7h | —           |

| 1E48h | —                      | 1EC8h | SSP2CLKPPS | 1F48h | IOCBP                  | 1FC8h | —           |

| 1E49h | —                      | 1EC9h | SSP2DATPPS | 1F49h | IOCBN                  | 1FC9h | —           |

| 1E4Ah | _                      | 1ECAh | SSP2SSPPS  | 1F4Ah | IOCBF                  | 1FCAh | —           |

| 1E4Bh | —                      | 1ECBh | RXDT1PPS   | 1F4Bh | _                      | 1FCBh | —           |

| 1E4Ch | —                      | 1ECCh | TXCK1PPS   | 1F4Ch | _                      | 1FCCh | —           |

| 1E4Dh | —                      | 1ECDh | RXD2TPPS   | 1F4Dh | _                      | 1FCDh | —           |

| 1E4Eh | —                      | 1ECEh | TXCK2PPS   | 1F4Eh | ANSELC                 | 1FCEh | —           |

| 1E4Fh | —                      | 1ECFh | _          | 1F4Fh | WPUC                   | 1FCFh | _           |

| 1E50h | ANSELF <sup>(2)</sup>  | 1ED0h | —          | 1F50h | ODCONC                 | 1FD0h | —           |

| 1E51h | WPUF <sup>(2)</sup>    | 1ED1h | _          | 1F51h | SLRCONC                | 1FD1h | _           |

| 1E52h | ODCONF <sup>(2)</sup>  | 1ED2h | _          | 1F52h | INLVLC                 | 1FD2h | _           |

| 1E53h | SLRCONF <sup>(2)</sup> | 1ED3h | _          | 1F53h | IOCCP                  | 1FD3h | _           |

| 1E54h | INLVLF <sup>(2)</sup>  | 1ED4h | _          | 1F54h | IOCCN                  | 1FD4h | _           |

| 1E55h |                        | 1ED5h | _          | 1F55h | IOCCF                  | 1FD5h | _           |

| 1E56h |                        | 1ED6h | _          | 1F56h | _                      | 1FD6h | _           |

| 1E57h | _                      | 1ED7h | _          | 1F57h | _                      | 1FD7h | _           |

| 1E58h | _                      | 1ED8h | _          | 1F58h | _                      | 1FD8h | _           |

| 1E59h | —                      | 1ED9h | _          | 1F59h | ANSELD <sup>(1)</sup>  | 1FD9h | _           |

| 1E5Ah | _                      | 1EDAh | _          | 1F5Ah | WPUD <sup>(1)</sup>    | 1FDAh | _           |

| 1E5Bh | _                      | 1EDBh | _          | 1F5Bh | ODCOND <sup>(1)</sup>  | 1FDBh | _           |

| 1E5Ch | _                      | 1EDCh | _          | 1F5Ch | SLRCOND <sup>(1)</sup> | 1FDCh | _           |

| 1E5Dh | _                      | 1EDDh | _          | 1F5Dh | INLVLD <sup>(1)</sup>  | 1FDDh | _           |

| 1E5Eh |                        | 1EDEh | _          | 1F5Eh | _                      | 1FDEh | _           |

| 1E5Fh |                        | 1EDFh | _          | 1F5Fh |                        | 1FDFh | _           |

| 1E60h | _                      | 1EE0h | _          | 1F60h |                        | 1FE0h | _           |

| 1E61h | _                      | 1EE1h | _          | 1F61h |                        | 1FE1h | _           |

| 1E62h | _                      | 1EE2h | _          | 1F62h | _                      | 1FE2h | _           |

| 1E63h | _                      | 1EE3h | _          | 1F63h | _                      | 1FE3h | BSR ICDSHAD |

| 1E64h | _                      | 1EE4h | _          | 1F64h | ANSELE <sup>(1)</sup>  | 1FE4h | STATUS SHAD |

| 1E65h | _                      | 1EE5h | _          | 1F65h | WPUE                   | 1FE5h | WREG_SHAD   |

| 1E66h | _                      | 1EE6h | _          | 1F66h | ODCONE <sup>(1)</sup>  | 1FE6h | BSR_SHAD    |

| 1E67h | _                      | 1EE7h | _          | 1F67h | SLRCONE <sup>(1)</sup> | 1FE7h | PCLATH SHAD |

| 1E68h | _                      | 1EE8h | _          | 1F68h | INLVLE                 | 1FE8h | FSR0L SHAD  |

| 1E69h | _                      | 1EE9h | _          | 1F69h | IOCEP                  | 1FE9h | FSR0H SHAD  |

| 1E6Ah |                        | 1EEAh | _          | 1F6Ah | IOCEN                  | 1FEAh | FSR1L SHAD  |

| 1E6Bh | _                      | 1EEBh | _          | 1F6Bh | IOCEF                  | 1FEBh | FSR1H_SHAD  |

| 1E6Ch |                        | 1EECh | _          | 1F6Ch |                        | 1FECh |             |

| 1E6Dh |                        | 1EEDh | _          | 1F6Dh | _                      | 1FEDh | STKPTR      |

| 1E6Eh |                        | 1EEEh | _          | 1F6Eh | _                      | 1FEEh | TOSL        |

| 1E6Fh |                        | 1EEFh | _          | 1F6Fh | _                      | 1FEFh | TOSH        |

# TABLE 4-9: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANKS 60, 61, 62, AND 63

Legend:

= Unimplemented data memory locations, read as '0'

**Note 1:** Present only on PIC16(L)F15375/76/85/86.

2: Present only on PIC16(L)F15385/86

| IABLE 4  | ABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |               |       |         |               |                   |           |           |       |                       |                            |  |  |  |

|----------|---------------------------------------------------------------------|---------------|-------|---------|---------------|-------------------|-----------|-----------|-------|-----------------------|----------------------------|--|--|--|

| Address  | Name                                                                | Bit 7         | Bit 6 | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1     | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |  |

| Bank 12  | ank 12                                                              |               |       |         |               |                   |           |           |       |                       |                            |  |  |  |

|          |                                                                     |               |       | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics |           |       |                       |                            |  |  |  |

| 60Ch     | CWG1CLKCON                                                          | —             | _     | —       | _             | —                 | —         | _         | CS    | 0                     | 0                          |  |  |  |

| 60Dh     | CWG1DAT                                                             | _             | _     | _       | _             |                   | DA        | T<3:0>    |       | 0000                  | 0000                       |  |  |  |

| 60Eh     | CWG1DBR                                                             | _             | —     |         |               | 00 0000           | 00 0000   |           |       |                       |                            |  |  |  |

| 60Fh     | CWG1DBF                                                             | _             | —     |         |               |                   | 00 0000   | 00 0000   |       |                       |                            |  |  |  |

| 610h     | CWG1CON0                                                            | EN            | LD    | —       | —             | —                 |           | MODE<2:0> | •     | 00000                 | 00000                      |  |  |  |

| 611h     | CWG1CON1                                                            | _             | —     | IN      | —             | POLD              | POLC      | POLB      | POLA  | x- 0000               | u- 0000                    |  |  |  |

| 612h     | CWG1AS0                                                             | SHUTDOWN      | REN   | LSBD    | <2:0>         | LSAC              | <2:0>     | —         | _     | 0001 01               | 0001 01                    |  |  |  |

| 613h     | CWG1AS1                                                             | _             | —     | _       | AS4E          | AS3E              | AS2E      | AS1E      | AS0E  | 0 0000                | u 0000                     |  |  |  |

| 614h     | CWG1STR                                                             | OVRD          | OVRC  | OVRB    | OVRA          | STRD              | STRC      | STRB      | STRA  | 0000 0000             | 0000 0000                  |  |  |  |

| 615h     |                                                                     |               |       |         | Linimalor     | mantad            |           |           |       |                       |                            |  |  |  |

| <br>61Fh | _                                                                   | Unimplemented |       |         |               |                   |           |           |       | _                     |                            |  |  |  |

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

PIC16(L)F15356/75/76/85/86

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATB<7:0>: RB<7:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register returns actual I/O pin values.

#### REGISTER 14-12: ANSELB: PORTB ANALOG SELECT REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSB7   | ANSB6   | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ANSB<7:0>: Analog Select between Analog or Digital Function on pins RB<7:0>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSD<7:0>**: Analog Select between Analog or Digital Function on Pins RD<7:0>, respectively<sup>(1)</sup> 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### REGISTER 14-29: WPUD: WEAK PULL-UP PORTD REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2   | WPUD1   | WPUD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUD<7:0>: Weak Pull-up Register bits<sup>(1)</sup>

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTD   | RD7     | RD6     | RD5     | RD4     | RD3     | RD2     | RD1     | RD0     | 216                 |

| TRISD   | TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  | 216                 |

| LATD    | LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   | 216                 |

| ANSELD  | ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   | 217                 |

| WPUD    | WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2   | WPUD1   | WPUD0   | 217                 |

| ODCOND  | ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2   | ODCD1   | ODCD0   | 218                 |

| SLRCOND | SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   | 218                 |

| INLVLD  | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 | 218                 |

### TABLE 14-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

# PIC16(L)F15356/75/76/85/86

|                       | 1     | · · · • · · · |       |             | · · · · · · · · · | 1        |       |       |                     |

|-----------------------|-------|---------------|-------|-------------|-------------------|----------|-------|-------|---------------------|

| Name                  | Bit 7 | Bit 6         | Bit 5 | Bit 4       | Bit 3             | Bit 2    | Bit 1 | Bit 0 | Register<br>on page |

| RC1PPS                | —     | —             | —     |             |                   | RC1PPS<  | 4:0>  |       | 242                 |

| RC2PPS                | _     | _             | _     |             |                   | RC2PPS<  | 4:0>  |       | 242                 |

| RC3PPS                | _     | _             | _     |             |                   | RC3PPS<  | 4:0>  |       | 242                 |

| RC4PPS                | _     | —             | _     |             |                   | RC4PPS<  | 4:0>  |       | 242                 |

| RC5PPS                | _     | —             | _     |             |                   | RC5PPS<  | 4:0>  |       | 242                 |

| RC6PPS                | _     | —             | _     |             |                   | RC6PPS<  | 4:0>  |       | 242                 |

| RC7PPS                | _     | _             | _     |             |                   | RC7PPS<  | 4:0>  |       | 242                 |

| RD0PPS <sup>(1)</sup> | _     | _             | _     |             |                   | RD0PPS<4 | :0>   |       | 242                 |

| RD1PPS <sup>(1)</sup> | _     | _             | _     |             |                   | RD1PPS<4 | :0>   |       | 242                 |

| RD2PPS <sup>(1)</sup> | _     | _             | _     |             | RD2PPS<4:0>       |          |       |       |                     |

| RD3PPS <sup>(1)</sup> | _     | _             | _     |             | RD3PPS<4:0>       |          |       |       |                     |

| RD4PPS <sup>(1)</sup> | —     | —             | —     |             | RD4PPS<4:0>       |          |       |       | 242                 |

| RD5PPS <sup>(1)</sup> | —     | _             | _     |             |                   | RD5PPS<4 | :0>   |       | 242                 |

| RD6PPS <sup>(1)</sup> | —     |               | _     |             |                   | RD6PPS<4 | :0>   |       | 242                 |

| RD7PPS <sup>(1)</sup> | _     | _             | _     |             |                   | RD7PPS<4 | :0>   |       | 242                 |

| RE0PPS <sup>(1)</sup> | —     | —             | _     |             |                   | RD5PPS<4 | :0>   |       | 242                 |

| RE1PPS <sup>(1)</sup> | —     | —             | —     |             |                   | RD6PPS<4 | :0>   |       | 242                 |

| RE2PPS <sup>(1)</sup> | —     | _             | —     |             |                   | RD7PPS<4 | :0>   |       | 242                 |

| RF0PPS <sup>(2)</sup> | —     | —             | —     |             |                   | RF0PPS<4 | :0>   |       | 242                 |

| RF1PPS <sup>(2)</sup> | —     | —             | —     | RF1PPS<4:0> |                   |          |       |       | 242                 |

| RF2PPS <sup>(2)</sup> | —     | —             | —     | RF2PPS<4:0> |                   |          |       |       | 242                 |

| RF3PPS <sup>(2)</sup> | -     | —             | _     | RF3PPS<4:0> |                   |          |       |       | 242                 |

| RF4PPS <sup>(2)</sup> | —     | _             | _     | RF4PPS<4:0> |                   |          |       |       | 242                 |

| RF5PPS <sup>(2)</sup> | —     | —             | —     | RF5PPS<4:0> |                   |          |       |       | 242                 |

| RF6PPS <sup>(2)</sup> | —     | —             | —     | RF6PPS<4:0> |                   |          |       |       | 242                 |

| RF7PPS <sup>(2)</sup> | —     | —             | —     |             |                   | RF7PPS<4 | :0>   |       | 242                 |

#### TABLE 15-8: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

Note 1: Present only on PIC16(L)F15375/76/85/86.

2: Present only on PIC16(L)F15385/86.

# PIC16(L)F15356/75/76/85/86

| ADC Clock P         | eriod (TAD) |                             |                             | Device Frequ                |                             |                               |                             |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|-----------------------------|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                         | 1 MHz                       |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>         | 2.0 μs                      |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                        | 4.0 μs                      |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                        | 8.0 μs <sup>(3)</sup>       |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                        | 16.0 μs <sup>(3)</sup>      |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>         | 32.0 μs <sup>(2)</sup>      |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <b><sup>(2)</sup></b> | 64.0 μs <sup>(2)</sup>      |

| ADCRC               | x11         | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup> |

### TABLE 20-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

Note 1: See TAD parameter for ADCRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

**4:** The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the ADCRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

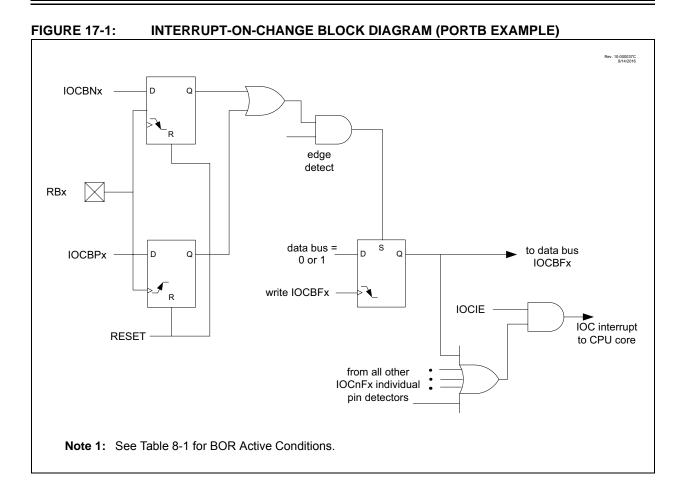

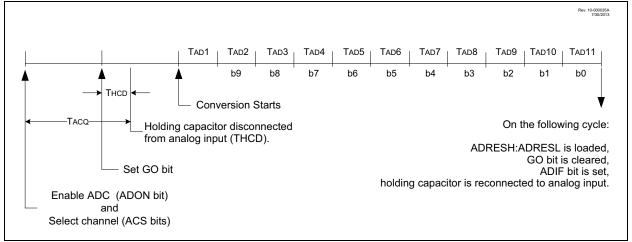

## FIGURE 20-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

### **REGISTER 22-6:** NCO1INCL: NCO1 INCREMENT REGISTER – LOW BYTE<sup>(1,2)</sup>

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-1/1 |

|----------|---------|---------|---------|---------|---------|---------|---------|

|          |         |         | NCO1I   | NC<7:0> |         |         |         |

| bit 7    |         |         |         |         |         |         | bit 0   |

|          |         |         |         |         |         |         |         |

| l egend: |         |         |         |         |         |         |         |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCO1INC<7:0>: NCO1 Increment, Low Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

2: DDSINC is double-buffered as INCBUF; INCBUF is updated on the next falling edge of NCOCLK after writing to NCO1INCL; NCO1INCU and NCO1INCH should be written prior to writing NCO1INCL.

## **REGISTER 22-7:** NCO1INCH: NCO1 INCREMENT REGISTER – HIGH BYTE<sup>(1)</sup>

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|----------|---------|---------|---------|

|         |         |         | NCO1IN  | IC<15:8> |         |         |         |

| bit 7   |         |         |         |          |         |         | bit 0   |

|         |         |         |         |          |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 NCO1INC<15:8>: NCO1 Increment, High Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

#### **REGISTER 22-8:** NCO1INCU: NCO1 INCREMENT REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | —   | —   | —   |         | NCO1IN  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1INC<19:16>: NCO1 Increment, Upper Byte

**Note 1:** The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

## 24.9 Register Definitions: ZCD Control

### REGISTER 24-1: ZCDCON: ZERO-CROSS DETECTION CONTROL REGISTER

| R/W-q/q          | U-0                                                                                                                  | R-x/x                                                                                     | R/W-0/0        | U-0                               | U-0             | R/W-0/0                            | R/W-0/0      |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|-----------------------------------|-----------------|------------------------------------|--------------|--|--|

| SEN              | —                                                                                                                    | OUT                                                                                       | POL            | —                                 | _               | INTP                               | INTN         |  |  |

| bit 7            |                                                                                                                      | -                                                                                         | ·              |                                   |                 |                                    | bit 0        |  |  |

|                  |                                                                                                                      |                                                                                           |                |                                   |                 |                                    |              |  |  |

| Legend:          |                                                                                                                      |                                                                                           |                |                                   |                 |                                    |              |  |  |

| R = Readable     | bit                                                                                                                  | W = Writable                                                                              | bit            | U = Unimpler                      | nented bit, rea | d as '0'                           |              |  |  |

| u = Bit is unch  | anged                                                                                                                | x = Bit is unk                                                                            | nown           | -n/n = Value a                    | at POR and BC   | OR/Value at all o                  | other Resets |  |  |

| '1' = Bit is set |                                                                                                                      | '0' = Bit is cle                                                                          | ared           | q = value dep                     | ends on Confi   | guration bits                      |              |  |  |

| bit 7            | 1 = Zero-cro                                                                                                         |                                                                                           | abled. ZCD pi  |                                   |                 | and sink currer<br>and TRIS contro |              |  |  |

| bit 6            | Unimplemer                                                                                                           | Unimplemented: Read as '0'                                                                |                |                                   |                 |                                    |              |  |  |

| bit 5            | $\frac{\text{POL bit} = 1}{1 = \text{ZCD pin}}$ $0 = \text{ZCD pin}$ $\frac{\text{POL bit} = 0}{1 = \text{ZCD pin}}$ | ross Detection<br>is sourcing cur<br>is sinking curr<br>is sinking curr<br>is sourcing cu | rrent<br>ent   | it                                |                 |                                    |              |  |  |

| bit 4            | 1 = ZCD log                                                                                                          | ross Detection<br>ic output is inve<br>ic output is not                                   | erted          | Polarity bit                      |                 |                                    |              |  |  |

| bit 3-2          | Unimplemer                                                                                                           | ted: Read as                                                                              | ʻ0'            |                                   |                 |                                    |              |  |  |

| bit 1            | INTP: Zero-C                                                                                                         | Cross Positive I                                                                          | Edge Interrupt | Enable bit                        |                 |                                    |              |  |  |

|                  |                                                                                                                      |                                                                                           |                | _output transition ZCDx_output    |                 |                                    |              |  |  |

| bit 0            | INTN: Zero-C                                                                                                         | Cross Negative                                                                            | Edge Interrup  | ot Enable bit                     |                 |                                    |              |  |  |

|                  |                                                                                                                      |                                                                                           |                | _output transiti<br>v ZCDx_output |                 |                                    |              |  |  |

|                  |                                                                                                                      |                                                                                           |                |                                   |                 |                                    |              |  |  |

#### TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| PIE3    | RC2IE | TX2IE | RC1IE | TX1IE | BCL2IE | SSP2IE | BCL1IE | SSP1IE | 150                 |

| PIR3    | RC2IF | TX2IF | RC1IF | TX1IF | BCL2IF | SSP2IF | BCL1IF | SSP1IF | 158                 |

| ZCDxCON | EN    | _     | OUT   | POL   |        |        | INTP   | INTN   | 314                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 24-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name       | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|------------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| 0.01/5/0.0 | 13:8 | _       | _       | DEBUG    | STVREN   | PPS1WAY  | ZCDDIS   | BORV    |         | 100                 |

| CONFIG2    | 7:0  | BOREN   | N <1:0> | LPBOREN  |          | —        |          | PWRTE   | MCLRE   | 103                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

## 31.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) module provides programmable logic that operates outside the speed limitations of software execution. The logic cell selects from 40 input signals and, through the use of configurable gates, reduces the inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

The CLC modules available are shown in Table 31-1.

TABLE 31-1: AVAILABLE CLC MODULES

| Device                         | CLC1 | CLC2 | CLC3 | CLC4 |

|--------------------------------|------|------|------|------|

| PIC16(L)F15356/75/76/85/8<br>6 | •    | •    | •    | ٠    |

| Note: | The CLC1, CLC2, CLC3 and CLC4 are            |

|-------|----------------------------------------------|

|       | four separate module instances of the        |

|       | same CLC module design. Throughout           |

|       | this section, the lower case 'x' in register |

|       | and bit names is a generic reference to      |

|       | the CLC number (which should be substi-      |

|       | tuted with 1, 2, 3, or 4 during code devel-  |

|       | opment). For example, the control register   |

|       | is generically described in this chapter as  |

|       | CLCxCON, but the actual device registers     |

|       | are CLC1CON, CLC2CON, CLC3CON                |

|       | and CLC4CON. Similarly, the LCxEN bit        |

|       | represents the LC1EN, LC2EN, LC3EN           |

|       | and LC4EN bits.                              |

Refer to Figure 31-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

#### 32.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of  $\overline{ACK}$  is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCL low and SDA unchanged (Figure 32-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

#### 32.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

#### 32.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 32.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

32.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPx-CON2 register. Interrupt is generated once the Stop/Restart condition is complete.

#### 33.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXxSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

#### 33.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 33.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode.

If two words are written to the TXxREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXxREG register.

- 3. The TXxIF bit will not be set.

- After the first character has been shifted out of TSR, the TXxREG register will transfer the second character to the TSR and the TXxIF bit will now be set.

- 5. If the PEIE and TXxIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 33.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- 4. If interrupts are desired, set the TXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXxREG register.

# PIC16(L)F15356/75/76/85/86

# REGISTER 33-4: RCxREG<sup>(1)</sup>: RECEIVE DATA REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|--------|-----|-----|-------|

|       |     |     | RCxRE | G<7:0> |     |     |       |

| bit 7 |     |     |       |        |     |     | bit 0 |

|       |     |     |       |        |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **RCxREG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 33-2)

**Note 1:** RCxREG (including the 9<sup>th</sup> bit) is double buffered, and data is available while new data is being received.

## REGISTER 33-5: TXxREG<sup>(1)</sup>: TRANSMIT DATA REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------|-------|-------|--------|-------|-------|-------|--|--|--|

|       |       |       | TXxRE | G<7:0> |       |       |       |  |  |  |

| bit 7 |       |       | bit 7 |        |       |       |       |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TXxREG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 33-1)

**Note 1:** TXxREG (including the 9th bit) is double buffered, and can be written when previous data has started shifting.

## **REGISTER 33-6:** SPxBRGL<sup>(1)</sup>: BAUD RATE GENERATOR REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| SPxBRG<7:0> |       |       |       |       |       |       |       |

| bit 7       |       |       |       |       |       |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SPxBRG<7:0>: Lower eight bits of the Baud Rate Generator

**Note 1:** Writing to SP1BRG resets the BRG counter.

### TABLE 37-18: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

|               | d Operating ( |                       | nless otherwise<br>≤ +125°C                                             | e stated)                                 |                                           |                          |                  |                    |                        |

|---------------|---------------|-----------------------|-------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------|------------------|--------------------|------------------------|

| Param.<br>No. | Sym.          |                       | Characteristic                                                          | Min.                                      | Тур†                                      | Max.                     | Units            | Conditions         |                        |

| 40*           | T⊤0H          | T0CKI High F          | OCKI High Pulse Width No Prescaler                                      |                                           |                                           | —                        | _                | ns-                | $\langle \rangle$      |

|               |               |                       | With Prescaler                                                          |                                           | 10                                        |                          | —                | / ns               |                        |

| 41*           | T⊤0L          | T0CKI Low F           | T0CKI Low Pulse Width No Prescaler                                      |                                           |                                           |                          | —/               | /ns /              |                        |

|               |               |                       | With Prescaler                                                          |                                           |                                           |                          | _                | NS                 |                        |

| 42*           | T⊤0P          | T0CKI Period          | 1                                                                       | Greater of:<br>20 or <u>Tcy + 40</u><br>N | -                                         | /                        | ns               | N = prescale value |                        |

| 45*           | T⊤1H          | T1CKI High            | Synchronous, N                                                          | lo Prescaler                              | 0.5 Tcy + 20                              | _/                       | K                | ns,                | Ŷ                      |

|               |               | Time                  | Synchronous, with Prescaler                                             |                                           | 15                                        | -                        | $\overline{1}$   | 715                |                        |

|               |               |                       | Asynchronous                                                            |                                           | 30 🔨                                      |                          |                  | ns                 |                        |

| 46*           | T⊤1L          | T1CKI Low             | Synchronous, N                                                          | lo Prescaler                              | 0.5 Tcy + 20                              | <u> </u>                 | /_/              | ns                 |                        |

|               |               | Time                  | Synchronous, w                                                          | ith Prescaler                             | 15                                        | $\langle - \rangle$      | $\rightarrow$    | ns                 |                        |

|               |               |                       | Asynchronous                                                            |                                           | 30                                        | $\overline{\mathcal{A}}$ | $\overline{)} -$ | ns                 |                        |

| 47*           | T⊤1P          | T1CKI Input<br>Period | Synchronous                                                             |                                           | Greater of:<br>30 or <u>Tcy + 40</u><br>N |                          | /_               | ns                 | N = prescale value     |

| 10            | <b>F</b> _4   |                       | Asynchronous                                                            |                                           | 60                                        | —<br>32.768              | —                | ns                 |                        |

| 48            | F⊤1           |                       | scillator Input Frequency Range 32.4 ;<br>abled by setting bit T1OSCEN) |                                           |                                           |                          | 33.1             | kHz                |                        |

| 49*           | TCKEZTMR1     | Increment             | xternal Clock Ed                                                        | $\overline{\overline{)}}$                 | 2 Tosc                                    | —                        | 7 Tosc           | —                  | Timers in Sync<br>mode |

These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C onless otherwise stated. These parameters are for design guidance only and are not tested.

© 2016 Microchip Technology Inc.

## 38.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

Unless otherwise noted, all graphs apply to both the L and LF devices.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum", "Max.", "Minimum" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

Charts and graphs are not available at this time.

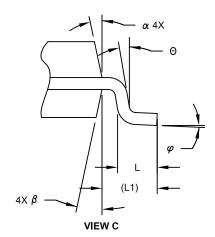

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |     |      |  |

|--------------------------|----|-------------|-----|------|--|

| Dimension Limits         |    | MIN         | NOM | MAX  |  |

| Number of Pins           | N  | 28          |     |      |  |

| Pitch                    | е  | 1.27 BSC    |     |      |  |

| Overall Height           | Α  | -           | -   | 2.65 |  |

| Molded Package Thickness | A2 | 2.05        | -   | -    |  |

| Standoff §               | A1 | 0.10        | -   | 0.30 |  |

| Overall Width            | E  | 10.30 BSC   |     |      |  |

| Molded Package Width     | E1 | 7.50 BSC    |     |      |  |

| Overall Length           | D  | 17.90 BSC   |     |      |  |

| Chamfer (Optional)       | h  | 0.25        | -   | 0.75 |  |

| Foot Length              | L  | 0.40        | -   | 1.27 |  |

| Footprint                | L1 | 1.40 REF    |     |      |  |

| Lead Angle               | Θ  | 0°          | -   | -    |  |

| Foot Angle               | φ  | 0°          | -   | 8°   |  |

| Lead Thickness           | С  | 0.18        | -   | 0.33 |  |

| Lead Width               | b  | 0.31        | -   | 0.51 |  |

| Mold Draft Angle Top     | α  | 5°          | -   | 15°  |  |

| Mold Draft Angle Bottom  | β  | 5°          | -   | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

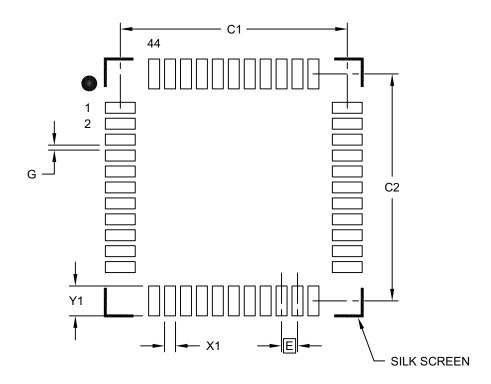

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

| Units                    |    | MILLIMETERS |       |      |  |

|--------------------------|----|-------------|-------|------|--|

| Dimension Limits         |    | MIN         | NOM   | MAX  |  |

| Contact Pitch            | E  | 0.80 BSC    |       |      |  |

| Contact Pad Spacing      | C1 |             | 11.40 |      |  |

| Contact Pad Spacing      | C2 |             | 11.40 |      |  |

| Contact Pad Width (X44)  | X1 |             |       | 0.55 |  |

| Contact Pad Length (X44) | Y1 |             |       | 1.50 |  |

| Distance Between Pads    | G  | 0.25        |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

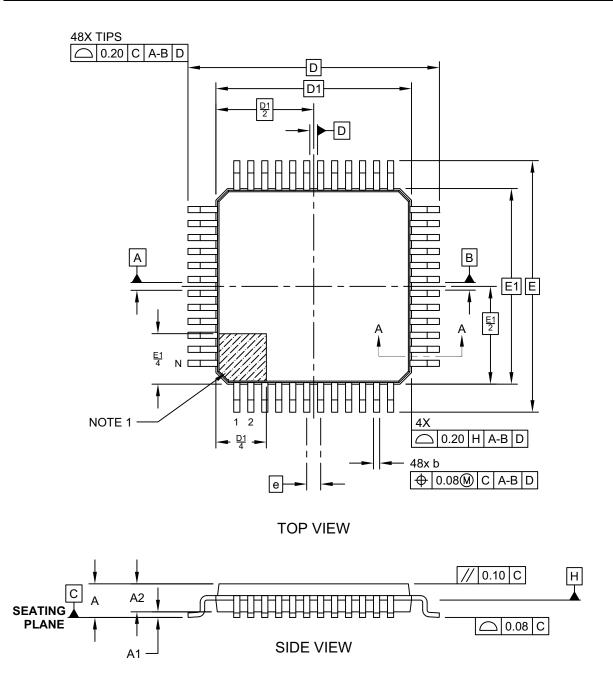

## 48-Lead Thin Quad Flatpack (PT) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-300-PT Rev A Sheet 1 of 2