Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 28KB (16K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15376t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-4:** PIC16(L)F15385/86 PINOUT DESCRIPTION (CONTINUED)

| Name                                                            | Function | Input<br>Type | Output Type       | Description                    |

|-----------------------------------------------------------------|----------|---------------|-------------------|--------------------------------|

| RF5/ANF5                                                        | RF5      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF5     | AN            | _                 | ADC Channel D0 input.          |

| RF6/ANF6                                                        | RF6      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF6     | AN            | —                 | ADC Channel D0 input.          |

| RF7/ANF7                                                        | RF5      | TTL/ST        | CMOS/OD           | General purpose I/O.           |

|                                                                 | ANF5     | AN            | _                 | ADC Channel D0 input.          |

| VDD                                                             | Vdd      | Power         | _                 | Positive supply voltage input. |

| Vss                                                             | Vss      | Power         | _                 | Ground reference.              |

| Legend: AN = Analog input or outp<br>TTL = TTL compatible input |          |               | mpatible input or |                                |

TTL = TTL compatible input

HV = High Voltage

XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-7.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for  $l^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the  $l^2C$  specific or SMBus input buffer thresholds. 4:

|      | BANK 24                                                   |      | BANK 25                                                   |      | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                       |

|------|-----------------------------------------------------------|------|-----------------------------------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| C00h | Core Registers<br>(Table 4-3)                             | C80h | Core Registers<br>(Table 4-3)                             | D00h | Core Registers<br>(Table 4-3) | D80h | Core Registers<br>(Table 4-3) | E00h | Core Registers<br>(Table 4-3) | E80h | Core Registers<br>(Table 4-3) | F00h | Core Registers<br>(Table 4-3) | F80h | Core Registers<br>(Table 4-3) |

| C0Bh |                                                           | C8Bh |                                                           | D0Bh |                               | D8Bh |                               | E0Bh |                               | E8Bh |                               | F0Bh |                               | F8Bh |                               |

| COCh | Unimplemented<br>Read as '0'                              | C8Ch | Unimplemented<br>Read as '0'                              | DOCh | Unimplemented<br>Read as '0'  |      | Unimplemented<br>Read as '0'  |

| C1Fh |                                                           | C9Fh |                                                           |      |                               |      |                               |      |                               |      |                               |      |                               |      |                               |

| C20h |                                                           | CA0h |                                                           |      |                               |      |                               |      |                               |      |                               |      |                               |      |                               |

|      | General<br>Purpose<br>Register<br>80 Bytes <sup>(1)</sup> |      | General<br>Purpose<br>Register<br>80 Bytes <sup>(1)</sup> |      |                               |      |                               |      |                               |      |                               |      |                               |      |                               |

| C6Fh |                                                           | CEFh |                                                           | D6Fh |                               | DEFh |                               | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                               |

| C70h | Accesses<br>70h – 7Fh                                     | CF0h | Accesses<br>70h – 7Fh                                     | D70h | Accesses<br>70h – 7Fh         | DF0h | Accesses<br>70h – 7Fh         | E70h | Accesses<br>70h – 7Fh         | EF0h | Accesses<br>70h – 7Fh         | F70h | Accesses<br>70h – 7Fh         | FF0h | Accesses<br>70h – 7Fh         |

|      |                                                           |      |                                                           |      |                               |      |                               |      |                               |      |                               |      |                               |      |                               |

#### TABLE 4-7: PIC16(L)F15356/75/76/85/86 MEMORY MAP, BANK 24-31

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Present only in PIC16(L)F15356/76/86.

| IADLE      | ABLE 4-11. SPECIAL FUNCTION REGISTER SUMMART BANKS 0-05 (CONTINUED) |       |       |       |       |        |            |       |       |                       |  |

|------------|---------------------------------------------------------------------|-------|-------|-------|-------|--------|------------|-------|-------|-----------------------|--|

| Address    | Name                                                                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2      | Bit 1 | Bit 0 | Value on:<br>POR, BOR |  |

| Bank 61 (0 | Continued)                                                          |       |       |       |       |        |            |       |       |                       |  |

| 1EC5h      | SSP1CLKPPS                                                          | —     | —     |       |       | SSP1CL | .KPPS<5:0> |       |       | 01 0011               |  |

| 1EC6h      | SSP1DATPPS — — SSP1DATPPS<5:0>                                      |       |       |       |       |        |            |       |       | 01 0100               |  |

| 1EC7h      | SSP1SSPPS                                                           | _     | —     |       |       | SSP1S  | SPPS<5:0>  |       |       | 00 0101               |  |

SSP2CLKPPS<5:0>

SSP2DATPPS<5:0>

SSP2SSPPS<5:0>

RX1DTPPS<5:0>

TX1CKPPS<5:0>

RX2DTPPS<5:0>

TX2CKPPS<5:0>

Unimplemented

#### TABLE 4-11: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

\_

\_\_\_\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

| Legend: | x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

1EC8h

1EC9h

1ECAh

1ECBh

1ECCh

1ECDh

1ECEh

1ECFh

1EEFh

SSP2CLKPPS

SSP2DATPPS

SSP2SSPPS

RX1DTPPS

TX1CKPPS

RX2DTPPS

TX2CKPPS

V<u>alue o</u>n: MCLR

--uu uuuu

--00 1001

--00 1000

--00 1000

--01 0111

--01 0110

--00 1111

--00 1110

### 5.0 DEVICE CONFIGURATION

Device configuration consists of the Configuration Words, User ID, Device ID, Device Information Area (DIA), (see Section 6.0 "Device Information Area"), and the Device Configuration Information (DCI) regions, (see Section 7.0 "Device Configuration Information").

#### 5.1 Configuration Words

The devices have several Configuration Words starting at address 8007h. The Configuration bits establish configuration values prior to the execution of any software; Configuration bits enable or disable device-specific features.

In terms of programming, these important Configuration bits should be considered:

#### 1. LVP: Low-Voltage Programming Enable bit

- <u>1</u> = ON Low-Voltage Programming is enabled. MCLR/VPP pin function is MCLR. MCLRE Configuration bit is ignored.

- 0 = OFF HV on MCLR/VPP must be used for programming.

- 2. CP: User Nonvolatile Memory (NVM) Program Memory Code Protection bit

- 1 = OFF User NVM code protection disabled

- 0 = ON User NVM code protection enabled

|                  |                    |                                    |                 | INEQUEU        |                  |                |              |

|------------------|--------------------|------------------------------------|-----------------|----------------|------------------|----------------|--------------|

| R/W/HS-0/0       | R/W/HS-0/0         | R/W/HS-0/0                         | R/W/HS-0/0      | U-0            | U-0              | U-0            | R/W/HS-0/0   |

| CLC4IF           | CLC3IF             | CLC2IF                             | CLC1IF          | —              |                  | —              | TMR1GIF      |

| bit 7            |                    |                                    |                 |                |                  |                | bit 0        |

|                  |                    |                                    |                 |                |                  |                |              |

| Legend:          |                    |                                    |                 |                |                  |                |              |

| R = Readable     | bit                | W = Writable                       | bit             | U = Unimpler   | mented bit, read | as '0'         |              |

| u = Bit is uncha | anged              | x = Bit is unkr                    | iown            | -n/n = Value a | at POR and BOI   | R/Value at all | other Resets |

| '1' = Bit is set |                    | '0' = Bit is clea                  | ared            | HS = Hardwa    | are set          |                |              |

|                  |                    |                                    |                 |                |                  |                |              |

| bit 7            | CLC4IF: CLC        | 4 Interrupt Flag                   | g bit           |                |                  |                |              |

|                  |                    |                                    |                 | curred (must l | be cleared in so | ftware)        |              |

|                  | 0 = No CLC4        | interrupt event                    | has occurred    |                |                  |                |              |

| bit 6            | CLC3IF: CLC        | 3 Interrupt Flag                   | g bit           |                |                  |                |              |

|                  |                    |                                    |                 | curred (must b | be cleared in so | ftware)        |              |

|                  | 0 = No CLC3        | interrupt event                    | has occurred    |                |                  |                |              |

| bit 5            | CLC2IF: CLC        | 2 Interrupt Flag                   | g bit           |                |                  |                |              |

|                  |                    | UT interrupt co<br>interrupt event |                 | curred (must b | be cleared in so | ftware)        |              |

| bit 4            |                    | 1 Interrupt Flag                   |                 |                |                  |                |              |

|                  |                    |                                    | 5               | curred (must l | be cleared in so | ftware)        |              |

|                  | 0 = No CLC1        | interrupt event                    | has occurred    |                |                  | ,              |              |

| bit 3-1          | Unimplemen         | ted: Read as '                     | כ'              |                |                  |                |              |

| bit 0            | TMR1GIF: Tir       | mer1 Gate Inte                     | rrupt Flag bit  |                |                  |                |              |

|                  |                    | r1 Gate has go                     |                 |                | s complete)      |                |              |

|                  | 0 = The Time       | r1 Gate has no                     | t gone inactive | 9              |                  |                |              |

|                  |                    |                                    |                 |                |                  |                |              |

| Note: Inte       | errupt flag bits a | re set when an                     | interrupt       |                |                  |                |              |

|                  | aprillag bito u    |                                    | apt             |                |                  |                |              |

#### REGISTER 10-15: PIR5: PERIPHERAL INTERRUPT REQUEST REGISTER 5

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |  |  |  |  |  |

#### EXAMPLE 13-1: PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELNVMADRL; Select Bank for NVMCON registersMOVLWPROG_ADDR_LO;MOVWFNVMADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWFNVMADRH; Store MSB of address

BCF

NVMCON1,NVMREGS ; Do not select Configuration Space

BSF

NVMCON1, RD

; Initiate read

MOVF

NVMDATL,W

; Get LSB of word

NVMDATL,W; Get LSB of wordPROG_DATA_LO; Store in user locationNVMDATH,W; Get MSB of wordPROG_DATA_HI; Store in user location

MOVWF

MOVF

MOVWF

```

#### 19.2.1 CALIBRATION

#### 19.2.1.1 Single-Point Calibration

Single-point calibration is performed by application software using Equation 19-1 and the assumed Mt. A reading of VTSENSE at a known temperature is taken, and the theoretical temperature is calculated by temporarily setting TOFFSET = 0. Then TOFFSET is computed as the difference of the actual and calculated temperatures. Finally, TOFFSET is stored in nonvolatile memory within the device, and is applied to future readings to gain a more accurate measurement.

#### 19.2.1.2 Higher-Order Calibration

If the application requires more precise temperature measurement, additional calibrations steps will be necessary. For these applications, two-point or three-point calibration is recommended.

| Note 1: | The TOFFSET value may be determined  |

|---------|--------------------------------------|

|         | by the user with a temperature test. |

- 2: Although the measurement range is -40°C to +125 °C due to the variations in offset error, the single-point uncalibrated calculated TSENSE value may indicate a temperature from -140°C to +225°C before the calibration offset is applied.

- The user must take into consideration self-heating of the device at different clock frequencies and output pin loading. For package related thermal characteristics information, refer to Section TABLE 37-6: "Thermal Characteristics".

#### 19.2.2 TEMPERATURE RESOLUTION

The resolution of the ADC reading, Ma (°C/count), depends on both the ADC resolution N and the reference voltage used for conversion, as shown in Equation 19-2. It is recommended to use the smallest VREF value, such as 2.048 FVR reference voltage, instead of VDD.

| Note: | Refer   | to     | Sec    | tion : | 37.0 | "Electrical |  |  |

|-------|---------|--------|--------|--------|------|-------------|--|--|

|       | Specif  | icatio | ons"   | for    | FVR  | reference   |  |  |

|       | voltage | e accu | uracy. |        |      |             |  |  |

#### EQUATION 19-2: TEMPERATURE RESOLUTION (°C/LSb)

$$Ma = \frac{V_{REF}}{2^N} \times Mt$$

$$Ma = \frac{\frac{V_{REF}}{2^N}}{Mv}$$

Where:

Mv = sensor voltage sensitivity (V/°C)

VREF = Reference voltage of the ADC module (in Volts)

N = Resolution of the ADC

The typical Mv value for a single diode is approximately -1.267 to -1.32 mV/C. The typical Mv value for a stack of two diodes (low range setting) is approximately -2.533 mV/C. The typical Mv value for a stack of three diodes (high range setting) is approximately -3.8 mV/C.

#### EXAMPLE 19-1: TEMPERATURE RESOLUTION

Using VREF = 2.048V and a 10-bit ADC provides 2 mV/LSb measurements.

Because Mv can vary from -2.40 to -2.65 mV/°C, the range of Ma = 0.75 to 0.83 °C/LSb.

### 19.3 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait a minimum of 25 us for the ADC value to settle, after the ADC input multiplexer is connected to the temperature indicator output, before the conversion is performed.

| ADC Clock P         | eriod (TAD) |                             | Device Frequency (Fosc)     |                             |                             |                               |                             |  |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|-----------------------------|--|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                         | 1 MHz                       |  |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>         | 2.0 μs                      |  |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                        | 4.0 μs                      |  |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                        | 8.0 μs <sup>(3)</sup>       |  |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                        | 16.0 μs <sup>(3)</sup>      |  |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>         | 32.0 μs <sup>(2)</sup>      |  |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <b><sup>(2)</sup></b> | 64.0 μs <sup>(2)</sup>      |  |  |

| ADCRC               | x11         | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup> |  |  |

#### TABLE 20-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

Note 1: See TAD parameter for ADCRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

**4:** The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the ADCRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

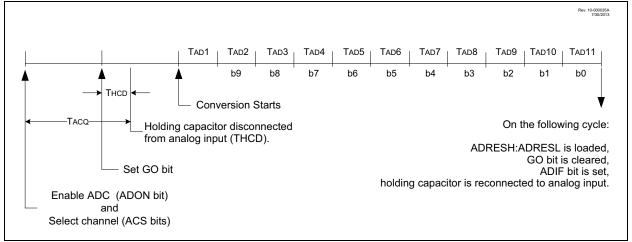

#### FIGURE 20-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### EXAMPLE 24-1:

VRMS = 120 VPEAK =VRMS\*  $\sqrt{2}$  = 169.7 f = 60 Hz C = 0.1 uF Z = VPEAK/3x10<sup>-4</sup> = 169.7/(3x10<sup>-4</sup>) = 565.7 kOhms Xc = 1/(2 $\Pi$ fC) = 1/(2 $\Pi$ \*60\*1\*10<sup>-7</sup>) = 26.53 kOhms R =  $\sqrt{(Z^2 - Xc^2)}$  = 565.1 kOhms (computed) R = 560 kOhms (used) ZR =  $\sqrt{(R^2 + Xc^2)}$  = 560.6 kOhms (using actual resistor) IPEAK = VPEAK/ZR = 302.7\*10<sup>-6</sup> VC = Xc\* IPEAK = 8.0 V  $\Phi$  = Tan<sup>-1</sup>(Xc/R) = 0.047 radians T $_{\Phi}$  =  $\Phi/(2\Pi f)$  = 125.6 us

#### 24.5.2 CORRECTION BY OFFSET CURRENT

When the waveform is varying relative to VSS, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 24-3.

#### EQUATION 24-3: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{Vcpinv}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VDD - Vcpinv}{VPEAK}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to Vss. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the VCPINV switching voltage. The pull-up or pull-down value can be determined with the equation shown in Equation 24-4.

#### EQUATION 24-4: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$R_{PULLUP} = \frac{R_{SERIES}(V_{PULLUP} - V_{cpinv})}{V_{cpinv}}$$

When External Signal is relative to VDD:

$$\left(RPULLDOWN = \frac{RSERIES \times (Vcpinv)}{(VDD - Vcpinv)}\right)$$

#### 24.6 Handling VPEAK variations

If the peak amplitude of the external voltage is expected to vary, the series resistor must be selected to keep the ZCD current source and sink below the design maximum range of  $\pm 600 \ \mu$ A and above a reasonable minimum range. A general rule of thumb is that the maximum peak voltage can be no more than six times the minimum peak voltage. To ensure that the maximum current does not exceed  $\pm 600 \ \mu$ A and the minimum is at least  $\pm 100 \ \mu$ A, compute the series resistance as shown in Equation 24-5. The compensating pull-up for this series resistance can be determined with Equation 24-4 because the pull-up value is not dependent from the peak voltage.

#### EQUATION 24-5: SERIES R FOR V RANGE

$$R_{SERIES} = \frac{V_{MAXPEAK} + V_{MINPEAK}}{7 \times 10^{-4}}$$

© 2016 Microchip Technology Inc.

| R/W-0/0         | U-0                        | R-0                         | R/W-0/0        | R/W-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------|----------------------------|-----------------------------|----------------|-------------------|------------------|------------------|--------------|

| <b>T0EN</b>     | _                          | TOOUT                       | T016BIT        |                   | TOOUTI           | PS<3:0>          |              |

| bit 7           |                            |                             |                |                   |                  |                  | bit          |

|                 |                            |                             |                |                   |                  |                  |              |

| Legend:         |                            |                             |                |                   |                  |                  |              |

| R = Readable    | e bit                      | W = Writable                | bit            | U = Unimplen      | nented bit, read | l as '0'         |              |

| u = Bit is unc  | changed                    | x = Bit is unk              | nown           | -n/n = Value a    | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se | t                          | '0' = Bit is cle            | ared           |                   |                  |                  |              |

|                 |                            |                             |                |                   |                  |                  |              |

| bit 7           | TOEN: Time                 | r0 Enable bit               |                |                   |                  |                  |              |

|                 |                            | dule is enabled             |                |                   |                  |                  |              |

|                 |                            | dule is disabled            |                | vest power mod    | de               |                  |              |

| bit 6           | Unimpleme                  | nted: Read as               | 0'             |                   |                  |                  |              |

| bit 5           | T0OUT: Tim<br>Timer0 outp  | er0 Output bit (ı<br>ut bit | read-only)     |                   |                  |                  |              |

| bit 4           | T016BIT: Tir               | mer0 Operating              | as 16-bit Time | er Select bit     |                  |                  |              |

|                 |                            | is a 16-bit timer           |                |                   |                  |                  |              |

|                 | 0 = Timer0 i               | s an 8-bit timer            |                |                   |                  |                  |              |

| bit 3-0         | T0OUTPS<                   | <b>3:0&gt;:</b> Timer0 ou   | tput postscale | r (divider) seled | ct bits          |                  |              |

|                 | 1111 = 1:16                |                             |                |                   |                  |                  |              |

|                 | 1110 = 1:15<br>1101 = 1:14 |                             |                |                   |                  |                  |              |

|                 | 1101 - 1.14<br>1100 = 1:13 |                             |                |                   |                  |                  |              |

|                 | 1011 = 1:12                |                             |                |                   |                  |                  |              |

|                 | 1010 = 1:11                |                             |                |                   |                  |                  |              |

|                 | 1001 = 1:10                | Postscaler                  |                |                   |                  |                  |              |

|                 | 1000 <b>= 1:9</b>          | Postscaler                  |                |                   |                  |                  |              |

|                 | 0111 <b>= 1:8</b>          |                             |                |                   |                  |                  |              |

|                 | 0110 = 1:7                 |                             |                |                   |                  |                  |              |

|                 | 0101 = 1:6                 |                             |                |                   |                  |                  |              |

|                 | 0100 = 1:5  <br>0011 = 1:4 |                             |                |                   |                  |                  |              |

|                 | 0011 = 1.41<br>0010 = 1:31 |                             |                |                   |                  |                  |              |

|                 | 0001 = 1:2                 |                             |                |                   |                  |                  |              |

|                 | 0000 = 1:1                 |                             |                |                   |                  |                  |              |

| ,         | bit 0        |

|-----------|--------------|

| ,         | bit 0        |

| ,         |              |

| ,         |              |

| ,         |              |

| ,         |              |

| ue at all | other Resets |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

|           |              |

#### REGISTER 26-3: T1CLK TIMER1 CLOCK SELECT REGISTER

#### 27.4 Timer2 Interrupt

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 27-3.

#### FIGURE 27-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

|                 | Rev. 10-00<br>4                                          | 00205A<br>/7/2016 |

|-----------------|----------------------------------------------------------|-------------------|

| CKPS            | 0b010                                                    |                   |

| PRx             | 1                                                        |                   |

| OUTPS           | 0b0001                                                   |                   |

| TMRx_clk        |                                                          |                   |

| TMRx            |                                                          |                   |

| TMRx_postscaled |                                                          |                   |

| TMRxIF          | (1) (2) (1)                                              |                   |

| Note 1:<br>2:   | Synchronization may take as many as 2 instruction cycles |                   |

#### REGISTER 27-4: T2RST: TIMER2 EXTERNAL RESET SIGNAL SELECTION REGISTER

| U-0                                                                  | U-0 | U-0 | U-0  | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0      |

|----------------------------------------------------------------------|-----|-----|------|-------------------------------------------------------|---------|---------|--------------|

| —                                                                    | _   | —   | -    |                                                       | RSEL    | <3:0>   |              |

| bit 7 bit 0                                                          |     |     |      |                                                       |         |         |              |

|                                                                      |     |     |      |                                                       |         |         |              |

| Legend:                                                              |     |     |      |                                                       |         |         |              |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |     |      |                                                       |         |         |              |

| u = Bit is unchanged x = Bit is unknown                              |     |     | iown | -n/n = Value at POR and BOR/Value at all other Resets |         |         | other Resets |

| '1' = Bit is set '0' = Bit is cleared                                |     |     |      |                                                       |         |         |              |

| bit 7-4 | Unimplemented: Read as '0'                                    |

|---------|---------------------------------------------------------------|

| bit 3-0 | RSEL<3:0>: Timer2 External Reset Signal Source Selection bits |

|         | 1111 = Reserved                                               |

|         | 1101 = LC4_out                                                |

|         | 1100 = LC3_out                                                |

|         | 1011 = LC2_out                                                |

|         | 1010 = LC1_out                                                |

|         | 1001 = ZCD1_output                                            |

|         | 1000 = C2OUT_sync                                             |

|         | 0111 = C1OUT_sync                                             |

|         | 0110 = PWM6_out                                               |

|         | 0101 = PWM5_out                                               |

|         | $0100 = PWM4_out$                                             |

|         | 0011 = PWM3_out                                               |

|         | 0010 = CCP2_out                                               |

|         | 0001 = CCP1_out                                               |

|         | 0000 = T2INPPS                                                |

#### 30.5 Dead-Band Control

The dead-band control provides non-overlapping PWM signals to prevent shoot-through current in PWM switches. Dead-band operation is employed for Half-Bridge and Full-Bridge modes. The CWG contains two 6-bit dead-band counters. One is used for the rising edge of the input source control in Half-Bridge mode or for reverse dead-band Full-Bridge mode. The other is used for the falling edge of the input source control in Half-Bridge mode or for forward dead band in Full-Bridge mode.

Dead band is timed by counting CWG clock periods from zero up to the value in the rising or falling deadband counter registers. See CWG1DBR and CWG1DBF registers, respectively.

## 30.5.1 DEAD-BAND FUNCTIONALITY IN HALF-BRIDGE MODE

In Half-Bridge mode, the dead-band counters dictate the delay between the falling edge of the normal output and the rising edge of the inverted output. This can be seen in Figure 30-9.

## 30.5.2 DEAD-BAND FUNCTIONALITY IN FULL-BRIDGE MODE

In Full-Bridge mode, the dead-band counters are used when undergoing a direction change. The MODE<0> bit of the CWG1CON0 register can be set or cleared while the CWG is running, allowing for changes from Forward to Reverse mode. The CWG1A and CWG1C signals will change upon the first rising input edge following a direction change, but the modulated signals (CWG1B or CWG1D, depending on the direction of the change) will experience a delay dictated by the deadband counters. This is demonstrated in Figure 30-3.

## 30.6 Rising Edge and Reverse Dead Band

CWG1DBR controls the rising edge dead-band time at the leading edge of CWG1A (Half-Bridge mode) or the leading edge of CWG1B (Full-Bridge mode). The CWG1DBR value is double-buffered. When EN = 0, the CWG1DBR register is loaded immediately when CWG1DBR is written. When EN = 1, then software must set the LD bit of the CWG1CON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

## 30.7 Falling Edge and Forward Dead Band

CWG1DBF controls the dead-band time at the leading edge of CWG1B (Half-Bridge mode) or the leading edge of CWG1D (Full-Bridge mode). The CWG1DBF value is double-buffered. When EN = 0, the CWG1DBF register is loaded immediately when CWG1DBF is written. When EN = 1 then software must set the LD bit of the CWG1CON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

Refer to Figure 30-6 and Figure 30-7 for examples.

| U-0             | U-0                                          | R-x                                    | U-0        | R/W-0/0        | R/W-0/0                            | R/W-0/0          | R/W-0/0      |  |

|-----------------|----------------------------------------------|----------------------------------------|------------|----------------|------------------------------------|------------------|--------------|--|

|                 | —                                            | IN                                     |            | POLD           | POLC                               | POLB             | POLA         |  |

| bit 7           |                                              |                                        |            |                |                                    |                  | bit C        |  |

|                 |                                              |                                        |            |                |                                    |                  |              |  |

| Legend:         |                                              |                                        |            |                |                                    |                  |              |  |

| R = Readab      | ole bit                                      | W = Writable                           | bit        | U = Unimpler   | U = Unimplemented bit, read as '0' |                  |              |  |

| u = Bit is un   | changed                                      | x = Bit is unkr                        | nown       | -n/n = Value a | at POR and BO                      | R/Value at all o | other Resets |  |

| '1' = Bit is se | et                                           | '0' = Bit is cle                       | ared       | q = Value de   | pends on condit                    | ion              |              |  |

|                 |                                              |                                        |            |                |                                    |                  |              |  |

| bit 7-6         | Unimplem                                     | ented: Read as '                       | 0'         |                |                                    |                  |              |  |

| bit 5           | IN: CWG Ir                                   | IN: CWG Input Value bit                |            |                |                                    |                  |              |  |

| bit 4           | Unimplem                                     | Unimplemented: Read as '0'             |            |                |                                    |                  |              |  |

| bit 3           | bit 3 <b>POLD:</b> CWG1D Output Polarity bit |                                        |            |                |                                    |                  |              |  |

|                 | 1 = Signal                                   | 1 = Signal output is inverted polarity |            |                |                                    |                  |              |  |

|                 | 0 = Signal                                   | output is normal                       | polarity   |                |                                    |                  |              |  |

| bit 2           | POLC: CW                                     | POLC: CWG1C Output Polarity bit        |            |                |                                    |                  |              |  |

|                 | 0                                            | output is inverted                     |            |                |                                    |                  |              |  |

|                 | 0 = Signal                                   | output is normal                       | polarity   |                |                                    |                  |              |  |

| bit 1           | t 1 POLB: CWG1B Output Polarity bit          |                                        |            |                |                                    |                  |              |  |

|                 |                                              | output is inverted                     |            |                |                                    |                  |              |  |

|                 | 0 = Signal                                   | output is normal                       | polarity   |                |                                    |                  |              |  |

| bit 0           | POLA: CW                                     | /G1A Output Pola                       | rity bit   |                |                                    |                  |              |  |

|                 | 1 = Signal                                   | output is inverted                     | l polarity |                |                                    |                  |              |  |

#### **REGISTER 30-2:** CWG1CON1: CWG1 CONTROL REGISTER 1

0 = Signal output is normal polarity

© 2016 Microchip Technology Inc.

#### **Instruction Descriptions** 36.3

| ADDFSR           | Add Literal to FSRn                                                                              |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                         |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                            |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                                  |

| Status Affected: | None                                                                                             |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair.    |

|                  | FSRn is limited to the range<br>0000h-FFFFh. Moving beyond these<br>bounds will cause the FSR to |

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) + k \to (W)$                                                                                             |

| Status Affected: | C, DC, Z                                                                                                      |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |

wrap-around.

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                               |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]ASRF f{,d}                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                                                         |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                            |

| Status Affected: | C, Z                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in |

register 'f'.

| ADDWFC A | DD W and CARRY bit to f |

|----------|-------------------------|

|----------|-------------------------|

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (W) + (f) + (C) $\rightarrow$ dest                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |

#### 39.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 39.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

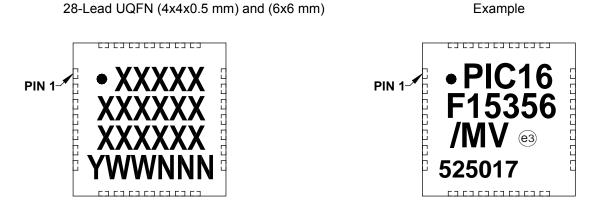

### 40.1 Package Marking Information (Continued)

| Legend | : XXX                                                                                                                                                     | Customer-specific information                              |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

|        | Y                                                                                                                                                         | Year code (last digit of calendar year)                    |

|        | ΥY                                                                                                                                                        | Year code (last 2 digits of calendar year)                 |

|        | WW                                                                                                                                                        | Week code (week of January 1 is week '01')                 |

|        | NNN                                                                                                                                                       | Alphanumeric traceability code                             |

|        |                                                                                                                                                           | Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)   |

|        | *                                                                                                                                                         | This package is Pb-free. The Pb-free JEDEC designator (e3) |

|        |                                                                                                                                                           | can be found on the outer packaging for this package.      |

|        |                                                                                                                                                           |                                                            |

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available |                                                            |

|        |                                                                                                                                                           |                                                            |

|        | characters for customer-specific information.                                                                                                             |                                                            |

|        |                                                                                                                                                           |                                                            |