Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

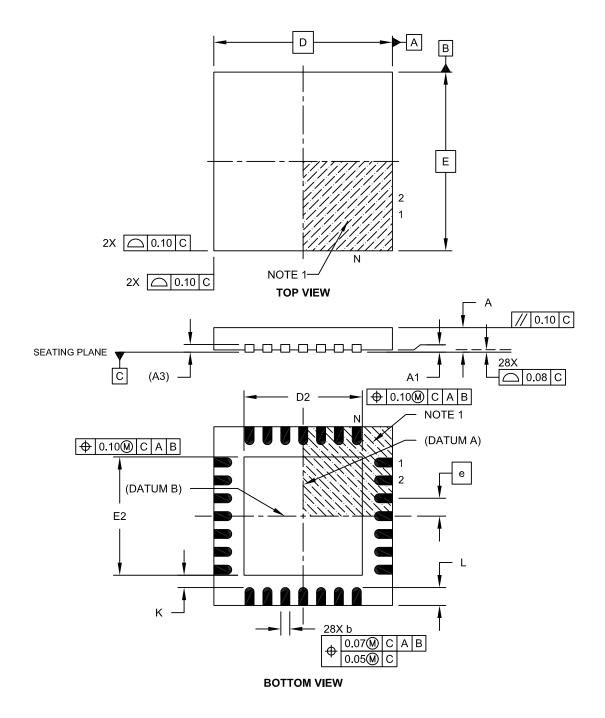

| Package / Case             | 48-TQFP                                                                     |

| Supplier Device Package    | 48-TQFP (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15385-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1: PIC16(L)F153XX FAMILY TYPES

| Device         | Data Sheet Index | Program Flash Memory (KW) | Program Flash Memory (KB) | Storage Area Flash (B) | Data SRAM<br>(bytes) | I/OPins | 10-bit ADC | 5-bit DAC | Comparator | 8-bit/ (with HLT) Timer | 16-bit Timer | Window Watchdog Timer | CCP/10-bit PWM | CWG | NCO | CLC | Zero-Cross Detect | Temperature Indicator | Memory Access Partition | <b>Device Information Area</b> | EUSART/ I <sup>2</sup> C-SPI | Peripheral Pin Select | Peripheral Module Disable | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------|---------------------------|------------------------|----------------------|---------|------------|-----------|------------|-------------------------|--------------|-----------------------|----------------|-----|-----|-----|-------------------|-----------------------|-------------------------|--------------------------------|------------------------------|-----------------------|---------------------------|----------------------|

| PIC16(L)F15313 | (C)              | 2                         | 3.5                       | 224                    | 256                  | 6       | 5          | 1         | 1          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Y                       | Y                              | 1/1                          | Y                     | Y                         | Ι                    |

| PIC16(L)F15323 | (C)              | 2                         | 3.5                       | 224                    | 256                  | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 1/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15324 | (D)              | 4                         | 7                         | 224                    | 512                  | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15325 | <b>(B)</b>       | 8                         | 14                        | 224                    | 1024                 | 12      | 11         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15344 | (D)              | 4                         | 7                         | 224                    | 512                  | 18      | 17         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15345 | <b>(B)</b>       | 8                         | 14                        | 224                    | 1024                 | 18      | 17         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/1                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15354 | (A)              | 4                         | 7                         | 224                    | 512                  | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15355 | (A)              | 8                         | 14                        | 224                    | 1024                 | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15356 | (E)              | 16                        | 28                        | 224                    | 2048                 | 25      | 24         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15375 | (E)              | 8                         | 14                        | 224                    | 1024                 | 36      | 35         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         |                      |

| PIC16(L)F15376 | (E)              | 16                        | 28                        | 224                    | 2048                 | 36      | 35         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Υ                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15385 | (E)              | 8                         | 14                        | 224                    | 1024                 | 44      | 43         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Υ                       | Υ                              | 2/2                          | Υ                     | Υ                         | Ι                    |

| PIC16(L)F15386 | (E)              | 16                        | 28                        | 224                    | 2048                 | 44      | 43         | 1         | 2          | 1                       | 2            | Υ                     | 2/4            | 1   | 1   | 4   | Y                 | Y                     | Y                       | Y                              | 2/2                          | Υ                     | Y                         | Ι                    |

**Note 1:** I - Debugging integrated on chip.

#### Data Sheet Index:

| ote: | For other small form | factor package availability and marking information, visit v |

|------|----------------------|--------------------------------------------------------------|

| E:   | DS40001866           | PIC16(L)F15356/75/76/85/86 Data Sheet, 28/40/48-Pin          |

| D:   | Future Release       | PIC16(L)F15324/44 Data Sheet, 14/20-Pin                      |

| C:   | Future Release       | PIC16(L)F15313/23 Data Sheet, 8/14-Pin                       |

| B:   | DS40001865           | PIC16(L)F15325/45 Data Sheet, 14/20-Pin                      |

| A:   | DS40001853           | PIC16(L)F15354/5 Data Sheet, 28-Pin                          |

|      |                      |                                                              |

**Note:** For other small form-factor package availability and marking information, visit www.microchip.com/packaging or contact your local sales office.

| IABL              | <b>= 4</b> : |             | 40/        | 44-r        |                      | LUCA      |                  | ADLE (P |          | 5375, 1                       |                     | L)F15570 | )                   |                               |      |                           |                       |      |                             |         |                 |

|-------------------|--------------|-------------|------------|-------------|----------------------|-----------|------------------|---------|----------|-------------------------------|---------------------|----------|---------------------|-------------------------------|------|---------------------------|-----------------------|------|-----------------------------|---------|-----------------|

| VO <sup>(2)</sup> | 40-Pin PDIP  | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC                  | Reference | Comparator       | NCO     | DAC      | Timers                        | ССР                 | MWd      | CWG                 | MSSP                          | ZCD  | EUSART                    | CLC                   | CLKR | Interrupt                   | Pull-up | Basic           |

| RA0               | 2            | 17          | 19         | 19          | ANA0                 | -         | C1IN0-<br>C2IN0- | _       | _        | —                             | —                   | _        | -                   | -                             | —    | —                         | CLCIN0 <sup>(1)</sup> | -    | IOCA0                       | Y       | _               |

| RA1               | 3            | 18          | 20         | 20          | ANA1                 | —         | C1IN1-<br>C2IN1- | _       | —        | —                             | _                   |          | _                   |                               | —    | _                         | CLCIN1 <sup>(1)</sup> |      | IOCA1                       | Y       | _               |

| RA2               | 4            | 19          | 21         | 21          | ANA2                 | —         | C1IN0+<br>C2IN0+ | —       | DAC1OUT1 | —                             | _                   |          | —                   | -                             | —    | -                         | -                     |      | IOCA2                       | Y       | —               |

| RA3               | 5            | 20          | 22         | 22          | ANA3                 | VREF+     | C1IN1+           | —       | DACREF+  | —                             | -                   | -        | -                   |                               | —    | -                         | -                     |      | IOCA3                       | Y       | Ι               |

| RA4               | 6            | 21          | 23         | 23          | ANA4                 | _         | _                | _       | _        | TOCKI(1)                      | _                   | _        | _                   | _                             | _    | _                         | _                     | -    | IOCA4                       | Y       | _               |

| RA5               | 7            | 22          | 24         | 24          | ANA5                 | _         | _                | _       | _        | T1G <sup>(1)</sup>            | _                   | _        | _                   | SS1 <sup>(1)</sup>            | _    | -                         | -                     | _    | IOCA5                       | Y       | _               |

| RA6               | 14           | 29          | 33         | 31          | ANA6                 | -         | —                | -       | -        | —                             | _                   | -        | -                   | -                             | —    | -                         | -                     | _    | IOCA6                       | Y       | CLKOUT/<br>OSC1 |

| RA7               | 13           | 28          | 32         | 30          | ANA7                 | -         | —                | -       | -        | —                             | _                   | _        | -                   | _                             | —    | _                         | -                     | _    | IOCA7                       | Y       | CLKIN/<br>OSC2  |

| RB0               | 33           | 8           | 9          | 8           | ANB0                 | -         | C2IN1+           | -       | -        | —                             | _                   | -        | CWG1 <sup>(1)</sup> | SS2 <sup>(1)</sup>            | ZCD1 | -                         | -                     | _    | INT <sup>(1)</sup><br>IOCB0 | Y       | Ι               |

| RB1               | 34           | 9           | 10         | 9           | ANB1                 | _         | C1IN3-<br>C2IN3- | _       | —        | —                             | _                   |          | _                   | SCL1<br>SCK1 <sup>(1,4)</sup> | —    | _                         | —                     |      | IOCB1                       | Y       | _               |

| RB2               | 34           | 10          | 11         | 10          | ANB2                 | _         | —                | —       | —        | —                             | —                   | _        | —                   | SDA1<br>SDI1 <sup>(1,4)</sup> | —    | _                         | —                     |      | IOCB2                       | Y       | —               |

| RB3               | 36           | 11          | 12         | 11          | ANB3                 | _         | C1IN2-<br>C2IN2- | _       | —        | —                             | _                   |          | _                   |                               | —    | _                         | —                     |      | IOCB3                       | Y       | _               |

| RB4               | 37           | 12          | 14         | 14          | ANB4<br>ADACT<br>(1) | -         | _                | —       | —        | _                             | _                   |          | _                   |                               | _    | _                         | -                     | _    | IOCB4                       | Y       | _               |

| RB5               | 38           | 13          | 15         | 15          | ANB5                 | —         | —                | —       | —        | —                             | -                   | -        | -                   |                               | —    | -                         | -                     |      | IOCB5                       | Y       | Ι               |

| RB6               | 39           | 14          | 16         | 16          | ANB6                 | -         | —                | -       | _        | —                             |                     | -        |                     | -                             | —    | TX2<br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> |      | IOCB6                       | Y       | ICSPCLK         |

| RB7               | 40           | 15          | 17         | 17          | ANB7                 | -         | —                | —       | DAC1OUT2 | —                             | —                   | -        | —                   | _                             | —    | RX2<br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> |      | IOCB7                       | Y       | ICSPDAT         |

| RC0               | 15           | 30          | 34         | 32          | ANC0                 | —         | —                | —       | —        | SOSCO<br>T1CKI <sup>(1)</sup> |                     |          | _                   | —                             | —    | -                         | -                     |      | IOCC0                       | Y       | —               |

| RC1               | 16           | 31          | 35         | 35          | ANC1                 | _         | —                | _       | _        | SOSCI                         | CCP2 <sup>(1)</sup> | _        | —                   | _                             | —    | -                         | —                     | -    | IOCC1                       | Υ       | _               |

| RC2               | 17           | 32          | 36         | 36          | ANC2                 | -         | —                | —       | _        | _                             | CCP1 <sup>(1)</sup> | —        | —                   | _                             | _    | _                         | —                     | _    | IOCC2                       | Υ       | _               |

TABLE 4: 40/44-PIN ALLOCATION TABLE (PIC16(L)F15375, PIC16(L)F15376)

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

| Н |          |

|---|----------|

|   | _        |

|   |          |

|   |          |

|   |          |

|   |          |

|   | <b>O</b> |

|   |          |

|   |          |

|   | Ŧ        |

|   |          |

|   |          |

|   |          |

|   | 35       |

|   |          |

|   | 5        |

|   |          |

|   | UT I     |

|   |          |

|   |          |

|   | 6        |

| I |          |

| I | 85/      |

| I |          |

| I | 8        |

| I | ő        |

| н |          |

Preliminary

| I/O <sup>(2)</sup> | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO | DAC | Timers              | CCP                 | MWM | SWC | ASSM                          | ZCD | EUSART                    | CLC | CLKR | Interrupt | Pull-up | Basic       |

|--------------------|------------------|------|-----------|------------|-----|-----|---------------------|---------------------|-----|-----|-------------------------------|-----|---------------------------|-----|------|-----------|---------|-------------|

| RC2                | 40               | ANC2 | —         | —          | —   | _   | —                   | CCP1 <sup>(1)</sup> | -   | —   | —                             |     | —                         | -   | —    | IOCC2     | Y       | —           |

| RC3                | 41               | ANC3 | -         | -          | -   | _   | T2IN <sup>(1)</sup> | -                   | _   | _   | SCL1<br>SCL2 <sup>(1,4)</sup> | _   | —                         | _   | -    | IOCC3     | Y       | -           |

| RC4                | 46               | ANC4 | -         | _          | _   | _   | -                   | —                   | _   | -   | SDA1<br>SDI1 <sup>(1,4)</sup> | _   | —                         | _   | _    | IOCC4     | Y       | _           |

| RC5                | 47               | ANC5 | _         | —          | _   | _   | _                   | _                   | _   | _   | _                             | _   | —                         | _   | _    | IOCC5     | Υ       | _           |

| RC6                | 48               | ANC6 | -         | —          | —   | _   | _                   | —                   | _   | —   | —                             |     | TX1<br>CK1 <sup>(1)</sup> | _   | -    | IOCC6     | Y       | —           |

| RC7                | 1                | ANC7 | -         | —          | —   | _   | —                   | —                   | _   | —   | _                             |     | RX1<br>DT1 <sup>(1)</sup> | _   | -    | IOCC7     | Y       | —           |

| RD0                | 42               | AND0 | -         | —          | -   | -   | -                   | —                   | —   | -   | SCK2<br>SCL2 <sup>(1,4)</sup> | —   | -                         | —   | -    | -         | Y       | —           |

| RD1                | 43               | AND1 | —         | —          | —   |     | —                   | —                   | _   | —   | SDA2<br>SDI2 <sup>(1,4)</sup> |     | _                         | _   | -    | —         | Y       | —           |

| RD2                | 44               | AND2 | _         | _          | —   | _   | _                   | _                   | -   | _   | _                             | _   | —                         | -   | _    | _         | Y       | _           |

| RD3                | 45               | AND3 | _         | _          | _   | _   | _                   | _                   |     | _   | _                             |     | _                         |     | —    | _         | Y       | _           |

| RD4                | 2                | AND4 | _         | _          | —   | _   | _                   | —                   | _   | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RD5                | 3                | AND5 | _         | _          | —   | _   | _                   | —                   | -   | _   | _                             | -   | _                         | -   | _    | _         | Υ       | _           |

| RD6                | 4                | AND6 | _         | _          | —   | _   | _                   | _                   | _   | —   | _                             | _   | _                         | _   | _    | —         | Υ       | _           |

| RD7                | 5                | AND7 | —         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE0                | 27               | ANE0 | -         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE1                | 28               | ANE1 | _         | —          | —   | _   | -                   | —                   | _   | -   | _                             | _   | _                         |     | —    | -         | Υ       | —           |

| RE2                | 29               | ANE2 | _         | —          | —   | —   | —                   | —                   | —   | —   | —                             | _   | —                         | —   | —    | —         | Y       | —           |

| RE3                | 20               | _    | -         | —          | —   |     | —                   | —                   | _   | —   | —                             | _   | —                         | _   | _    | IOCE3     | Y       | MCLR<br>VPP |

| RF0                | 36               | ANF0 | _         | _          | —   | _   | —                   | _                   | _   | —   | _                             |     | _                         | _   | _    | —         | Y       | _           |

| RF1                | 37               | ANF1 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF2                | 38               | ANF2 | _         | —          | —   | _   | -                   | _                   | _   | —   | —                             | _   | —                         | _   | —    | —         | Υ       | _           |

| RF3                | 39               | ANF3 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF4                | 12               | ANF4 | —         | —          | —   |     | —                   | —                   |     | _   | _                             |     | _                         |     | —    | —         | Υ       | —           |

TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

| Name                                                                      | Function              | Input<br>Type | Output Type | Description                                                    |

|---------------------------------------------------------------------------|-----------------------|---------------|-------------|----------------------------------------------------------------|

| RB3/ANB3/C1IN2-/C2IN2-/IOCB3                                              | RB3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                           |

|                                                                           | ANB3                  | AN            | _           | ADC Channel B3 input.                                          |

|                                                                           | C1IN2-                | AN            | _           | Comparator 1 negative input.                                   |

|                                                                           | C2IN2-                | AN            | _           | Comparator 2 negative input.                                   |

|                                                                           | IOCB3                 | TTL/ST        | -           | Interrupt-on-change input.                                     |

| RB4/ANB4/ADACT <sup>(1)</sup> /IOCB4                                      | RB4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                           |

|                                                                           | ANB4                  | AN            | -           | ADC Channel B4 input.                                          |

|                                                                           | ADACT <sup>(1)</sup>  | TTL/ST        | -           | ADC Auto-Conversion Trigger input.                             |

|                                                                           | IOCB4                 | TTL/ST        | _           | Interrupt-on-change input.                                     |

| RB5/ANB5/T1G <sup>(1)</sup> /IOCB5                                        | RB5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                           |

|                                                                           | ANB5                  | AN            | -           | ADC Channel B5 input.                                          |

|                                                                           | T1G <sup>(1)</sup>    | ST            | _           | Timer1 Gate input.                                             |

|                                                                           | IOCB5                 | TTL/ST        | _           | Interrupt-on-change input.                                     |

| RB6/ANB6/CLCIN2 <sup>(1)</sup> /IOCB6/TX2/<br>CK2 <sup>(3)</sup> /ICSPCLK | RB6                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                           |

| JK2 <sup>w</sup> /IUSPULK                                                 | ANB6                  | AN            | _           | ADC Channel B6 input.                                          |

|                                                                           | CLCIN2 <sup>(1)</sup> | TTL/ST        | -           | Configurable Logic Cell source input.                          |

|                                                                           | IOCB6                 | TTL/ST        | -           | Interrupt-on-change input.                                     |

|                                                                           | TX2                   | —             | CMOS        | EUSART2 asynchronous.                                          |

|                                                                           | CK2 <sup>(3)</sup>    | TTL/ST        | CMOS/OD     | EUSART2 synchronous mode clock input/output.                   |

|                                                                           | ICSPCLK               | ST            | -           | In-Circuit Serial Programming™ and debugging clock inpu        |

| RB7/ANB7/RX2/DT2/CLCIN3 <sup>(1)</sup> /                                  | RB7                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                           |

| IOCB7/DAC1OUT2/ICSPDAT                                                    | ANB7                  | AN            | -           | ADC Channel B7 input.                                          |

|                                                                           | CLCIN3 <sup>(1)</sup> | TTL/ST        | -           | Configurable Logic Cell source input.                          |

|                                                                           | IOCB7                 | TTL/ST        | _           | Interrupt-on-change input.                                     |

|                                                                           | RX2 <sup>(1)</sup>    | TTL/ST        | _           | EUSART2 Asynchronous mode receiver data input.                 |

|                                                                           | DT2 <sup>(3)</sup>    | TTL/ST        | CMOS/OD     | EUSART2 Synchronous mode data input/output.                    |

|                                                                           | DAC1OUT2              | _             | AN          | Digital-to-Analog Converter output.                            |

|                                                                           | ICSPDAT               | ST            | CMOS        | In-Circuit Serial Programming™ and debugging data inpu output. |

| RC0/ANC0/T1CKI <sup>(1)</sup> /IOCC0/SOSCO                                | RC0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                           |

|                                                                           | ANC0                  | AN            | _           | ADC Channel C0 input.                                          |

|                                                                           | T1CKI <sup>(1)</sup>  | TTL/ST        | _           | Timer1 external digital clock input.                           |

|                                                                           | IOCC0                 | TTL/ST        | _           | Interrupt-on-change input.                                     |

|                                                                           | SOSCO                 | _             | AN          | 32.768 kHz secondary oscillator crystal driver output.         |

**TABLE 1-2:** PIC16(L)F15356 PINOUT DESCRIPTION (CONTINUED)

Note

Schmitt Trigger input of output

Schmitt Trigger input with CMOS levels

Crystal levels

$\begin{aligned} HV &= \text{Airadeg input of output} & \text{Since on the comparison of the comparison o$ 1:

2: options as described in Table 15-3. This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and

3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

# REGISTER 10-10: PIR0: PERIPHERAL INTERRUPT STATUS REGISTER 0

| U-0              | U-0   | R/W/HS-0/0        | R-0  | U-0                                | U-0           | U-0            | R/W/HS-0/0          |  |  |  |  |

|------------------|-------|-------------------|------|------------------------------------|---------------|----------------|---------------------|--|--|--|--|

| _                |       | - TMR0IF          |      | _                                  |               |                | INTF <sup>(1)</sup> |  |  |  |  |

| bit 7            |       |                   |      | ·                                  |               |                | bit 0               |  |  |  |  |

|                  |       |                   |      |                                    |               |                |                     |  |  |  |  |

| Legend:          |       |                   |      |                                    |               |                |                     |  |  |  |  |

| R = Readable b   | oit   | W = Writable I    | bit  | U = Unimplemented bit, read as '0' |               |                |                     |  |  |  |  |

| u = Bit is uncha | anged | x = Bit is unkn   | own  | -n/n = Value a                     | at POR and BO | R/Value at all | other Resets        |  |  |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared | HS= Hardware Set                   |               |                |                     |  |  |  |  |

|                  |       |                   |      |                                    |               |                |                     |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | TMR0IF: Timer0 Overflow Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = Timer0 register has overflowed (must be cleared in software)</li> <li>0 = Timer0 register did not overflow</li> </ul>                                                  |

| bit 4   | IOCIF: Interrupt-on-Change Interrupt Flag bit (read-only) <sup>(2)</sup>                                                                                                            |

|         | <ul> <li>1 = One or more of the IOCAF-IOCEF register bits are currently set, indicating an enabled edge was<br/>detected by the IOC module.</li> </ul>                              |

|         | 0 = None of the IOCAF-IOCEF register bits are currently set                                                                                                                         |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                                                                          |

| bit 0   | INTF: INT External Interrupt Flag bit <sup>(1)</sup>                                                                                                                                |

|         | <ul> <li>1 = The INT external interrupt occurred (must be cleared in software)</li> <li>0 = The INT external interrupt did not occur</li> </ul>                                     |

| Note 1: | The External Interrupt GPIO pin is selected by INTPPS (Register 15-1).                                                                                                              |

| 2:      | The IOCIF bit is the logical OR of all the IOCAF-IOCEF flags. Therefore, to clear the IOCIF flag, application firmware must clear all of the lower level IOCAF-IOCEF register bits. |

| Note:   | Interrupt flag bits are set when an interrupt                                                                                                                                       |

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state     |

|       | of its corresponding enable bit or the        |

|       | Global Enable bit, GIE, of the INTCON         |

|       | register. User software should ensure the     |

|       | appropriate interrupt flag bits are clear     |

|       | prior to enabling an interrupt.               |

© 2016 Microchip Technology Inc.

| Name      | Bit 7   | Bit 6                                                                             | Bit 5                          | Bit 4 | Bit 3     | Bit 2     | Bit 1    | Bit 0  | Register<br>on Page |  |  |           |  |  |  |  |

|-----------|---------|-----------------------------------------------------------------------------------|--------------------------------|-------|-----------|-----------|----------|--------|---------------------|--|--|-----------|--|--|--|--|

| OSCCON1   | _       |                                                                                   | NOSC<2:0>                      |       |           | NDIV<3:0> |          |        |                     |  |  |           |  |  |  |  |

| OSCCON2   | —       | COSC<2:0>                                                                         |                                |       |           | CDIV<3:0> |          |        |                     |  |  | CDIV<3:0> |  |  |  |  |

| OSCCON3   | CSWHOLD | SOSCPWR                                                                           | —                              | ORDY  | NOSCR     | —         | —        | -      | 136                 |  |  |           |  |  |  |  |

| PCON0     | STKOVF  | STKUNF                                                                            | WDTWV                          | RWDT  | RMCLR     | RI        | POR      | BOR    | 124                 |  |  |           |  |  |  |  |

| STATUS    | _       | —                                                                                 | _                              | TO    | PD        | Z         | DC       | С      | 54                  |  |  |           |  |  |  |  |

| WDTCON0   | —       | —                                                                                 |                                |       | WDTPS<4:0 | )>        |          | SWDTEN | 175                 |  |  |           |  |  |  |  |

| WDTCON1   | —       | V                                                                                 | VDTCS<2:0>                     |       | —         | WI        | NDOW<2:0 | >      | 176                 |  |  |           |  |  |  |  |

| WDTPSL    |         |                                                                                   |                                | PSCN  | T<7:0>    |           |          |        |                     |  |  |           |  |  |  |  |

| WDTPSH    |         |                                                                                   |                                | PSCN  | T<15:8>   | <15:8>    |          |        |                     |  |  |           |  |  |  |  |

| WDTTMR    | —       |                                                                                   | WDTTMR<4:0> STATE PSCNT<17:16> |       |           |           |          |        |                     |  |  |           |  |  |  |  |

| Lonondi - |         | unimplemented leastions read as '0'. Checked calls are not used by Watehday Timer |                                |       |           |           |          |        |                     |  |  |           |  |  |  |  |

# TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 12-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5   | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1    | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|------------|----------|----------|----------|------------|----------|---------------------|

|         | 13:8 |         | _       | FCMEN      | _        | CSWEN    | _        | _          | CLKOUTEN | 100                 |

| CONFIG1 | 7:0  | _       | F       | RSTOSC<2:0 | >        | _        | F        | EXTOSC<2:0 | >        | 102                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

#### EXAMPLE 13-3: ERASING ONE ROW OF PROGRAM FLASH MEMORY (PFM)

|                |                  | ( )                                                                                                   |

|----------------|------------------|-------------------------------------------------------------------------------------------------------|

| ; 1.A valid ad |                  | umes the following:<br>e row is loaded in variables ADDRH:ADDRL<br>common RAM (locations 0x70 - 0x7F) |

| BANKSEL        | NVMADRL          |                                                                                                       |

| MOVF           | ADDRL,W          |                                                                                                       |

| MOVWF          | NVMADRL          | ; Load lower 8 bits of erase address boundary                                                         |

| MOVF           | ADDRH,W          |                                                                                                       |

| MOVWF          | NVMADRH          | ; Load upper 6 bits of erase address boundary                                                         |

| BCF            | NVMCON1, NVMREGS | ; Choose PFM memory area                                                                              |

| BSF            | NVMCON1, FREE    | ; Specify an erase operation                                                                          |

| BSF            | NVMCON1,WREN     | ; Enable writes                                                                                       |

| BCF            | INTCON,GIE       | ; Disable interrupts during unlock sequence                                                           |

| ;              | REQ              | UIRED UNLOCK SEQUENCE:                                                                                |

| MOVLW          | 55h              | ; Load 55h to get ready for unlock sequence                                                           |

| MOVWF          | NVMCON2          | ; First step is to load 55h into NVMCON2                                                              |

| MOVLW          | AAh              | ; Second step is to load AAh into W                                                                   |

| MOVWF          | NVMCON2          | ; Third step is to load AAh into NVMCON2                                                              |

| BSF            | NVMCON1,WR       | ; Final step is to set WR bit                                                                         |

| ;              |                  |                                                                                                       |

| BSF            | INTCON, GIE      | ; Re-enable interrupts, erase is complete                                                             |

| BCF            | NVMCON1,WREN     | ; Disable writes                                                                                      |

# TABLE 13-2: NVM ORGANIZATION AND ACCESS INFORMATION

|                    | Master Values                                |                       | N                           | VMREG Acce       | ess                   | FSR            | FSR Access                    |  |

|--------------------|----------------------------------------------|-----------------------|-----------------------------|------------------|-----------------------|----------------|-------------------------------|--|

| Memory<br>Function | Program<br>Counter (PC),<br>ICSP™<br>Address | Memory<br>Type        | NVMREGS<br>bit<br>(NVMCON1) | NVMADR<<br>14:0> | Allowed<br>Operations | FSR<br>Address | FSR<br>Programming<br>Address |  |

| Reset Vector       | 0000h                                        |                       | 0                           | 0000h            |                       | 8000h          |                               |  |

| User Memory        | 0001h                                        |                       | 0                           | 0001h            |                       | 8001h          |                               |  |

| User Memory        | 0003h                                        |                       | 0                           | 0003h            |                       | 8003h          |                               |  |

| INT Vector         | 0004h                                        | PFM                   | 0                           | 0004h            | Read<br>Write         | 8004h          | Read-0nly                     |  |

|                    | 0005h                                        |                       |                             | 0005h            | White                 | 8005h          |                               |  |

| User Memory        | 1FFFh                                        |                       | 0                           | 1FFFh            |                       | 9FFFh          |                               |  |

|                    | 3FFFh                                        |                       |                             | 3FFFh            |                       | BFFFh          |                               |  |

|                    | 8000h                                        | PFM                   | 1                           | 0000h            | Read                  |                |                               |  |

| User ID            | 8003h                                        | PEM                   | 1                           | 0003h            | Write                 |                |                               |  |

| Reserved           | 8004h                                        | —                     | -                           | 0004h            | _                     |                |                               |  |

| Rev ID             | 8005h                                        |                       | 1                           | 0005h            | Deed Only             |                |                               |  |

| Device ID          | 8006h                                        |                       | 1                           | 0006h            | Read-Only             | No             | A                             |  |

| CONFIG1            | 8007h                                        |                       | 1                           | 0007h            |                       | INO            | Access                        |  |

| CONFIG2            | 8008h                                        | PFM                   | 1                           | 0008h            | <b>_</b> .            |                |                               |  |

| CONFIG3            | 8009h                                        |                       | 1                           | 0009h            | Read<br>Write         |                |                               |  |

| CONFIG4            | 800Ah                                        | 1                     | 1                           | 000Ah            | VVIILE                |                |                               |  |

| CONFIG5            | 800Bh                                        |                       | 1                           | 000Bh            |                       |                |                               |  |

| DIA and DCI        | 8100h-82FFh                                  | PFM and<br>Hard coded | 1                           | 0100h-<br>02FFh  | Read-Only             | No             | Access                        |  |

# 14.12 PORTF Registers

Note: Present only on PIC16(L)F15385/86.

## 14.12.1 DATA REGISTER

PORTF is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISF (Register 14-42). Setting a TRISF bit (= 1) will make the corresponding PORTF pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISF bit (= 0) will make the corresponding PORTF pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize an I/O port.

Reading the PORTF register (Register 14-41) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATF).

The PORT data latch LATF (Register 14-43) holds the output port data, and contains the latest value of a LATF or PORTF write.

#### 14.12.2 DIRECTION CONTROL

The TRISF register (Register 14-42) controls the PORTF pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISF register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.12.3 INPUT THRESHOLD CONTROL

The INLVLF register (Register 14-48) controls the input voltage threshold for each of the available PORTF input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTF register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 14.12.4 OPEN-DRAIN CONTROL

The ODCONF register (Register 14-46) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONF bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONF bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

# 14.12.5 SLEW RATE CONTROL

The SLRCONF register (Register 14-47) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONF bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONF bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

### 14.12.6 ANALOG CONTROL

The ANSELF register (Register 14-44) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELF bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELF bits has no effect on digital output functions. A pin with TRIS clear and ANSELF set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELF bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 14.12.7 WEAK PULL-UP CONTROL

The WPUF register (Register 14-45) controls the individual weak pull-ups for each port pin.

### 14.12.8 PORTF FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| Output Signal | RxyPPS                   | Remappable to Pins of PORTx<br>PIC16(L)F15385/86 |       |       |       |       |       |  |  |

|---------------|--------------------------|--------------------------------------------------|-------|-------|-------|-------|-------|--|--|

| Name          | RxyPP5<br>Register Value |                                                  |       |       |       |       |       |  |  |

|               | 5                        | PORTA                                            | PORTB | PORTC | PORTD | PORTE | PORTF |  |  |

| CLKR          | 0x1B                     |                                                  | •     |       |       | •     |       |  |  |

| NCO1OUT       | 0x1A                     | •                                                |       |       | •     |       |       |  |  |

| TMR0          | 0x19                     |                                                  |       | •     |       |       | •     |  |  |

| SDO2/SDA2     | 0x18                     |                                                  | •     |       | •     |       |       |  |  |

| SCK2/SCL2     | 0X17                     |                                                  | •     |       | •     |       |       |  |  |

| SDO1/SDA1     | 0x16                     |                                                  | •     | •     |       |       |       |  |  |

| SCK1/SCL1     | 0x15                     |                                                  | •     | •     |       |       |       |  |  |

| C2OUT         | 0x14                     | ٠                                                |       |       |       | •     |       |  |  |

| C1OUT         | 0x13                     | ٠                                                |       |       | •     |       |       |  |  |

| DT2           | 0x12                     |                                                  | •     | •     |       |       |       |  |  |

| TX2/CK2       | 0x11                     |                                                  | •     |       | •     |       |       |  |  |

| DT1           | 0x10                     |                                                  |       | •     |       |       | ٠     |  |  |

| TX1/CK1       | 0x0F                     |                                                  |       | •     |       |       | ٠     |  |  |

| PWM6OUT       | 0x0E                     | ٠                                                |       |       | •     |       |       |  |  |

| PWM5OUT       | 0x0D                     | ٠                                                |       |       |       |       | •     |  |  |

| PWM4OUT       | 0x0C                     |                                                  | •     |       | •     |       |       |  |  |

| PWM3OUT       | 0x0B                     |                                                  | •     |       | •     |       |       |  |  |

| CCP2          | 0x0A                     |                                                  |       | •     |       |       | •     |  |  |

| CCP1          | 0x09                     |                                                  |       | •     |       |       | •     |  |  |

| CWG1D         | 0x08                     |                                                  | •     |       | •     |       |       |  |  |

| CWG1C         | 0x07                     |                                                  | •     |       | •     |       |       |  |  |

| CWG1B         | 0x06                     |                                                  | •     |       | •     |       |       |  |  |

| CWG1A         | 0x05                     |                                                  | •     | •     |       |       |       |  |  |

| CLC4OUT       | 0x04                     |                                                  | •     |       | •     |       |       |  |  |

| CLC3OUT       | 0x03                     |                                                  | •     |       | •     |       |       |  |  |

| CLC2OUT       | 0x02                     | •                                                |       |       |       |       | •     |  |  |

| CLC1OUT       | 0x01                     | •                                                |       |       |       |       | •     |  |  |

# TABLE 15-7: PPS OUTPUT SIGNAL ROUTING OPTIONS (PIC16(L)F15385/86)

| ADC Clock Period (TAD) |           |                             | Device Frequency (Fosc)     |                             |                             |                               |                             |

|------------------------|-----------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|-----------------------------|

| ADC<br>Clock Source    | ADCS<2:0> | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                         | 1 MHz                       |

| Fosc/2                 | 000       | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>         | 2.0 μs                      |

| Fosc/4                 | 100       | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                        | 4.0 μs                      |

| Fosc/8                 | 001       | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                        | 8.0 μs <sup>(3)</sup>       |

| Fosc/16                | 101       | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                        | 16.0 μs <sup>(3)</sup>      |

| Fosc/32                | 010       | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>         | 32.0 μs <sup>(2)</sup>      |

| Fosc/64                | 110       | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <b><sup>(2)</sup></b> | 64.0 μs <sup>(2)</sup>      |

| ADCRC                  | x11       | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup> |

# TABLE 20-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

Note 1: See TAD parameter for ADCRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

**4:** The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the ADCRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

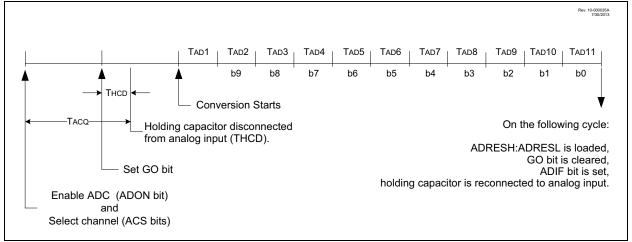

# FIGURE 20-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

| TABLE 20-3 | . 000000 |        |           |        |          |         |          | 1      | 1                   |

|------------|----------|--------|-----------|--------|----------|---------|----------|--------|---------------------|

| Name       | Bit 7    | Bit 6  | Bit 5     | Bit 4  | Bit 3    | Bit 2   | Bit 1    | Bit 0  | Register<br>on Page |

| INTCON     | GIE      | PEIE   | —         | —      | —        | —       | —        | INTEDG | 146                 |

| PIE1       | OSFIE    | CSWIE  | —         | —      | —        | —       | —        | ADIE   | 148                 |

| PIR1       | OSFIF    | CSWIF  | _         | _      | _        | _       | _        | ADIF   | 156                 |

| TRISA      | TRISA7   | TRISA6 | TRISA5    | TRISA4 | TRISA3   | TRISA2  | TRISA1   | TRISA0 | 200                 |

| TRISB      | TRISB7   | TRISB6 | TRISB5    | TRISB4 | TRISB3   | TRISB2  | TRISB1   | TRISB0 | 206                 |

| TRISC      | TRISC7   | TRISC6 | TRISC5    | TRISC4 | TRISC3   | TRISC2  | TRISC1   | TRISC0 | 211                 |

| ANSELA     | ANSA7    | ANSA6  | ANSA5     | ANSA4  | ANSA3    | ANSA2   | ANSA1    | ANSA0  | 201                 |

| ANSELB     | ANSB7    | ANSB6  | ANSB5     | ANSB4  | ANSB3    | ANSB2   | ANSB1    | ANSB0  | 207                 |

| ANSELC     | ANSC7    | ANSC6  | ANSC5     | ANSC4  | ANSC3    | ANSC2   | ANSC1    | ANSC0  | 212                 |

| ADCON0     |          |        | CHS<      | :5:0>  |          |         | GO/DONE  | ADON   | 277                 |

| ADCON1     | ADFM     |        | ADCS<2:0> |        | —        | _       | ADPREF   | <1:0>  | 279                 |

| ADACT      | _        | —      | —         | —      |          | ADA     | ACT<3:0> |        | 280                 |

| ADRESH     |          |        |           | ADRE   | SH<7:0>  |         |          |        | 281                 |

| ADRESL     |          |        |           | ADRE   | ESL<7:0> |         |          |        | 281                 |

| FVRCON     | FVREN    | FVRRDY | TSEN      | TSRNG  | CDAFV    | ′R<1:0> | ADFVR<   | <1:0>  | 264                 |

| DAC1CON1   |          | _      | _         |        |          | DAC1R<4 | :0>      |        | 287                 |

| OSCSTAT1   | EXTOR    | HFOR   | MFOR      | LFOR   | SOR      | ADOR    | _        | PLLR   | 137                 |

## TABLE 20-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** – = unimplemented read as '0'. Shaded cells are not used for the ADC module.

# 21.6 Register Definitions: DAC Control

## REGISTER 21-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | U-0                          | R/W-0/0                                                                                                                                                                                            | R/W-0/0         | R/W-0/0        | R/W-0/0          | U-0            | R/W-0/0      |

|------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|------------------|----------------|--------------|

| DAC1EN           | —                            | DAC10E1                                                                                                                                                                                            | DAC10E2         | DAC1F          | 'SS<1:0>         | —              | DAC1NSS      |

| bit 7            |                              |                                                                                                                                                                                                    |                 |                |                  |                | bit 0        |

| Legend:          |                              |                                                                                                                                                                                                    |                 |                |                  |                |              |

| R = Readable     | e bit                        | W = Writable                                                                                                                                                                                       | bit             | U = Unimpler   | nented bit, read | as '0'         |              |

| u = Bit is uncl  | nanged                       | x = Bit is unki                                                                                                                                                                                    | nown            | -n/n = Value a | at POR and BOI   | R/Value at all | other Resets |

| '1' = Bit is set |                              | '0' = Bit is cle                                                                                                                                                                                   | ared            |                |                  |                |              |

| bit 7            | 1 = DAC is e<br>0 = DAC is d | isabled                                                                                                                                                                                            | e l             |                |                  |                |              |

| bit 6            | Unimplemen                   | ted: Read as '                                                                                                                                                                                     | 0'              |                |                  |                |              |

| bit 5            | 1 = DAC volt                 | AC1 Voltage C<br>age level is an<br>age level is dis                                                                                                                                               | output on the   | DAC1OUT1 p     |                  |                |              |

| bit 4            | 1 = DAC volt                 | <ul> <li>DAC1OE2: DAC1 Voltage Output 1 Enable bit</li> <li>1 = DAC voltage level is an output on the DAC1OUT2 pin</li> <li>0 = DAC voltage level is disconnected from the DAC1OUT2 pin</li> </ul> |                 |                |                  |                |              |

| bit 3-2          |                              | •                                                                                                                                                                                                  | sitive Source S | Select bits    |                  |                |              |

| bit 1            | Unimplemen                   | ted: Read as '                                                                                                                                                                                     | 0'              |                |                  |                |              |

| hit 0            |                              |                                                                                                                                                                                                    |                 |                |                  |                |              |

bit 0 DAC1NSS: Read as '0'

## REGISTER 21-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | —   |         |         | DAC1R<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DAC1R<4:0>: DAC1 Voltage Output Select bits VOUT = (VSRC+ - VSRC-)\*(DAC1R<4:0>/32) + VSRC

#### 29.1.1 PWM CLOCK SELECTION

The PIC16(L)F15356/75/76/85/86 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

#### 29.1.2 USING THE TMR2 WITH THE PWM MODULE

This device has a newer version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than on older parts. Refer to Section 27.5 "Operation Examples" for examples of PWM signal generation using the different modes of Timer2.

| Note: | PWM operation requires that the timer |

|-------|---------------------------------------|

|       | used as the PWM time base has the     |

|       | FOSC/4 clock source selected.         |

#### 29.1.3 **PWM PERIOD**

Referring to Figure 29-1, the PWM output has a period and a pulse width. The frequency of the PWM is the inverse of the period (1/period).

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### EQUATION 29-1: **PWM PERIOD**

$$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC$$

$$\cdot (TMR2 Prescale Value)$$

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWMx pin is set (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM pulse width is latched from PWMxDC.

| Note: | If the p | ulse v | width value | is grea | ter than | the  |

|-------|----------|--------|-------------|---------|----------|------|

|       | period   | the    | assigned    | PWM     | pin(s)   | will |

|       | remain   | unch   | anged.      |         |          |      |

#### 29.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDC register. The PWMxDCH contains the eight MSbs and the PWMxDCL<7:6> bits contain the two LSbs.

The PWMDC register is double-buffered and can be updated at any time. This double buffering is essential for glitch-free PWM operation. New values take effect when TMR2 = PR2. Note that PWMDC is left-justified.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

Equation 29-2 is used to calculate the PWM pulse width.

Equation 29-3 is used to calculate the PWM duty cycle ratio.

# EQUATION 29-2: PULSE WIDTH

$Pulse Width = (PWMxDC) \cdot TOSC \cdot$ (TMR2 Prescale Value)

#### EQUATION 29-3: DUTY CYCLE RATIO

(PWMxDC) Duty Cycle Ratio =

```

4(PR2 + 1)

```

#### 29.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 29-4.

#### EQUATION 29-4: **PWM RESOLUTION**

Resolution =

$$\frac{\log[4(PR2+1)]}{\log(2)}$$

bits

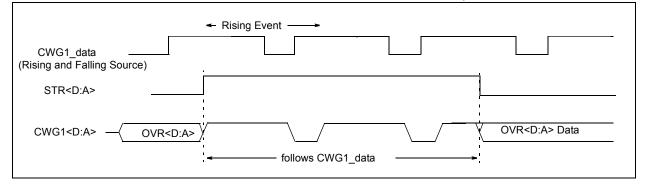

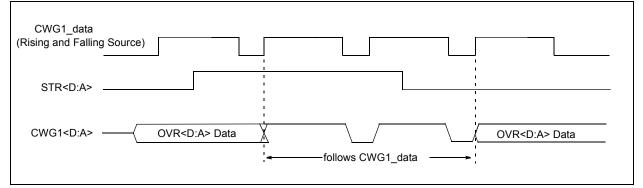

# 30.9 CWG Steering Mode

In Steering mode (MODE = 00x), the CWG allows any combination of the CWG1x pins to be the modulated signal. The same signal can be simultaneously available on multiple pins, or a fixed-value output can be presented.

When the respective STRx bit of CWG1OCON0 is '0', the corresponding pin is held at the level defined. When the respective STRx bit of CWG1OCON0 is '1', the pin is driven by the input data signal. The user can assign the input data signal to one, two, three, or all four output pins.

The POLx bits of the CWG1CON1 register control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 30.10** "**Auto-Shutdown**". An auto-shutdown event will only affect pins that have STRx = 1.

# 30.9.1 STEERING SYNCHRONIZATION