Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 44                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-TQFP                                                                      |

| Supplier Device Package    | 48-TQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15385t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                | Function              | Input<br>Type    | Output Type | Description                                                                                                 |

|-------------------------------------------------------------------------------------|-----------------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------|

| RC2/ANC2/CCP1 <sup>(1)</sup> /IOCC2                                                 | RC2                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                                        |

|                                                                                     | ANC2                  | AN               | _           | ADC Channel C2 input.                                                                                       |

|                                                                                     | CCP1 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | Capture/compare/PWM1 (default input location for capture function).                                         |

|                                                                                     | IOCC2                 | TTL/ST           | —           | Interrupt-on-change input.                                                                                  |

| RC3/ANC3/SCL1 <sup>(1)</sup> /SDI1 <sup>(1,4)</sup> /T2IN <sup>(1)</sup> /<br>IOCC3 | RC3                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                                        |

|                                                                                     | ANC3                  | AN               | —           | ADC Channel C3 input.                                                                                       |

|                                                                                     | SCL1 <sup>(1)</sup>   | l <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C input/output.                                                                        |

|                                                                                     | SDI1 <sup>(1,4)</sup> | TTL/ST           | _           | MSSP1 SPI serial data input (default input location, SDI1 is a PPS remappable input and output).            |

|                                                                                     | T2IN <sup>(1)</sup>   | TTL/ST           | —           | Timer2 external input.                                                                                      |

|                                                                                     | IOCC3                 | TTL/ST           | —           | Interrupt-on-change input.                                                                                  |

| RC4/ANC4/SDA1 <sup>(1)</sup> /SDI1 <sup>(1,4)</sup> /IOCC4                          | RC4                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                                        |

|                                                                                     | ANC4                  | AN               | _           | ADC Channel C4 input.                                                                                       |

| -                                                                                   | SDA1 <sup>(1)</sup>   | l <sup>2</sup> C | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                            |

|                                                                                     | SDI1 <sup>(1,4)</sup> | TTL/ST           | _           | MSSP1 SPI serial data input (default input location, SDI1 is a PPS remappable input and output).            |

|                                                                                     | IOCC4                 | TTL/ST           | —           | Interrupt-on-change input.                                                                                  |

| RC5/ANC5/IOCC5                                                                      | RC5                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                                        |

|                                                                                     | ANC5                  | AN               | —           | ADC Channel C5 input.                                                                                       |

|                                                                                     | IOCC5                 | TTL/ST           | —           | Interrupt-on-change input.                                                                                  |

| RC6/ANC6/TX1/CK1 <sup>(3)</sup> /IOCC6                                              | RC6                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                                        |

|                                                                                     | ANC6                  | AN               | —           | ADC Channel C6 input.                                                                                       |

|                                                                                     | TX1                   | —                | CMOS        | EUSART1 asynchronous.                                                                                       |

|                                                                                     | CK1 <sup>(3)</sup>    | TTL/ST           | CMOS/OD     | EUSART Synchronous mode clock input/output.                                                                 |

|                                                                                     | IOCC6                 | TTL/ST           | —           | Interrupt-on-change input.                                                                                  |

| RC7/ANC7/RX1/DT1 <sup>(1)</sup> /IOCC7                                              | RC7                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                                        |

|                                                                                     | ANC7                  | AN               | _           | ADC Channel C7 input.                                                                                       |

| -                                                                                   | RX1                   | TTL/ST           | _           | EUSART1 Asynchronous mode receiver data input.                                                              |

|                                                                                     | DT1 <sup>(1)</sup>    | TTL/ST           | CMOS/OD     | EUSART1 Synchronous mode data input/output.                                                                 |

|                                                                                     | IOCC7                 | TTL/ST           | —           | Interrupt-on-change input.                                                                                  |

| RD0/AND0/SCK2 <sup>(1)</sup> /SCL2 <sup>(1,4)</sup>                                 | RD0                   | TTL/ST           | CMOS/OD     | General purpose I/O.                                                                                        |

|                                                                                     | AND0                  | AN               | —           | ADC Channel D0 input.                                                                                       |

|                                                                                     | SCK2 <sup>(1)</sup>   | TTL/ST           | CMOS/OD     | MSSP2 SPI clock input/output.                                                                               |

|                                                                                     | SCL2 <sup>(1,4)</sup> | I <sup>2</sup> C | OD          | MSSP2 I <sup>2</sup> C input/output (default input location, SCL2 is a PP-<br>remappable input and output). |

#### TABLE 1-4: PIC16(L)F15385/86 PINOUT DESCRIPTION (CONTINUED)

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-7.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

# PIC16(L)F15356/75/76/85/86

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|---------|--------|--------|--------|--------|-----------|-----------------------|-----------------------|-----------------------|---------------------|

| INTCON  | GIE    | PEIE   | _      | _      | _         | —                     | _                     | INTEDG                | 146                 |

| PIE0    | —      |        | TMR0IE | IOCIE  | —         | _                     |                       | INTE                  | 147                 |

| PIE1    | OSFIE  | CSWIE  | _      |        | —         | —                     |                       | ADIE                  | 148                 |

| PIE2    | _      | ZCDIE  | _      | _      | _         | _                     | C2IE                  | C1IE                  | 149                 |

| PIE3    | RC2IE  | TX2IE  | RC1IE  | TX1IE  | BCL2IE    | SSP2IE                | BCL1IE                | SSP1IE                | 150                 |

| PIE4    | —      | _      | _      | —      | —         | —                     | TMR2IE                | TMR1IE                | 151                 |

| PIR0    | —      | _      | TMR0IF | IOCIF  | —         | —                     |                       | INTF                  | 155                 |

| PIR1    | OSFIF  | CSWIF  | _      |        | _         | _                     | _                     | ADIF                  | 156                 |

| PIR2    | —      | ZCDIF  |        | _      | —         | —                     | C2IF                  | C1IF                  | 157                 |

| PIR3    | RC2IF  | TX2IF  | RC1IF  | TX1IF  | BCL2IF    | SSP2IF                | BCL1IF                | SSP1IF                | 158                 |

| PIR4    | _      |        | _      | _      | —         | _                     | TMR2IF                | TMR1IF                | 159                 |

| IOCAP   | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3    | IOCAP2                | IOCAP1                | IOCAP0                | 255                 |

| IOCAN   | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3    | IOCAN2                | IOCAN1                | IOCAN0                | 255                 |

| IOCAF   | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3    | IOCAF2                | IOCAF1                | IOCAF0                | 256                 |

| IOCBP   | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3    | IOCBP2                | IOCBP1                | IOCBP0                | 257                 |

| IOCBN   | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3    | IOCBN2                | IOCBN1                | IOCBN0                | 257                 |

| IOCBF   | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3    | IOCBF2                | IOCBF1                | IOCBF0                | 258                 |

| IOCCP   | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3    | IOCCP2                | IOCCP1                | IOCCP0                | 259                 |

| IOCCN   | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3    | IOCCN2                | IOCCN1                | IOCCN0                | 259                 |

| IOCCF   | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3    | IOCCF2                | IOCCF1                | IOCCF0                | 259                 |

| IOCEP   | —      |        |        | _      | IOCEP3    | IOCEP2 <sup>(1)</sup> | IOCEP1 <sup>(1)</sup> | IOCEP0 <sup>(1)</sup> | 260                 |

| IOCEN   | —      | _      | _      | —      | IOCEN3    | IOCEN2 <sup>(1)</sup> | IOCEN1 <sup>(1)</sup> | IOCEN0 <sup>(1)</sup> | 260                 |

| IOCEF   | —      |        |        | _      | IOCEF3    | IOCEF2 <sup>(1)</sup> | IOCEF1 <sup>(1)</sup> | IOCEF0 <sup>(1)</sup> | 261                 |

| STATUS  | _      | _      | _      | TO     | PD        | Z                     | DC                    | С                     | 54                  |

| VREGCON | _      | _      | _      | _      | _         | —                     | VREGPM                | _                     | 168                 |

| CPUDOZE | IDLEN  | DOZEN  | ROI    | DOE    | _         |                       | DOZE<2:0>             |                       | 169                 |

| WDTCON0 | —      | —      |        | ١      | NDTPS<4:0 | >                     |                       | SWDTEN                | 175                 |

## TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

**Note 1:** Present only in PIC16(L)F15375/76/85/86.

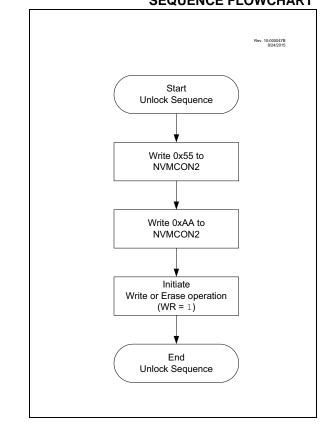

#### 13.3.2 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- · Load of PFM write latches

- Write of PFM write latches to PFM memory

- · Write of PFM write latches to User IDs

The unlock sequence consists of the following steps and must be completed in order:

- Write 55h to NVMCON2

- Write AAh to NMVCON2

- Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

| Note: | The two NOP instructions after setting the |

|-------|--------------------------------------------|

|       | WR bit that were required in previous      |

|       | devices are not required for               |

|       | PIC16(L)F15356/75/76/85/86 devices.        |

|       | See Figure 13-2.                           |

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

| EXAMPLE 13-2: | NVM UNLOCK SEQUENCE |

|---------------|---------------------|

| BC |       | INTCON, GIE                                                                                | ; Recommended so sequence is not interrupted                                  |  |  |  |  |

|----|-------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

|    | NKSEL | NVMCON1                                                                                    |                                                                               |  |  |  |  |

| BS | 5 F.  | NVMCON1, WREN                                                                              | ; Enable write/erase                                                          |  |  |  |  |

| MC | DVLW  | 55h                                                                                        | ; Load 55h                                                                    |  |  |  |  |

| MC | DVWF  | NVMCON2                                                                                    | ; Step 1: Load 55h into NVMCON2                                               |  |  |  |  |

| MC | NTA   | AAh                                                                                        | ; Step 2: Load W with AAh                                                     |  |  |  |  |

| MC | DVWF  | NVMCON2                                                                                    | ; Step 3: Load AAH into NVMCON2                                               |  |  |  |  |

| BS | SF    | NVMCON1, WR                                                                                | ; Step 4: Set WR bit to begin write/erase                                     |  |  |  |  |

| BS | SF    | INTCON, GIE                                                                                | ; Re-enable interrupts                                                        |  |  |  |  |

| Ν  |       | 1 8                                                                                        | n NVMCON2 is written; steps 1-4 must occur in the cycle-accurate order shown. |  |  |  |  |

|    | 2:    | Opcodes shown are illustrative; any instruction that has the indicated effect may be used. |                                                                               |  |  |  |  |

#### **FIGURE 13-2: NVM UNLOCK**

## SEQUENCE FLOWCHART

#### 14.10 PORTE Registers

#### 14.10.1 DATA REGISTER

PORTE is a 4-bit wide port. The corresponding data direction register is TRISE (Register 14-33). Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize PORTE.

Reading the PORTE register (Register 14-33) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATE).

#### 14.10.2 DIRECTION CONTROL

The TRISE register (Register 14-34) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

| Note: | The TRISE3 bit is a read-only bit and it |

|-------|------------------------------------------|

|       | always reads a '1'.                      |

#### 14.10.3 OPEN-DRAIN CONTROL

The ODCONE register (Register 14-38) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONE bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONE bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for I <sup>2</sup> C; the I <sup>2</sup> C |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                                       |

#### 14.10.4 SLEW RATE CONTROL

The SLRCONE register (Register 14-39) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONE bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONE bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.10.5 INPUT THRESHOLD CONTROL

The INLVLE register (Register 14-40) controls the input voltage threshold for each of the available PORTE input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTE register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 14.10.6 ANALOG CONTROL

The ANSELE register (Register 14-36) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELE bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELE bits has no effect on digital output functions. A pin with TRIS clear and ANSELE set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELE bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 14.10.7 WEAK PULL-UP CONTROL

The WPUE register (Register 14-37) controls the individual weak pull-ups for each port pin.

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTF   | RF7     | RF6     | RF5     | RF4     | RF3     | RF2     | RF1     | RF0     | 216                 |

| TRISF   | TRISF7  | TRISF6  | TRISF5  | TRISF4  | TRISF3  | TRISF2  | TRISF1  | TRISF0  | 216                 |

| LATF    | LATF7   | LATF6   | LATF5   | LATF4   | LATF3   | LATF2   | LATF1   | LATF0   | 216                 |

| ANSELF  | ANSF7   | ANSF6   | ANSF5   | ANSF4   | ANSF3   | ANSF2   | ANSF1   | ANSF0   | 217                 |

| WPUF    | WPUF7   | WPUF6   | WPUF5   | WPUF4   | WPUF3   | WPUF2   | WPUF1   | WPUF0   | 217                 |

| ODCONF  | ODCF7   | ODCF6   | ODCF5   | ODCF4   | ODCF3   | ODCF2   | ODCF1   | ODCF0   | 218                 |

| SLRCONF | SLRF7   | SLRF6   | SLRF5   | SLRF4   | SLRF3   | SLRF2   | SLRF1   | SLRF0   | 218                 |

| INLVLF  | INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4 | INLVLF3 | INLVLF2 | INLVLF1 | INLVLF0 | 218                 |

#### TABLE 14-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

Legend: - = unimplemented locations read as '0'. Shaded cells are not used by PORTF.

### 15.8 Register Definitions: PPS Input Selection

#### **REGISTER 15-1:** xxxPPS: PERIPHERAL xxx INPUT SELECTION<sup>(1)</sup>

| U-0              | U-0   | R/W-q/u                                              | R/W-q/u | R/W/q/u        | R/W-q/u          | R/W-q/u          | R/W-q/u     |

|------------------|-------|------------------------------------------------------|---------|----------------|------------------|------------------|-------------|

| _                | —     |                                                      |         | xxxPF          | °S<5:0>          |                  |             |

| bit 7            |       |                                                      |         |                |                  |                  | bit 0       |

|                  |       |                                                      |         |                |                  |                  |             |

| Legend:          |       |                                                      |         |                |                  |                  |             |

| R = Readable I   | bit   | W = Writable                                         | bit     | U = Unimplen   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged | x = Bit is unkr                                      | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |       | '0' = Bit is cleared q = value depends on peripheral |         |                |                  |                  |             |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **xxxPPS<5:0>:** Peripheral xxx Input Selection bits See Tables 15-1 through 15-3.

- **Note 1:** The "xxx" in the register name "xxxPPS" represents the input signal function name, such as "INT", "T0CKI", "RX", etc. This register summary shown here is only a prototype of the array of actual registers, as each input function has its own dedicated SFR (ex: INTPPS, T0CKIPPS, RXPPS, etc.).

- 2: Each specific input signal may only be mapped to a subset of these I/O pins, as shown in Table 15-4. Attempting to map an input signal to a non-supported I/O pin will result in undefined behavior. For example, the "INT" signal map be mapped to any PORTA or PORTB pin. Therefore, the INTPPS register may be written with values from 0x00-0x0F (corresponding to RA0-RB7). Attempting to write 0x10 or higher to the INTPPS register is not supported and will result in undefined behavior.

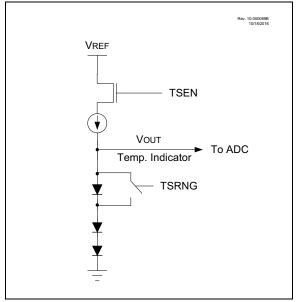

## 19.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The main purpose of the temperature indicator module is to provide a temperature-dependent voltage that can be measured by the Analog-to-Digital Converter.

The circuit's range of operating temperature falls between -40°C and +125°C. The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately.

## **19.1 Module Operation**

The temperature indicator module consists of a temperature-sensing circuit that provides a voltage to the device ADC. The analog voltage output, VTSENSE, varies inversely to the device temperature. The output of the temperature indicator is referred to as VOUT.

Figure 19-1 shows a simplified block diagram of the temperature indicator module.

#### FIGURE 19-1: TEMPERATURE INDICATOR BLOCK DIAGRAM

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 20.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

The ON/OFF bit for the module is located in the FVRCON register. See **Section 18.0** "**Fixed Voltage Reference (FVR)**" for more information. The circuit is enabled by setting the TSEN bit of the FVRCON register. When the module is disabled, the circuit draws no current.

The circuit operates in either High or Low range. Refer to **Section 19.5** "**Temperature Indicator Range**" for more details on the range settings.

## 19.2 Estimation of Temperature

This section describes how the sensor voltage can be used to estimate the temperature of the module. To use the sensor, the output voltage, VTSENSE, is measured and the corresponding temperature is determined. Equation 19-1 provides an estimate for the die temperature based on the VTSENSE value.

## EQUATION 19-1: SENSOR TEMPERATURE

$$T_{SENSE} = V_{TSENSE} \times (-Mt) + T_{OFFSET}$$

Where:

Mt = 1/Mv, where Mv = sensor voltage sensitivity (V/°C). TOFFSET is the temperature difference between the theoretical temperature and the actual temperature.

## 19.4 Minimum Operating VDD

When the temperature circuit is operated in Low range, the device may be operated at any operating voltage that is within specifications. When the temperature circuit is operated in High range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 19-1 shows the recommended minimum  $V \mbox{\scriptsize DD}$  vs. Range setting.

TABLE 19-1: RECOMMENDED VDD vs. RANGE

| Min.VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|--------------------|---------------------|

| (High Range)       | (Low Range)         |

| ≥ 2.5              | ≥ 1.8               |

## 19.5 Temperature Indicator Range

The temperature indicator circuit operates in either High or Low range. The High range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range. High range requires a higher-bias voltage to operate and thus, a higher VDD is needed. The Low range is selected by clearing the TSRNG bit of the FVRCON register. The Low range generates a lower sensor voltage and thus, a lower VDD voltage is needed to operate the circuit.

The output voltage of the sensor is the highest value at  $-40^{\circ}$ C and the lowest value at  $+125^{\circ}$ C.

- **High Range:** The High range is used in applications with the reference for the ADC, VREF = 2.048V. This range may not be suitable for battery-powered applications.

- Low Range: This mode is useful in applications in which the VDD is too low for high-range operation.

The VDD in this mode can be as low as 1.8V. VDD must, however, be at least 0.5V higher than the maximum sensor voltage depending on the expected low operating temperature.

## **19.6 DIA Information**

DIA data provide ADC reading at one operating temperature. DIA data is taken during factory testing and stored within the device. The 90°C reading alone allows single-point calibration as described in Section 19.2.1, Calibration, by solving Equation 19-1 for TOFFSET.

| Note: | Note that the lower temperature range   |

|-------|-----------------------------------------|

|       | (e.g., -40°C) will suffer in accuracy   |

|       | because temperature conversion must     |

|       | extrapolate below the reference points, |

|       | amplifying any measurement errors.      |

Refer to **Section 6.0** "**Device Information Area**" for more information on the data stored in the DIA and how to access them.

| Name   | Bit 7              | Bit 6    | Bit 5    | Bit 4 | Bit 3 Bit 2     |                   | Bit 1  | Bit 0 | Register<br>on Page |  |

|--------|--------------------|----------|----------|-------|-----------------|-------------------|--------|-------|---------------------|--|

| FVRCON | FVREN              | FVRRDY   | TSEN     | TSRNG | CDFVI           | CDFVR<1:0> ADFVR< |        | <1:0> | 264                 |  |

| ADCON0 |                    | CHS<5:0> |          |       | )> GO/DONE ADOI |                   |        |       |                     |  |

| ADCON1 | ADFM               | A        | DCS<2:0> | >     | —               | _                 | ADPREF | 279   |                     |  |

| ADACT  | _                  | —        | _        | _     |                 | 280               |        |       |                     |  |

| ADRESH | ADRESH<7:0>        |          |          |       |                 |                   |        | 281   |                     |  |

| ADRESL | ADRESL ADRESL<7:0> |          |          |       |                 |                   |        |       |                     |  |

## TABLE 19-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

**Legend:** Shaded cells are unused by the Temperature Indicator module.

## 22.2 FIXED DUTY CYCLE MODE

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled at a frequency rate half of the FOVERFLOW. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 22-2.

The FDC mode is selected by clearing the N1PFM bit in the NCO1CON register.

### 22.3 PULSE FREQUENCY MODE

In Pulse Frequency (PF) mode, every time the Accumulator overflows, the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output. The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 22-2.

The value of the active and inactive states depends on the polarity bit, N1POL in the NCO1CON register.

The PF mode is selected by setting the N1PFM bit in the NCO1CON register.

#### 22.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the N1PWS<2:0> bits in the NCO1CLK register.

When the selected pulse width is greater than the Accumulator overflow time frame, then NCO1 output does not toggle.

## 22.4 OUTPUT POLARITY CONTROL

The last stage in the NCO module is the output polarity. The N1POL bit in the NCO1CON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCO output signal (NCO1\_out) is available to the following peripherals:

- CLC

- CWG

- Timer1

- Timer2

- CLKR

#### 22.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCO Interrupt Flag bit, NCO1IF, of the PIR7 register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- N1EN bit of the NCO1CON register

- NCO1IE bit of the PIE7 register

- PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCO1IF bit in the Interrupt Service Routine.

#### 22.6 Effects of a Reset

All of the NCO registers are cleared to zero as the result of a Reset.

#### 22.7 Operation in Sleep

The NCO module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO clock source, when the NCO is enabled, the CPU will go idle during Sleep, but the NCO will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

## 23.10 CWG1 Auto-shutdown Source

The output of the comparator module can be used as an auto-shutdown source for the CWG1 module. When the output of the comparator is active and the corresponding ASxE is enabled, the CWG operation will be suspended immediately (see **Section 30.10 "Auto-Shutdown"**).

## 23.11 Operation in Sleep Mode

The comparator module can operate during Sleep. The comparator clock source is based on the Timer1 clock source. If the Timer1 clock source is either the system clock (FOSC) or the instruction clock (FOSC/4), Timer1 will not operate during Sleep, and synchronized comparator outputs will not operate.

A comparator interrupt will wake the device from Sleep. The CxIE bits of the PIE2 register must be set to enable comparator interrupts.

### REGISTER 23-3: CMxNSEL: COMPARATOR Cx NEGATIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| —     | _   | _   | _   | _   |         | NCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

## Legend:

| Logonal              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bits

| bit 7-3 | Unimplemented: Read as '0'                         |

|---------|----------------------------------------------------|

| bit 2-0 | NCH<2:0>: Comparator Negative Input Channel Select |

|         | 111 = CxVN connects to AVss                        |

|         | 110 = CxVN connects to FVR Buffer 2                |

|         | 101 = CxVN unconnected                             |

|         | 100 = CxVN unconnected                             |

- 011 = CxVN connects to CxIN3- pin

- 010 = CxVN connects to CxIN2- pin

- 001 = CxVN connects to CxIN1- pin

- 000 = CxVN connects to CxINO- pin

#### REGISTER 23-4: CMxPSEL: COMPARATOR Cx POSITIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | _   | _   | —   | _   |         | PCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 PCH<2:0>: Comparator Positive Input Channel Select bits

- 111 = CxVP connects to AVss

- 110 = CxVP connects to FVR Buffer 2

- 101 = CxVP connects to DAC output

- 100 = CxVP unconnected

- 011 = CxVP unconnected

- 010 = CxVP unconnected

- 001 = CxVP connects to CxIN1+ pin

- 000 = CxVP connects to CxIN0+ pin

## 27.5.9 EDGE-TRIGGERED MONOSTABLE MODES

The Edge-Triggered Monostable modes start the timer on an edge from the external Reset signal input, after the ON bit is set, and stop incrementing the timer when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 10001)

- Falling edge (MODE<4:0> = 10010)

- Rising or Falling edge (MODE<4:0> = 10011)

When an Edge-Triggered Monostable mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external Reset signal edge that starts the timer, but will not go active when the timer matches the PRx value. While the timer is incrementing, additional edges on the external Reset signal will not affect the CCP PWM.

| Name     | Bit 7       | Bit 6           | Bit 5        | Bit 4       | Bit 3         | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |  |  |  |

|----------|-------------|-----------------|--------------|-------------|---------------|-----------|--------|--------|---------------------|--|--|--|

| CCP1CON  | EN          | _               | OUT          | FMT         | FMT MODE<3:0> |           |        |        |                     |  |  |  |

| CCP2CON  | EN          | _               | OUT          | FMT         | FMT MODE<3:0> |           |        |        |                     |  |  |  |

| INTCON   | GIE         | PEIE            | _            | _           | —             | —         | —      | INTEDG | 146                 |  |  |  |

| PIE1     | OSFIE       | CSWIE           | _            | _           | —             | —         | _      | ADIE   | 148                 |  |  |  |

| PIR1     | OSFIF       | CSWIF           | _            | _           | —             | _         | _      | ADIF   | 156                 |  |  |  |

| PR2      | Timer2 Modu | ule Period Re   | gister       |             |               |           |        |        |                     |  |  |  |

| TMR2     | Holding Reg | ister for the 8 | -bit TMR2 Re | gister      |               |           |        |        |                     |  |  |  |

| T2CON    | ON          |                 | CKPS<2:0>    |             |               | OUTP      | S<3:0> |        | 355                 |  |  |  |

| T2CLKCON | _           | _               | _            | — CS<3:0>   |               |           |        |        |                     |  |  |  |

| T2RST    | —           |                 | _            | — RSEL<3:0> |               |           |        |        |                     |  |  |  |

| T2HLT    | PSYNC       | CKPOL           | CKSYNC       |             |               | MODE<4:0> |        |        | 356                 |  |  |  |

#### TABLE 27-2: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

#### 32.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of  $\overline{ACK}$  is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCL low and SDA unchanged (Figure 32-28).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

#### 32.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

#### 32.6.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

#### 32.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

32.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPxBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 9. The user loads the SSPxBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPx-CON2 register. Interrupt is generated once the Stop/Restart condition is complete.

## 33.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 33-3 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 33.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 33-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 33.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 33.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

#### 33.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 33.4.1.2 "Clock Polarity"**.

#### 33.1.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE3 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

# PIC16(L)F15356/75/76/85/86

© 2016 Microchip Technology Inc.

#### 37.3 **DC** Characteristics

| 37.3 DC Characteristics |           |                                |             |                                                         |                          |               |                                      |  |  |  |

|-------------------------|-----------|--------------------------------|-------------|---------------------------------------------------------|--------------------------|---------------|--------------------------------------|--|--|--|

| TABLE 3                 | 87-1: 3   | SUPPLY VOLTAGE                 |             |                                                         |                          |               | {                                    |  |  |  |

| PIC16LF                 | 15356/75  | 5/76/85/86                     | Standa      | Standard Operating Conditions (unless otherwise stated) |                          |               |                                      |  |  |  |

| PIC16F15356/75/76/85/86 |           |                                |             |                                                         |                          |               |                                      |  |  |  |

| Param.<br>No.           | Sym.      | Characteristic                 | Min.        | Typ.†                                                   | Max.                     | Units         | Conditions                           |  |  |  |

| Supply \                | /oltage   |                                |             |                                                         |                          |               |                                      |  |  |  |

| D002                    | Vdd       |                                | 1.8<br>2.5  | -                                                       | 3.6<br>3.6               | × ≯           | Fosc ≥ 16 MHz<br>Fosc > 16 MH≱       |  |  |  |

| D002                    | Vdd       |                                | 2.3<br>2.5  | _                                                       | 5.5<br>5.5               | 7 V           | Fosc ≤ 16 MHz<br>Føsç ≥ 16 MHz       |  |  |  |

| RAM Da                  | ta Retent | tion <sup>(1)</sup>            |             | •                                                       | $\wedge$                 |               | ~/                                   |  |  |  |

| D003                    | Vdr       |                                | 1.5         | —                                                       | $\langle \gamma \rangle$ | V \           | Device in Sleep mode                 |  |  |  |

| D003                    | Vdr       |                                | 1.7         |                                                         |                          | X             | Device in Sleep mode                 |  |  |  |

| Power-o                 | n Reset   | Release Voltage <sup>(2)</sup> |             | $\langle$                                               |                          | $\rightarrow$ |                                      |  |  |  |

| D004                    | Vpor      |                                | —           | /1,6                                                    |                          | V             | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| D004                    | Vpor      |                                |             | 1.6                                                     | Á                        | > V           | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| Power-o                 | n Reset   | Rearm Voltage <sup>(2)</sup>   |             | $ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                | $\langle \ \rangle$      |               |                                      |  |  |  |

| D005                    | VPORR     |                                | $\neq \ell$ | 8.0                                                     | $\searrow$               | V             | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| D005                    | VPORR     | $\land$                        | $\sim$      | 1,5                                                     | > -                      | V             | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| VDD Rise                | e Rate to | ensure internal Power-on F     | Reset sig   | ynal <sup>(2)//</sup>                                   |                          |               |                                      |  |  |  |

| D006                    | SVDD      | $\land$                        | 0.05        | $\searrow$                                              | _                        | V/ms          | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| D006                    | SVDD      |                                | 0.05        | > -                                                     | —                        | V/ms          | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- 2: See Figure 37-3, POR and POR REARM with Slow Rising VDD.

- 3: See Table 37-11 for BQR and LPBOR trip point information. = F device

4:

## PIC16(L)F15356/75/76/85/86

## 39.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- MPLAB® XPRESS IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 39.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

# PIC16(L)F15356/75/76/85/86

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | Τ Τ                                                                                 | - <u>x</u>                                                                                                                                                                     | <u>/xx</u>              | <u>xxx</u> | Exa  | mples | 5:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                   | Tape and Ree<br>Option                                                              | I Temperature<br>Range                                                                                                                                                         | Package                 | Pattern    | a)   | Exten | 6F15356- E/SP<br>ided temperature<br>P package                                                                                                                                                                                                                                                                                                                                                                                           |

| Device:                  | PIC16F15379<br>PIC16F15376<br>PIC16F15389                                           | 6, PIC16LF15356<br>5, PIC16LF15375<br>6, PIC16LF15376<br>5, PIC16LF15385<br>6, PIC16LF15386                                                                                    |                         |            |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Tape and Reel<br>Option: |                                                                                     | ndard packaging (tu<br>be and Reel <sup>(1)</sup>                                                                                                                              | be or tray)             |            |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Temperature<br>Range:    |                                                                                     |                                                                                                                                                                                | ndustrial)<br>Extended) |            | Note | ə 1:  | Tape and Reel identifier only appears in                                                                                                                                                                                                                                                                                                                                                                                                 |

| Package: <sup>(2)</sup>  | MV = 28<br>MV = 40<br>MV = 48<br>P = 40<br>PT = 44<br>PT = 48<br>SO = 28<br>SP = 28 | -lead QFN 8x8mm<br>-lead UQFN 4x4mn<br>-lead UQFN 5x5mn<br>-lead UQFN 6x6mn<br>-lead PDIP<br>-lead TQFP 10x10n<br>-lead TQFP 10x10n<br>-lead SOIC<br>-lead SPDIP<br>-lead SSOP | ו<br>ו<br>חm            |            |      | 2:    | the catalog part number description. This<br>identifier is used for ordering purposes and<br>is not printed on the device package.<br>Check with your Microchip Sales Office<br>for package availability with the Tape and<br>Reel option.<br>Small form-factor packaging options may<br>be available. Check<br><u>www.microchip.com/packaging</u> for<br>small-form factor package availability, or<br>contact your local Sales Office. |

| Pattern:                 | QTP, SQTP, (<br>(blank otherw                                                       | Code or Special Rec<br>rise)                                                                                                                                                   | quirements              |            |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                          |