Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15386-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

© 2016 Microchip Technology Inc.

# \_ \_ \_ CLKOUT/ OSC1 CLKIN/ OSC2 \_ \_ \_ \_ \_ \_ ICSPCLK ICSPDAT

Pull-up

Y

Y

Y

Y

Y

Y

Υ

Y

Υ

Y

Υ

Υ

Υ

Y

Y

\_

\_

Basic

\_

| 2<br>2<br>2<br>2<br>2<br>2<br>3<br>3<br>3 | 48-Pin UQFN/T | ADC                          | Reference | Comparato        | NCO | DAC      | Timers                        | ССР                 | MWA | CWG                 | dssm                          | ZCD  | EUSART                    | CLC                   | ССКК | Interrupt                   |

|-------------------------------------------|---------------|------------------------------|-----------|------------------|-----|----------|-------------------------------|---------------------|-----|---------------------|-------------------------------|------|---------------------------|-----------------------|------|-----------------------------|

| 2<br>2<br>2<br>2<br>2<br>3<br>3<br>3      | 21            | ANA0                         | -         | C1IN0-<br>C2IN0- |     | —        | -                             | -                   |     | -                   | -                             |      | —                         | CLCIN0 <sup>(1)</sup> |      | IOCA0                       |

| 2<br>2<br>2<br>2<br>3<br>3<br>3           | 22            | ANA1                         |           | C1IN1-<br>C2IN1- | _   | —        | _                             | _                   | _   | _                   | _                             | _    | —                         | CLCIN1 <sup>(1)</sup> | l    | IOCA1                       |

| 22                                        | 23            | ANA2                         | Ι         | C1IN0+<br>C2IN0+ | -   | DAC1OUT1 | -                             | -                   | -   | -                   | -                             | -    | —                         | -                     |      | IOCA2                       |

| 3                                         | 24            | ANA3                         | VREF+     | C1IN1+           | _   | DACREF+  | _                             | _                   | _   | _                   | _                             | _    | _                         | _                     | -    | IOCA3                       |

| 3                                         | 25            | ANA4                         | _         | C1IN1-           | _   | _        | T0CKI <sup>(1)</sup>          | _                   | _   | _                   | _                             | _    | —                         | _                     |      | IOCA4                       |

| 3                                         | 26            | ANA5<br>ADACT                |           |                  |     | _        | T1G <sup>(1)</sup>            |                     |     |                     | SS1 <sup>(1)</sup>            |      | —                         | —                     |      | IOCA5                       |

|                                           | 33            | ANA6                         | -         | _                | _   | —        | _                             | _                   | _   | _                   | _                             | _    | —                         | —                     |      | IOCA6                       |

|                                           | 32            | ANA7                         |           |                  | -   | _        |                               | -                   | -   | -                   | -                             | -    | —                         | -                     |      | IOCA7                       |

|                                           | 8             | ANB0                         |           | C2IN1+           | —   | _        | -                             | -                   | _   | CWG1 <sup>(1)</sup> | SS2 <sup>(1)</sup>            | ZCD1 | -                         | —                     |      | INT <sup>(1)</sup><br>IOCB0 |

| 9                                         | 9             | ANB1                         |           | C1IN3-<br>C2IN3- |     | _        |                               |                     |     |                     | SCL1<br>SCK1 <sup>(1,4)</sup> |      | —                         | —                     |      | IOCB1                       |

| 1                                         | 10            | ANB2                         | Ι         | -                | -   | _        | -                             | -                   | -   | -                   | SDA1<br>SDI1 <sup>(1,4)</sup> | -    | —                         | -                     |      | IOCB2                       |

| 1                                         | 11            | ANB3                         |           | C1IN2-<br>C2IN2- | _   | _        |                               | -                   | _   | -                   | -                             | -    | —                         | —                     |      | IOCB3                       |

| 1                                         | 16            | ANB4<br>ADACT <sup>(1)</sup> | I         |                  |     | _        |                               |                     |     |                     |                               |      | —                         | —                     |      | IOCB4                       |

| 1                                         | 17            | ANB5                         | -         | _                | _   | _        | _                             | _                   | -   | _                   | _                             |      | —                         | _                     | Ι    | IOCB5                       |

| 1                                         | 18            | ANB6                         | Ι         | -                | -   | _        | -                             | -                   | -   | -                   | -                             | -    | TX2<br>CK2 <sup>(1)</sup> | CLCIN2 <sup>(1)</sup> |      | IOCB6                       |

| 1                                         | 19            | ANB7                         |           |                  | _   | DAC1OUT2 |                               | -                   | -   |                     |                               |      | RX2<br>DT2 <sup>(1)</sup> | CLCIN3 <sup>(1)</sup> |      | IOCB7                       |

| 3                                         | 34            | ANC0                         | -         | —                | —   | _        | SOSCO<br>T1CKI <sup>(1)</sup> | -                   | -   |                     | —                             |      | -                         | —                     |      | IOCC0                       |

| 3                                         | 35            | ANC1                         | _         | _                | _   | _        | SOSCI                         | CCP2 <sup>(1)</sup> | _   | _                   | _                             | _    | _                         | _                     | _    | IOCC1                       |

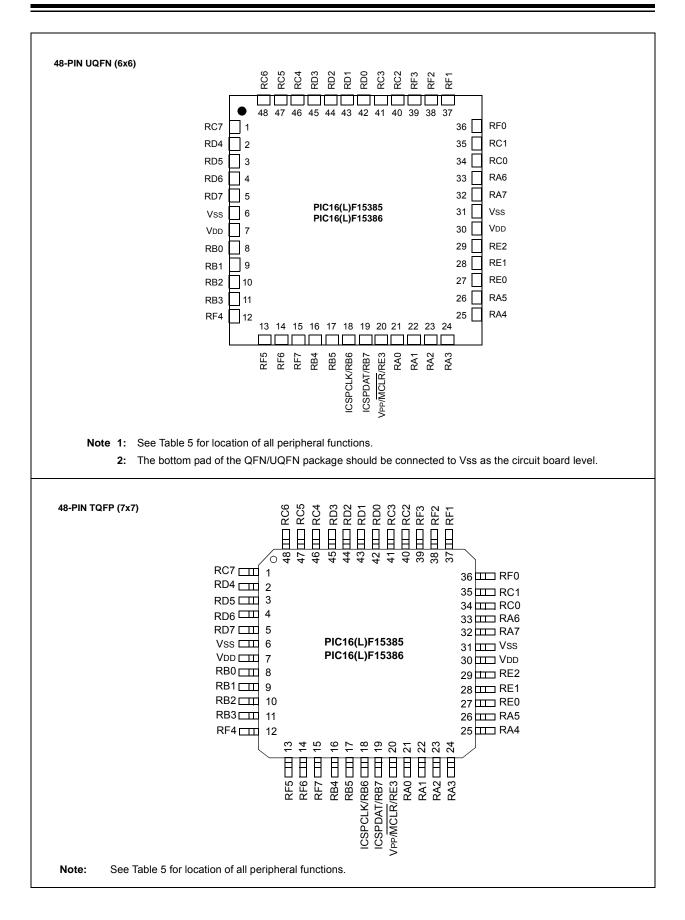

### 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) TABLE 5:

This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Note 1:

All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options. 2:

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

TQFP

I/O<sup>(2)</sup>

RA0 RA1

RA2

RA3

RA4

RA5

RA6

RA7

RB0

RB1

RB2

RB3

RB4

RB5

RB6

RB7

RC0

RC1

| Name                                                    | Function              | Input<br>Type | Output Type | Description                                       |

|---------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------|

| RA0/ANA0/C1IN0-/C2IN0-/CLCIN0 <sup>(1)</sup> /<br>IOCA0 | RA0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IUCAU                                                   | ANA0                  | AN            | _           | ADC Channel A0 input.                             |

|                                                         | C1IN0-                | AN            | _           | Comparator 1 negative input.                      |

|                                                         | C2IN0-                | AN            | _           | Comparator 2 negative input.                      |

|                                                         | CLCIN0 <sup>(1)</sup> | TTL/ST        |             | Configurable Logic Cell source input.             |

|                                                         | IOCA0                 | TTL/ST        | -           | Interrupt-on-change input.                        |

| RA1/ANA1/C1IN1-/C2IN1-/CLCIN1 <sup>(1)</sup> /<br>IOCA1 | RA1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IOCAT                                                   | ANA1                  | AN            |             | ADC Channel A1 input.                             |

|                                                         | C1IN1-                | AN            |             | Comparator 1 negative input.                      |

|                                                         | C2IN1-                | AN            |             | Comparator 2 negative input.                      |

|                                                         | CLCIN1 <sup>(1)</sup> | TTL/ST        |             | Configurable Logic Cell source input.             |

|                                                         | IOCA1                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA2/ANA2/C1IN0+/C2IN0+/<br>DAC1OUT1/IOCA2               | RA2                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| DACTOUTINOCAZ                                           | ANA2                  | AN            | _           | ADC Channel A2 input.                             |

|                                                         | C1IN0+                | AN            | -           | Comparator 2 positive input.                      |

|                                                         | C2IN0+                | AN            | _           | Comparator 2 positive input.                      |

|                                                         | DAC1OUT1              | _             | AN          | Digital-to-Analog Converter output.               |

|                                                         | IOCA2                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA3/ANA3/C1IN1+/VREF+/IOCA3/<br>DAC1REF+                | RA3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| DACIREFT                                                | ANA3                  | AN            | _           | ADC Channel A3 input.                             |

|                                                         | C1IN1+                | AN            | _           | Comparator 1 positive input.                      |

|                                                         | VREF+                 | AN            | _           | External ADC and/or DAC positive reference input. |

|                                                         | IOCA3                 | TTL/ST        | _           | Interrupt-on-change input.                        |

|                                                         | DAC1REF+              | TTL/ST        | AN          | DAC positive reference.                           |

| RA4/ANA4/T0CKI <sup>(1)</sup> /IOCA4                    | RA4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA4                  | AN            | -           | ADC Channel A4 input.                             |

|                                                         | T0CKI <sup>(1)</sup>  | TTL/ST        | _           | Timer0 clock input.                               |

|                                                         | IOCA4                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA5/ANA5/SS1 <sup>(1)</sup> /IOCA5                      | RA5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA5                  | AN            | _           | ADC Channel A5 input.                             |

|                                                         | SS1 <sup>(1)</sup>    | TTL/ST        | _           | MSSP1 SPI slave select input.                     |

|                                                         | IOCA5                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| <b>TABLE 1-2:</b> | PIC16(L)F15356 PINOUT DESCRIPTION |

|-------------------|-----------------------------------|

|-------------------|-----------------------------------|

CMOS = CMOS compatible input or output Legend: AN = Analog input or output OD = Open-Drain I<sup>2</sup>C TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx 1: pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for  $I^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the  $I^2C$  specific or SMBus input buffer thresholds. 4:

Note

| Address | Name                  | Bit 7 | Bit 6 | Bit 5   | Bit 4                | Bit 3            | Bit 2        | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|-----------------------|-------|-------|---------|----------------------|------------------|--------------|-------|-------|-----------------------|----------------------------|

| Bank 62 |                       |       |       |         |                      |                  |              |       |       |                       |                            |

|         |                       |       |       | CPU COF | RE REGISTERS;        | see Table 4-3 fo | or specifics |       |       |                       |                            |

| 1F0Ch   | _                     |       |       |         | Unimple              | mented           |              |       |       | _                     | _                          |

| 1F0Dh   | _                     |       |       |         | Unimple              | mented           |              |       |       | _                     | _                          |

| 1F0Eh   | —                     |       |       |         | Unimple              | mented           |              |       |       | —                     |                            |

| 1F0Fh   | —                     |       |       |         | Unimple              | mented           |              |       |       | —                     | _                          |

| 1F10h   | RA0PPS                | —     | —     | —       |                      |                  | RA0PPS<4:0   | >     |       | 00 0000               | uu uuuu                    |

| 1F11h   | RA1PPS                | —     | —     | —       |                      |                  | RA1PPS<4:0   | >     |       | 00 0000               | uu uuuu                    |

| 1F12h   | RA2PPS                | _     | _     | _       |                      |                  | RA2PPS<4:0   | >     |       | 00 0000               | uu uuui                    |

| 1F13h   | <b>RA3PPS</b>         | —     | —     | —       |                      |                  | RA3PPS<4:0   | >     |       | 00 0000               | uu uuuu                    |

| 1F14h   | RA4PPS                | —     | —     | —       |                      |                  | RA4PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

| 1F15h   | RA5PPS                | —     | —     | —       |                      |                  | RA5PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

| 1F16h   | RA6PPS                | —     | —     | —       |                      |                  | RA6PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

| 1F17h   | RA7PPS                | _     | —     | —       |                      | RA7PPS<4:0>      |              |       |       |                       | uu uuu                     |

| 1F18h   | RB0PPS                | _     | —     | —       |                      | RB0PPS<4:0>      |              |       |       | 00 0000               | uu uuu                     |

| 1F19h   | RB1PPS                | _     | —     | —       |                      | RB1PPS<4:0>      |              |       |       |                       | uu uuu                     |

| 1F1Ah   | RB2PPS                | —     | —     | —       |                      | RB2PPS<4:0>      |              |       |       |                       | uu uuu                     |

| 1F1Bh   | RB3PPS                | —     | —     | —       |                      |                  | RB3PPS<4:0   | >     |       | 00 0000               | uu uuuu                    |

| 1F1Ch   | RB4PPS                | —     | —     | —       |                      | RB4PPS<4:0>      |              |       |       |                       | uu uuu                     |

| 1F1Dh   | RB5PPS                | —     | —     | —       |                      | RB5PPS<4:0>      |              |       |       |                       | uu uuuu                    |

| 1F1Eh   | RB6PPS                | —     | —     | —       |                      | RB6PPS<4:0>      |              |       |       |                       | uu uuuu                    |

| 1F1Fh   | RB7PPS                | —     | —     | —       |                      |                  | RB7PPS<4:0   | >     |       | 00 0000               | uu uuuu                    |

| 1F20h   | RC0PPS                | —     | —     | —       |                      |                  | RC0PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

| 1F21h   | RC1PPS                | —     | —     | —       |                      |                  | RC1PPS<4:0   | >     |       | 00 0000               | uu uuuu                    |

| 1F22h   | RC2PPS                | _     | —     | —       |                      |                  | RC2PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

| 1F23h   | RC3PPS                | _     | —     | —       |                      |                  | RC3PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

| 1F24h   | RC4PPS                | _     | —     | —       |                      |                  | RC4PPS<4:0   | >     |       | 00 0000               | uu uuuu                    |

| 1F25h   | RC5PPS                | _     | —     | —       | RC5PPS<4:0>00 0000 - |                  |              |       |       |                       | uu uuuu                    |

| 1F26h   | RC6PPS                | _     | —     | —       | RC6PPS<4:0>00 0000u  |                  |              |       |       |                       | uu uuuu                    |

| 1F27h   | RC7PPS                | —     | —     | —       |                      |                  | RC7PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

| 1F28h   | RD0PPS <sup>(1)</sup> | —     | —     | —       |                      |                  | RD0PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

| 1F29h   | RD1PPS <sup>(1)</sup> | _     | _     |         |                      |                  | RD1PPS<4:0   | >     |       | 00 0000               | uu uuu                     |

### SPECIAL EUNCTION DECISTED SUMMARY PANKS 0.62 (CONTINUED) A 44.

Legend:x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.Note1:Present only on PIC16(L)F15375/76/85/86.

**REGISTER 5-2:**

### **CONFIGURATION WORD 2: SUPERVISORS**

| REGISTER                | 5-2:                                                                                                                                                                                                                                                                                                                                                           | CONFIGUR                                                      | ATION WOR        | D 2: SUPER         | VISORS                                 |                                |                     |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|--------------------|----------------------------------------|--------------------------------|---------------------|--|--|

|                         |                                                                                                                                                                                                                                                                                                                                                                | R/P-1                                                         | R/P-1            | R/P-1              | R/P-1                                  | R/P-1                          | U-1                 |  |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                | DEBUG                                                         | STVREN           | PPS1WAY            | ZCDDIS                                 | BORV                           |                     |  |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                | bit 13                                                        |                  |                    |                                        |                                | bit 8               |  |  |

| <b></b>                 |                                                                                                                                                                                                                                                                                                                                                                |                                                               |                  |                    |                                        |                                |                     |  |  |

| R/P-1                   | R/P-1                                                                                                                                                                                                                                                                                                                                                          | R/P-1                                                         | U-1              | U-1                | U-1                                    | R/P-1                          | R/P-1               |  |  |

| BOREN1                  | BOREN0                                                                                                                                                                                                                                                                                                                                                         | LPBOREN                                                       | —                |                    |                                        | PWRTE                          | MCLRE               |  |  |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                |                                                               |                  |                    |                                        |                                | bit 0               |  |  |

| Lonondi                 |                                                                                                                                                                                                                                                                                                                                                                |                                                               |                  |                    |                                        |                                |                     |  |  |

| Legend:<br>R = Readable | a bit                                                                                                                                                                                                                                                                                                                                                          | P = Programma                                                 | ahle hit         | x = Bit is unkno   |                                        | U = Unimpleme                  | nted hit read as    |  |  |

|                         | , Dit                                                                                                                                                                                                                                                                                                                                                          | i – i logramma                                                |                  |                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | '1'                            | ited bit, read as   |  |  |

| '0' = Bit is cle        | ared                                                                                                                                                                                                                                                                                                                                                           | '1' = Bit is set                                              |                  | W = Writable bi    | t                                      | n = Value when I<br>Erase      | olank or after Bulk |  |  |

| bit 13                  | 1 = Backgrour                                                                                                                                                                                                                                                                                                                                                  | ugger Enable bit<br>nd debugger disa<br>nd debugger ena       |                  |                    |                                        |                                |                     |  |  |

| bit 12                  | 1 = Stack Ove                                                                                                                                                                                                                                                                                                                                                  | ck Overflow/Unde<br>erflow or Underflo<br>erflow or Underflo  | w will cause a F | Reset              |                                        |                                |                     |  |  |

| bit 11                  | 1 = The PPSL                                                                                                                                                                                                                                                                                                                                                   |                                                               | cleared and set  | only once; PPS i   | egisters remain l                      | ocked after one c<br>sequence) | lear/set cycle      |  |  |

| bit 10                  | 1 = ZCD disab                                                                                                                                                                                                                                                                                                                                                  | -Cross Detect Di<br>bled. ZCD can be<br>ys enabled (ZCD       | enabled by sett  |                    | I bit of the ZCDC                      | ON register                    |                     |  |  |

| bit 9                   | 1 = Brown-out                                                                                                                                                                                                                                                                                                                                                  | -out Reset Voltag<br>t Reset voltage (\<br>t Reset voltage (\ | /BOR) set to low | er trip point leve |                                        |                                |                     |  |  |

| bit 8                   | Unimplement                                                                                                                                                                                                                                                                                                                                                    | ed: Read as '1'                                               |                  |                    |                                        |                                |                     |  |  |

| bit 7-6                 | BOREN<1:0>: Brown-out Reset Enable bits<br>When enabled, Brown-out Reset Voltage (VBOR) is set by the BORV bit<br>11 = Brown-out Reset is enabled; SBOREN bit is ignored<br>10 = Brown-out Reset is enabled while running, disabled in Sleep; SBOREN bit is ignored<br>01 = Brown-out Reset is enabled according to SBOREN<br>00 = Brown-out Reset is disabled |                                                               |                  |                    |                                        |                                |                     |  |  |

| bit 5                   | LPBOREN: Low-Power BOR Enable bit<br>1 = ULPBOR is disabled<br>0 = ULPBOR is enabled                                                                                                                                                                                                                                                                           |                                                               |                  |                    |                                        |                                |                     |  |  |

| bit 4-2                 | Unimplement                                                                                                                                                                                                                                                                                                                                                    | ed: Read as '1'                                               |                  |                    |                                        |                                |                     |  |  |

| bit 1                   | PWRTE: Power-up Timer Enable bit         1 = PWRT is disabled         0 = PWRT is enabled                                                                                                                                                                                                                                                                      |                                                               |                  |                    |                                        |                                |                     |  |  |

| bit 0                   | MCLRE: Master Clear (MCLR) Enable bit<br>If LVP = 1:<br>RE3 pin function is MCLR (it will reset the device when driven low)<br>If LVP = 0:<br>1 = MCLR pin is MCLR (it will reset the device when driven low)<br>0 = MCLR pin may be used as general purpose RE3 input                                                                                         |                                                               |                  |                    |                                        |                                |                     |  |  |

|                         | <ul> <li>0 = MCLR pin may be used as general purpose RE3 input</li> <li>ee Vbor parameter for specific trip point voltages.</li> <li>DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers</li> </ul>                                                                                                      |                                                               |                  |                    |                                        |                                |                     |  |  |

2: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

| NOSC<2:0>/<br>COSC<2:0> | Clock Source                              |

|-------------------------|-------------------------------------------|

| 111                     | EXTOSC <sup>(1)</sup>                     |

| 110                     | HFINTOSC <sup>(2)</sup>                   |

| 101                     | LFINTOSC                                  |

| 100                     | SOSC                                      |

| 011                     | Reserved (operates like<br>NOSC = 110)    |

| 010                     | EXTOSC with 4x PLL <sup>(1)</sup>         |

| 001                     | HFINTOSC with 2x PLL <sup>(1)</sup>       |

| 000                     | Reserved (it operates like<br>NOSC = 110) |

| Note 1. EVTORC config   | ured by the FEVTORC bits of               |

**Note 1:** EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 5-1).

### TABLE 9-2: NDIV/CDIV BIT SETTINGS

| NDIV<3:0>/<br>CDIV<3:0> | Clock divider |

|-------------------------|---------------|

| 1111-1010               | Reserved      |

| 1001                    | 512           |

| 1000                    | 256           |

| 0111                    | 128           |

| 0110                    | 64            |

| 0101                    | 32            |

| 0100                    | 16            |

| 0011                    | 8             |

| 0010                    | 4             |

| 0001                    | 2             |

| 0000                    | 1             |

### REGISTER 9-3: OSCCON3: OSCILLATOR CONTROL REGISTER 3

| R/W/HC-0/0 | R/W-0/0 | U-0 | R-0/0 | R-0/0 | U-0 | U-0 | U-0   |

|------------|---------|-----|-------|-------|-----|-----|-------|

| CSWHOLD    | SOSCPWR | —   | ORDY  | NOSCR | —   | —   | —     |

| bit 7      |         |     |       |       |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | CSWHOLD: Clock Switch Hold bit                                                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Clock switch will hold (with interrupt) when the oscillator selected by NOSC is ready</li> <li>0 = Clock switch may proceed when the oscillator selected by NOSC is ready; if this bit</li> </ul>           |

|         | is clear at the time that NOSCR becomes '1', the switch will occur                                                                                                                                                       |

| bit 6   | SOSCPWR: Secondary Oscillator Power Mode Select bit                                                                                                                                                                      |

|         | 1 = Secondary oscillator operating in High-power mode                                                                                                                                                                    |

|         | 0 = Secondary oscillator operating in Low-power mode                                                                                                                                                                     |

| bit 5   | Unimplemented: Read as '0'.                                                                                                                                                                                              |

| bit 4   | ORDY: Oscillator Ready bit (read-only)                                                                                                                                                                                   |

|         | 1 = OSCCON1 = OSCCON2; the current system clock is the clock specified by NOSC                                                                                                                                           |

|         | 0 = A clock switch is in progress                                                                                                                                                                                        |

| bit 3   | NOSCR: New Oscillator is Ready bit (read-only)                                                                                                                                                                           |

|         | <ul> <li>1 = A clock switch is in progress and the oscillator selected by NOSC indicates a "ready" condition</li> <li>0 = A clock switch is not in progress, or the NOSC-selected oscillator is not yet ready</li> </ul> |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                                                                                                               |

<sup>2:</sup> HFINTOSC settings are configured with the HFFRQ bits of the OSCFRQ register (Register 9-6).

| NEOIDTER J       | 0. 000L                                                                                                                                                                                |                   |                                                      |                 | LOIOTEN             |                |              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------|-----------------|---------------------|----------------|--------------|

| R/W-0/0          | R/W-0/0                                                                                                                                                                                | R/W-0/0           | R/W-0/0                                              | R/W-0/0         | R/W-0/0             | U-0            | U-0          |

| EXTOEN           | HFOEN                                                                                                                                                                                  | MFOEN             | LFOEN                                                | SOSCEN          | ADOEN               |                |              |

| bit 7            |                                                                                                                                                                                        |                   |                                                      |                 |                     |                | bit 0        |

|                  |                                                                                                                                                                                        |                   |                                                      |                 |                     |                |              |

| Legend:          |                                                                                                                                                                                        |                   |                                                      |                 |                     |                |              |

| R = Readable     | bit                                                                                                                                                                                    | W = Writable      | bit                                                  | U = Unimpler    | mented bit, read    | d as '0'       |              |

| u = Bit is unch  | anged                                                                                                                                                                                  | x = Bit is unkr   | nown                                                 | -n/n = Value a  | at POR and BC       | R/Value at all | other Resets |

| '1' = Bit is set |                                                                                                                                                                                        | '0' = Bit is cle  | ared                                                 |                 |                     |                |              |

| bit 7            | 1 = EXTOS                                                                                                                                                                              | C is explicitly e | or Manual Requ<br>nabled, operati<br>abled by some i | ing as specifie | (1)<br>d by FEXTOSC | 2              |              |

| bit 6            | <b>HFOEN:</b> HFINTOSC Oscillator Manual Request Enable bit<br>1 = HFINTOSC is explicitly enabled, operating as specified by OSCFRQ<br>0 = HFINTOSC could be enabled by another module |                   |                                                      |                 |                     |                |              |

| bit 5            | 1 = MFINTOS                                                                                                                                                                            | SC is explicitly  | ator Manual Re<br>enabled<br>abled by anoth          |                 | bit                 |                |              |

| bit 4            | •                                                                                                                                                                                      |                   |                                                      |                 |                     |                |              |

| bit 3            |                                                                                                                                                                                        |                   |                                                      |                 |                     |                |              |

| bit 2            | 1 = FRC is e                                                                                                                                                                           | explicitly enable | nual Request E<br>ed<br>by another mo                |                 |                     |                |              |

| bit 1-0          | Unimplemen                                                                                                                                                                             | ted: Read as '    | 0'                                                   |                 |                     |                |              |

|                  |                                                                                                                                                                                        |                   |                                                      |                 |                     |                |              |

### REGISTER 9-5: OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

| U-0                       | U-0                                                                  | R/W-0/0                                                                                                                            | R/W-0/0                                                 | U-0           | U-0              | U-0              | R/W-0/0     |

|---------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------|------------------|------------------|-------------|

|                           |                                                                      | NVMIE                                                                                                                              | NCO1IE                                                  |               |                  | _                | CWG1IE      |

| bit 7                     |                                                                      |                                                                                                                                    | NOOTIL                                                  |               |                  |                  | bit C       |

| Legend:                   |                                                                      |                                                                                                                                    |                                                         |               |                  |                  |             |

| R = Readable              | e bit                                                                | W = Writable                                                                                                                       | bit                                                     | U = Unimpler  | mented bit, read | as '0'           |             |

| u = Bit is und            | hanged                                                               | x = Bit is unkr                                                                                                                    | nown                                                    | -n/n = Value  | at POR and BOI   | R/Value at all o | ther Resets |

| '1' = Bit is se           | t                                                                    | '0' = Bit is cle                                                                                                                   | ared                                                    | HS = Hardwa   | are set          |                  |             |

| bit 7-6<br>bit 5<br>bit 4 | NVMIE: NVM<br>1 = NVM ta:<br>0 = NVM int<br>NCO1IE: NC<br>1 = NCO ro | ted: Read as '<br>Interrupt Enat<br>sk complete int<br>terrupt not enal<br>O Interrupt Ena<br>llover interrupt<br>llover interrupt | ole bit<br>errupt enable<br>oled<br>able bit<br>enabled | d             |                  |                  |             |

| bit 3-1<br>bit 0          | <b>CWG1IE:</b> Co<br>1 = CWG1                                        | ted: Read as '<br>mplementary V<br>nterrupt is ena<br>nterrupt disable                                                             | Vaveform Ger<br>bled                                    | nerator (CWG) | 2 Interrupt Enat | le bit           |             |

| se                        | it PEIE of the IN<br>et to enable a<br>ontrolled by regis            | ny peripheral                                                                                                                      | interrupt                                               |               |                  |                  |             |

### REGISTER 10-9: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

## 11.4 Register Definitions: Voltage Regulator and DOZE Control

### **REGISTER 11-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER <sup>(1)</sup>

| U-0                 | U-0   | U-0               | U-0  | U-0                                                   | U-0 | R/W-0/0 | U-0   |  |  |

|---------------------|-------|-------------------|------|-------------------------------------------------------|-----|---------|-------|--|--|

| _                   | —     | —                 | —    | —                                                     | —   | VREGPM  | _     |  |  |

| bit 7               |       |                   |      |                                                       |     |         | bit C |  |  |

|                     |       |                   |      |                                                       |     |         |       |  |  |

| Legend:             |       |                   |      |                                                       |     |         |       |  |  |

| R = Readable b      | bit   | W = Writable      | bit  | U = Unimplemented bit, read as '0'                    |     |         |       |  |  |

| u = Bit is uncha    | inged | x = Bit is unkr   | nown | -n/n = Value at POR and BOR/Value at all other Resets |     |         |       |  |  |

| '1' = Bit is set '0 |       | '0' = Bit is clea | ared |                                                       |     |         |       |  |  |

bit 7-2 Unimplemented: Read as '0'

bit 1

VREGPM: Voltage Regulator Power Mode Selection bit

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

- Draws lowest current in Sleep, slower wake-up

- Normal Power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up

bit 0 Unimplemented: Read as '1'. Maintain this bit set

Note 1: PIC16F15356/75/76/85/86 only.

2: See Section 37.0 "Electrical Specifications".

### TABLE 14-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Register<br>on Page |

|-----------------------|-------|-------|-------|-------|---------|------------------------|------------------------|------------------------|---------------------|

| PORTE                 | —     |       |       |       | RE3     | RE2 <sup>(1)</sup>     | RE1 <sup>(1)</sup>     | RE0 <sup>(1)</sup>     | 222                 |

| TRISE                 | —     | —     | _     | _     | _(2)    | TRISE2 <sup>(1)</sup>  | TRISE2 <sup>(1)</sup>  | TRISE2 <sup>(1)</sup>  | 222                 |

| LATE <sup>(1)</sup>   | —     | —     |       |       | —       | LATE2                  | LATE2                  | LATE2                  | 223                 |

| ANSELE <sup>(1)</sup> | —     | —     | -     | -     | —       | ANSE2                  | ANSE1                  | ANSE0                  | 217                 |

| WPUE                  | —     | —     |       |       | WPUE3   | WPUE2 <sup>(1)</sup>   | WPUE1 <sup>(1)</sup>   | WPUE0 <sup>(1)</sup>   | 224                 |

| ODCONE <sup>(1)</sup> | —     | —     | -     | -     | —       | ODCE2                  | ODCE1                  | ODCE0                  | 224                 |

| SLRCONE               | _     | _     | _     | _     | SLRE3   | SLRE2 <sup>(1)</sup>   | SLRE1 <sup>(1)</sup>   | SLRE0 <sup>(1)</sup>   | 225                 |

| INLVLE                | —     |       |       |       | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> | 225                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: Present only in PIC16(L)F15375/76/85/86.

2: Unimplemented, read as '1'

### TABLE 14-7: SUMMARY OF CONFIGURATION WORD WITH PORTE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         | _       | DEBUG    | STVREN   | PPS1WAY  | ZCDDIS   | BORV    |         | 102                 |

| CONFIG2 | 7:0  | BOREN   | l <1:0> | LPBOREN  |          |          | _        | PWRTE   | MCLRE   | 103                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTE.

### 14.12 PORTF Registers

Note: Present only on PIC16(L)F15385/86.

### 14.12.1 DATA REGISTER

PORTF is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISF (Register 14-42). Setting a TRISF bit (= 1) will make the corresponding PORTF pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISF bit (= 0) will make the corresponding PORTF pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize an I/O port.

Reading the PORTF register (Register 14-41) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATF).

The PORT data latch LATF (Register 14-43) holds the output port data, and contains the latest value of a LATF or PORTF write.

### 14.12.2 DIRECTION CONTROL

The TRISF register (Register 14-42) controls the PORTF pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISF register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

### 14.12.3 INPUT THRESHOLD CONTROL

The INLVLF register (Register 14-48) controls the input voltage threshold for each of the available PORTF input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTF register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 14.12.4 OPEN-DRAIN CONTROL

The ODCONF register (Register 14-46) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONF bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONF bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

### 14.12.5 SLEW RATE CONTROL

The SLRCONF register (Register 14-47) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONF bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONF bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

### 14.12.6 ANALOG CONTROL

The ANSELF register (Register 14-44) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELF bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELF bits has no effect on digital output functions. A pin with TRIS clear and ANSELF set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELF bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

### 14.12.7 WEAK PULL-UP CONTROL

The WPUF register (Register 14-45) controls the individual weak pull-ups for each port pin.

### 14.12.8 PORTF FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

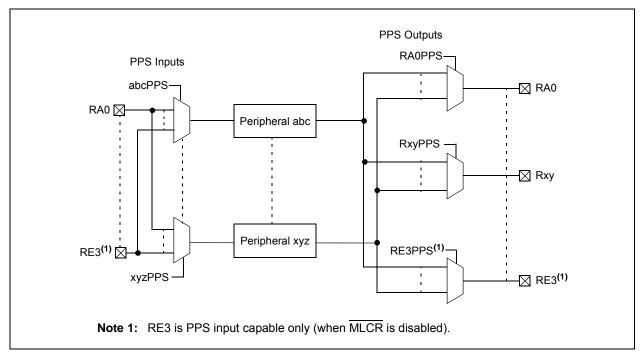

### 15.0 PERIPHERAL PIN SELECT (PPS) MODULE

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections.

All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 15-1.

### FIGURE 15-1: SIMPLIFIED PPS BLOCK DIAGRAM

### 15.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 15-1.

**Note:** The notation "xxx" in the register name is a place holder for the peripheral identifier. For example, CLC1PPS.

### 15.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals are (See Section 15.3 "Bidirectional Pins"):

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 15-2.

**Note:** The notation "Rxy" is a place holder for the pin port and bit identifiers. For example, x and y for PORTA bit 0 would be A and 0, respectively, resulting in the pin PPS output selection register RA0PPS.

### 21.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected.

### 21.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DAC10UT1/2 pins.

- The DAC1R<4:0> range select bits are cleared.

### **30.3 Selectable Input Sources**

The CWG generates the output waveforms from the input sources in Table 30-2.

### TABLE 30-2: SELECTABLE INPUT SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| CWG input PPS pin | CWG1IN PPS  |

| CCP1              | CCP1_out    |

| CCP2              | CCP2_out    |

| PWM3              | PWM3_out    |

| PWM4              | PWM4_out    |

| PWM5              | PWM5_out    |

| PWM6              | PWM6_out    |

| NCO               | NCO1_out    |

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

| CLC3              | LC3_out     |

| CLC4              | LC4_out     |

The input sources are selected using the CWG1ISM register.

### 30.4 Output Control

### 30.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWG1CON1. Auto-shutdown and steering options are unaffected by polarity.

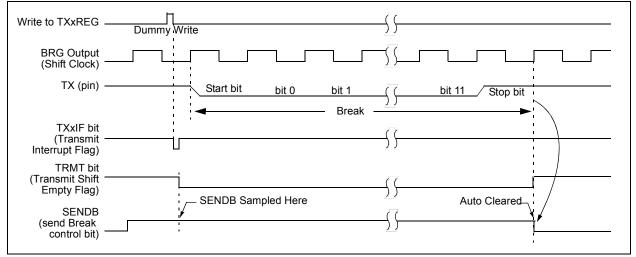

### 33.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCxSTA register and the received data as indicated by RCxREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when:

- · RXxIF bit is set

- · FERR bit is set

- RCxREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 33.3.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RXxIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDxCON register before placing the EUSART in Sleep mode.

### 34.0 REFERENCE CLOCK OUTPUT MODULE

The reference clock output module provides the ability to send a clock signal to the clock reference output pin (CLKR).

The reference clock output module has the following features:

- Selectable input clock

- Programmable clock divider

- Selectable duty cycle

### 34.1 CLOCK SOURCE

The reference clock output module has a selectable clock source. The CLKRCLK register (Register 34-2) controls which input is used.

### 34.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (CLKREN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

### 34.2 PROGRAMMABLE CLOCK DIVIDER

The module takes the system clock input and divides it based on the value of the CLKRDIV<2:0> bits of the CLKRCON register (Register 34-1).

The following configurations can be made based on the CLKRDIV<2:0> bits:

- · Base clock value

- · Base clock value divided by 2

- · Base clock value divided by 4

- Base clock value divided by 8

- Base clock value divided by 16

- Base clock value divided by 32

- Base clock value divided by 64

- Base clock value divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDIV<2:0> bits should only be changed when the module is disabled (CLKREN = 0).

### 34.3 SELECTABLE DUTY CYCLE

The CLKRDC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDC<1:0> bits should only be changed when the module is disabled (CLKREN = 0).

Note: The CLKRDC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

### 34.4 OPERATION IN SLEEP MODE

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal.

| TABLE 37-9: P | LL SPECIFICATIONS |

|---------------|-------------------|

|---------------|-------------------|

| Standard Operating Conditions (unless otherwise stated) VDD $\ge 2.5V$ |                                                      |                                         |       |       |                     |       |            |  |

|------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------|-------|-------|---------------------|-------|------------|--|

| Param.<br>No.                                                          | Sym.                                                 | Characteristic                          | Min.  | Тур†  | Max.                | Units | Conditions |  |

| PLL01                                                                  | FPLLIN                                               | PLL Input Frequency Range               | 4     | —     | 8                   | MHz   |            |  |

| PLL02                                                                  | FPLLOUT                                              | PLL Output Frequency Range              | 16    | —     | 32                  | MHz   | Note 1     |  |

| PLL03                                                                  | TPLLST                                               | PLL Lock Time from Start-up             | —     | 200 / | $\langle - \rangle$ | μs_   | -          |  |

| PLL04                                                                  | FPLLJIT                                              | PLL Output Frequency Stability (Jitter) | -0.25 | \     | 0.25                | -%    |            |  |

| *                                                                      | * These parameters are characterized but not tested. |                                         |       |       |                     |       |            |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: The output frequency of the PLL must meet the Fosc requirements listed in Parameter D002.

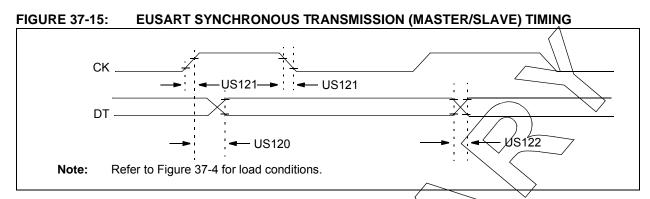

### TABLE 37-21: EUSART SYNCHRONOUS TRANSMISSION CHARACTERISTICS

| Param.<br>No. | Symbol   | Characteristic                    | Min.                | Max. | Units | Conditions                       |

|---------------|----------|-----------------------------------|---------------------|------|-------|----------------------------------|

| JS120         | TCKH2DTV | SYNC XMIT (Master and Slave)      |                     | 80   | ns    | $3.0V \le V\text{DD} \le 5.5V$   |

|               |          | Clock high to data-out valid      | $\langle - \rangle$ | 100  | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| US121         | TCKRF    | Clock out rise time and fall time | $\langle - \rangle$ | 45   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |

|               |          | (Master mode)                     |                     | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |

| US122         | TDTRF    | Data-out rise time and fall time  | $\langle \rangle$   | 45   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |

|               |          |                                   | $\overline{)}$      | 50   | ns    | $1.8V \le V\text{DD} \le 5.5V$   |

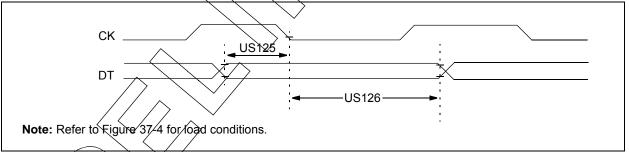

## FIGURE 37-16: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 37-22: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating C | onditions (unless otherwise stated)                                             |      |      |       |            |

|----------------------|---------------------------------------------------------------------------------|------|------|-------|------------|

| Param.<br>No. Symbol | Characteristic                                                                  | Min. | Max. | Units | Conditions |

|                      | SYNC RCV (Master and Slave)<br>Data-setup before CK $\downarrow$ (DT hold time) | 10   | _    | ns    |            |

| US126 TCKL2DTL       | Data-hold after CK $\downarrow$ (DT hold time)                                  | 15   |      | ns    |            |

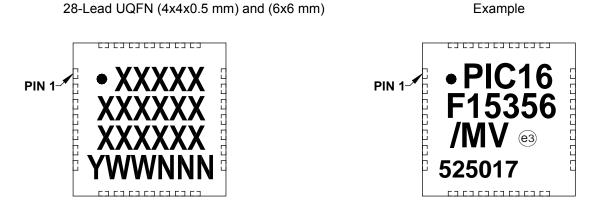

### 40.1 Package Marking Information (Continued)

| Legend | : XXX      | Customer-specific information                                            |

|--------|------------|--------------------------------------------------------------------------|

|        | Y          | Year code (last digit of calendar year)                                  |

|        | ΥY         | Year code (last 2 digits of calendar year)                               |

|        | WW         | Week code (week of January 1 is week '01')                               |

|        | NNN        | Alphanumeric traceability code                                           |

|        |            | Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)                 |

|        | *          | This package is Pb-free. The Pb-free JEDEC designator (e3)               |

|        |            | can be found on the outer packaging for this package.                    |

|        |            |                                                                          |

| Note:  | In the eve | ent the full Microchip part number cannot be marked on one line, it will |

|        | be carrie  | d over to the next line, thus limiting the number of available           |

|        | character  | s for customer-specific information.                                     |

|        |            |                                                                          |