Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 44                                                                           |

| Program Memory Size        | 28KB (16K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 48-UQFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15386t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Н |          |

|---|----------|

|   | _        |

|   |          |

|   |          |

|   |          |

|   |          |

|   | <b>O</b> |

|   |          |

|   |          |

|   | Ŧ        |

|   |          |

|   |          |

|   |          |

|   | 35       |

|   |          |

|   | 5        |

|   |          |

|   | UT I     |

|   |          |

|   |          |

|   | 6        |

| I |          |

| I | 85/      |

| I |          |

| I | 8        |

| I | ő        |

| н |          |

Preliminary

| I/O <sup>(2)</sup> | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO | DAC | Timers              | CCP                 | MWM | SWC | ASSM                          | ZCD | EUSART                    | CLC | CLKR | Interrupt | Pull-up | Basic       |

|--------------------|------------------|------|-----------|------------|-----|-----|---------------------|---------------------|-----|-----|-------------------------------|-----|---------------------------|-----|------|-----------|---------|-------------|

| RC2                | 40               | ANC2 | —         | —          | —   | _   | —                   | CCP1 <sup>(1)</sup> | -   | —   | —                             |     | —                         | -   | —    | IOCC2     | Y       | —           |

| RC3                | 41               | ANC3 | -         | -          | -   | _   | T2IN <sup>(1)</sup> | -                   | _   | _   | SCL1<br>SCL2 <sup>(1,4)</sup> | _   | —                         | _   | -    | IOCC3     | Y       | -           |

| RC4                | 46               | ANC4 | -         | _          | _   | _   | -                   | —                   | _   | -   | SDA1<br>SDI1 <sup>(1,4)</sup> | _   | —                         | _   | _    | IOCC4     | Y       | _           |

| RC5                | 47               | ANC5 | _         | —          | _   | _   | _                   | _                   | _   | _   | _                             | _   | —                         | _   | _    | IOCC5     | Υ       | _           |

| RC6                | 48               | ANC6 | -         | —          | —   | _   | —                   | —                   | _   | —   | —                             |     | TX1<br>CK1 <sup>(1)</sup> | _   | -    | IOCC6     | Y       | —           |

| RC7                | 1                | ANC7 | -         | —          | —   | _   | —                   | —                   | _   | —   | —                             |     | RX1<br>DT1 <sup>(1)</sup> | _   | -    | IOCC7     | Y       | —           |

| RD0                | 42               | AND0 | -         | —          | -   | -   | -                   | —                   | —   | -   | SCK2<br>SCL2 <sup>(1,4)</sup> | —   | -                         | —   | -    | -         | Y       | —           |

| RD1                | 43               | AND1 | —         | —          | —   |     | —                   | —                   | _   | —   | SDA2<br>SDI2 <sup>(1,4)</sup> |     | _                         | _   | -    | —         | Y       | —           |

| RD2                | 44               | AND2 | _         | _          | —   | _   | _                   | _                   | -   | _   | _                             | _   | —                         | -   | _    | _         | Y       | _           |

| RD3                | 45               | AND3 | _         | _          | _   | _   | _                   | _                   |     | _   | _                             |     | _                         |     | —    | _         | Y       | _           |

| RD4                | 2                | AND4 | _         | _          | —   | _   | _                   | —                   | _   | _   | _                             | _   | _                         | _   | _    | _         | Υ       | _           |

| RD5                | 3                | AND5 | _         | —          | —   | _   | _                   | —                   | -   | _   | _                             | -   | _                         | -   | _    | _         | Υ       | _           |

| RD6                | 4                | AND6 | _         | _          | —   | _   | _                   | _                   | _   | —   | _                             | _   | _                         | _   | _    | —         | Υ       | _           |

| RD7                | 5                | AND7 | —         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE0                | 27               | ANE0 | -         | —          | —   | _   | —                   | —                   | -   | —   | —                             | -   | —                         | -   | —    | —         | Υ       | —           |

| RE1                | 28               | ANE1 | _         | —          | —   | _   | -                   | —                   |     | -   | _                             | _   | _                         | _   | —    | -         | Υ       | —           |

| RE2                | 29               | ANE2 | _         | —          | —   | —   | —                   | —                   | —   | —   | —                             | _   | —                         | —   | —    | —         | Y       | —           |

| RE3                | 20               | _    | -         | —          | —   |     | —                   | —                   | _   | —   | —                             | _   | —                         | _   | _    | IOCE3     | Y       | MCLR<br>VPP |

| RF0                | 36               | ANF0 | _         | _          | —   | _   | —                   | _                   | _   | —   | _                             |     | _                         | _   | _    | —         | Υ       | _           |

| RF1                | 37               | ANF1 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF2                | 38               | ANF2 | _         | —          | —   | _   | -                   | _                   | _   | —   | —                             | _   | —                         | _   | —    | —         | Υ       | _           |

| RF3                | 39               | ANF3 | _         | —          | —   | _   | -                   | —                   | -   | —   | —                             | _   | —                         | -   | —    | —         | Υ       | —           |

| RF4                | 12               | ANF4 | —         | —          | —   |     | —                   | —                   |     | _   | _                             |     | _                         |     | —    | —         | Υ       | —           |

TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

| Address | Name     | Bit 7              | Bit 6       | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|--------------------|-------------|---------|---------------|-------------------|-----------|-------|-------|-----------------------|----------------------------|

| Bank 2  |          |                    |             |         | •             | •                 |           |       | •     |                       |                            |

|         |          |                    |             | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics |       |       |                       |                            |

|         |          |                    |             |         |               |                   |           |       |       |                       |                            |

| 10Ch    | _        |                    |             |         | Unimpler      | mented            |           |       |       | _                     | _                          |

| 118h    |          |                    |             |         |               |                   |           |       |       |                       |                            |

| 119h    | RC1REG   | EUSART Receive Dat | a Register  |         |               |                   |           |       |       | 0000 0000             | 0000 0000                  |

| 11Ah    | TX1REG   | EUSART Transmit Da | ta Register |         |               |                   |           |       |       | 0000 0000             | 0000 0000                  |

| 11Bh    | SP1BRGL  |                    |             |         | SP1BR0        | G<7:0>            |           |       |       | 0000 0000             | 0000 0000                  |

| 11Ch    | SP1BRGH  |                    |             |         | SP1BRG        | 6<15:8>           |           |       |       | 0000 0000             | 0000 0000                  |

| 11Dh    | RC1STA   | SPEN               | RX9         | SREN    | CREN          | ADDEN             | FERR      | OERR  | RX9D  | 0000 0000             | 0000 0000                  |

| 11Eh    | TX1STA   | CSRC               | TX9         | TXEN    | SYNC          | SENDB             | BRGH      | TRMT  | TX9D  | 0000 0010             | 0000 0010                  |

| 11Fh    | BAUD1CON | ABDOVF             | RCIDL       | _       | SCKP          | BRG16             | —         | WUE   | ABDEN | 01-0 0-00             | 01-0 0-00                  |

## CISTED SUMMADY DANKS A 62 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

|                       |              | R/W-1                        | U-1                  | R/W-1                            | U-1            | R/W-1                           | R/W-1               |

|-----------------------|--------------|------------------------------|----------------------|----------------------------------|----------------|---------------------------------|---------------------|

|                       |              | LVP                          | —                    | WRTSAF <sup>(1)</sup>            | —              | WRTC <sup>(1)</sup>             | WRTB <sup>(1)</sup> |

|                       |              | bit 13                       | 12                   | 11                               | 10             | 9                               | bit 8               |

| R/W-1                 | U-1          | U-1                          | R/W-1                | R/W-1                            | R/W-1          | R/W-1                           | R/W-1               |

| WRTAPP <sup>(1)</sup> | 0-1          | 0-1                          | SAFEN <sup>(1)</sup> | BBEN <sup>(1)</sup>              | BBSIZE2        | BBSIZE1                         |                     |

|                       |              |                              |                      |                                  |                | _                               | BBSIZE0             |

| bit 7                 | 6            | 5                            | 4                    | 3                                | 2              | 1                               | bit                 |

| Legend:               |              |                              |                      |                                  |                |                                 |                     |

| R = Readable          | e bit        | P = Programı                 | nable bit            | x = Bit is unkn                  | own            | U = Unimplem<br>read as '1'     | nented bit,         |

| '0' = Bit is clea     | ared         | '1' = Bit is set             |                      | W = Writable t                   | bit            | n = Value whe<br>after Bulk Era |                     |

| bit 13                |              | oltage Programr              | ning Enable bit      |                                  |                |                                 |                     |

|                       |              |                              |                      | ICLR/VPP pin fu                  | nction is MCL  | R. MCLRE Cont                   | iguration bit i     |

|                       | ignored      |                              | 4 h a a a d fa a a   |                                  |                |                                 |                     |

|                       |              | MCLR/VPP mus                 |                      | rogramming.<br>le operating fror | n tha LVD ara  | aromming intorf                 | ann Tha             |

|                       |              |                              |                      | om dropping out                  |                |                                 |                     |

|                       |              |                              |                      | e from the config                |                |                                 |                     |

|                       |              | litioned (erased)            | •                    |                                  | garation state |                                 |                     |

| bit 12                | -            | nted: Read as '              |                      |                                  |                |                                 |                     |

| bit 11                |              | torage Area Fla              |                      | ction bit                        |                |                                 |                     |

|                       |              | DT write-protect             |                      |                                  |                |                                 |                     |

|                       |              | ite-protected                | cu                   |                                  |                |                                 |                     |

|                       |              |                              | ot supported in      | the device famil                 | ly and only ap | plicable if SAFE                | <b>N</b> = 0.       |

| bit 10                |              | nted: Read as '              |                      |                                  |                |                                 |                     |

| bit 9                 |              | figuration Regis             |                      | ction bit                        |                |                                 |                     |

|                       |              | uration Register             |                      |                                  |                |                                 |                     |

|                       |              | uration Register             |                      |                                  |                |                                 |                     |

| bit 8                 | Ŭ            | t Block Write Pr             | •                    |                                  |                |                                 |                     |

|                       |              | lock NOT write-              |                      |                                  |                |                                 |                     |

|                       |              | lock write-prote             |                      |                                  |                |                                 |                     |

|                       |              | ble if $\overline{BBEN} = 0$ |                      |                                  |                |                                 |                     |

| bit 7                 |              | pplication Block             |                      | on bit                           |                |                                 |                     |

|                       |              | ation Block NOT              |                      |                                  |                |                                 |                     |

|                       |              | ation Block write            |                      |                                  |                |                                 |                     |

| bit 6-5               | Unimpleme    | nted: Read as '              | 1'                   |                                  |                |                                 |                     |

| bit 4                 | SAFEN: SAF   | Enable bit                   |                      |                                  |                |                                 |                     |

|                       | 1 = SAF dis  | sabled                       |                      |                                  |                |                                 |                     |

|                       | 0 = SAF en   | abled                        |                      |                                  |                |                                 |                     |

| bit 3                 | BBEN: Boot   | Block Enable b               | it                   |                                  |                |                                 |                     |

|                       | 1 = Boot Bl  |                              |                      |                                  |                |                                 |                     |

|                       | 0 = Boot Bl  | ock enabled                  |                      |                                  |                |                                 |                     |

| bit 2-0               | BBSIZE[2:0]  | · Boot Block Size            | Soloction hite       |                                  |                |                                 |                     |

| DIL 2-0               |              |                              |                      |                                  |                |                                 |                     |

| DIL 2-0               | BBSIZE is us | sed only when E              | BBEN = 0             | = 1; after BBEN                  |                |                                 |                     |

**Note 1:** Bits are implemented as sticky bits. Once protection is enabled, it can only be reset through a Bulk Erase.

| REGIST | ER 5-7:      | REVI     | SIONID | : REVIS | SION ID | REGIS     | TER      |   |         |          |         |   |       |

|--------|--------------|----------|--------|---------|---------|-----------|----------|---|---------|----------|---------|---|-------|

| R      | R            | R        | R      | R       | R       | R         | R        | R | R       | R        | R       | R | R     |

| 1      | 0            |          |        | MJRRE   | V<5:0>  |           |          |   |         | MNRRE    | EV<5:0> |   |       |

| bit 13 |              |          |        |         |         |           |          |   |         |          |         |   | bit 0 |

|        |              |          |        |         |         |           |          |   |         |          |         |   |       |

| Legend |              |          |        |         |         |           |          |   |         |          |         |   |       |

|        | R = Read     | able bit |        |         |         |           |          |   |         |          |         |   |       |

|        | '0' = Bit is | cleared  |        |         |         | '1' = Bit | t is set |   | x = Bit | is unkno | own     |   |       |

bit 13-12 **Fixed Value**: Read-only bits

These bits are fixed with value `10' for all devices included in this data sheet.

bit 11-6MJRREV<5:0>: Major Revision ID bits<br/>These bits are used to identify a major revision.bit 5-0MNRREV<5:0>: Minor Revision ID bits

These bits are used to identify a minor revision.

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|---------|--------|--------|--------|--------|-----------|-----------------------|-----------------------|-----------------------|---------------------|

| INTCON  | GIE    | PEIE   | _      | _      | _         | —                     | _                     | INTEDG                | 146                 |

| PIE0    | —      |        | TMR0IE | IOCIE  | —         | _                     |                       | INTE                  | 147                 |

| PIE1    | OSFIE  | CSWIE  | _      |        | —         | —                     |                       | ADIE                  | 148                 |

| PIE2    | _      | ZCDIE  | _      | _      | _         | _                     | C2IE                  | C1IE                  | 149                 |

| PIE3    | RC2IE  | TX2IE  | RC1IE  | TX1IE  | BCL2IE    | SSP2IE                | BCL1IE                | SSP1IE                | 150                 |

| PIE4    | —      | _      | _      | —      | —         | —                     | TMR2IE                | TMR1IE                | 151                 |

| PIR0    | —      | _      | TMR0IF | IOCIF  | —         | —                     |                       | INTF                  | 155                 |

| PIR1    | OSFIF  | CSWIF  | _      |        | _         | _                     | _                     | ADIF                  | 156                 |

| PIR2    | —      | ZCDIF  |        | _      | —         | —                     | C2IF                  | C1IF                  | 157                 |

| PIR3    | RC2IF  | TX2IF  | RC1IF  | TX1IF  | BCL2IF    | SSP2IF                | BCL1IF                | SSP1IF                | 158                 |

| PIR4    | _      |        | _      | _      | —         | _                     | TMR2IF                | TMR1IF                | 159                 |

| IOCAP   | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3    | IOCAP2                | IOCAP1                | IOCAP0                | 255                 |

| IOCAN   | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3    | IOCAN2                | IOCAN1                | IOCAN0                | 255                 |

| IOCAF   | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3    | IOCAF2                | IOCAF1                | IOCAF0                | 256                 |

| IOCBP   | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3    | IOCBP2                | IOCBP1                | IOCBP0                | 257                 |

| IOCBN   | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3    | IOCBN2                | IOCBN1                | IOCBN0                | 257                 |

| IOCBF   | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3    | IOCBF2                | IOCBF1                | IOCBF0                | 258                 |

| IOCCP   | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3    | IOCCP2                | IOCCP1                | IOCCP0                | 259                 |

| IOCCN   | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3    | IOCCN2                | IOCCN1                | IOCCN0                | 259                 |

| IOCCF   | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3    | IOCCF2                | IOCCF1                | IOCCF0                | 259                 |

| IOCEP   | —      |        |        | _      | IOCEP3    | IOCEP2 <sup>(1)</sup> | IOCEP1 <sup>(1)</sup> | IOCEP0 <sup>(1)</sup> | 260                 |

| IOCEN   | —      | _      | _      | —      | IOCEN3    | IOCEN2 <sup>(1)</sup> | IOCEN1 <sup>(1)</sup> | IOCEN0 <sup>(1)</sup> | 260                 |

| IOCEF   | —      |        |        | _      | IOCEF3    | IOCEF2 <sup>(1)</sup> | IOCEF1 <sup>(1)</sup> | IOCEF0 <sup>(1)</sup> | 261                 |

| STATUS  | _      | _      | _      | TO     | PD        | Z                     | DC                    | С                     | 54                  |

| VREGCON | _      | _      | _      | _      | _         | —                     | VREGPM                | _                     | 168                 |

| CPUDOZE | IDLEN  | DOZEN  | ROI    | DOE    | _         |                       | DOZE<2:0>             |                       | 169                 |

| WDTCON0 | —      | —      |        | ١      | NDTPS<4:0 | >                     |                       | SWDTEN                | 175                 |

## TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

**Note 1:** Present only in PIC16(L)F15375/76/85/86.

### 13.3.8 WRERR BIT

The WRERR bit can be used to determine if a write error occurred.

WRERR will be set if one of the following conditions occurs:

- If WR is set while the NVMADRH:NMVADRL points to a write-protected address

- A Reset occurs while a self-write operation was in progress

- An unlock sequence was interrupted

The WRERR bit is normally set by hardware, but can be set by the user for test purposes. Once set, WRERR must be cleared in software.

| Free | LWLO | Actions for PFM when WR = 1                                                                                          | Comments                                                                                                                                              |

|------|------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | x    | Erase the 32-word row of NVMADRH:NVMADRL<br>location. See Section 13.3.3 "NVMREG Erase<br>of PFM"                    | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>All 32 words are erased</li> <li>NVMDATH:NVMDATL is ignored</li> </ul>         |

| 0    | 1    | Copy NVMDATH:NVMDATL to the write latch<br>corresponding to NVMADR LSBs. See Section<br>13.3.3 "NVMREG Erase of PFM" | <ul><li>Write protection is ignored</li><li>No memory access occurs</li></ul>                                                                         |

| 0    | 0    | Write the write-latch data to PFM row. See Sec-<br>tion 13.3.3 "NVMREG Erase of PFM"                                 | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>Write latches are reset to 3FFh</li> <li>NVMDATH:NVMDATL is ignored</li> </ul> |

TABLE 13-4: ACTIONS FOR PFM WHEN WR = 1

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

| WPUA7            | WPUA6   | WPUA5             | WPUA4   | WPUA3          | WPUA2            | WPUA1            | WPUA0       |

| bit 7            |         | ·                 |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | iown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

| •                |         |                   |         |                |                  |                  |             |

### REGISTER 14-5: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-0 WPUA<7:0>: Weak Pull-up Register bits 1 = Pull-up enabled 0 = Pull-up disabled

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

#### REGISTER 14-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCA7   | ODCA6   | ODCA5   | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

ODCA<7:0>: PORTA Open-Drain Enable bits bit 7-0

For RA<7:0> pins, respectively

- 1 = Port pin operates as open-drain drive (sink current only)

- 0 = Port pin operates as standard push-pull drive (source and sink current)

© 2016 Microchip Technology Inc.

| R/W-0/0         | U-0                        | R-0                                            | R/W-0/0        | R/W-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |  |

|-----------------|----------------------------|------------------------------------------------|----------------|-------------------|------------------|------------------|--------------|--|--|--|--|--|

| <b>T0EN</b>     | _                          | TOOUT                                          | T016BIT        |                   | TOOUTI           | PS<3:0>          |              |  |  |  |  |  |

| bit 7           |                            |                                                |                |                   |                  |                  | bit          |  |  |  |  |  |

|                 |                            |                                                |                |                   |                  |                  |              |  |  |  |  |  |

| Legend:         |                            |                                                |                |                   |                  |                  |              |  |  |  |  |  |

| R = Readable    | e bit                      | W = Writable                                   | bit            | U = Unimplen      | nented bit, read | l as '0'         |              |  |  |  |  |  |

| u = Bit is unc  | changed                    | x = Bit is unk                                 | nown           | -n/n = Value a    | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |  |

| '1' = Bit is se | t                          | '0' = Bit is cle                               | ared           |                   |                  |                  |              |  |  |  |  |  |

|                 |                            |                                                |                |                   |                  |                  |              |  |  |  |  |  |

| bit 7           | TOEN: Time                 | r0 Enable bit                                  |                |                   |                  |                  |              |  |  |  |  |  |

|                 |                            | dule is enabled                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 |                            | dule is disabled                               |                | vest power mod    | de               |                  |              |  |  |  |  |  |

| bit 6           | Unimpleme                  | nted: Read as                                  | 0'             |                   |                  |                  |              |  |  |  |  |  |

| bit 5           | T0OUT: Tim<br>Timer0 outp  | er0 Output bit (ı<br>ut bit                    | read-only)     |                   |                  |                  |              |  |  |  |  |  |

| bit 4           | T016BIT: Tir               | mer0 Operating                                 | as 16-bit Time | er Select bit     |                  |                  |              |  |  |  |  |  |

|                 |                            | is a 16-bit timer                              |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 0 = Timer0 i               | s an 8-bit timer                               |                |                   |                  |                  |              |  |  |  |  |  |

| bit 3-0         | T0OUTPS<                   | <b>3:0&gt;:</b> Timer0 ou                      | tput postscale | r (divider) seled | ct bits          |                  |              |  |  |  |  |  |

|                 | 1111 = 1:16                |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 1110 = 1:15<br>1101 = 1:14 |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 1101 - 1.14<br>1100 = 1:13 |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 1011 = 1:12                |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 1010 = 1:11                |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 1001 = 1:10                | Postscaler                                     |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 1000 <b>= 1:9</b>          | Postscaler                                     |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 0111 <b>= 1:8  </b>        |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 0110 = 1:7                 |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 0101 = 1:6                 |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 0100 = 1:5  <br>0011 = 1:4 |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 | 0011 = 1.41<br>0010 = 1:31 |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 |                            |                                                |                |                   |                  |                  |              |  |  |  |  |  |

|                 |                            | 0001 = 1:2 Postscaler<br>0000 = 1:1 Postscaler |                |                   |                  |                  |              |  |  |  |  |  |

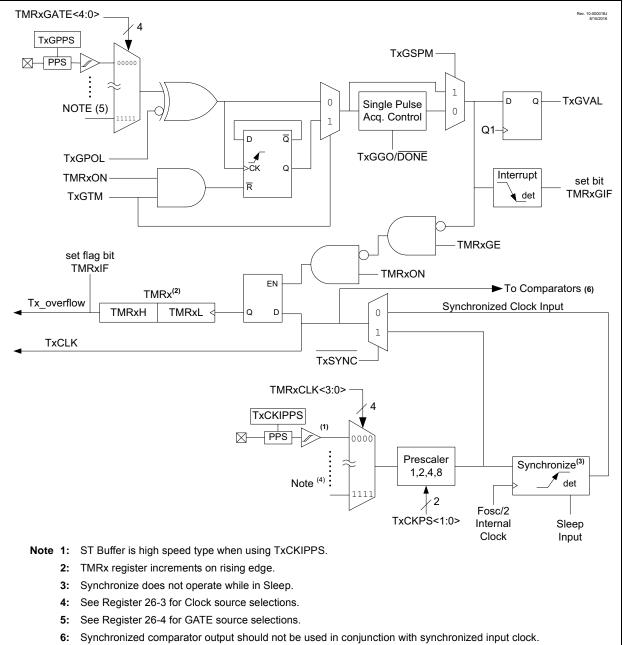

## 26.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is 16-bit timer/counters with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- Clock source for optional comparator synchronization

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- · Time base for the Capture/Compare function

- Auto-conversion Trigger (with CCP)

- · Selectable Gate Source Polarity

- Gate Toggle mode

- · Gate Single-Pulse mode

- Gate Value Status

- · Gate Event Interrupt

Figure 26-1 is a block diagram of the Timer1 module. This device has one instance of Timer1 type modules.

## FIGURE 26-1: TIMER1 BLOCK DIAGRAM

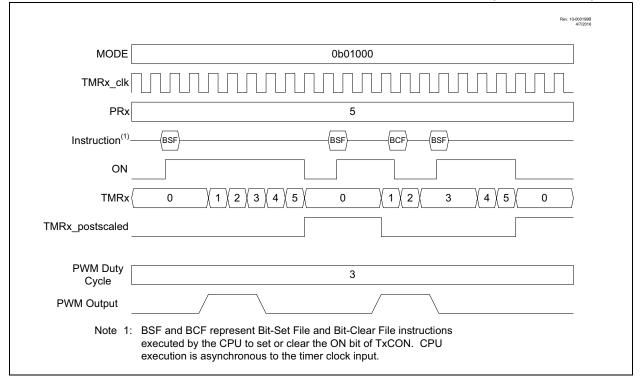

### 27.5.5 SOFTWARE START ONE-SHOT MODE

In One-Shot mode the timer resets and the ON bit is cleared when the timer value matches the PRx period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 27-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the PRx match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a PRx period count match.

FIGURE 27-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

### 27.5.8 LEVEL RESET, EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

In Level -Triggered One-Shot mode the timer count is reset on the external signal level and starts counting on the rising/falling edge of the transition from Reset level to the active level while the ON bit is set. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 01110)

- High Reset level (MODE<4:0> = 01111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control a new external signal edge is required after the ON bit is set to start the counter.

When Level-Triggered Reset One-Shot mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external signal edge that starts the timer. The PWM drive goes inactive when the timer count equals the CCPRx pulse width count. The PWM drive does not go active when the timer count clears at the PRx period count match.

### REGISTER 28-1: CCPxCON: CCPx CONTROL REGISTER (CONTINUED)

- bit 3-0 MODE<3:0>: CCPx Mode Select bits<sup>(1)</sup>

- 1111 1100 = PWM mode (Timer2 as the timer source)

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Reserved

- 1011 = Compare mode: output will pulse 0-1-0; Clears TMR1

- 1010 = Compare mode: output will pulse 0-1-0

- 1001 = Compare mode: clear output on compare match

- 1000 = Compare mode: set output on compare match

- 0111 = Capture mode: every 16th rising edge of CCPx input

- 0110 = Capture mode: every 4th rising edge of CCPx input

- 0101 = Capture mode: every rising edge of CCPx input

- 0100 = Capture mode: every falling edge of CCPx input

- 0011 = Capture mode: every edge of CCPx input

- 0010 = Compare mode: toggle output on match

- 0001 = Compare mode: toggle output on match; clear TMR1

- 0000 = Capture/Compare/PWM off (resets CCPx module)

- **Note 1:** All modes will set the CCPxIF bit, and will trigger an ADC conversion if CCPx is selected as the ADC trigger source.

| Name     | Bit 7                                | Bit 6                       | Bit 5            | Bit 4 | Bit 3        | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |  |  |

|----------|--------------------------------------|-----------------------------|------------------|-------|--------------|------------|--------|--------|---------------------|--|--|

| INTCON   | GIE                                  | PEIE                        | —                | —     | —            | —          | —      | INTEDG | 146                 |  |  |

| PIR4     | —                                    | _                           | _                | —     | _            | _          | TMR2IF | TMR1IF | 159                 |  |  |

| PIE4     | _                                    | _                           | _                | _     | _            | _          | TMR2IE | TMR1IE | 151                 |  |  |

| CCP1CON  | EN                                   | —                           | OUT              | FMT   |              | 366        |        |        |                     |  |  |

| CCP1CAP  |                                      | _                           | —                | —     | —            | — CTS<2:0> |        |        |                     |  |  |

| CCPR1L   | Capture/Con                          | ompare/PWM Register 1 (LSB) |                  |       |              |            |        |        | 368                 |  |  |

| CCPR1H   | Capture/Compare/PWM Register 1 (MSB) |                             |                  |       |              |            |        | 369    |                     |  |  |

| CCP2CON  | EN                                   |                             | OUT              | FMT   |              | 366        |        |        |                     |  |  |

| CCP2CAP  | _                                    | —                           | _                | —     | _            |            | 368    |        |                     |  |  |

| CCPR2L   | Capture/Con                          | npare/PWM F                 | Register 1 (LSB) |       |              |            |        |        |                     |  |  |

| CCPR2H   | Capture/Compare/PWM Register 1 (MSB) |                             |                  |       |              |            |        |        | 368                 |  |  |

| CCP1PPS  | _                                    | —                           |                  |       | CCP1PPS<5:0> |            |        |        |                     |  |  |

| CCP2PPS  | _                                    | —                           | CCP2PPS<5:0>     |       |              |            |        |        |                     |  |  |

| RxyPPS   | _                                    | _                           | _                |       |              | 242        |        |        |                     |  |  |

| ADACT    | _                                    | —                           | —                | —     |              | 280        |        |        |                     |  |  |

| CLCxSELy | _                                    | —                           | —                |       | •            | 412        |        |        |                     |  |  |

| CWG1ISM  | _                                    | —                           | —                | —     |              | 401        |        |        |                     |  |  |

## TABLE 28-5: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

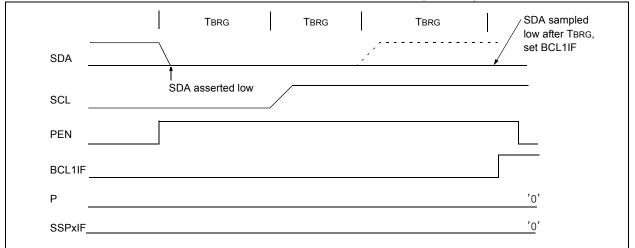

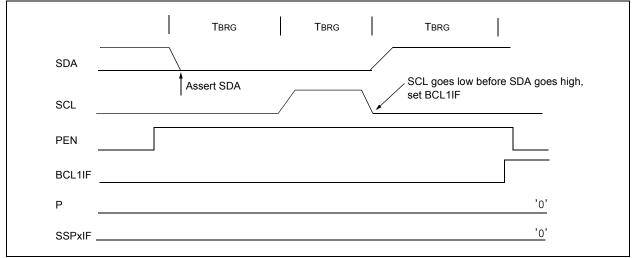

### 32.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 32-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 32-39).

#### FIGURE 32-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 32-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

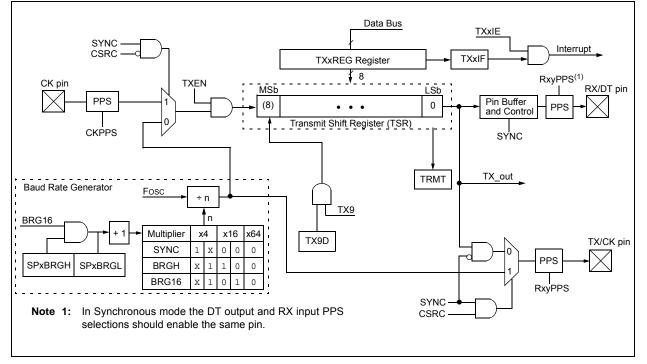

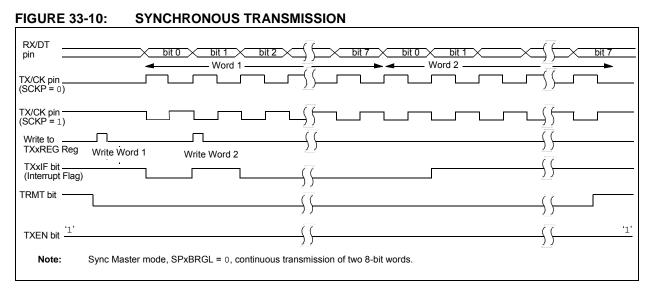

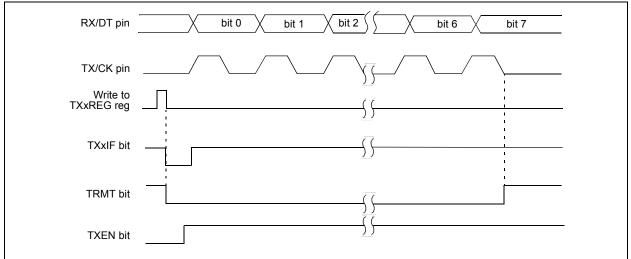

## 33.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

Note: Two identical EUSART modules are implemented on this device, EUSART1 and EUSART2. All references to EUSART1 apply to EUSART2 as well. The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- · 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 33-1 and Figure 33-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

Configurable Logic Cell (CLC)

## FIGURE 33-1: EUSART TRANSMIT BLOCK DIAGRAM

FIGURE 33-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

## 33.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCxSTA register) or the Continuous Receive Enable bit (CREN of the RCxSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence. To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RXxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCxREG. The RXxIF bit remains set as long as there are unread characters in the receive FIFO.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

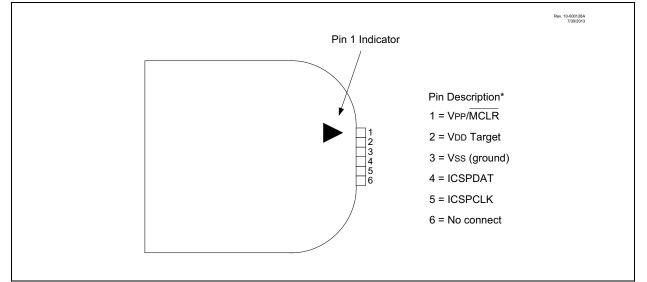

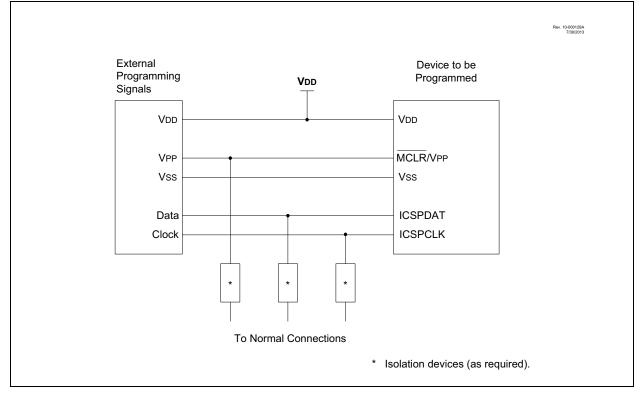

#### FIGURE 35-2: PICkit<sup>™</sup> PROGRAMMER STYLE CONNECTOR INTERFACE

| TABLE 37-4: I/O PORTS     |      |                                                  |                                       |                 |                               |                          |                                                          |  |  |  |

|---------------------------|------|--------------------------------------------------|---------------------------------------|-----------------|-------------------------------|--------------------------|----------------------------------------------------------|--|--|--|

| Standard<br>Param.<br>No. | Sym. | ng Conditions (unless otherwis<br>Characteristic | se stated)<br>Min.                    | Тур†            | Max.                          | Units                    | Conditions                                               |  |  |  |

|                           | VIL  | Input Low Voltage                                |                                       |                 |                               |                          |                                                          |  |  |  |

|                           |      | I/O PORT:                                        |                                       |                 |                               |                          |                                                          |  |  |  |

| D300                      |      | with TTL buffer                                  | _                                     | _               | 0.8                           | V                        | 4.5V ≤ VDD ≤ 5.5V                                        |  |  |  |

| D301                      |      |                                                  | _                                     | _               | 0.15 VDD                      | V                        | 1.8V ≤ Vop ≤ 4.5V                                        |  |  |  |

| D302                      |      | with Schmitt Trigger buffer                      | _                                     | _               | 0.2 VDD                       | V                        | 2.0V ≤ VpD ≤ 5.5V                                        |  |  |  |

| D303                      |      | with I <sup>2</sup> C levels                     | _                                     | _               | 0.3 VDQ                       | V                        |                                                          |  |  |  |

| 0304                      |      | with SMBus levels                                | _                                     | _               | 0.8                           | V                        | $2.7V \le VDD \le 5.5V$                                  |  |  |  |

| D305                      |      | MCLR                                             | _                                     | _               | 0.2 Vdd                       | $\setminus$ $\checkmark$ |                                                          |  |  |  |

|                           | VIH  | Input High Voltage                               |                                       |                 |                               |                          |                                                          |  |  |  |

|                           |      | I/O PORT:                                        |                                       |                 | //                            |                          |                                                          |  |  |  |

| 0320                      |      | with TTL buffer                                  | 2.0                                   | 1               | $- \overline{-}$              | $\setminus \vee^{\vee}$  | $4.5V \leq V\text{DD} \leq 5.5V$                         |  |  |  |

| 0321                      |      |                                                  | 0.25 VDD +<br>0.8                     | <u> </u>        |                               | X                        | $1.8V \le V\text{DD} \le 4.5V$                           |  |  |  |

| 0322                      |      | with Schmitt Trigger buffer                      | 0.8 Vdd <                             | $\overline{}$   | $\langle \mathcal{F} \rangle$ | V                        | $2.0V \leq V \text{DD} \leq 5.5 V$                       |  |  |  |

| D323                      |      | with I <sup>2</sup> C levels                     | 0.7 Yap                               | /-/             | $\searrow$                    | V                        |                                                          |  |  |  |

| D324                      |      | with SMBus levels                                | 2.1                                   |                 | $\setminus -$                 | V                        | $2.7V \leq V\text{DD} \leq 5.5V$                         |  |  |  |

| D325                      |      | MCLR                                             | 0.7 VDD                               |                 | V _                           | V                        |                                                          |  |  |  |

|                           | lı∟  | Input Leakage Current <sup>(1)</sup>             | $\sim$ $\sim$ $\sim$                  | $\overline{//}$ |                               |                          |                                                          |  |  |  |

| D340                      |      | I/O Ports                                        |                                       | ±5              | ± 125                         | nA                       | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 85°C  |  |  |  |

| D341                      |      |                                                  | $\langle  \rangle$                    | ±5              | ± 1000                        | nA                       | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 125°C |  |  |  |

| D342                      |      | MCLR <sup>(2)</sup>                              | $\overline{}$                         | ± 50            | ± 200                         | nA                       | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance, 85°C   |  |  |  |

|                           | IPUR | Weak Pull-up Current                             | · · · · · · · · · · · · · · · · · · · |                 |                               |                          | •                                                        |  |  |  |

| 0350                      |      |                                                  | 25                                    | 120             | 200                           | μA                       | VDD = 3.0V, VPIN = VSS                                   |  |  |  |

|                           | Vol  | Output Løw Voltage                               |                                       |                 |                               |                          |                                                          |  |  |  |

| 0360                      |      | I/O ports                                        | —                                     | _               | 0.6                           | V                        | IOL = 10.0mA, VDD = 3.0V                                 |  |  |  |

|                           | Voн  | Øutput High Voltage                              | •                                     |                 |                               |                          | •                                                        |  |  |  |

| 0370                      |      | I/O ports                                        | Vdd - 0.7                             | _               | _                             | V                        | ЮН = 6.0 mA, VDD = 3.0V                                  |  |  |  |

| D380                      | CIO  | All I/O pins                                     | _                                     | 5               | 50                            | pF                       |                                                          |  |  |  |

† Data in "Typ) column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent

normal operating conditions. Higher leakage current may be measured at different input voltages.

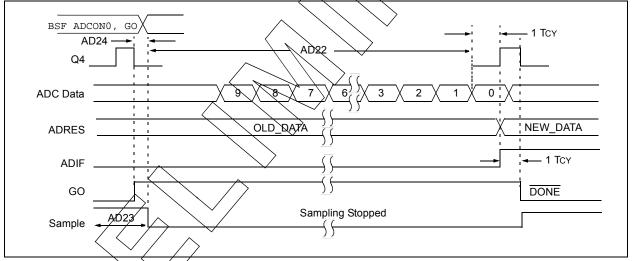

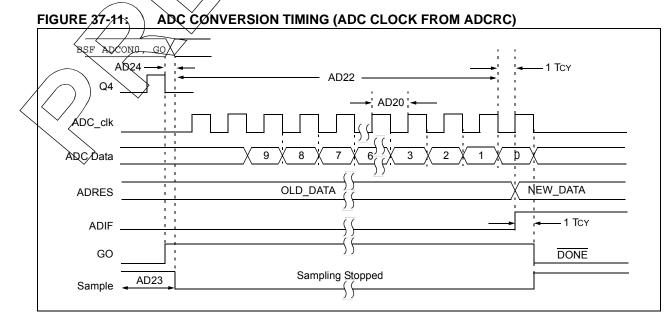

### TABLE 37-13: ANALOG-TO-DIGITAL CONVERTER (ADC) CONVERSION TIMING SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |      |                                              |      |      |      |       |                                                                              |

|---------------------------------------------------------|------|----------------------------------------------|------|------|------|-------|------------------------------------------------------------------------------|

| Param.<br>No.                                           | Sym. | Characteristic                               | Min. | Тур† | Max. | Units | Conditions                                                                   |

| AD20                                                    | Tad  | ADC Clock Period                             | 1    | _    | 9    | μs    | The requirement is to set ADCCS correctly to produce this period/friequency. |

| AD21                                                    |      |                                              | 1    | 2    | 6    | μs    | Using FRC as the ADC clock<br>source ADOSC = 1                               |

| AD22                                                    | TCNV | Conversion Time                              | -    | 11   | -    | TAD   | Set of GO/DONE bit to Clear of GO/DONE bit                                   |

| AD23                                                    | TACQ | Acquisition Time                             | —    | 2    | Ύ,   | μs    |                                                                              |

| AD24                                                    | Тнср | Sample and Hold Capacitor<br>Disconnect Time | —    | -    | _/   | μs    | Fosc-based clock source<br>FRC-based clock source                            |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## FIGURE 37-10: ADC CONVERSION TIMING (AQC CLOCK Fosc-BASED)

© 2016 Microchip Technology Inc.

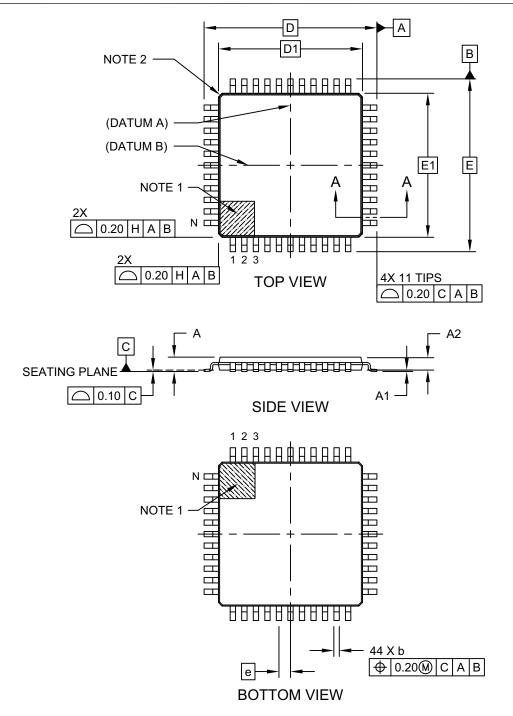

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2