Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 44                                                                           |

| Program Memory Size        | 28KB (16K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 43x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-TQFP                                                                      |

| Supplier Device Package    | 48-TQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15386t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 5: 48-PIN ALLOCATION TABLE (PIC16(L)F15385, PIC16(L)F15386) (CONTINUED)

| I/O <sup>(2)</sup> | 48-Pin UQFN/TQFP | ADC  | Reference | Comparator | NCO     | DAC | Timers | ССР  | MWM     | CWG            | MSSP                                           | ZCD | EUSART            | CLC     | CLKR | Interrupt | Pull-up | Basic |

|--------------------|------------------|------|-----------|------------|---------|-----|--------|------|---------|----------------|------------------------------------------------|-----|-------------------|---------|------|-----------|---------|-------|

| RF5                | 13               | ANF5 | —         |            | _       | _   |        | _    | _       | _              |                                                |     | —                 | —       | —    | —         | Y       | —     |

| RF6                | 14               | ANF6 | —         | —          | —       | —   | -      | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | Y       | _     |

| RF7                | 15               | ANF7 | _         | _          | —       | _   |        | —    | —       | _              | -                                              | _   | —                 | —       | —    | —         | Y       | —     |

| VDD                | 30               | —    | —         | —          | —       | —   | -      | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | Y       | VDD   |

| VDD                | 7                | —    | —         | —          | —       | _   |        | _    | —       | —              | -                                              | —   | —                 | —       | —    | —         | —       | VDD   |

| Vss                | 6                | —    | —         |            | _       |     |        | _    | —       |                |                                                |     | _                 | —       | —    | —         | —       | Vss   |

| Vss                | 31               | _    | _         | —          | —       | —   | _      | _    | _       | —              | —                                              | —   | —                 | _       | —    | _         | —       | Vss   |

| OUT <sup>(2)</sup> | —                | —    | —         | C1OUT      | NCO10UT |     | TMR0   | CCP1 | PWM3OUT | CWG1A<br>CWG2A | SDO1<br>SDO2                                   |     | DT <sup>(3)</sup> | CLC1OUT | CLKR | —         | -       | —     |

|                    | —                | —    |           | C2OUT      | —       | _   |        | CCP2 | PWM4OUT | CWG1B<br>CWG2B | SCK1<br>SCK2                                   | -   | CK1<br>CK2        | CLC2OUT | -    | —         | -       | —     |

|                    | —                | -    | _         | _          | -       | —   | —      | _    | PWM5OUT | CWG1C<br>CWG2C | SCK1 <sup>(3,4)</sup><br>SCL2 <sup>(3,4)</sup> | _   | TX1<br>TX2        | CLC3OUT | _    | _         | -       | -     |

|                    | —                | _    | _         | _          | _       | —   | _      | _    | PWM6OUT | CWG1D<br>CWG2D | SDA1 <sup>(3,4)</sup><br>SDA2 <sup>(3,4)</sup> | _   | —                 | CLC4OUT | -    | _         | -       | —     |

Note 1: This is a PPS re-mappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All digital output signals shown in this row are PPS re-mappable. These signals may be mapped to output onto one of several PORTx pin options.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. PPS assignments to the other pins will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUS input buffer thresholds.

| Name                                                    | Function              | Input<br>Type | Output Type | Description                                       |

|---------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------|

| RA0/ANA0/C1IN0-/C2IN0-/CLCIN0 <sup>(1)</sup> /<br>IOCA0 | RA0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IOCAU                                                   | ANA0                  | AN            | —           | ADC Channel A0 input.                             |

|                                                         | C1IN0-                | AN            | —           | Comparator negative input.                        |

|                                                         | C2IN0-                | AN            | —           | Comparator negative input.                        |

|                                                         | CLCIN0 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.             |

|                                                         | IOCA0                 | TTL/ST        | —           | Interrupt-on-change input.                        |

| RA1/ANA1/C1IN1-/C2IN1-/CLCIN1 <sup>(1)</sup> /<br>IOCA1 | RA1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IUCAT                                                   | ANA1                  | AN            | _           | ADC Channel A1 input.                             |

|                                                         | C1IN1-                | AN            | —           | Comparator negative input.                        |

|                                                         | C2IN1-                | AN            | _           | Comparator negative input.                        |

|                                                         | CLCIN1 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.             |

|                                                         | IOCA1                 | TTL/ST        | —           | Interrupt-on-change input.                        |

| RA2/ANA2/C1IN0+/C2IN0+/<br>DAC1OUT1/IOCA2               | RA2                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| DACTOUTI/IOCAZ                                          | ANA2                  | AN            | _           | ADC Channel A2 input.                             |

|                                                         | C1IN0+                | AN            | _           | Comparator positive input.                        |

|                                                         | C2IN0+                | AN            | _           | Comparator positive input.                        |

|                                                         | DAC1OUT1              | _             | AN          | Digital-to-Analog Converter output.               |

|                                                         | IOCA2                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA3/ANA3/C1IN1+/VREF+/DACREF+/                          | RA3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

| IOCA3                                                   | ANA3                  | AN            | _           | ADC Channel A3 input.                             |

|                                                         | C1IN1+                | AN            | _           | Comparator positive input.                        |

|                                                         | VREF+                 | AN            | _           | External ADC and/or DAC positive reference input. |

|                                                         | IOCA3                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA4/ANA4/T0CKI <sup>(1)</sup> /IOCA4                    | RA4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA4                  | AN            | _           | ADC Channel A4 input.                             |

|                                                         | T0CKI <sup>(1)</sup>  | TTL/ST        | —           | Timer0 clock input.                               |

|                                                         | IOCA4                 | TTL/ST        | _           | Interrupt-on-change input.                        |

| RA5/ANA5/SS1 <sup>(1)</sup> /T1G <sup>(1)</sup> /IOCA5  | RA5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                              |

|                                                         | ANA5                  | AN            | —           | ADC Channel A5 input.                             |

|                                                         | SS1 <sup>(1)</sup>    | TTL/ST        | _           | MSSP1 SPI slave select input.                     |

|                                                         | T1G <sup>(1)</sup>    | TTL/ST        | _           | Timer1 gate input.                                |

|                                                         | IOCA5                 | TTL/ST        | _           | Interrupt-on-change input.                        |

### **TABLE 1-3:** PIC16(L)F15375/76 PINOUT DESCRIPTION

CMOS = CMOS compatible input or output Legend: AN = Analog input or output TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels XTAL

HV = High Voltage

Note

= Crystal levels This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx 1: pins. Refer to Table 15-4 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-5, Table 15-6 and Table 15-6.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for  $I^2C$  logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, 4: instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

<sup>=</sup> Open-Drain 1<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

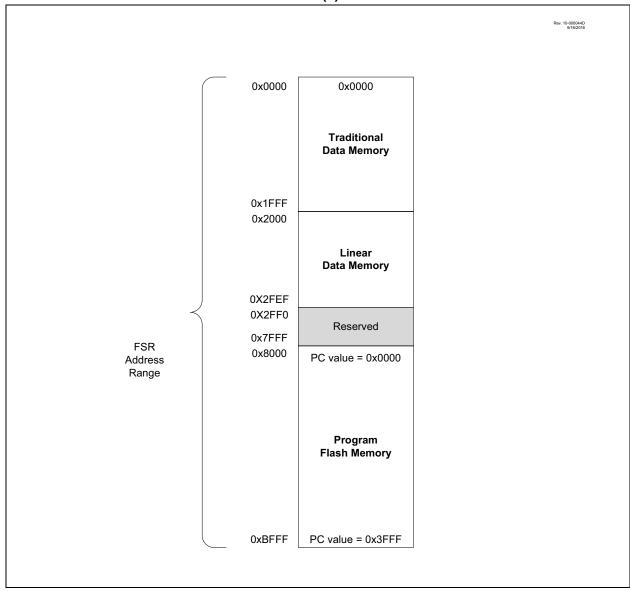

The HIGH directive will set bit 7 if a label points to a location in the program memory. This applies to the assembly code Example 4-2 shown below.

## EXAMPLE 4-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants  |            |      |         |      |  |

|------------|------------|------|---------|------|--|

| RETLW      | DATA0      |      | ;Index0 | data |  |

| RETLW      | DATA1      |      | ;Index1 | data |  |

| RETLW      | DATA2      |      |         |      |  |

| RETLW      | DATA3      |      |         |      |  |

| my_functi  | on         |      |         |      |  |

| ;… LOI     | TS OF CODE | c    |         |      |  |

| MOVLW      | LOW con    | stan | ts      |      |  |

| MOVWF      | FSR1L      |      |         |      |  |

| MOVLW      | HIGH CO    | nsta | nts     |      |  |

| MOVWF      | FSR1H      |      |         |      |  |

| MOVIW      | 0[FSR1]    |      |         |      |  |

| ; THE PROG | RAM MEMORY | Y IS | IN W    |      |  |

|            |            |      |         |      |  |

# 4.2 Memory Access Partition (MAP)

User Flash is partitioned into:

- Application Block

- Boot Block, and

- Storage Area Flash (SAF) Block

The user can allocate the memory usage by setting the BBEN bit, selecting the size of the partition defined by BBSIZE[2:0] bits and enabling the Storage Area Flash by the SAFEN bit of the Configuration Word (see Register 5-4). Refer to Table 4-2 for the different user Flash memory partitions.

# 4.2.1 APPLICATION BLOCK

Default settings of the Configuration bits ( $\overline{BBEN} = 1$ and  $\overline{SAFEN} = 1$ ) assign all memory in the user Flash area to the Application Block.

# 4.2.2 BOOT BLOCK

If  $\overline{\text{BBEN}} = 1$ , the Boot Block is enabled and a specific address range is alloted as the Boot Block based on the value of the BBSIZE bits of Configuration Word (Register 5-4) and the sizes provided in Table 5-1.

# 4.2.3 STORAGE AREA FLASH

Storage Area Flash (SAF) is enabled by clearing the SAFEN bit of the Configuration Word in Register 5-4. If enabled, the SAF block is placed at the end of memory and spans 128 words. If the Storage Area Flash (SAF) is enabled, the SAF area is not available for program execution.

# 4.2.4 MEMORY WRITE PROTECTION

All the memory blocks have corresponding write protection fuses WRTAPP, WRTB and WRTC bits in the Configuration Word 4 (Register 5-4). If write-protected locations are written from NVMCON registers, memory is not changed and the WRERR bit defined in Register 12-5 is set as explained in **Section 13.3.8 "WRERR Bit**".

# 4.2.5 MEMORY VIOLATION

A Memory Execution Violation Reset occurs while executing an instruction that has been fetched from outside a valid execution area, clearing the MEMV bit. Refer to **Section 8.12 "Memory Execution Violation"** for the available valid program execution areas and the PCON1 register definition (Register 8-3) for MEMV bit conditions.

| Address            | Name                   | Bit 7         | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|--------------------|------------------------|---------------|---------|---------|---------|---------|------------------------|------------------------|------------------------|-----------------------|----------------------------|

| Bank 62 (Co        | ontinued)              | •             | •       |         | •       | •       | -                      | •                      |                        | •                     |                            |

| 1F4Eh              | ANSELC                 | ANSC7         | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2                  | ANSC1                  | ANSC0                  | 1111 1111             | 1111 1111                  |

| 1F4Fh              | WPUC                   | WPUC7         | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2                  | WPUC1                  | WPUC0                  | 0000 0000             | 0000 0000                  |

| 1F50h              | ODCONC                 | ODCC7         | ODCC6   | ODCC5   | ODCC4   | ODCC3   | ODCC2                  | ODCC1                  | ODCC0                  | 0000 0000             | 0000 0000                  |

| 1F51h              | SLRCONC                | SLRC7         | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2                  | SLRC1                  | SLRC0                  | 1111 1111             | 1111 1111                  |

| 1F52h              | INLVLC                 | INLVLC7       | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2                | INLVLC1                | INLVLC0                | 1111 1111             | 1111 1111                  |

| 1F53h              | IOCCP                  | IOCCP7        | IOCCP6  | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2                 | IOCCP1                 | IOCCP0                 | 0000 0000             | 0000 0000                  |

| 1F54h              | IOCCN                  | IOCCN7        | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2                 | IOCCN1                 | IOCCN0                 | 0000 0000             | 0000 0000                  |

| 1F55h              | IOCCF                  | IOCCF7        | IOCCF6  | IOCCF5  | IOCCF4  | IOCCF3  | IOCCF2                 | IOCCF1                 | IOCCF0                 | 0000 0000             | 0000 0000                  |

| 1F56h<br><br>1F58h | _                      | Unimplemented |         |         |         |         |                        |                        |                        |                       | _                          |

| 1F59h              | ANSELD <sup>(1)</sup>  | ANSD7         | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2                  | ANSD1                  | ANSD0                  | 1111 1111             | 1111 1111                  |

| 1F5Ah              | WPUD <sup>(1)</sup>    | WPUD7         | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2                  | WPUD1                  | WPUD0                  | 0000 0000             | 0000 0000                  |

| 1F5Bh              | ODCOND <sup>(1)</sup>  | ODCD7         | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2                  | ODCD1                  | ODCD0                  | 0000 0000             | 0000 0000                  |

| 1F5Ch              | SLRCOND <sup>(1)</sup> | SLRD7         | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2                  | SLRD1                  | SLRD0                  | 1111 1111             | 1111 1111                  |

| 1F5Dh              | INLVLD <sup>(1)</sup>  | INLVLD7       | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2                | INLVLD1                | INLVLD0                | 1111 1111             | 1111 1111                  |

| 1F5Eh<br><br>1F63h | _                      |               |         |         | Unimple | mented  |                        |                        |                        | -                     | _                          |

| 1F64h              | ANSELE <sup>(1)</sup>  | _             | _       | _       | _       | _       | ANSE2                  | ANSE1                  | ANSE0                  | 111                   | uuu                        |

| 1F65h              | WPUE                   | —             | _       | _       | _       | WPUE3   | WPUE2 <sup>(1)</sup>   | WPUE1 <sup>(1)</sup>   | WPUE0 <sup>(1)</sup>   | 0000                  | uuuu                       |

| 1F66h              | ODCONE <sup>(1)</sup>  | _             | _       | _       | _       | _       | ODCE2                  | ODCE1                  | ODCE0                  | 000                   | 000                        |

| 1F67h              | SLRCONE <sup>(1)</sup> | _             | _       | _       | _       | _       | SLRE2                  | SLRE1                  | SLRE0                  | 111                   | 111                        |

| 1F68h              | INLVLE                 | _             | _       | _       | _       | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> | 1111                  | uuuu                       |

| 1F69h              | IOCEP                  | _             | _       | _       | _       | IOCEP3  | IOCEP2 <sup>(1)</sup>  | IOCEP1 <sup>(1)</sup>  | IOCEP0 <sup>(1)</sup>  | 0000                  | 0000                       |

| 1F6Ah              | IOCEN                  | —             | _       | _       | _       | IOCEN3  | IOCEN2 <sup>(1)</sup>  | IOCEN1 <sup>(1)</sup>  | IOCEN0 <sup>(1)</sup>  | 0000                  | 0000                       |

| 1F6Bh              | IOCEF                  | _             | _       | _       | _       | IOCEF3  | IOCEF2 <sup>(1)</sup>  | IOCEF1 <sup>(1)</sup>  | IOCEF0 <sup>(1)</sup>  | 0000                  | 0000                       |

| 1F6Ch<br><br>1F6Fh | _                      |               |         | _       | -       |         |                        |                        |                        |                       |                            |

### SPECIAL EUNCTION DECISTED SUMMARY PANKS 0.62 (CONTINUED) TABLE A 44.

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Present only on PIC16(L)F15375/76/85/86.

# FIGURE 4-10: INDIRECT ADDRESSING PIC16(L)F15356/76/86

© 2016 Microchip Technology Inc.

# **REGISTER 9-7: OSCTUNE: HFINTOSC TUNING REGISTER**

| U-0   | U-0 | R/W-1/1 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-------|-----|---------|------------|---------|---------|---------|---------|--|--|

| —     | —   |         | HFTUN<5:0> |         |         |         |         |  |  |

| bit 7 |     |         |            |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 <b>U</b> | nimplemented: Read as '0'.                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01               | FTUN<5:0>: HFINTOSC Frequency Tuning bits 1 1111 = Maximum frequency 1 1110 =                                                                                                                                       |

|                  | <ul> <li>0 0001 =</li> <li>0 0000 = Center frequency. Oscillator module is running at the calibrated frequency (default value).</li> <li>1 1111 =</li> <li>0 0001 =</li> <li>0 0000 = Minimum frequency.</li> </ul> |

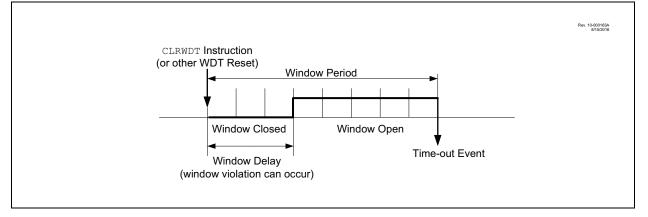

# TABLE 12-2: WDT CLEARING CONDITIONS

| Conditions                                       | WDT        |  |  |

|--------------------------------------------------|------------|--|--|

| WDTE<1:0> = 00                                   |            |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                    |            |  |  |

| WDTE<1:0> = 10 and enter Sleep                   | Cleared    |  |  |

| CLRWDT Command                                   | Cleared    |  |  |

| Oscillator Fail Detected                         |            |  |  |

| Exit Sleep + System Clock = SOSC, EXTOSC, INTOSC |            |  |  |

| Change INTOSC divider (IRCF bits)                | Unaffected |  |  |

# FIGURE 12-2: WINDOW PERIOD AND DELAY

| Quitout Signal        | RxyPPS         | Remappable to Pins of PORTx |       |              |       |       |  |  |  |  |

|-----------------------|----------------|-----------------------------|-------|--------------|-------|-------|--|--|--|--|

| Output Signal<br>Name | Ragister Value |                             | PIC   | C16(L)F15375 | /76   |       |  |  |  |  |

|                       | -              | PORTA                       | PORTB | PORTC        | PORTD | PORTE |  |  |  |  |

| CLKR                  | 0x1B           |                             | •     | •            |       |       |  |  |  |  |

| NCO1OUT               | 0x1A           | •                           |       |              | •     |       |  |  |  |  |

| TMR0                  | 0x19           |                             | •     | •            |       |       |  |  |  |  |

| SDO2/SDA2             | 0x18           |                             | •     |              | •     |       |  |  |  |  |

| SCK2/SCL2             | 0x17           |                             | •     |              | •     |       |  |  |  |  |

| SDO1/SDA1             | 0x16           |                             | •     | •            |       |       |  |  |  |  |

| SCK1/SCL1             | 0x15           |                             | •     | •            |       |       |  |  |  |  |

| C2OUT                 | 0x14           | ٠                           |       |              |       | ٠     |  |  |  |  |

| C1OUT                 | 0x13           | ٠                           |       |              | •     |       |  |  |  |  |

| DT2                   | 0x12           |                             | •     |              | •     |       |  |  |  |  |

| TX2/CK2               | 0x11           |                             | •     |              | ٠     |       |  |  |  |  |

| DT1                   | 0x10           |                             | •     | •            |       |       |  |  |  |  |

| TX1/CK1               | 0x0F           |                             | •     | •            |       |       |  |  |  |  |

| PWM6OUT               | 0x0E           | ٠                           |       |              | ٠     |       |  |  |  |  |

| PWM5OUT               | 0x0D           | ٠                           |       | •            |       |       |  |  |  |  |

| PWM4OUT               | 0x0C           |                             | •     |              | •     |       |  |  |  |  |

| PWM3OUT               | 0x0B           |                             | •     |              | ٠     |       |  |  |  |  |

| CCP2                  | 0x0A           |                             | •     | •            |       |       |  |  |  |  |

| CCP1                  | 0x09           |                             | •     | •            |       |       |  |  |  |  |

| CWG1D                 | 0x08           |                             | •     |              | •     |       |  |  |  |  |

| CWG1C                 | 0x07           |                             | •     |              | •     |       |  |  |  |  |

| CWG1B                 | 0x06           |                             | •     |              | •     |       |  |  |  |  |

| CWG1A                 | 0x05           |                             | •     | •            |       |       |  |  |  |  |

| CLC4OUT               | 0x04           |                             | •     |              | •     |       |  |  |  |  |

| CLC3OUT               | 0x03           |                             | •     |              | •     |       |  |  |  |  |

| CLC2OUT               | 0x02           | •                           |       | •            |       |       |  |  |  |  |

| CLC1OUT               | 0x01           | •                           |       | •            |       |       |  |  |  |  |

# TABLE 15-6: PPS OUTPUT SIGNAL ROUTING OPTIONS (PIC16(L)F15375/76)

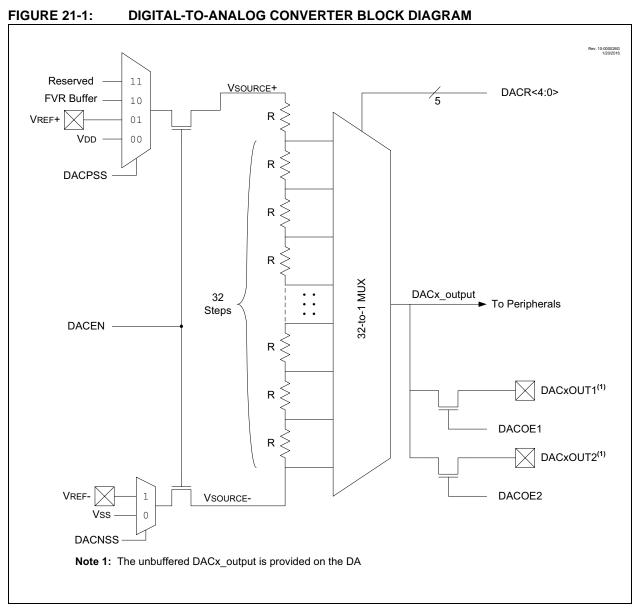

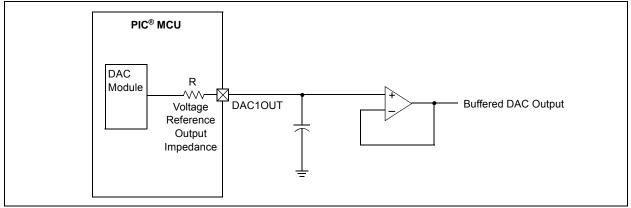

# FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

© 2016 Microchip Technology Inc.

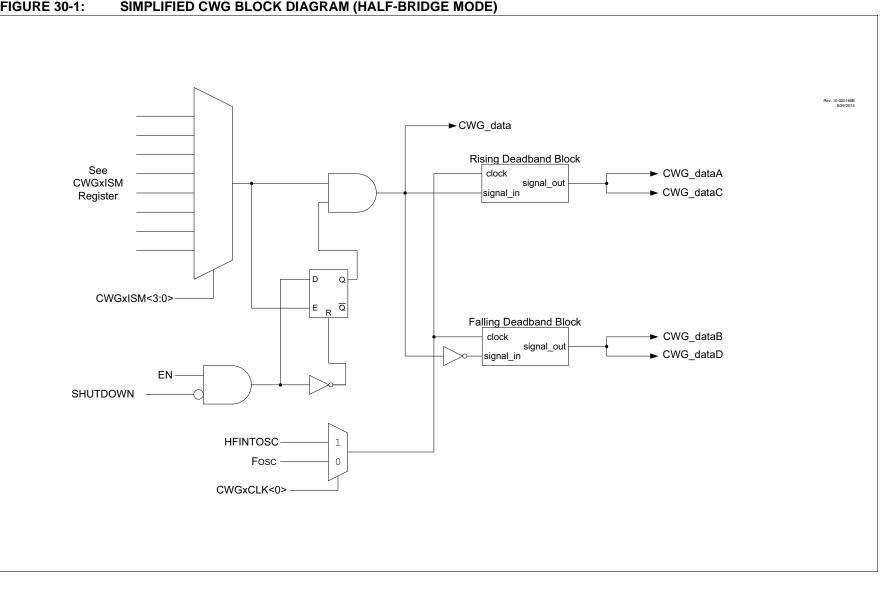

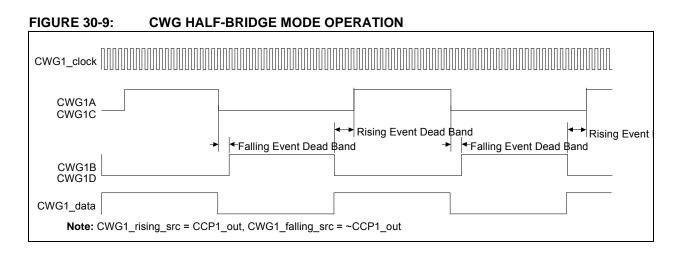

### FIGURE 30-1: SIMPLIFIED CWG BLOCK DIAGRAM (HALF-BRIDGE MODE)

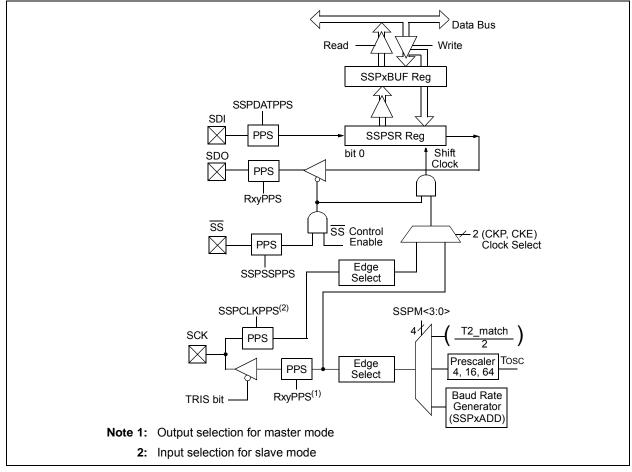

# 32.0 MASTER SYNCHRONOUS SERIAL PORT (MSSPx) MODULES

# 32.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- · Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 32-1 is a block diagram of the SPI interface module.

# 32.8 Register Definitions: MSSPx Control

# REGISTER 32-1: SSPxSTAT: SSPx STATUS REGISTER

| R/W-0/0                                                                                                                                                                                                                                                                                   | R/W-0/0                                                                                                                                            | R/HS/HC-0                                                                                                                | R/HS/HC-0                                                   | R/HS/HC-0                       | R/HS/HC-0                                | R/HS/HC-0           | R/HS/HC-0 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------------------------|---------------------|-----------|

| SMP                                                                                                                                                                                                                                                                                       | CKE <sup>(1)</sup>                                                                                                                                 | D/A                                                                                                                      | P <sup>(2)</sup>                                            | S <sup>(2)</sup>                | R/W                                      | UA                  | BF        |

| bit 7                                                                                                                                                                                                                                                                                     |                                                                                                                                                    |                                                                                                                          |                                                             |                                 | •                                        |                     | bit C     |

|                                                                                                                                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                          |                                                             |                                 |                                          |                     |           |

| Legend:                                                                                                                                                                                                                                                                                   | .,                                                                                                                                                 |                                                                                                                          |                                                             |                                 |                                          |                     |           |

| R = Readable b                                                                                                                                                                                                                                                                            |                                                                                                                                                    | W = Writable bit                                                                                                         |                                                             | •                               | inted bit, read as '0                    |                     |           |

| u = Bit is uncha                                                                                                                                                                                                                                                                          | nged                                                                                                                                               | x = Bit is unknow                                                                                                        |                                                             |                                 | POR and BOR/Val                          | ue at all other Res | ets       |

| '1' = Bit is set                                                                                                                                                                                                                                                                          |                                                                                                                                                    | '0' = Bit is cleare                                                                                                      | d                                                           | HS/HC = Hardv                   | vare set/clear                           |                     |           |

| bit 7                                                                                                                                                                                                                                                                                     | SPI Master mod<br>1 = Input data s<br>0 = Input data s<br><u>SPI Slave mode</u><br>SMP must be c                                                   | ampled at end of o<br>ampled at middle<br><u>e:</u><br>leared when SPI is                                                | of data output tir                                          |                                 |                                          |                     |           |

|                                                                                                                                                                                                                                                                                           | In I <sup>2</sup> C Master of<br>1 = Slew rate of<br>0 = Slew rate of                                                                              | <u>r Slave mode:</u><br>control disabled for<br>control enabled for                                                      | Standard Speed<br>High-Speed mod                            | l mode (100 kHz<br>de (400 kHz) | and 1 MHz)                               |                     |           |

| bit 6                                                                                                                                                                                                                                                                                     | In SPI Master o<br>1 = Transmit oc<br>0 = Transmit oc<br>In I <sup>2</sup> C mode onl<br>1 = Enable inpu                                           | curs on transition                                                                                                       | from active to Idl<br>from Idle to activ<br>sholds are comp | e clock state<br>e clock state  | specification                            |                     |           |

| bit 5                                                                                                                                                                                                                                                                                     | 1 = Indicates th                                                                                                                                   | ess bit (I <sup>2</sup> C mode<br>at the last byte rec<br>at the last byte rec                                           | eived or transmi                                            |                                 |                                          |                     |           |

| bit 4                                                                                                                                                                                                                                                                                     | 1 = Indicates th                                                                                                                                   | This bit is cleared<br>at a Stop bit has b<br>s not detected last                                                        |                                                             |                                 | led, SSPEN is clea<br>Reset)             | red.)               |           |

| bit 3                                                                                                                                                                                                                                                                                     | 1 = Indicates th                                                                                                                                   | This bit is cleared<br>at a Start bit has b<br>s not detected last                                                       |                                                             |                                 | led, SSPEN is clea<br>Reset)             | red.)               |           |

| bit 2                                                                                                                                                                                                                                                                                     | This bit holds th<br>next Start bit, St<br>$In I^2C$ Slave mo<br>1 = Read<br>0 = Write<br>$In I^2C$ Master m<br>1 = Transmit is<br>0 = Transmit is | top bit, or not ACK<br><u>ide:</u><br>s in progress<br>s not in progress                                                 | ion following the bit.                                      |                                 | ch. This bit is only t                   |                     |           |

| OR-ing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in IDLE mode.<br>bit 1 UA: Update Address bit (10-bit I <sup>2</sup> C mode only) 1 = Indicates that the user needs to update the address in the SSPxADD register 0 = Address does not need to be updated |                                                                                                                                                    |                                                                                                                          |                                                             |                                 |                                          |                     |           |

| bit 0                                                                                                                                                                                                                                                                                     | <b>BF:</b> Buffer Full :<br><u>Receive (SPI ar</u><br>1 = Receive cor<br>0 = Receive not<br><u>Transmit (I<sup>2</sup>C m</u><br>1 = Data transm   | Status bit<br>nd I <sup>2</sup> C modes):<br>mplete, SSPxBUF<br>t complete, SSPxE<br>node only):<br>nit in progress (doe | is full<br>UF is empty<br>as not include the                |                                 | its), SSPxBUF is fr<br>s), SSPxBUF is em |                     |           |

|                                                                                                                                                                                                                                                                                           | plarity of clock state                                                                                                                             |                                                                                                                          | bit of the SSPxC                                            | CON register.                   |                                          | P1)                 |           |

2: This bit is cleared on Reset and when SSPEN is cleared.

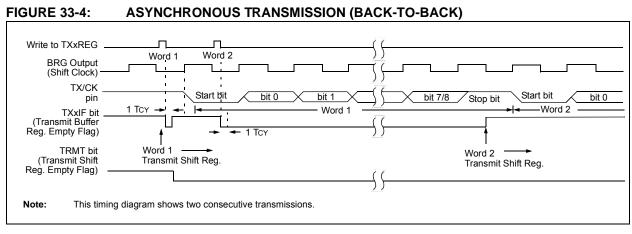

# 33.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 33-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCxREG register.

# 33.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCxSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

# 33.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 33.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RXxIF interrupt flag bit of the PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCxREG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See Section 33.1.2.5 "Receive Overrun Error" for more information on overrun errors.

$\wedge$

# TABLE 37-2: SUPPLY CURRENT (IDD)<sup>(1,2,4)</sup>

| IADLE         | ABLE 37-2: SUPPLY CORRENT (IDD), |                                                  |                                                         |      |       |       |                 |  |  |  |  |

|---------------|----------------------------------|--------------------------------------------------|---------------------------------------------------------|------|-------|-------|-----------------|--|--|--|--|

| PIC16LF       | F15356/75/76                     | /85/86                                           | Standard Operating Conditions (unless otherwise stated) |      |       |       |                 |  |  |  |  |

| PIC16F1       | PIC16F15356/75/76/85/86          |                                                  |                                                         |      |       |       |                 |  |  |  |  |

| Param.<br>No. | Symbol                           | Min.                                             | Тур.†                                                   | Max. | Units | VDD   | Conditions Note |  |  |  |  |

| D100          | IDD <sub>XT4</sub>               | XT = 4 MHz                                       | —                                                       | 360  | 470   | μA    | 3.0V            |  |  |  |  |

| D100          | IDD <sub>XT4</sub>               | XT = 4 MHz                                       | _                                                       | 380  | 480   | μA    | 3.00            |  |  |  |  |

| D101          | IDD <sub>HFO16</sub>             | HFINTOSC = 16 MHz                                | _                                                       | 1.4  | 2.3   | _mA   | 3.0             |  |  |  |  |

| D101          | IDD <sub>HFO16</sub>             | HFINTOSC = 16 MHz                                | —                                                       | 1.5  | 2.3   | > mA  | <b>3</b> .0∨    |  |  |  |  |

| D102          | IDD <sub>HFOPLL</sub>            | HFINTOSC = 32 MHz                                | -                                                       | 2.6  | 3.6   | /mA ` | 3.0V            |  |  |  |  |

| D102          | IDD <sub>HFOPLL</sub>            | HFINTOSC = 32 MHz                                | $\left\{ \right\}$                                      | 2.7  | 3,7   | mA    | 3.0V            |  |  |  |  |

| D103          | IDD <sub>HSPLL32</sub>           | HS+PLL = 32 MHz                                  | _                                                       | 2.6  | 3.6   | ∕mA   | 3.0V            |  |  |  |  |

| D103          | IDD <sub>HSPLL32</sub>           | HS+PLL = 32 MHz                                  | /                                                       | 21   | 3.7   | mA    | 3.0V            |  |  |  |  |

| D104          | IDD <sub>IDLE</sub>              | IDLE mode, HFINTOSC = 16 MHz                     | X                                                       | 1.05 | Z     | mA    | 3.0V            |  |  |  |  |

| D104          | IDD <sub>IDLE</sub>              | IDLE mode, HFINTOSC = 16 MHz                     | $\nearrow$                                              | 1.15 | _     | mA    | 3.0V            |  |  |  |  |

| D105          | IDD <sub>DOZE</sub> (3)          | DOZE mode, HFINTOSC = 16 MHz, Doze<br>Ratio = 16 | -                                                       | 1.1  | _     | mA    | 3.0V            |  |  |  |  |

| D105          | IDD <sub>DOZE</sub> (3)          | DOZE mode, HFINTOSC = 16 MHz, Doze<br>Ratio = 16 | $\bigtriangledown$                                      | 1.2  | —     | mA    | 3.0V            |  |  |  |  |

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins are outputs driven low, MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3:  $IDD_{DOZE} = [IDD_{IDLE} / (N 1)/N] + IDD_{HFO} 16/N$  where N = DOZE Ratio (Register 11-2).

- 4: PMD bits are all in the default state, no modules are disabled.

- 5: = F device

# TABLE 37-14: COMPARATOR SPECIFICATIONS

|               | Standard Operating Conditions (unless otherwise stated)<br>/DD = 3.0V, TA = 25°C |                                   |      |      |       |          |                           |  |  |

|---------------|----------------------------------------------------------------------------------|-----------------------------------|------|------|-------|----------|---------------------------|--|--|

| Param.<br>No. | Sym.                                                                             | Characteristics                   | Min. | Тур. | Max.  | Units    | Comments                  |  |  |

| CM01          | VIOFF                                                                            | Input Offset Voltage              | _    | —    | ±30   | mV       | VICM = VDD/2              |  |  |

| CM02          | VICM                                                                             | Input Common Mode Range           | GND  | _    | Vdd   | V        |                           |  |  |

| CM03          | CMRR                                                                             | Common Mode Input Rejection Ratio | _    | 50   | _     | dB <     |                           |  |  |

| CM04          | VHYST                                                                            | Comparator Hysteresis             | 15   | 25   | 35    | mV       | $\langle \langle \rangle$ |  |  |

| CM05          | TRESP <sup>(1)</sup>                                                             | Response Time, Rising Edge        | _    | 300  | 600 / | <u>ب</u> | $\langle \rangle$         |  |  |

|               |                                                                                  | Response Time, Falling Edge       | _    | 220  | 500   | L'US     | × ×                       |  |  |

| CMOS6         | TMCV2VO <sup>(2)</sup>                                                           | Mode Change to Valid Output       |      |      | 10    | AIS /    | $\sim$                    |  |  |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

2: A mode change includes changing any of the control register values, including module enable.

# TABLE 37-15: 5-BIT DAC SPECIFICATIONS

|               | Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |                              |                     |                        |       |       |          |  |  |  |

|---------------|----------------------------------------------------------------------------------|------------------------------|---------------------|------------------------|-------|-------|----------|--|--|--|

| Param.<br>No. | Sym.                                                                             | Characteristics              | Min.                | Тур.                   | Max.  | Units | Comments |  |  |  |

| DSB01         | VLSB                                                                             | Step Size                    |                     | (VDACREF+ VDACREF-)/32 | —     | V     |          |  |  |  |

| DSB01         | VACC                                                                             | Absolute Accuracy            | $ \ge $             | $\searrow$             | ± 0.5 | LSb   |          |  |  |  |

| DSB03*        | RUNIT                                                                            | Unit Resistor Value          | $\langle - \rangle$ | 5000                   | _     | Ω     |          |  |  |  |

| DSB04*        | TST                                                                              | Settling Time <sup>(1)</sup> | $\langle -\rangle$  | · · · ·                | 10    | μS    |          |  |  |  |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Settling time measured while DACR<4:0> transitions from '00000' to '01111'.

# TABLE 37-16: FIXED VOLTAGE REFERENCE (FVR) SPECIFICATIONS

| Standard      | Standard Operating Conditions (unless otherwise stated) |                                                     |      |      |      |       |                                                                                                                                                  |  |  |

|---------------|---------------------------------------------------------|-----------------------------------------------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol                                                  | Characteristic                                      | Min. | Тур. | Max. | Units | Conditions                                                                                                                                       |  |  |

| FVR01         | VEVR1                                                   | 1x Gain (1.024V)                                    | -4   | _    | +4   | %     | $\begin{array}{l} V\text{DD} \geq 2.5\text{V}, \ \text{-40}^{\circ}\text{C} \ \text{to} \\ 85^{\circ}\text{C} \end{array}$                       |  |  |

| FVR02         | VFVR2                                                   | 2x Gain (2.048V)                                    | -4   | —    | +4   | %     | $\label{eq:VDD} \begin{array}{l} V\text{DD} \geq 2.5 \text{V} \text{, } \text{-}40^{\circ}\text{C} \text{ to} \\ 85^{\circ}\text{C} \end{array}$ |  |  |

| FVR03         | XFVR4                                                   | 4x Gain (4.096V)                                    | -5   | —    | +5   | %     | $VDD \ge 4.75V, -40^{\circ}C$ to $85^{\circ}C$                                                                                                   |  |  |

| FVR04         | TFVRST                                                  | FVR Start-up Time                                   | -    | 25   | _    | us    |                                                                                                                                                  |  |  |

| FVR05         | FVRA1x/FVRC1x                                           | FVR output voltage for 1x setting stored in the DIA | —    | 1024 | —    | mV    |                                                                                                                                                  |  |  |

| FVR06         | FVRA2x/FVRC2x                                           | FVR output voltage for 2x setting stored in the DIA | —    | 2048 | —    | mV    |                                                                                                                                                  |  |  |

| FVR07         | FVRA4x/FVRC4x                                           | FVR output voltage for 4x setting stored in the DIA | —    | 4096 | _    | mV    |                                                                                                                                                  |  |  |

© 2016 Microchip Technology Inc.

# TABLE 37-23: SPI MODE REQUIREMENTS

| Standard      | andard Operating Conditions (unless otherwise stated) |                                          |                                |      |                |             |                                |  |  |

|---------------|-------------------------------------------------------|------------------------------------------|--------------------------------|------|----------------|-------------|--------------------------------|--|--|

| Param.<br>No. | Symbol                                                | Characteristic                           | Min.                           | Тур† | Max.           | Units       | Conditions                     |  |  |

| SP70*         | TssL2scH,<br>TssL2scL                                 | SS↓ to SCK↓ or SCK↑ input                | 2.25*Tcy                       | —    | —              | ns          | $\square$                      |  |  |

| SP71*         | TscH                                                  | SCK input high time (Slave mode)         | Tcy + 20                       | —    | —              | ng          |                                |  |  |

| SP72*         | TscL                                                  | SCK input low time (Slave mode)          | Tcy + 20                       | —    | _              | ns          |                                |  |  |

| SP73*         | TDIV2scH,<br>TDIV2scL                                 | Setup time of SDI data input to SCK edge | 100                            | - /  |                | ns          |                                |  |  |

| SP74*         | TscH2DIL,<br>TscL2DIL                                 | Hold time of SDI data input to SCK edge  | 100                            | -<   |                | - <b>RS</b> | >                              |  |  |

| SP75*         | TDOR                                                  | SDO data output rise time                | _                              | 10   | 25             | ns          | $3.0V \le VDD \le 5.5V$        |  |  |

|               |                                                       |                                          | - <                            | 25   | \ <b>5</b> 0 < | ns          | $1.8V \le V\text{DD} \le 5.5V$ |  |  |

| SP76*         | TDOF                                                  | SDO data output fall time                | _                              | 10   | 25             | ns          |                                |  |  |

| SP77*         | TssH2doZ                                              | SS↑ to SDO output high-impedance         | 10                             |      | 50             | ns          |                                |  |  |

| SP78*         | TscR                                                  | SCK output rise time                     | $\gamma \neq L$                | -10  | 25             | ns          | $3.0V \le V\text{DD} \le 5.5V$ |  |  |

|               |                                                       | (Master mode)                            | $\overline{\langle - \rangle}$ | 25   | 50             | ns          | $1.8V \le V\text{DD} \le 5.5V$ |  |  |

| SP79*         | TscF                                                  | SCK output fall time (Master mode)       | \_\<br>_                       | 10   | 25             | ns          |                                |  |  |

| SP80*         | TscH2doV,                                             | SDO data output valid after SCK edge     |                                | _    | 50             | ns          | $3.0V \le V\text{DD} \le 5.5V$ |  |  |

|               | TscL2DoV                                              |                                          | $\sim - \sim$                  | 1 —  | 145            | ns          | $1.8V \le V\text{DD} \le 5.5V$ |  |  |

| SP81*         | TDOV2SCH,<br>TDOV2SCL                                 | SDO data output setup to SCK edge        |                                | —    | —              | ns          |                                |  |  |

| SP82*         | TssL2DoV                                              | SDO data output valid after SS↓ edge     | $\searrow$ -                   | _    | 50             | ns          |                                |  |  |

| SP83*         | TscH2ssH,<br>TscL2ssH                                 | SS ↑ after SCK edge                      | 1.5 TCY + 40                   | —    | —              | ns          |                                |  |  |

These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 37-25: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No. | Symbol  | Characte                     | eristic      | Min.       | Max. | Units | Conditions                                  |

|---------------|---------|------------------------------|--------------|------------|------|-------|---------------------------------------------|

| SP100*        | Тнідн   | Clock high time              | 100 kHz mode | 4.0        | -    | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                              | 400 kHz mode | 0.6        |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                              | SSP module   | 1.5Tcy     | _    |       |                                             |

| SP101*        | TLOW    | Clock low time               | 100 kHz mode | 4.7        | -    | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                              | 400 kHz mode | 1.3        |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                              | SSP module   | 1.5Tcy     | _    |       |                                             |

| SP102*        | Tr      | SDA and SCL rise time        | 100 kHz mode | —          | 1000 | ns    |                                             |

|               |         |                              | 400 kHz mode | 20 + 0.1CB | 300  | ns    | CB is specified to be from 10-400 pF        |

| SP103*        | TF      | SDA and SCL fall time        | 100 kHz mode | —          | 250  | ns    |                                             |

|               |         |                              | 400 kHz mode | 20 + 0.1CB | 250  | ns    | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT | D:DAT Data input hold time   | 100 kHz mode | 0          | _    | ns    |                                             |

|               |         |                              | 400 kHz mode | 0          | 0.9  | μs    |                                             |

| SP107*        | TSU:DAT | SU:DAT Data input setup time | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |

|               |         |                              | 400 kHz mode | 100        | —    | ns    |                                             |

| SP109*        | ΤΑΑ     | Output valid from            | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|               |         | clock                        | 400 kHz mode | —          | _    | ns    |                                             |

| SP110*        | TBUF    | UF Bus free time             | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                   |

|               |         |                              | 400 kHz mode | 1.3        | _    | μS    | before a new transmissior<br>can start      |

| SP111         | Св      | Bus capacitive loading       |              | _          | 400  | pF    |                                             |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

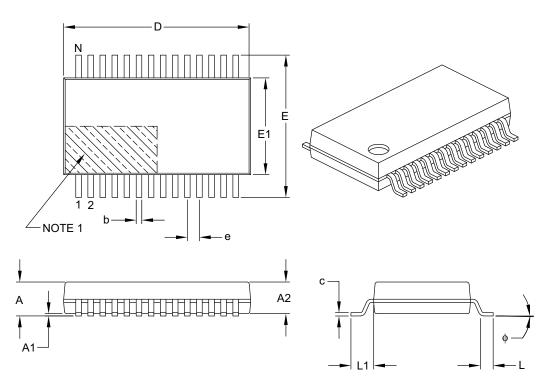

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS |       |  |  |  |

|--------------------------|------------------|----------|-------------|-------|--|--|--|

|                          | Dimension Limits | MIN      | NOM         | MAX   |  |  |  |

| Number of Pins           | N                | 28       |             |       |  |  |  |

| Pitch                    | е                |          | 0.65 BSC    |       |  |  |  |

| Overall Height           | А                | _        | -           | 2.00  |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85  |  |  |  |

| Standoff                 | A1               | 0.05     | -           | -     |  |  |  |

| Overall Width            | E                | 7.40     | 7.80        | 8.20  |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60  |  |  |  |

| Overall Length           | D                | 9.90     | 10.20       | 10.50 |  |  |  |

| Foot Length              | L                | 0.55     | 0.75        | 0.95  |  |  |  |

| Footprint                | L1               | 1.25 REF |             |       |  |  |  |

| Lead Thickness           | С                | 0.09     | -           | 0.25  |  |  |  |

| Foot Angle               | φ                | 0°       | 4°          | 8°    |  |  |  |

| Lead Width               | b                | 0.22     | -           | 0.38  |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

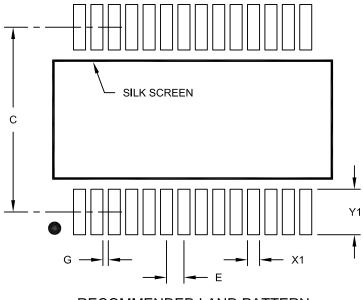

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Units            |          |      | S    |  |

|--------------------------|------------------|----------|------|------|--|

| Dimensio                 | Dimension Limits |          |      | MAX  |  |

| Contact Pitch            | E                | 0.65 BSC |      |      |  |

| Contact Pad Spacing      | С                |          | 7.20 |      |  |

| Contact Pad Width (X28)  | X1               |          |      | 0.45 |  |

| Contact Pad Length (X28) | Y1               |          |      | 1.75 |  |

| Distance Between Pads    | G                | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A