#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                          |

| Number of I/O              | 56                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                             |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g30f128g-e-qfn64r |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• Data retention of the entire memory in EM0 to EM3

# **5.6 Device Information (DI) Page**

The DI page contains calibration values, a unique identification number and other useful data. See the table below for a complete overview.

Table 5.4. Device Information Page Contents

| DI Address | Register              | Description                                                                                                                                              |

|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0FE08020 | CMU_LFRCOCTRL         | Register reset value.                                                                                                                                    |

| 0x0FE08028 | CMU_HFRCOCTRL         | Register reset value.                                                                                                                                    |

| 0x0FE08030 | CMU_AUXHFRCOCTRL      | Register reset value.                                                                                                                                    |

| 0x0FE08040 | ADC0_CAL              | Register reset value.                                                                                                                                    |

| 0x0FE08048 | ADC0_BIASPROG         | Register reset value.                                                                                                                                    |

| 0x0FE08050 | DAC0_CAL              | Register reset value.                                                                                                                                    |

| 0x0FE08058 | DAC0_BIASPROG         | Register reset value.                                                                                                                                    |

| 0x0FE08060 | ACMP0_CTRL            | Register reset value.                                                                                                                                    |

| 0x0FE08068 | ACMP1_CTRL            | Register reset value.                                                                                                                                    |

| 0x0FE08078 | CMU_LCDCTRL           | Register reset value.                                                                                                                                    |

| 0x0FE081B0 | DI_CRC                | [15:0]: DI data CRC-16.                                                                                                                                  |

| 0x0FE081B2 | CAL_TEMP_0            | [7:0] Calibration temperature (°C).                                                                                                                      |

| 0x0FE081B4 | ADC0_CAL_1V25         | [14:8]: Gain for 1V25 reference, [6:0]: Offset for 1V25 reference.                                                                                       |

| 0x0FE081B6 | ADC0_CAL_2V5          | [14:8]: Gain for 2V5 reference, [6:0]: Offset for 2V5 reference.                                                                                         |

| 0x0FE081B8 | ADC0_CAL_VDD          | [14:8]: Gain for VDD reference, [6:0]: Offset for VDD reference.                                                                                         |

| 0x0FE081BA | ADC0_CAL_5VDIFF       | [14:8]: Gain for 5VDIFF reference, [6:0]: Offset for 5VDIFF reference.                                                                                   |

| 0x0FE081BC | ADC0_CAL_2XVDD        | [14:8]: Reserved (gain for this reference cannot be calibrated), [6:0]: Offset for 2XVDD reference.                                                      |

| 0x0FE081BE | ADC0_TEMP_0_READ_1V25 | [15:4] Temperature reading at 1V25 reference, [3:0] Reserved.                                                                                            |

| 0x0FE081C8 | DAC0_CAL_1V25         | [22:16]: Gain for 1V25 reference, [13:8]: Channel 1 offset for 1V25 reference, [5:0]: Channel 0 offset for 1V25 reference.                               |

| 0x0FE081CC | DAC0_CAL_2V5          | [22:16]: Gain for 2V5 reference, [13:8]: Channel 1 offset for 2V5 reference, [5:0]: Channel 0 offset for 2V5 reference.                                  |

| 0x0FE081D0 | DAC0_CAL_VDD          | [22:16]: Reserved (gain for this reference cannot be calibrated), [13:8]: Channel 1 offset for VDD reference, [5:0]: Channel 0 offset for VDD reference. |

| 0x0FE081D4 | RESERVED              | [31:0] Reserved                                                                                                                                          |

| 0x0FE081D8 | RESERVED              | [31:0] Reserved                                                                                                                                          |

| 0x0FE081DC | HFRCO_CALIB_BAND_1    | [7:0]: Tuning for the 1.2 MHZ HFRCO band.                                                                                                                |

| 0x0FE081DD | HFRCO_CALIB_BAND_7    | [7:0]: Tuning for the 6.6 MHZ HFRCO band.                                                                                                                |

| 0x0FE081DE | HFRCO_CALIB_BAND_11   | [7:0]: Tuning for the 11 MHZ HFRCO band.                                                                                                                 |

## **EFM<sup>®</sup>32**

| Bit     | Field         | Value          | Description                                                                                                  |

|---------|---------------|----------------|--------------------------------------------------------------------------------------------------------------|

| [20:18] | src_prot_ctrl | -              | Configures the state of HPROT when the controller reads the source data                                      |

| [13:4]  | n_minus_1     | N <sup>1</sup> | Configures the controller to perform N DMA transfers, where N is a multiple of four                          |

| [3]     | next_useburst | -              | When set to 1, the controller sets the chnl_useburst_set [C] bit to 1 after the alternate transfer completes |

<sup>1</sup>Because the R\_power field is set to four, you must set N to be a multiple of four. The value given by N/4 is the number of times that you must configure the alternate data structure.

See Section 8.4.3.3 (p. 56) for more information.

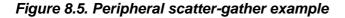

Figure 8.5 (p. 52) shows a peripheral scatter-gather example.

Initialization:1. Configure primary to enable the copy A, B, C, and D operations: cycle\_ctrl = b110, 2<sup>R</sup> = 4, N = 16. 2. Write the primary source data in memory, using the structure shown in the following table.

| 2. Write the p  | 2. Write the primary source data in memory, daing the structure shown in the following table. |                  |                                              |            |  |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------|------------------|----------------------------------------------|------------|--|--|--|--|--|--|--|

|                 | src_data_end_ptr                                                                              | dst_data_end_ptr | channel_cfg                                  | Unused     |  |  |  |  |  |  |  |

| Data for Task A | 0x0A00000                                                                                     | 0x0AE00000       | cycle_ctrl = b111, 2 <sup>R</sup> = 4, N = 3 | 0xXXXXXXXX |  |  |  |  |  |  |  |

| Data for Task B | 0x0B000000                                                                                    | 0x0BE00000       | cycle_ctrl = b111, 2 <sup>R</sup> = 2, N = 8 | 0xXXXXXXXX |  |  |  |  |  |  |  |

| Data for Task C | 0x0C000000                                                                                    | 0x0CE00000       | cycle_ctrl = b111, 2 <sup>R</sup> = 8, N = 5 | 0xXXXXXXXX |  |  |  |  |  |  |  |

| Data for Task D | 0x0D000000                                                                                    | 0x0DE00000       | $cycle_ctrl = b001, 2^{R} = 4, N = 4$        | 0xXXXXXXXX |  |  |  |  |  |  |  |

In Figure 8.5 (p. 52) :

Initialization

- 1. The host processor configures the primary data structure to operate in peripheral scatter-gather mode by setting cycle\_ctrl to b110. Because a data structure for a single channel consists of four words then you must set 2<sup>R</sup> to 4. In this example, there are four tasks and therefore N is set to 16.

- 2. The host processor writes the data structure for tasks A, B, C, and D to the memory locations that the primary src\_data\_end\_ptr specifies.

- 3. The host processor enables the channel.

The peripheral scatter-gather transaction commences when the controller receives a request on  $dma\_req[$ ]. The transaction continues as follows:

Table 8.11 (p. 60) lists the destination addresses for a DMA transfer of 12 bytes using a halfword increment.

| Table 8.11. DN | IA cycle of 1 | 2 bytes using a | halfword increment |

|----------------|---------------|-----------------|--------------------|

|----------------|---------------|-----------------|--------------------|

| h = h01 n minus 1 -             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                         |           |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------|

| = 501, 11_111103_1 -            | = b1011, cy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | cle_ctrl = 1, R_po                                      | wer = b11 |

| End Pointer                     | Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Difference <sup>1</sup>                                 | Address   |

| 0x5E7                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x16                                                    | 0x5D1     |

| 0x5E7                           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x14                                                    | 0x5D3     |

| 0x5E7                           | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x12                                                    | 0x5D5     |

| 0x5E7                           | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x10                                                    | 0x5D7     |

| 0x5E7                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0xE                                                     | 0x5D9     |

| 0x5E7                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0xC                                                     | 0x5DB     |

| 0x5E7                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0xA                                                     | 0x5DD     |

| 0x5E7                           | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x8                                                     | 0x5DF     |

| after 2 <sup>R</sup> DMA transf | ers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         |           |

| = b01, n_minus_1 =              | = b011, cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e_ctrl = 1, R_pov                                       | ver = b11 |

| End Pointer                     | Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Difference                                              | Address   |

| 0x5E7                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x6                                                     | 0x5E1     |

| 0x5E7                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x4                                                     | 0x5E3     |

| 0x5E7                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x2                                                     | 0x5E5     |

| 0x5E7                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x0                                                     | 0x5E7     |

|                                 | $     \begin{array}{r}       0x5E7 \\       after 2R DMA transfer        2R DMA transfer      $ | $     \begin{array}{c cccccccccccccccccccccccccccccccc$ |           |

src\_size = b00, dst\_inc = b01, n\_minus\_1 = 0, cycle\_ctrl = 0<sup>2</sup>, R\_power = b11

<sup>1</sup>This value is the result of count being shifted left by the value of dst\_inc.

<sup>2</sup>After the controller completes the DMA cycle it invalidates the channel\_cfg memory location by clearing the cycle\_ctrl field.

## 8.4.4 Interaction with the EMU

The DMA interacts with the Energy Management Unit (EMU) to allow transfers from , e.g., the LEUART to occur in EM2. The EMU can wake up the DMA sufficiently long to allow data transfers to occur. See section "DMA Support" in the LEUART documentation.

### 8.4.5 Interrupts

The PL230 dma\_done[n:0] signals (one for each channel) as well as the dma\_err signal, are available as interrupts to the Cortex-M3 core. They are combined into one interrupt vector, DMA\_INT. If the interrupt for the DMA is enabled in the ARM Cortex-M3 core, an interrupt will be made if one or more of the interrupt flags in DMA\_IF and their corresponding bits in DMA\_IEN are set.

## 8.5 Examples

A basic example of how to program the DMA for transferring 42 bytes from the USART1 to memory location 0x20003420. Assumes that the channel 0 is currently disabled, and that the DMA\_ALTCTRLBASE register has already been configured.

### Example 8.1. DMA Transfer

- 1. Configure the channel select for using USART1 with DMA channel 0 a. Write SOURCESEL=0b001101 and SIGSEL=XX to DMA CHCTRL0

- 2. Configure the primary channel descriptor for DMA channel 0

- a. Write XX (read address of USART1) to src\_data\_end\_ptr

- b. Write 0x20003420 + 40 to dst\_data\_end\_ptr c

- c. Write these values to channel\_cfg for channel 0:

- i. dst\_inc=b01 (destination halfword address increment)

- ii. dst\_size=b01 (halfword transfer size)

- iii. src\_inc=b11 (no address increment for source)

- iv. src\_size=01 (halfword transfer size)

- v. dst\_prot\_ctrl=000 (no cache/buffer/privilege)

- vi.src\_prot\_ctrl=000 (no cache/buffer/privilege)

- vii.R\_power=b0000 (arbitrate after each DMA transfer)

- viiin\_minus\_1=d20 (transfer 21 halfwords)

- ix.next\_useburst=b0 (not applicable)

- x. cycle\_ctrl=b001 (basic operating mode)

- 3. Enable the DMA

- a. Write EN=1 to DMA\_CONFIG

- 4. Disable the single requests for channel 0 (i.e., do not react to data available, wait for buffer full) a. Write DMA\_CHUSEBURSTS[0]=1

- 5. Enable buffer-full requests for channel 0 a. Write DMA\_CHREQMASKC[0]=1

- 6. Use the primary data structure for channel 0

- a. Write DMA\_CHALTC[0]=1

- 7. Enable channel 0

- a. Write DMA\_CHENS[0]=1

# 8.7 Register Description

# 8.7.1 DMA\_STATUS - DMA Status Registers

| Offset |                                                                                                                             |      | _    |      |              |     |       |      |       |       |        |       |        |        |        | it Po  | 1       | 1      |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

|--------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------|-----|-------|------|-------|-------|--------|-------|--------|--------|--------|--------|---------|--------|--------|-------|-------|------|-------|-----|------|-------|--------|-------|------|--------|--------|------|

| 0x000  | 33                                                                                                                          | 30   | 29   | 28   | 27           | 26  | 25    | 24   | 23    | 22    | 21     | 20    | 19     | 18     | 17     | 16     | 15      | 4      | 13     | 12    | 7     | 10   | റ     | 8   | ~    | - 4   | 2<br>C | 4     | ო    | 7      | -      | (    |

| Reset  |                                                                                                                             |      |      |      |              |     |       |      |       |       |        |       |        | 0×07   |        |        |         |        |        |       |       |      |       |     |      |       | 0x0    |       |      |        |        |      |

| Access |                                                                                                                             |      |      |      |              |     |       |      |       |       |        |       |        | 2      |        |        |         |        |        |       |       |      |       |     |      |       | R      | _     |      |        |        | 6    |

|        |                                                                                                                             |      |      |      |              |     |       |      |       |       |        |       |        |        |        |        |         |        |        |       |       |      |       |     |      |       |        | _     |      |        |        | -    |

| Name   |                                                                                                                             |      |      |      |              |     |       |      |       |       |        |       |        | CHNUM  |        |        |         |        |        |       |       |      |       |     |      |       | STATE  |       |      |        |        | i    |

| Bit    | Nar                                                                                                                         | ne   |      |      |              |     |       | Re   | eset  |       |        | A     | ١cc    | ess    | ;      | De     | scr     | iptio  | on     |       |       |      |       |     |      |       |        |       |      |        |        |      |

| 31:21  | Res                                                                                                                         | erve | d    |      |              |     |       | Тс   | ens   | ure d | comp   | atib  | ility  | with   | n futu | ire d  | evice   | es, a  | lway   | ys n  | rite  | bits | to 0. | Мог | e ir | nfori | natio  | on in | Sect | tion 2 | 2.1 (j | р.   |

| 20:16  | CHN                                                                                                                         | IUM  |      |      |              |     |       | 0x(  | 07    |       |        | R     | 2      |        |        | Ch     | anne    | el Nu  | umb    | ber   |       |      |       |     |      |       |        |       |      |        |        |      |

|        | Number of available DMA channels minus one.                                                                                 |      |      |      |              |     |       |      |       |       |        |       |        |        |        |        |         |        |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

| 15:8   | Res                                                                                                                         | erve | d    |      |              |     |       | Тс   | ens   | ure ( | comp   | atib  | oility | with   | n futu | ire d  | evice   | es, a  | lwaj   | ys n  | rite  | bits | to 0. | Мог | e ir | nfori | natio  | on in | Sect | tion 2 | 2.1 (J | р.   |

| 7:4    | STATE     0x0     R     Control Current State       State can be one of the following. Higher values (11-15) are undefined. |      |      |      |              |     |       |      |       |       |        |       |        |        |        |        |         |        |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

|        | State                                                                                                                       | e ca | n be | e on | e of         | the | follo | owin | g. Hi | ghei  | · valu | ies ( | (11-   | 15)    | are    | unde   | fined   | d.     |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

|        | Value Mode                                                                                                                  |      |      |      |              |     |       |      |       |       |        | [     | Descr  | iptior | 1      |        |         |        |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

|        | 0                                                                                                                           |      |      |      | 10           | DLE |       |      |       |       |        |       |        | 1      | dle    |        |         |        |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

|        | 1                                                                                                                           |      |      |      | R            | DCH | НСТ   | RLD  | ATA   |       |        |       |        | F      | Readi  | ing cł | nanne   | el cor | ntroll | er da | ata   |      |       |     |      |       |        |       |      |        |        |      |

|        | 2                                                                                                                           |      |      |      | R            | DSF | RCE   | NDP  | TR    |       |        |       |        | F      | Readi  | ing so | ource   | data   | end    | l poi | nter  |      |       |     |      |       |        |       |      |        |        |      |

|        | 3                                                                                                                           |      |      |      | R            | DDS | STEI  | NDP  | TR    |       |        |       |        | F      | Readi  | ing de | estina  | tion   | data   | end   | poir  | nter |       |     |      |       |        |       |      |        |        |      |

|        | 4                                                                                                                           |      |      |      | R            | DSF | RCD   | ATA  |       |       |        |       |        | F      | Readi  | ing so | ource   | data   | I      |       |       |      |       |     |      |       |        |       |      |        |        |      |

|        | 5                                                                                                                           |      |      |      | V            | RD  | STD   | ATA  |       |       |        |       |        | ١      | Vritin | g des  | stinati | on d   | ata    |       |       |      |       |     |      |       |        |       |      |        |        |      |

|        | 6                                                                                                                           |      |      |      | V            | AIT | REC   |      | 2     |       |        |       |        | ١      | Vaitir | ng for | DMA     | req    | uest   | to c  | ear   |      |       |     |      |       |        |       |      |        |        |      |

|        | 7                                                                                                                           |      |      |      | v            | /RC | нст   | RLD  | ATA   |       |        |       |        | ١      | Vritin | g cha  | nnel    | cont   | rolle  | r dat | а     |      |       |     |      |       |        |       |      |        |        |      |

|        | 8                                                                                                                           |      |      |      | S            | TAL | LED   | )    |       |       |        |       |        | 5      | Stalle | d      |         |        |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

|        | 9                                                                                                                           |      |      |      | D            | ON  | E     |      |       |       |        |       |        | [      | Done   |        |         |        |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

|        | 10                                                                                                                          |      |      |      | PERSCATTRANS |     |       |      |       |       |        |       |        | F      | Periph | neral  | scatt   | er-ga  | ther   | tran  | sitio | n    |       |     |      |       |        |       |      |        |        |      |

| 3:1    | Res                                                                                                                         | erve | d    |      |              |     |       | Тс   | ens   | ure d | comp   | atib  | oility | with   | n futu | ire d  | evice   | es, a  | lway   | ys n  | rite  | bits | to 0. | Мог | e ir | nfori | natio  | on in | Sect | tion 2 | 2.1 (p | p. : |

| 0      | EN                                                                                                                          |      |      |      |              |     |       | 0    |       |       |        | R     | 1      |        |        | DN     | AE      | nabl   | le S   | tatu  | s     |      |       |     |      |       |        |       |      |        |        |      |

|        |                                                                                                                             |      |      |      |              |     |       |      |       |       |        |       |        |        |        |        |         |        |        |       |       |      |       |     |      |       |        |       |      |        |        |      |

## 8.7.2 DWA\_CONFIG - DWA CONTIGURATION REGISTER

| Offset |                                                           |                      | В                                                                                                        | it Position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |    |  |  |  |  |  |  |

|--------|-----------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----|--|--|--|--|--|--|

| 0x004  | 31 33 33 30 33 30 228 228 228 226 226 226 226 226 226 226 | 24<br>23<br>21<br>21 | 20<br>19<br>17                                                                                           | 16         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 | Ω 4 m 0 <del>c</del> | 0  |  |  |  |  |  |  |

| Reset  |                                                           |                      |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                    | 0  |  |  |  |  |  |  |

| Access |                                                           |                      |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | >                    | ≥  |  |  |  |  |  |  |

| Name   |                                                           |                      |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CHPROT               | EN |  |  |  |  |  |  |

| Bit    | Name                                                      | Reset                | Access                                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |    |  |  |  |  |  |  |

| 31:6   | Reserved                                                  | To ensure comp       | To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |    |  |  |  |  |  |  |

| 5      | CHPROT                                                    | 0                    | W                                                                                                        | Channel Protection Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |    |  |  |  |  |  |  |

| Bit | Name            | Reset                 | Access | Description          |                                                              |

|-----|-----------------|-----------------------|--------|----------------------|--------------------------------------------------------------|

| 3:2 | LFB             | 0x1                   | RW     | Clock Select for LFE | 3                                                            |

|     | Selects the clo | ck source for LFBCLK. |        |                      |                                                              |

|     | LFB             | LFBE                  |        | Mode                 | Description                                                  |

|     | 0               | 0                     |        | Disabled             | LFBCLK is disabled                                           |

|     | 1               | 0                     |        | LFRCO                | LFRCO selected as LFBCLK                                     |

|     | 2               | 0                     |        | LFXO                 | LFXO selected as LFBCLK                                      |

|     | 3               | 0                     |        | HFCORECLKLEDIV2      | HFCORECLK <sub>LE</sub> divided by two is selected as LFBCLK |

|     | 0               | 1                     |        | ULFRCO               | ULFRCO selected as LFBCLK                                    |

1:0

LFA

0x1

RW

Clock Select for LFA

Selects the clock source for LFACLK.

| LFA | LFAE | Mode            | Description                                           |

|-----|------|-----------------|-------------------------------------------------------|

| 0   | 0    | Disabled        | LFACLK is disabled                                    |

| 1   | 0    | LFRCO           | LFRCO selected as LFACLK                              |

| 2   | 0    | LFXO            | LFXO selected as LFACLK                               |

| 3   | 0    | HFCORECLKLEDIV2 | $HFCORECLK_LE$ divided by two is selected as $LFACLK$ |

| 0   | 1    | ULFRCO          | ULFRCO selected as LFACLK                             |

# 11.5.12 CMU\_STATUS - Status Register

| Offset |    | Bit Position |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |        |         |          |         |          |         |         |          |          |             |             |         |         |          |          |

|--------|----|--------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|---------|----------|---------|----------|---------|---------|----------|----------|-------------|-------------|---------|---------|----------|----------|

| 0x02C  | 31 | 30           | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14     | 13      | 12       | 1       | 10       | ი       | 8       | 7        | 9        | 5           | 4           | e       | 2       | -        | 0        |