Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 8KB (8K × 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 640 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Data Converters            | A/D 5x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-UFQFN                                                               |

| Supplier Device Package    | 20-UFQFPN (3x3)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s903f3u6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         | Table 5. 1350F20/3020/0FQFFN20 pill descriptions (continued) |                                      |      |          |       |      |                          |       |      |    |                                |                                                                         |                                                            |  |

|---------|--------------------------------------------------------------|--------------------------------------|------|----------|-------|------|--------------------------|-------|------|----|--------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------|--|

|         | 0                                                            | 0                                    |      |          | Input | t    |                          | Ou    | tput |    | ç o                            | nate                                                                    | ~ 운포                                                       |  |

| TSSOP20 | <b>UFQFPN20</b>                                              | Pin name                             | Type | floating | ndw   | Ext. | High sink <sup>(1)</sup> | Speed | ao   | dd | Main function<br>(after reset) | Default alternate<br>function                                           | Alternate<br>function<br>after remap<br>[option bit]       |  |

| 19      | 16                                                           | PD2/AIN3/<br>[TIM5_CH3]              | I/O  | x        | х     | х    | HS                       | O3    | х    | х  | Port<br>D2                     | -                                                                       | Analog input 3<br>[AFR2] Timer<br>52 - channel 3<br>[AFR1] |  |

| 20      | 17                                                           | PD3/ AIN4/<br>TIM5_CH2/<br>ADC_ETR   | I/O  | x        | x     | x    | HS                       | O3    | x    | x  | Port<br>D3                     | Analog input<br>4 Timer 52 -<br>channel<br>2/ADC<br>external<br>trigger | -                                                          |  |

| 1       | 18                                                           | PD4/ TIM5_CH1/<br>BEEP<br>[UART1_CK] | I/O  | x        | х     | х    | HS                       | O3    | х    | х  | Port<br>D4                     | Timer 5 -<br>channel<br>1/BEEP<br>output                                | UART clock<br>[AFR2]                                       |  |

| 2       | 19                                                           | PD5/ AIN5/<br>UART1_TX               | I/O  | x        | х     | х    | HS                       | O3    | х    | х  | Port<br>D5                     | Analog input<br>5/ UART1<br>data transmit                               | -                                                          |  |

| 3       | 20                                                           | PD6/ AIN6/<br>UART1_RX               | I/O  | x        | х     | х    | HS                       | O3    | х    | х  | Port<br>D6                     | Analog input<br>6/ UART1<br>data receive                                | -                                                          |  |

| Table 5. 1350F20/3020/0FQFFN20 pill descriptions (continued) | Table 5 | . TSSOP20/SO20/UFQFPN20 | pin descri | ptions | (continued) |

|--------------------------------------------------------------|---------|-------------------------|------------|--------|-------------|

|--------------------------------------------------------------|---------|-------------------------|------------|--------|-------------|

1. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package. In addition, the total driven current must respect the absolute maximum ratings (see *Section 10.2: Absolute maximum ratings*).

2. When the MCU is in Halt/Active-halt mode, PA1 is automatically configured in input weak pull-up and cannot be used for waking up the device. In this mode, the output state of PA1 is not driven. It is recommended to use PA1 only in input mode if Halt/Active-halt is used in the application.

3. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to VDD are not implemented)

4. The PD1 pin is in input pull-up during the reset phase and after internal reset release.

|        | 32           |                        |      |          | Input | t              |                          | Out   | put |    | E                              | ate                                      | ion                                               |  |

|--------|--------------|------------------------|------|----------|-------|----------------|--------------------------|-------|-----|----|--------------------------------|------------------------------------------|---------------------------------------------------|--|

| SDIP32 | LQFP/ UFQFP: | Pin name               | Type | floating | ndw   | Ext. interrupt | High sink <sup>(1)</sup> | Speed | ao  | dd | Main function<br>(after reset) | Default alternate<br>function            | Alternate function<br>after remap<br>[option bit] |  |

| 4      | 31           | PD6/ AIN6/<br>UART1_RX | I/O  | x        | х     | х              | HS                       | О3    | х   | х  | Port D6                        | Analog input 6/<br>UART1 data<br>receive | -                                                 |  |

| 5      | 32           | PD7/ TLI<br>[TIM1_CH4] | I/O  | x        | х     | х              | HS                       | O3    | х   | х  | Port D7                        | Top level<br>interrupt                   | Timer 1 -<br>channel 4<br>[AFR6]                  |  |

#### Table 6. STM8S903K3 UFQFPN32/LQFP32/SDIP32 pin descriptions (continued)

1. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package. In addition, the total driven current must respect the absolute maximum ratings (see Section 10: Electrical characteristics).

2. When the MCU is in Halt/Active-halt mode, PA1 is automatically configured in input weak pull-up and cannot be used for waking up the device. In this mode, the output state of PA1 is not driven. It is recommended to use PA1 only in input mode if Halt/Active-halt is used in the application.

3. In the open-drain output column, "T" defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to V<sub>DD</sub> are not implemented).

4. The PD1 pin is in input pull-up during the reset phase and after internal reset release.

# 7 Interrupt vector mapping

| IRQ no. | Source block | Description                                               | Wakeup from<br>halt mode | Wakeup from active-halt mode | Vector address |

|---------|--------------|-----------------------------------------------------------|--------------------------|------------------------------|----------------|

| -       | RESET        | Reset                                                     | Yes                      | Yes                          | 0x00 8000      |

| -       | TRAP         | Software interrupt                                        | -                        | -                            | 0x00 8004      |

| 0       | TLI          | External top level<br>interrupt                           | -                        | -                            | 0x00 8008      |

| 1       | AWU          | Auto wake up from halt                                    | -                        | Yes                          | 0x00 800C      |

| 2       | CLK          | Clock controller                                          | -                        | -                            | 0x00 8010      |

| 3       | EXTI0        | Port A external<br>interrupts                             | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>           | 0x00 8014      |

| 4       | EXTI1        | Port B external<br>interrupts                             | Yes                      | Yes                          | 0x00 8018      |

| 5       | EXTI2        | Port C external<br>interrupts                             | Yes                      | Yes                          | 0x00 801C      |

| 6       | EXTI3        | Port D external<br>interrupts                             | Yes                      | Yes                          | 0x00 8020      |

| 7       | EXTI4        | Port E external<br>interrupts                             | Yes                      | Yes                          | 0x00 8024      |

| 8       | EXTI5        | Port F external<br>interrupts                             | -                        | -                            | 0x00 8028      |

| 9       | Reserved     | -                                                         | -                        | -                            | 0x00 802C      |

| 10      | SPI          | End of transfer                                           | Yes                      | Yes                          | 0x00 8030      |

| 11      | TIM1         | TIM1 update/<br>overflow/<br>underflow/ trigger/<br>break | -                        | -                            | 0x00 8034      |

| 12      | TIM1         | TIM1 capture/<br>compare                                  | -                        | -                            | 0x00 8038      |

| 13      | TIM5         | TIM5 update/<br>overflow/trigger                          | -                        | -                            | 0x00 803C      |

| 14      | TIM5         | TIM5 capture/<br>compare                                  | -                        | -                            | 0x00 8040      |

| 15      | Reserved     | -                                                         | -                        | -                            | 0x00 8044      |

| 16      | Reserved     | -                                                         | -                        | -                            | 0x00 8048      |

| 17      | UART1        | Tx complete                                               | -                        | -                            | 0x00 804C      |

| 18      | UART1        | Receive register<br>DATA FULL                             | _                        | -                            | 0x00 8050      |

| 19      | I2C          | I2C interrupt                                             | Yes                      | Yes                          | 0x00 8054      |

## Table 10. Interrupt mapping

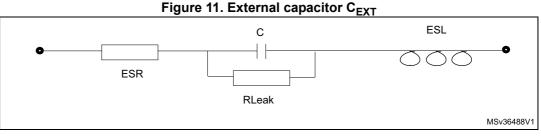

## 10.3.1 VCAP external capacitor

The stabilization for the main regulator is achieved by connecting an external capacitor  $C_{\text{EXT}}$  to the V<sub>CAP</sub> pin.  $C_{\text{EXT}}$  is specified in *Table 21*. Care should be taken to limit the series inductance to less than 15 nH.

1. ESR is the equivalent series resistance and ESL is the equivalent inductance.

## **10.3.2** Supply current characteristics

The current consumption is measured as illustrated in Figure 9: Pin input voltage.

### Total supply current consumption in run mode

The MCU is placed under the following conditions:

- All I/O pins in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled (clock stopped by peripheral clock gating registers) except if explicitly mentioned.

Subject to general operating conditions for V<sub>DD</sub> and T<sub>A</sub>.

| Table 23. Total current consumption with code execution in run mode at $V_{DD}$ = 5 V | ent consumption with code execution in r | run mode at V <sub>DD</sub> = 5 V |

|---------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|

|---------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|

| Symbol               | Parameter                                 | Conditi                                                     | ons                             | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|-------------------------------------------|-------------------------------------------------------------|---------------------------------|------|--------------------|------|

|                      |                                           |                                                             | HSE crystal osc. (16 MHz)       | 2.3  | -                  |      |

|                      |                                           | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock<br>(16 MHz) | 2    | 2.35               |      |

|                      | Supply<br>current in<br>Run mode,<br>code |                                                             | HSI RC osc. (16 MHz)            | 1.7  | 2                  |      |

| I <sub>DD(RUN)</sub> |                                           | $f_{CPU} = f_{MASTER} / 128 = 125 \text{ kHz}$              | HSE user ext. clock<br>(16 MHz) | 0.86 | -                  | mA   |

|                      | executed<br>from RAM                      |                                                             | HSI RC osc. (16 MHz)            | 0.7  | 0.87               |      |

|                      |                                           | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)          | 0.46 | 0.58               |      |

|                      |                                           | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)           | 0.41 | 0.55               |      |

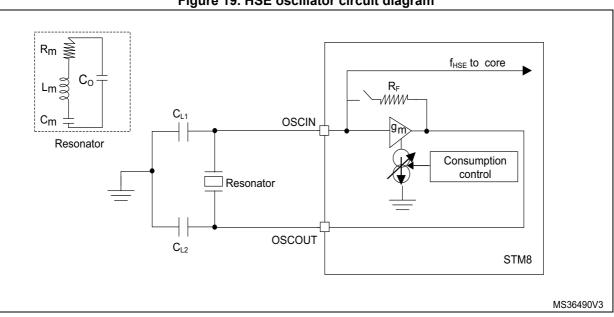

## HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

|                                     |                                             |                                        |     |     | 1                                               |      |

|-------------------------------------|---------------------------------------------|----------------------------------------|-----|-----|-------------------------------------------------|------|

| Symbol                              | Parameter                                   | Conditions                             | Min | Тур | Max                                             | Unit |

| f <sub>HSE</sub>                    | External high speed oscillator frequency    | -                                      | 1   | -   | 16                                              | MHz  |

| R <sub>F</sub>                      | Feedback resistor                           | -                                      | -   | 220 | -                                               | kΩ   |

| C <sup>(1)</sup>                    | Recommended load capacitance <sup>(2)</sup> | -                                      | -   | -   | 20                                              | pF   |

|                                     | HSE oscillator power                        | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (start up)<br>1.6 (stabilized) <sup>(3)</sup> | mA   |

| I <sub>DD(HSE)</sub>                | consumption                                 | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (start up)<br>1.2 (stabilized) <sup>(3)</sup> |      |

| 9 <sub>m</sub>                      | Oscillator<br>transconductance              | -                                      | 5   | -   | -                                               | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | V <sub>DD</sub> is stabilized          | -   | 1   | -                                               | ms   |

| Table | 35  | HSF | oscillator | characteristics |

|-------|-----|-----|------------|-----------------|

| Table | 55. |     | Uscillator |                 |

1. C is approximately equivalent to 2 x crystal Cload.

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small Rm value. Refer to crystal manufacturer for more details

3. Guaranteed by characterization results.

t<sub>SU(HSE)</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 16 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

#### Figure 19. HSE oscillator circuit diagram

## HSE oscillator critical g<sub>m</sub> equation

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

$R_m$ : Notional resistance (see crystal specification)  $L_m$ : Notional inductance (see crystal specification)  $C_m$ : Notional capacitance (see crystal specification) Co: Shunt capacitance (see crystal specification)  $C_{L1} = C_{L2} = C$ : Grounded external capacitance  $g_m \gg g_{mcrit}$

## Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

| Symbol               | Parameter                        | Conditions | Min | Тур | Max | Unit |

|----------------------|----------------------------------|------------|-----|-----|-----|------|

| f <sub>LSI</sub>     | Frequency                        | -          | 110 | 128 | 150 | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time       | -          | -   | -   | 7   | μs   |

| IDD(LSI)             | LSI oscillator power consumption | -          | -   | 5   | -   | μA   |

#### 25°C 85°C -125°C 5.00% -45'C 4.00% 3.00% 2.00% % accuracy 1.00% 0.00% -1.00% -2.00% -3.00% -4.00% -5.00% 3.5 2 2.5 3 4 4.5 5 5.5 6 $V_{pp}(V)$

## Figure 21. Typical LSI frequency variation vs $V_{\text{DD}} @$ 4 temperatures

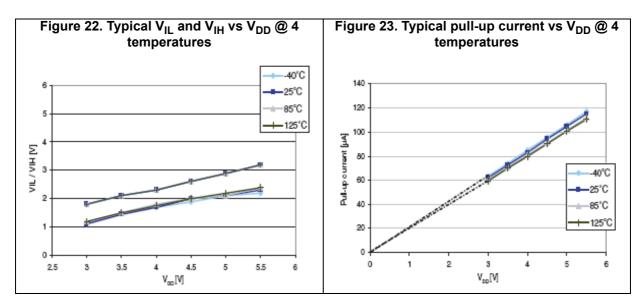

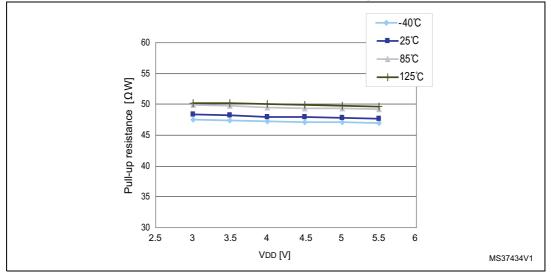

Figure 24. Typical pull-up resistance vs VDD @ 4 temperatures

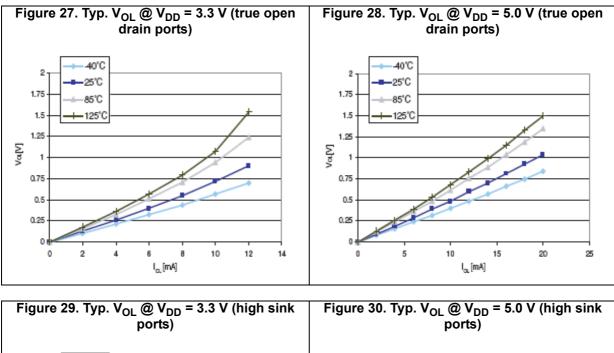

| Symbol          | Parameter                                | Conditions                                         | Min                | Мах                | Unit |

|-----------------|------------------------------------------|----------------------------------------------------|--------------------|--------------------|------|

| N.              | Output low level with 8<br>pins sunk     | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | -                  | 2.0                |      |

| V <sub>OL</sub> | Output low level with 4 pins sunk        | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | -                  | 1.0 <sup>(1)</sup> | V    |

| N               | Output high level with 8<br>pins sourced | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | 2.8                | -                  | V    |

| V <sub>OH</sub> | Output high level with 4<br>pins sourced | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | 2.1 <sup>(1)</sup> | -                  |      |

1. Guaranteed by characterization results

DocID15590 Rev 11

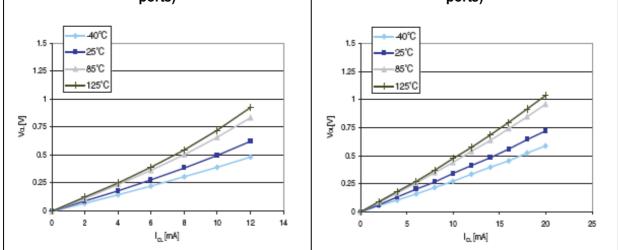

Figure 44. Typical application with ADC

1. Legend:  $R_{AIN}$  = external resistance,  $C_{AIN}$  = capacitors,  $C_{samp}$  = internal sample and hold capacitor.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

|        |                       | T <sub>A</sub> = 25 °C  |                      |

| LU     | Static latch-up class | T <sub>A</sub> = 85 °C  | А                    |

|        |                       | T <sub>A</sub> = 125 °C |                      |

#### Table 53. Electrical sensitivities

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

# 11 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

## 11.1 LQFP32 package information

Figure 45. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

DocID15590 Rev 11

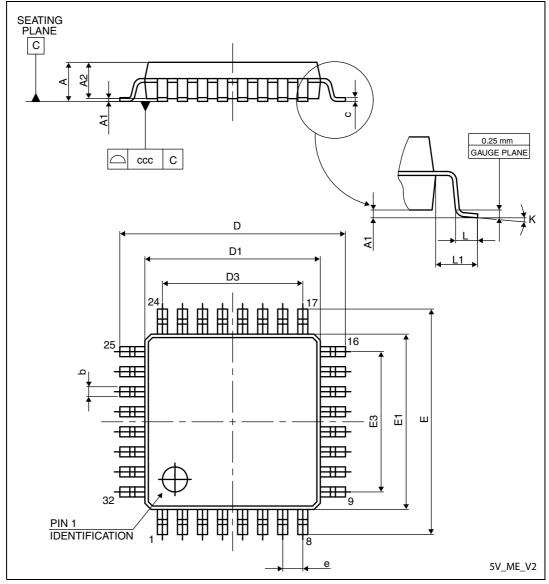

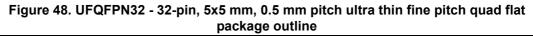

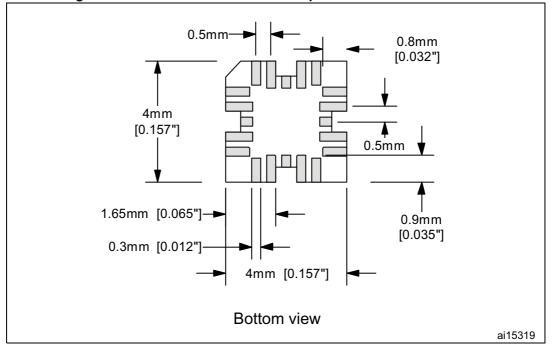

# 11.2 UFQFPN32 package information

1. Drawing is not to scale.

- 2. All leads/pads should be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this backside pad to PCB ground.

- 4. Dimensions are in millimeters.

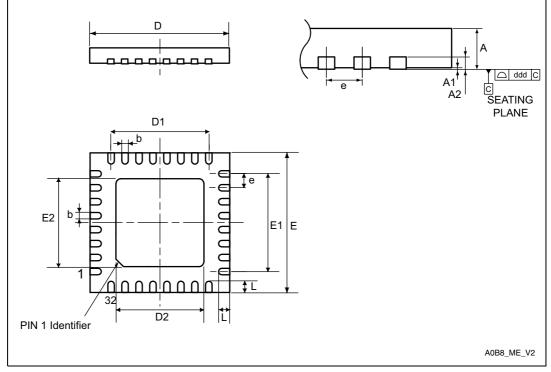

# 11.4 SDIP32 package information

### Figure 54. SDIP32 package outline

### Table 57. SDIP32 package mechanical data

| Dim  | mm     |        |        | inches <sup>(1)</sup> |        |        |

|------|--------|--------|--------|-----------------------|--------|--------|

| Dim. | Min    | Тур    | Мах    | Min                   | Тур    | Max    |

| А    | 3.556  | 3.759  | 5.080  | 0.1400                | 0.1480 | 0.2000 |

| A1   | 0.508  | -      | -      | 0.0200                | -      | -      |

| A2   | 3.048  | 3.556  | 4.572  | 0.1200                | 0.1400 | 0.1800 |

| В    | 0.356  | 0.457  | 0.584  | 0.0140                | 0.0180 | 0.0230 |

| B1   | 0.762  | 1.016  | 1.397  | 0.0300                | 0.0400 | 0.0550 |

| С    | 0.203  | 0.254  | 0.356  | 0.0079                | 0.0100 | 0.0140 |

| D    | 27.430 | 27.940 | 28.450 | 1.0799                | 1.1000 | 1.1201 |

| E    | 9.906  | 10.410 | 11.050 | 0.3900                | 0.4098 | 0.4350 |

| E1   | 7.620  | 8.890  | 9.398  | 0.3000                | 0.3500 | 0.3700 |

| е    | -      | 1.778  | -      | -                     | 0.0700 | -      |

| eA   | -      | 10.160 | -      | -                     | 0.4000 | -      |

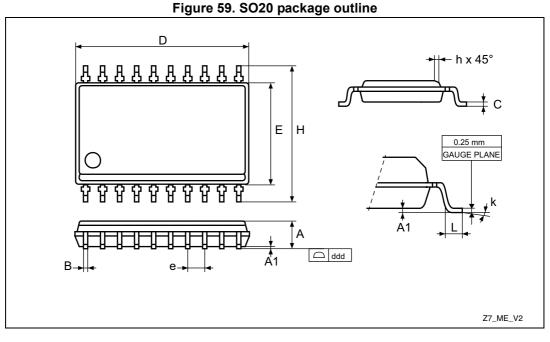

## 11.6 SO20 package information

## Table 59. SO20 mechanical data

| Dim  | mm     |       |        | inches <sup>(1)</sup> |        |        |

|------|--------|-------|--------|-----------------------|--------|--------|

| Dim. | Min    | Тур   | Max    | Min                   | Тур    | Max    |

| А    | 2.350  | -     | 2.650  | 0.0925                | -      | 0.1043 |

| A1   | 0.100  | -     | 0.300  | 0.0039                | -      | 0.0118 |

| В    | 0.330  | -     | 0.510  | 0.013                 | -      | 0.0201 |

| С    | 0.230  | -     | 0.320  | 0.0091                | -      | 0.0126 |

| D    | 12.600 | -     | 13.000 | 0.4961                | -      | 0.5118 |

| E    | 7.400  | -     | 7.600  | 0.2913                | -      | 0.2992 |

| е    | -      | 1.270 | -      | -                     | 0.0500 | -      |

| Н    | 10.000 | -     | 10.650 | 0.3937                | -      | 0.4193 |

| h    | 0.250  | -     | 0.750  | 0.0098                | -      | 0.0295 |

| L    | 0.400  | -     | 1.270  | 0.0157                | -      | 0.0500 |

| k    | 0.0°   | -     | 8.0°   | 0.0°                  | -      | 8.0°   |

| ddd  | -      | -     | 0.100  | -                     | -      | 0.0039 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

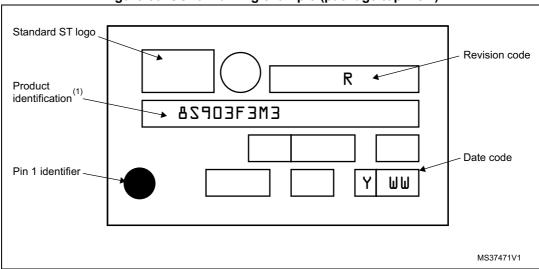

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 60. SO20 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# **11.7 UFQFPN recommended footprint**

## OTP2 alternate function remapping for STM8S903K3

Do not use more than one remapping option in the same port.

|                                 | [] 00: Remapping options inactive. Default alternate functions                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | used. Refer to pinout description.                                                                                                                                                                                                                                                                                                                                                             |

|                                 | [] 01: Port C5 alternate function = TIM5_CH1, port C6 alternate function = TIM1_CH1, and port C7 alternate function = TIM1_CH2.                                                                                                                                                                                                                                                                |

| AFR1, AFR0                      | [] 10: Port A3 alternate function = SPI_NSS and port D2 alternate function = TIM5_CH3.                                                                                                                                                                                                                                                                                                         |

| (check only one option)         | [] 11: Port D2 alternate function = TIM5_CH3, port C5 alternate<br>function = TIM5_CH1, port C6 alternate function = TIM1_CH1,<br>port C7 alternate function = TIM1_CH2, port C2 alternate<br>function = TIM1_CH3N, port C1 alternate function =<br>TIM1_CH2N, port E5 alternate function = TIM1_CH1N, port A3<br>alternate function = UART1_TX, and port F4 alternate function<br>= UART1_RX. |

| AFR2                            | [] 0: Remapping option inactive. Default alternate functions used. Refer to pinout description.                                                                                                                                                                                                                                                                                                |

| (check only one option)         | [] 1: Port C4 alternate function = AIN2, port D2 alternate function = AIN3, port D4 alternate function = UART1_CK.                                                                                                                                                                                                                                                                             |

| AFR3                            | [] 0: Remapping option inactive. Default alternate functions used. Refer to pinout description.                                                                                                                                                                                                                                                                                                |

| (check only one option)         | [] 1: Port C3 alternate function = TLI.                                                                                                                                                                                                                                                                                                                                                        |

| AFR4                            | [] 0: Remapping option inactive. Default alternate functions used. Refer to pinout description.                                                                                                                                                                                                                                                                                                |

| (check only one option)         | [] 1: Port B4 alternate function = ADC_ETR, port B5 alternate function = TIM1_BKIN.                                                                                                                                                                                                                                                                                                            |

| AFR5<br>(check only one option) | <ul> <li>[] 0: Remapping option inactive. Default alternate functions used. Refer to pinout description.</li> <li>[] 1: Port D0 alternate function = CLK CCO.</li> </ul>                                                                                                                                                                                                                       |

|                                 | [] 0: Remapping option inactive. Default alternate functions                                                                                                                                                                                                                                                                                                                                   |

| AFR6<br>(check only one option) | used. Refer to pinout description.<br>[] 1: Port D7 alternate function = TIM1_CH4.                                                                                                                                                                                                                                                                                                             |

| AFR7                            | [] 0: Remapping option inactive. Default alternate functions used. Refer to pinout description.                                                                                                                                                                                                                                                                                                |

| (check only one option)         | [] 1: Port C3 alternate function = TIM1_CH1N, port C4 alternate function = TIM1_CH2N.                                                                                                                                                                                                                                                                                                          |

## 14.3 **Programming tools**

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the application board via the SWIM protocol. Additional tools include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for the STM8 programming.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28-Jul-2011 | 6        | <ul> <li>Added note for OPT1 option list.</li> <li>Updated OPT2 option list for STM8S903K3 and created OPT2 option list for STM8S903F3 in Section 13.1:<br/>STM8S903K3/F3 FASTROM microcontroller option list.</li> <li>Updated UART1 interrupt vector addresses in Table 10:<br/>Interrupt mapping.</li> <li>Updated note related to true open-drain outputs in Table 6: STM8S903K3 UFQFPN32/LQFP32/SDIP32 pin descriptions and Table 5: TSSOP20/SO20/UFQFPN20 pin descriptions.</li> <li>Added UFQFPN20 package.</li> <li>Removed CLK_CANCCR register from Table 8: General hardware register map.</li> <li>Added note for Px_IDR registers in Table 7: I/O port hardware register map.</li> <li>Updated the caption of Figure 63: STM8S903K3/F3 access line ordering information scheme<sup>(1)</sup>.</li> <li>Removed Typical HSI accuracy curve in High speed internal RC oscillator (HSI)</li> <li>Updated the value of recommended external capacitor to 100 nF in Table 44: NRST pin characteristics.</li> <li>Updated the disclaimer.</li> </ul> |

| 04-Apr-2012 | 7        | Renamed internal reference voltage as internal bandgap<br>reference voltage.Updated notes related to VCAP in Table 21: General<br>operating conditions.Added values of t <sub>R</sub> /t <sub>F</sub> for 50 pF load capacitance, and<br>updated note in Table 40: I/O static characteristics.Updated typical and maximum values of RPU in<br>Table 40: I/O static characteristics and Table 44: NRST<br>pin characteristics.Changed SCK input to SCK output in Table 45: SPI<br>characteristics.Modified Figure 51: UFQFPN20 - 20-lead, 3x3 mm, 0.5<br>mm pitch, ultra thin fine pitch quad flat package outline.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13-Jun-2012 | 8        | Restored Figure 44: Typical application with ADC.<br>Modified Figure 51: UFQFPN20 - 20-lead, 3x3 mm, 0.5<br>mm pitch, ultra thin fine pitch quad flat package outline.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 61. Document revision history (continued)

| Date Revision |   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-Feb-2015   | 9 | <ul> <li>Updated:</li> <li>Section 11.5: TSSOP20 package information</li> <li>Section 11.3: UFQFPN20 package information.</li> <li>Added:</li> <li>Figure 46: LQFP32 recommended footprint</li> <li>Figure 47: LQFP32 marking example (package top view)</li> <li>Figure 50: UFQFPN32 marking example (package top view)</li> <li>Figure 53: UFQFPN20 marking example (package top view)</li> <li>Figure 55: SDIP32 marking example (package top view)</li> <li>Figure 57: TSSOP20 recommended package footprint</li> <li>Figure 58: TSSOP20 marking example (package top view)</li> <li>Figure 58: TSSOP20 marking example (package top view)</li> <li>Figure 60: SO20 marking example (package top view)</li> </ul> |