#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             |                                                 |

|----------------------------|-------------------------------------------------|

|                            | Active                                          |

| Core Processor             | STM8                                            |

| Core Size                  | 8-Bit                                           |

| Speed                      | 16MHz                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT           |

| Number of I/O              | 28                                              |

| Program Memory Size        | 8KB (8K x 8)                                    |

| Program Memory Type        | FLASH                                           |

| EEPROM Size                | 640 x 8                                         |

| RAM Size                   | 1K x 8                                          |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                    |

| Data Converters            | A/D 7x10b                                       |

| Oscillator Type            | Internal                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                               |

| Mounting Type              | Surface Mount                                   |

| Package / Case             | 32-LQFP                                         |

| Supplier Device Package    | -                                               |

|                            |                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

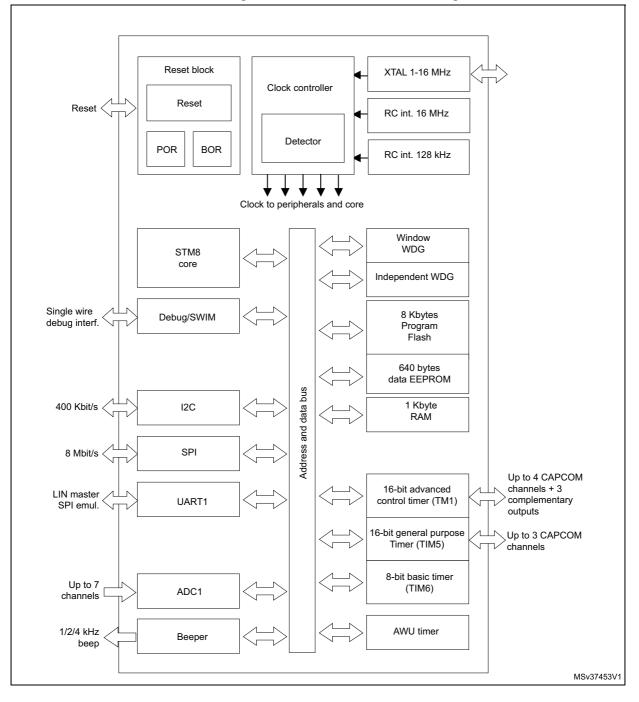

# 3 Block diagram

57

DocID15590 Rev 11

## 4.11 TIM5 - 16-bit general purpose timer

- 16-bit autoreload (AR) up-counter

- 15-bit prescaler adjustable to fixed power of 2 ratios 1...32768

- 3 individually configurable capture/compare channels

- PWM mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update

- Synchronization module to control the timer with external signals or to synchronize with TIM1 or TIM6

## 4.12 TIM6 - 8-bit basic timer

- 8-bit autoreload, adjustable prescaler ratio to any power of 2 from 1 to 128

- Clock source: CPU clock

- Interrupt source: 1 x overflow/update

- Synchronization module to control the timer with external signals or to synchronize with TIM1 or TIM5.

| Timer | Counter<br>size (bits) | Prescaler                            | Counting<br>mode | CAPCOM<br>channels | Complementary<br>outputs | Ext.<br>trigger | Timer<br>synchronization/<br>chaining |

|-------|------------------------|--------------------------------------|------------------|--------------------|--------------------------|-----------------|---------------------------------------|

| TIM1  | 16                     | Any integer<br>from 1 to<br>65536    | Up/down          | 4                  | 3                        | Yes             |                                       |

| TIM5  | 16                     | Any power of<br>2 from 1 to<br>32768 | Up               | 3                  | 0                        | No              | Yes                                   |

| TIM6  | 8                      | Any power of<br>2 from 1 to<br>128   | Up               | 0                  | 0                        | No              |                                       |

### Table 3. TIM timer features

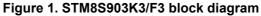

## 5 Pinouts and pin descriptions

| Туре                           | I= Input, O = Output, S = Power su                                                                                                                                                                                                      | ipply                                                      |  |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|

|                                | Input                                                                                                                                                                                                                                   | CM = CMOS                                                  |  |  |  |  |

| Level                          | Output                                                                                                                                                                                                                                  | HS = High sink                                             |  |  |  |  |

| Output speed                   | <ul> <li>O1 = Slow (up to 2 MHz)</li> <li>O2 = Fast (up to 10 MHz)</li> <li>O3 = Fast/slow programmability with slow as default state after res</li> <li>O4 = Fast/slow programmability with fast as default state after res</li> </ul> |                                                            |  |  |  |  |

| Dent and a sector l            | Input                                                                                                                                                                                                                                   | float = floating,<br>wpu = weak pull-up                    |  |  |  |  |

| Port and control configuration | Output                                                                                                                                                                                                                                  | T = True open drain,<br>OD = Open drain,<br>PP = Push pull |  |  |  |  |

| Reset state                    | Bold <b>X</b> (pin state after internal reset release).<br>Unless otherwise specified, the pin state is the same during the resphase and after the internal reset release.                                                              |                                                            |  |  |  |  |

#### Table 4. Legend/abbreviations for pinout tables

## 5.1 STM8S903F3 TSSOP20/SO20 pinout

#### Figure 3. STM8S903F3 TSSOP20/SO20 pinout

1. HS high sink capability.

- 2. (T) True open drain (P-buffer and protection diode to  $V_{DD}$  not implemented).

- 3. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function)

|        | 32            |                                              |      |          | Input | t              |                          | Out   | put      |    | c                              | te                                                    | noi                                                                        |

|--------|---------------|----------------------------------------------|------|----------|-------|----------------|--------------------------|-------|----------|----|--------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|

| SDIP32 | LQFP/ UFQFP32 | Pin name                                     | Type | floating | ndw   | Ext. interrupt | High sink <sup>(1)</sup> | Speed | QD       | РР | Main function<br>(after reset) | Default alternate<br>function                         | Alternate function<br>after remap<br>[option bit]                          |

| 12     | 7             | PA3/ TIM5_CH3<br>[SPI_NSS]<br>[UART1_TX]     | I/O  | x        | x     | x              | HS                       | O3    | x        | x  | Port A3                        | Timer 5 channel<br>3                                  | SPI master/<br>slave select<br>[AFR1] /UART1<br>data transmit<br>[AFR 1:0] |

| 13     | 8             | PF4<br>[UART1_RX]                            | I/O  | x        | Х     | -              | -                        | 01    | х        | Х  | Port F4                        | -                                                     | UART1 data<br>receive [AFR1:0]                                             |

| 14     | 9             | PB7                                          | I/O  | x        | х     | х              | -                        | 01    | х        | х  | Port B7                        | -                                                     | -                                                                          |

| 15     | 10            | PB6                                          | I/O  | x        | х     | Х              | -                        | 01    | х        | х  | Port B6                        | -                                                     | -                                                                          |

| 16     | 11            | PB5/ I2C_SDA<br>[TIM1_BKIN]                  | I/O  | x        | -     | х              | -                        | 01    | T<br>(3) | -  | Port B5                        | I2C data                                              | Timer 1 - break<br>input [AFR4]                                            |

| 17     | 12            | PB4/ I2C_SCL<br>[ADC_ETR]                    | I/O  | x        | -     | Х              | -                        | 01    | Т        | -  | Port B4                        | I2C clock                                             | ADC external trigger [AFR4]                                                |

| 18     | 13            | PB3/<br>AIN3/TIM1_ETR                        | I/O  | x        | х     | х              | HS                       | О3    | х        | х  | Port B3                        | Analog input 3/<br>Timer 1 external<br>trigger        | -                                                                          |

| 19     | 14            | PB2/ AIN2/<br>TIM1_CH3N                      | I/O  | x        | х     | х              | HS                       | O3    | х        | х  | Port B2                        | Analog input 2/<br>Timer 1 -<br>inverted channel<br>3 | -                                                                          |

| 20     | 15            | PB1/ AIN1/<br>TIM1_CH2N                      | I/O  | x        | х     | х              | HS                       | O3    | х        | х  | Port B1                        | Analog input 1/<br>Timer 1 -<br>inverted channel<br>2 | -                                                                          |

| 21     | 16            | PB0/ AIN0/<br>TIM1_CH1N                      | I/O  | x        | х     | х              | HS                       | O3    | х        | х  | Port B0                        | Analog input 0/<br>Timer 1 -<br>inverted channel<br>1 | -                                                                          |

| 22     | 17            | PE5/ SPI_NSS<br>[TIM1_CH1N]                  | I/O  | x        | х     | х              | HS                       | О3    | х        | х  | Port E5                        | SPI master/slave select                               | Timer 1 -<br>inverted channel<br>1 [AFR1:0]                                |

| 23     | 18            | PC1/<br>TIM1_CH1/<br>UART1_CK<br>[TIM1_CH2N] | I/O  | x        | х     | x              | HS                       | O3    | х        | х  | Port C1                        | Timer 1 -<br>channel 1<br>UART1 clock                 | Timer 1 -<br>inverted channel<br>2 [AFR1:0]                                |

## Table 6. STM8S903K3 UFQFPN32/LQFP32/SDIP32 pin descriptions (continued)

# 6.2 Register map

## 6.2.1 I/O port hardware register map

## Table 7. I/O port hardware register map

| Address   | Block  | Register label | Register name                     | Reset status        |

|-----------|--------|----------------|-----------------------------------|---------------------|

| 0x00 5000 |        | PA_ODR         | Port A data output latch register | 0x00                |

| 0x00 5001 |        | PA_IDR         | Port A input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5002 | Port A | PA_DDR         | Port A data direction register    | 0x00                |

| 0x00 5003 |        | PA_CR1         | Port A control register 1         | 0x00                |

| 0x00 5004 |        | PA_CR2         | Port A control register 2         | 0x00                |

| 0x00 5005 |        | PB_ODR         | Port B data output latch register | 0x00                |

| 0x00 5006 |        | PB_IDR         | Port B input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5007 | Port B | PB_DDR         | Port B data direction register    | 0x00                |

| 0x00 5008 |        | PB_CR1         | Port B control register 1         | 0x00                |

| 0x00 5009 |        | PB_CR2         | Port B control register 2         | 0x00                |

| 0x00 500A |        | PC_ODR         | Port C data output latch register | 0x00                |

| 0x00 500B |        | PB_IDR         | Port C input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 500C | Port C | PC_DDR         | Port C data direction register    | 0x00                |

| 0x00 500D |        | PC_CR1         | Port C control register 1         | 0x00                |

| 0x00 500E |        | PC_CR2         | Port C control register 2         | 0x00                |

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00                |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00                |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x02                |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00                |

| 0x00 5014 |        | PE_ODR         | Port E data output latch register | 0x00                |

| 0x00 5015 |        | PE_IDR         | Port E input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 5016 | Port E | PE_DDR         | Port E data direction register    | 0x00                |

| 0x00 5017 |        | PE_CR1         | Port E control register 1         | 0x00                |

| 0x00 5018 |        | PE_CR2         | Port E control register 2         | 0x00                |

| 0x00 5019 |        | PF_ODR         | Port F data output latch register | 0x00                |

| 0x00 501A |        | PF_IDR         | Port F input pin value register   | 0xXX <sup>(1)</sup> |

| 0x00 501B | Port F | PF_DDR         | Port F data direction register    | 0x00                |

| 0x00 501C |        | PF_CR1         | Port F control register 1         | 0x00                |

| 0x00 501D | 1      | PF_CR2         | Port F control register 2         | 0x00                |

1. Depends on the external circuitry.

| Block | Register label           | Register name                                                                                                                                 | Reset status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       | TIM6_CR1                 | TIM6 control register 1                                                                                                                       | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | TIM6_CR2                 | TIM6 control register 2                                                                                                                       | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| •     | TIM6_SMCR                | TIM6 slave mode control register                                                                                                              | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | TIM6_IER                 | TIM6 interrupt enable register                                                                                                                | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| TIM6  | TIM6_SR                  | TIM6 status register                                                                                                                          | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | TIM6_EGR                 | TIM6 event generation register                                                                                                                | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | TIM6_CNTR                | TIM6 counter                                                                                                                                  | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | TIM6_PSCR                | TIM6 prescaler register                                                                                                                       | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | TIM6_ARR                 | TIM6 auto-reload register                                                                                                                     | 0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | Reserved area (153 byte) |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| ADC1  | ADC_DBxR                 | ADC data buffer registers                                                                                                                     | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | Reserved area (12 byte)  |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|       | Block<br>TIM6            | Block Register label TIM6_CR1 TIM6_CR2 TIM6_SMCR TIM6_IER TIM6_IER TIM6_SR TIM6_EGR TIM6_EGR TIM6_PSCR TIM6_PSCR TIM6_ARR Reser ADC1 ADC_DBxR | Block         Register label         Register name           TIM6_CR1         TIM6 control register 1           TIM6_CR2         TIM6 control register 2           TIM6_SMCR         TIM6 slave mode control register           TIM6_IER         TIM6 interrupt enable register           TIM6_SR         TIM6 status register           TIM6_EGR         TIM6 event generation register           TIM6_PSCR         TIM6 prescaler register           TIM6_ARR         TIM6 auto-reload register           Reserved area (153 byte)         ADC1 |  |  |  |  |

Table 8. General hardware register map (continued)

2. Refer to STM8S903K3 pin descriptions.

#### Table 14. STM8S903F3 alternate function remapping bits [7:2] for 20-pin packages

| AFR7 Alternate function remapping option 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Option byte no. | Description <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0: AFR7 remapping option inactive: Default alternate functions. <sup>(2)</sup> 1: Port C3 alternate function = TIM1_CH1N;         port C4 alternate function = TIM1_CH2N.         AFR6 Alternate function remapping option 6         Reserved.         AFR5 Alternate function remapping option 5         Reserved.         AFR4 Alternate function remapping option 4         0: AFR4 remapping option inactive: Default alternate functions. <sup>(2)</sup> 1: Port B4 alternate function = ADC_ETR;         port B5 alternate function remapping option 3         0: AFR3 remapping option inactive: Default alternate function. <sup>(2)</sup> 1: Port C3 alternate function = TIM1_BKIN.         AFR3 Alternate function = TIM1_BKIN.         AFR3 Alternate function = TLI.         AFR2 Alternate function = TLI.         AFR2 Alternate function remapping option 2         Reserved. |                 | <ul> <li>AFR7 Alternate function remapping option 7</li> <li>0: AFR7 remapping option inactive: Default alternate functions.<sup>(2)</sup></li> <li>1: Port C3 alternate function = TIM1_CH1N; port C4 alternate function = TIM1_CH2N.</li> <li>AFR6 Alternate function remapping option 6</li> <li>Reserved.</li> <li>AFR5 Alternate function remapping option 5</li> <li>Reserved.</li> <li>AFR4 Alternate function remapping option 4</li> <li>0: AFR4 remapping option inactive: Default alternate functions.<sup>(2)</sup></li> <li>1: Port B4 alternate function = ADC_ETR; port B5 alternate function = TIM1_BKIN.</li> <li>AFR3 Alternate function remapping option 3</li> <li>0: AFR3 remapping option inactive: Default alternate function.<sup>(2)</sup></li> <li>1: Port C3 alternate function = TLI.</li> <li>AFR2 Alternate function remapping option 2</li> </ul> |

1. Do not use more than one remapping option in the same port.

2. Refer to STM8S903K3 pin descriptions.

| AFR1 option bit value | AFR0 option bit value | I/O port                                                                         | Alternate function<br>mapping |  |

|-----------------------|-----------------------|----------------------------------------------------------------------------------|-------------------------------|--|

| 0                     | 0                     | AFR1 and AFR0 remapping options inact Default alternate functions <sup>(1)</sup> |                               |  |

|                       |                       | PC5                                                                              | TIM5_CH1                      |  |

| 0                     | 1                     | PC6                                                                              | TIM1_CH1                      |  |

|                       |                       | PC7                                                                              | TIM1_CH2                      |  |

| 1                     | 0                     | PA3                                                                              | SPI_NSS                       |  |

|                       | 0                     | PD2                                                                              | TIM5_CH3                      |  |

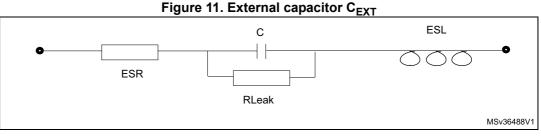

## 10.3.1 VCAP external capacitor

The stabilization for the main regulator is achieved by connecting an external capacitor  $C_{\text{EXT}}$  to the V<sub>CAP</sub> pin.  $C_{\text{EXT}}$  is specified in *Table 21*. Care should be taken to limit the series inductance to less than 15 nH.

1. ESR is the equivalent series resistance and ESL is the equivalent inductance.

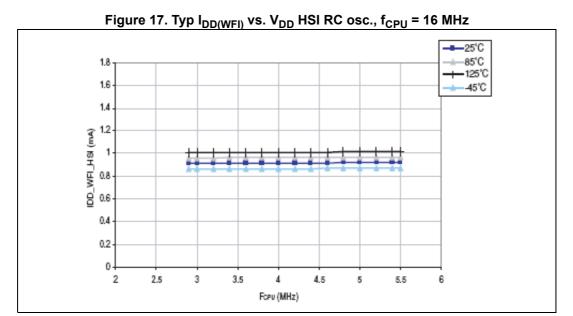

### **10.3.2** Supply current characteristics

The current consumption is measured as illustrated in Figure 9: Pin input voltage.

#### Total supply current consumption in run mode

The MCU is placed under the following conditions:

- All I/O pins in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled (clock stopped by peripheral clock gating registers) except if explicitly mentioned.

Subject to general operating conditions for V<sub>DD</sub> and T<sub>A</sub>.

| Table 23. Total current consumption with code execution in run mode at $V_{DD}$ = 5 V | ent consumption with code execution in r | run mode at V <sub>DD</sub> = 5 V |

|---------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|

|---------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|

| Symbol               | Parameter                                                         | Conditi                                                     | Тур                             | Max <sup>(1)</sup> | Unit |    |

|----------------------|-------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|--------------------|------|----|

|                      |                                                                   |                                                             | HSE crystal osc. (16 MHz)       | 2.3                | -    |    |

|                      | Supply<br>current in<br>Run mode,<br>code<br>executed<br>from RAM | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock<br>(16 MHz) | 2                  | 2.35 |    |

| I <sub>DD(RUN)</sub> |                                                                   |                                                             | HSI RC osc. (16 MHz)            | 1.7                | 2    | mA |

|                      |                                                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSE user ext. clock<br>(16 MHz) | 0.86               | -    |    |

|                      |                                                                   |                                                             | HSI RC osc. (16 MHz)            | 0.7                | 0.87 |    |

|                      |                                                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)          | 0.46               | 0.58 |    |

|                      |                                                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)           | 0.41               | 0.55 |    |

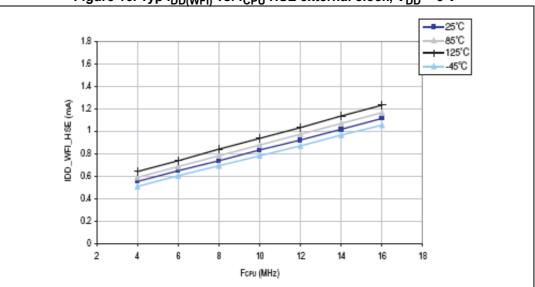

Figure 16. Typ  $I_{DD(WFI)}$  vs.  $f_{CPU}$  HSE external clock,  $V_{DD}$  = 5 V

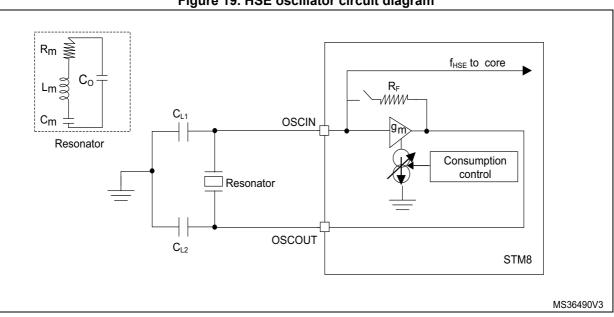

#### Figure 19. HSE oscillator circuit diagram

## HSE oscillator critical g<sub>m</sub> equation

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

$R_m$ : Notional resistance (see crystal specification)  $L_m$ : Notional inductance (see crystal specification)  $C_m$ : Notional capacitance (see crystal specification) Co: Shunt capacitance (see crystal specification)  $C_{L1} = C_{L2} = C$ : Grounded external capacitance  $g_m \gg g_{mcrit}$

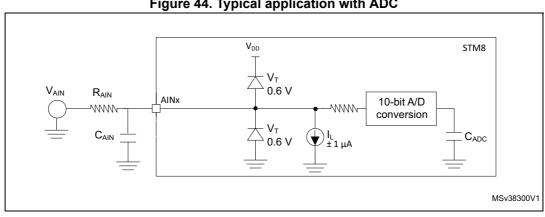

## **10.3.10 10-bit ADC characteristics**

Subject to general operating conditions for  $V_{\text{DDA}},\,f_{\text{MASTER}},\,\text{and}\,\,T_{\text{A}}\,\,\text{unless}$  otherwise specified.

| Symbol             | Parameter                               | Conditions                         | Min      | Тур  | Max      | Unit               |

|--------------------|-----------------------------------------|------------------------------------|----------|------|----------|--------------------|

| £                  |                                         | $V_{\rm DD}\text{=}$ 2.95 to 5.5 V | 1        | -    | 4        |                    |

| f <sub>ADC</sub>   | ADC clock frequency                     | V <sub>DD</sub> = 4.5 to 5.5 V     | 1        | -    | - 6 MHz  |                    |

| V <sub>AIN</sub>   | Conversion voltage range <sup>(1)</sup> | -                                  | $V_{SS}$ | -    | $V_{DD}$ | V                  |

| V <sub>BGREF</sub> | Internal bandgap reference voltage      | V <sub>DD</sub> = 2.95 to 5.5 V    | 1.19     | 1.22 | 1.25     | V                  |

| C <sub>ADC</sub>   | Internal sample and hold capacitor      | -                                  | -        | 3    | -        | pF                 |

| ts <sup>(1)</sup>  | Minimum sampling time                   | f <sub>ADC</sub> = 4 MHz           | -        | 0.75 | -        | 110                |

| us Y               |                                         | f <sub>ADC</sub> = 6 MHz           | -        | 0.5  | -        | μs                 |

| t <sub>STAB</sub>  | Wakeup time from standby                | -                                  | -        | 7.0  | -        | μs                 |

|                    | Minimum total conversion time           | f <sub>ADC</sub> = 4 MHz           |          | 3.5  |          | μs                 |

| t <sub>CONV</sub>  | (including sampling time, 10-           | f <sub>ADC</sub> = 6 MHz           |          | 2.33 |          | μs                 |

|                    | bit resolution)                         | -                                  | 14       |      |          | 1/f <sub>ADC</sub> |

During the sample time, the sampling capacitance, C<sub>AIN</sub> (3 pF max), can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>S</sub> depend on programming.

Figure 44. Typical application with ADC

1. Legend:  $R_{AIN}$  = external resistance,  $C_{AIN}$  = capacitors,  $C_{samp}$  = internal sample and hold capacitor.

### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC 61967-2 which specifies the board and the loading of each pin.

| Symbol           |            | Conditions                                                            |                   |                  |      |      |  |  |

|------------------|------------|-----------------------------------------------------------------------|-------------------|------------------|------|------|--|--|

|                  | Parameter  |                                                                       | Monitored         | Max f            | Unit |      |  |  |

|                  |            | General conditions                                                    | frequency band    | 16 MHz/<br>8 MHz |      |      |  |  |

|                  | Peak level | $V_{DD} = 5 V,$<br>$T_A = 25 °C,$<br>LQFP32 package.<br>Conforming to | 0.1 MHz to 30 MHz | 5                | 5    |      |  |  |

| e                |            |                                                                       | 30 MHz to 130 MHz | 4                | 5    | dBµV |  |  |

| S <sub>EMI</sub> |            |                                                                       | 130 MHz to 1 GHz  | 5 5              |      |      |  |  |

|                  | EMI level  | IEC 61967-2                                                           | EMI level         | 2.5              | 2.5  | -    |  |  |

| Table | 51. | EMI | data |

|-------|-----|-----|------|

|-------|-----|-----|------|

1. Guaranteed by characterization results.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD, DLU and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts x (n+1) supply pin). One model can be simulated: Human body model. This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                                  | Conditions                                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|---------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model)    | $T_A = 25^{\circ}C$ , conforming to JESD22-A114                     | А     | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage<br>(Charge device model) | T <sub>A</sub> = 25°C, conforming to<br>SD22-C101<br>LQFP32 package | IV    | 1000                            | V    |

| Table 52. | ESD | absolute | maximum | ratings |

|-----------|-----|----------|---------|---------|

|           |     |          |         |         |

1. Guaranteed by characterization results

### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin), and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

DocID15590 Rev 11

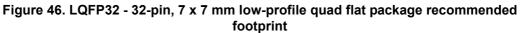

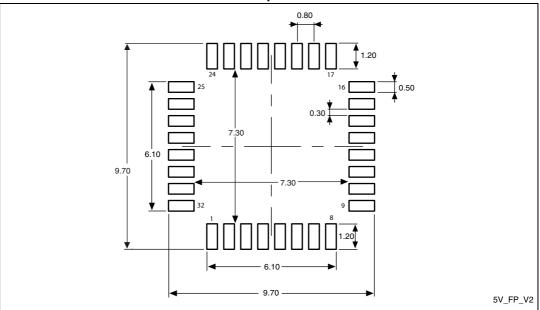

| Querra ha a l |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |  |  |

|---------------|-------|-------------|-------|-----------------------|--------|--------|--|--|--|

| Symbol        | Min   | Тур         | Мах   | Min                   | Тур    | Max    |  |  |  |

| А             | -     | -           | 1.600 | -                     | -      | 0.0630 |  |  |  |

| A1            | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |  |  |  |

| A2            | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |  |  |

| b             | 0.300 | 0.370       | 0.450 | 0.0118                | 0.0146 | 0.0177 |  |  |  |

| С             | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |  |  |  |

| D             | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |  |  |

| D1            | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |  |  |

| D3            | -     | 5.600       | -     | -                     | 0.2205 | -      |  |  |  |

| E             | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |  |  |

| E1            | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |  |  |

| E3            | -     | 5.600       | -     | -                     | 0.2205 | -      |  |  |  |

| е             | -     | 0.800       | -     | -                     | 0.0315 | -      |  |  |  |

| L             | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |  |  |

| L1            | -     | 1.000       | -     | -                     | 0.0394 | -      |  |  |  |

| k             | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |  |  |

| CCC           | -     | -           | 0.100 | -                     | -      | 0.0039 |  |  |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

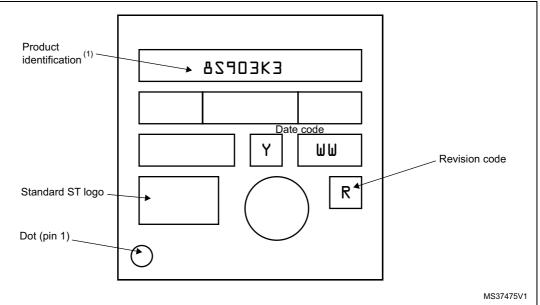

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Table 01. Obli 02 package mechanical data (continued) |       |       |        |        |                       |        |  |  |  |

|-------------------------------------------------------|-------|-------|--------|--------|-----------------------|--------|--|--|--|

| Dim.                                                  |       | mm    |        |        | inches <sup>(1)</sup> |        |  |  |  |

| Dini.                                                 | Min   | Тур   | Max    | Min    | Тур                   | Max    |  |  |  |

| eB                                                    | -     | -     | 12.700 | -      | -                     | 0.5000 |  |  |  |

| L                                                     | 2.540 | 3.048 | 3.810  | 0.1000 | 0.1200                | 0.1500 |  |  |  |

Table 57. SDIP32 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits

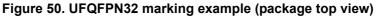

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 55. SDIP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

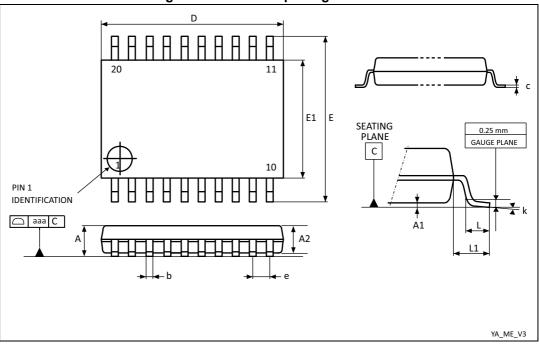

## 11.5 TSSOP20 package information

#### Figure 56. TSSOP20 package outline

## Table 58. TSSOP20 package mechanical data

| Dim.              |       | mm    |       | inches <sup>(1)</sup> |        |        |  |  |

|-------------------|-------|-------|-------|-----------------------|--------|--------|--|--|

| Dini.             | Min   | Тур   | Max   | Min                   | Тур    | Мах    |  |  |

| А                 | -     | -     | 1.200 | -                     | -      | 0.0472 |  |  |

| A1                | 0.050 | -     | 0.150 | 0.0020                | -      | 0.0059 |  |  |

| A2                | 0.800 | 1.000 | 1.050 | 0.0315                | 0.0394 | 0.0413 |  |  |

| b                 | 0.190 | -     | 0.300 | 0.0075                | -      | 0.0118 |  |  |

| с                 | 0.090 | -     | 0.200 | 0.0035                | -      | 0.0079 |  |  |

| D <sup>(2)</sup>  | 6.400 | 6.500 | 6.600 | 0.2520                | 0.2559 | 0.2598 |  |  |

| E                 | 6.200 | 6.400 | 6.600 | 0.2441                | 0.2520 | 0.2598 |  |  |

| E1 <sup>(3)</sup> | 4.300 | 4.400 | 4.500 | 0.1693                | 0.1732 | 0.1772 |  |  |

| е                 | -     | 0.650 | -     | -                     | 0.0256 | -      |  |  |

| L                 | 0.450 | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1                | -     | 1.000 | -     | - 0.0394              |        | -      |  |  |

| k                 | 0.0°  | -     | 8.0°  | 0.0°                  | -      | 8.0°   |  |  |

| ааа               | -     | -     | 0.100 | -                     | -      | 0.0039 |  |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

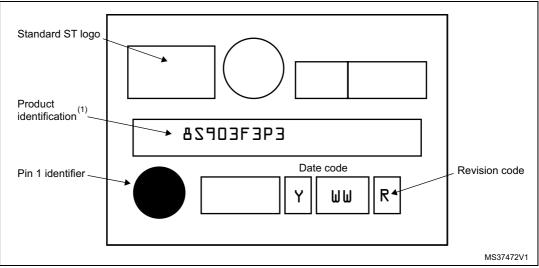

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 58. TSSOP20 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# **13** Ordering information

| Figure 63. STM8S903K3/F3                                                                                                                                                             | access li       | ne or   | dering    | g inf  | orma | ation | sch   | neme <sup>(1</sup> | 1) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|-----------|--------|------|-------|-------|--------------------|----|

| Evennlei                                                                                                                                                                             | OTMO            | 0       | 002       | K      | 0    | Ŧ     | 0     | 0                  | тр |

| Example:                                                                                                                                                                             | STM8            | S       | 903<br>I  | K<br>I | 3    | Т     | 6<br> | C<br>I             | TR |

| Product class STM8 microcontroller                                                                                                                                                   |                 |         |           |        |      |       |       |                    |    |

| Family type<br>S = Standard                                                                                                                                                          |                 |         |           |        |      |       |       |                    |    |

| Sub-family type<br>903 = 903 sub-family                                                                                                                                              |                 |         |           |        |      |       |       |                    |    |

| Pin count<br>K = 32 pins<br>F= 20 pins                                                                                                                                               |                 |         |           |        |      |       |       |                    |    |

| Program memory size<br>3 = 8 Kbytes                                                                                                                                                  |                 |         |           |        |      |       |       |                    |    |

| Package type $B = SDIP$ $T = LQFP$ $U = VFQFPN$ $P = TSSOP$ $M = SO$ Temperature range $3 = -40$ to $125 °C$ $6 = -40$ to $85 °C$ Package pitchBlank = 0.5 to 0.65 mm <sup>(2)</sup> |                 |         |           |        |      |       |       |                    |    |

| $C = 0.8 \text{ mm}^{(3)}$                                                                                                                                                           |                 |         |           |        |      |       |       |                    |    |

| Packing<br>No character = Tray or tube<br>TR = Tape and reel                                                                                                                         |                 |         |           |        |      |       |       |                    |    |

| 1 A dedicated ordering information scheme :                                                                                                                                          | will be release | ad if i | - 41 5-14 |        |      |       | ~~~~~ |                    |    |

A dedicated ordering information scheme will be released if, in the future, memory programming service (FastROM) is required The letter "P" will be added after STM8S. Three unique letters identifying the customer application code will also be visible in the codification. Example: STM8SP903K3MACTR.

2. UFQFPN, TSSOP, and SO packages.

3. LQFP package.

DocID15590 Rev 11