#### STMicroelectronics - STM8S903K3U3TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 28                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 640 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s903k3u3tr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

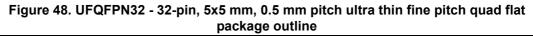

|    | 11.2  | UFQFPN32 package information                      |

|----|-------|---------------------------------------------------|

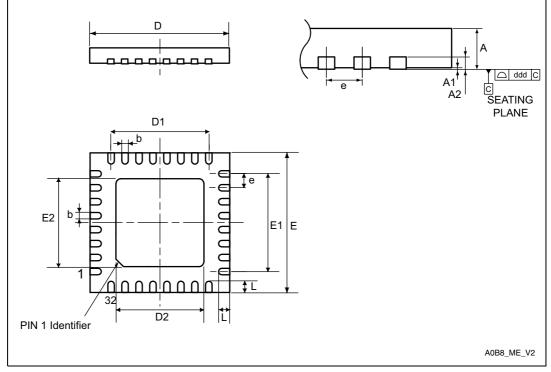

|    | 11.3  | UFQFPN20 package information                      |

|    | 11.4  | SDIP32 package information                        |

|    | 11.5  | TSSOP20 package information                       |

|    | 11.6  | SO20 package information 104                      |

|    | 11.7  | UFQFPN recommended footprint 105                  |

| 12 | Ther  | mal characteristics                               |

|    | 12.1  | Reference document                                |

|    | 12.2  | Selecting the product temperature range           |

| 13 | Orde  | ring information                                  |

|    | 13.1  | STM8S903K3/F3 FASTROM microcontroller option list |

| 14 | STM   | 3 development tools 115                           |

|    | 14.1  | Emulation and in-circuit debugging tools          |

|    |       | 14.1.1 STice key features 115                     |

|    | 14.2  | Software tools                                    |

|    |       | 14.2.1 STM8 toolset                               |

|    |       | 14.2.2 C and assembly toolchains                  |

|    | 14.3  | Programming tools                                 |

| 15 | Revis | sion history                                      |

### 4.5 Clock controller

The clock controller distributes the system clock (fMASTER) coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness.

#### Features

- Clock prescaler: to get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Master clock sources:** four different clock sources can be used to drive the master clock:

- 1-16 MHz high-speed external crystal (HSE)

- Up to 16 MHz high-speed user-external clock (HSE user-ext)

- 16 MHz high-speed internal RC oscillator (HSI)

- 128 kHz low-speed internal RC (LSI)

- **Startup clock:** After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): This feature can be enabled by software. If an HSE clock failure occurs, the internal RC (16 MHz/8) is automatically selected by the CSS and an interrupt can optionally be generated.

- **Configurable main clock output (CCO):** This outputs an external clock for use by the application.

| Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock |

|---------|---------------------|---------|---------------------|---------|---------------------|---------|---------------------|

| PCKEN17 | TIM1                | PCKEN13 | UART1               | PCKEN27 | Reserved            | PCKEN23 | ADC                 |

| PCKEN16 | TIM5                | PCKEN12 | Reserved            | PCKEN26 | Reserved            | PCKEN22 | AWU                 |

| PCKEN15 | Reserved            | PCKEN11 | SPI                 | PCKEN25 | Reserved            | PCKEN21 | Reserved            |

| PCKEN14 | TIM6                | PCKEN10 | 12C                 | PCKEN24 | Reserved            | PCKEN20 | Reserved            |

Table 2. Peripheral clock gating bit assignments in CLK\_PCKENR1/2 registers

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (fCPU/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (fCPU/16)

#### LIN master mode

- Emission: Generates 13-bit synch. break frame

- Reception: Detects 11-bit break frame

#### 4.14.2 SPI

- Maximum speed: 8 Mbit/s (fMASTER/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave/master selection input pin

# 4.14.3 I<sup>2</sup>C

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I2C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz)

- Fast speed (up to 400 kHz)

|         |                 | Table 5. 1550F20/5020/0FQFFN20 pill descriptions (continued) |      |          |       |      |                          |       |      |    |                                |                                                                         |                                                            |

|---------|-----------------|--------------------------------------------------------------|------|----------|-------|------|--------------------------|-------|------|----|--------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------|

|         | 0               | 0                                                            |      |          | Input | t    |                          | Ou    | tput |    | ç o                            | nate                                                                    | ~ 운포                                                       |

| TSSOP20 | <b>UFQFPN20</b> | Pin name                                                     | Type | floating | ndw   | Ext. | High sink <sup>(1)</sup> | Speed | ao   | dd | Main function<br>(after reset) | Default alternate<br>function                                           | Alternate<br>function<br>after remap<br>[option bit]       |

| 19      | 16              | PD2/AIN3/<br>[TIM5_CH3]                                      | I/O  | x        | х     | х    | HS                       | O3    | х    | х  | Port<br>D2                     | -                                                                       | Analog input 3<br>[AFR2] Timer<br>52 - channel 3<br>[AFR1] |

| 20      | 17              | PD3/ AIN4/<br>TIM5_CH2/<br>ADC_ETR                           | I/O  | x        | x     | x    | HS                       | O3    | x    | x  | Port<br>D3                     | Analog input<br>4 Timer 52 -<br>channel<br>2/ADC<br>external<br>trigger | -                                                          |

| 1       | 18              | PD4/ TIM5_CH1/<br>BEEP<br>[UART1_CK]                         | I/O  | x        | х     | х    | HS                       | O3    | х    | х  | Port<br>D4                     | Timer 5 -<br>channel<br>1/BEEP<br>output                                | UART clock<br>[AFR2]                                       |

| 2       | 19              | PD5/ AIN5/<br>UART1_TX                                       | I/O  | x        | х     | х    | HS                       | O3    | х    | х  | Port<br>D5                     | Analog input<br>5/ UART1<br>data transmit                               | -                                                          |

| 3       | 20              | PD6/ AIN6/<br>UART1_RX                                       | I/O  | x        | х     | х    | HS                       | O3    | х    | х  | Port<br>D6                     | Analog input<br>6/ UART1<br>data receive                                | -                                                          |

| Table 5. 1350F20/3020/0FQFFN20 pill descriptions (continued) | Table 5 | . TSSOP20/SO20/UFQFPN20 | pin descri | ptions | (continued) |

|--------------------------------------------------------------|---------|-------------------------|------------|--------|-------------|

|--------------------------------------------------------------|---------|-------------------------|------------|--------|-------------|

1. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package. In addition, the total driven current must respect the absolute maximum ratings (see *Section 10.2: Absolute maximum ratings*).

2. When the MCU is in Halt/Active-halt mode, PA1 is automatically configured in input weak pull-up and cannot be used for waking up the device. In this mode, the output state of PA1 is not driven. It is recommended to use PA1 only in input mode if Halt/Active-halt is used in the application.

3. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to VDD are not implemented)

4. The PD1 pin is in input pull-up during the reset phase and after internal reset release.

| Address                | Block | Register label           | Register name                           | Reset status |  |  |  |

|------------------------|-------|--------------------------|-----------------------------------------|--------------|--|--|--|

| 0x00 526A              |       | TIM1_CCR3L               | TIM1 capture/compare<br>register 3 low  | 0x00         |  |  |  |

| 0x00 526B              |       | TIM1_CCR4H               | TIM1 capture/compare<br>register 4 high | 0x00         |  |  |  |

| 0x00 526C              | TIM1  | TIM1_CCR4L               | TIM1 capture/compare<br>register 4 low  | 0x00         |  |  |  |

| 0x00 526D              |       | TIM1_BKR                 | TIM1 break register                     | 0x00         |  |  |  |

| 0x00 526E              |       | TIM1_DTR                 | TIM1 dead-time register                 | 0x00         |  |  |  |

| 0x00 526F              |       | TIM1_OISR                | TIM1 output idle state register         | 0x00         |  |  |  |

| 0x00 5270 to 0x00 52FF |       | Reserved area (147 byte) |                                         |              |  |  |  |

#### Table 8. General hardware register map (continued)

| Address Plack Perioter label Perioter roma Post status |                |                |                                           |              |  |  |

|--------------------------------------------------------|----------------|----------------|-------------------------------------------|--------------|--|--|

| Address                                                | Block          | Register label | Register name                             | Reset status |  |  |

| 0x00 5400                                              |                | ADC_CSR        | ADC control/status register               | 0x00         |  |  |

| 0x00 5401                                              |                | ADC_CR1        | ADC configuration register 1              | 0x00         |  |  |

| 0x00 5402                                              |                | ADC_CR2        | ADC configuration register 2              | 0x00         |  |  |

| 0x00 5403                                              |                | ADC_CR3        | ADC configuration register 3              | 0x00         |  |  |

| 0x00 5404                                              |                | ADC_DRH        | ADC data register high                    | 0xXX         |  |  |

| 0x00 5405                                              |                | ADC_DRL        | ADC data register low                     | 0xXX         |  |  |

| 0x00 5406                                              |                | ADC_TDRH       | ADC Schmitt trigger disable register high | 0x00         |  |  |

| 0x00 5407                                              | ADC1<br>cont'd | ADC_TDRL       | ADC Schmitt trigger disable register low  | 0x00         |  |  |

| 0x00 5408                                              |                | ADC_HTRH       | ADC high threshold register<br>high       | 0x03         |  |  |

| 0x00 5409                                              |                | ADC_HTRL       | ADC high threshold register low           | 0xFF         |  |  |

| 0x00 540A                                              |                | ADC_LTRH       | ADC low threshold register<br>high        | 0x00         |  |  |

| 0x00 540B                                              |                | ADC_LTRL       | ADC low threshold register low            | 0x00         |  |  |

| 0x00 540C                                              |                | ADC_AWSRH      | ADC analog watchdog status register high  | 0x00         |  |  |

| 0x00 540D                                              |                | ADC_AWSRL      | ADC analog watchdog status register low   | 0x00         |  |  |

| 0x00 540E                                              |                | ADC _AWCRH     | ADC analog watchdog control register high | 0x00         |  |  |

| 0x00 540F                                              |                | ADC_AWCRL      | ADC analog watchdog control register low  | 0x00         |  |  |

| 0x00 5410 to 0x00 57FF                                 |                | Reserv         | ved area (1008 byte)                      |              |  |  |

Table 8. General hardware register map (continued)

1. Depends on the previous reset source.

2. Write-only register.

# 7 Interrupt vector mapping

| IRQ no. Source block |          | Description                                               | Wakeup from<br>halt mode | Wakeup from active-halt mode | Vector address |

|----------------------|----------|-----------------------------------------------------------|--------------------------|------------------------------|----------------|

| -                    | RESET    | Reset                                                     | Yes                      | Yes                          | 0x00 8000      |

| -                    | TRAP     | Software interrupt                                        | -                        | -                            | 0x00 8004      |

| 0                    | TLI      | External top level<br>interrupt                           | -                        | -                            | 0x00 8008      |

| 1                    | AWU      | Auto wake up from halt                                    | -                        | Yes                          | 0x00 800C      |

| 2                    | CLK      | Clock controller                                          | -                        | -                            | 0x00 8010      |

| 3                    | EXTI0    | Port A external<br>interrupts                             | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>           | 0x00 8014      |

| 4                    | EXTI1    | Port B external<br>interrupts                             | Yes                      | Yes                          | 0x00 8018      |

| 5                    | EXTI2    | Port C external<br>interrupts                             | Yes                      | Yes                          | 0x00 801C      |

| 6                    | EXTI3    | Port D external<br>interrupts                             | Yes                      | Yes                          | 0x00 8020      |

| 7                    | EXTI4    | Port E external<br>interrupts                             | Yes                      | Yes                          | 0x00 8024      |

| 8                    | EXTI5    | Port F external<br>interrupts                             | -                        | -                            | 0x00 8028      |

| 9                    | Reserved | -                                                         | -                        | -                            | 0x00 802C      |

| 10                   | SPI      | End of transfer                                           | Yes                      | Yes                          | 0x00 8030      |

| 11                   | TIM1     | TIM1 update/<br>overflow/<br>underflow/ trigger/<br>break | -                        | -                            | 0x00 8034      |

| 12                   | TIM1     | TIM1 capture/<br>compare                                  | -                        | -                            | 0x00 8038      |

| 13                   | TIM5     | TIM5 update/<br>overflow/trigger                          | -                        | -                            | 0x00 803C      |

| 14                   | TIM5     | TIM5 capture/<br>compare                                  | -                        | -                            | 0x00 8040      |

| 15                   | Reserved | -                                                         | -                        | -                            | 0x00 8044      |

| 16                   | Reserved | -                                                         | -                        | -                            | 0x00 8048      |

| 17                   | UART1    | Tx complete                                               | -                        | -                            | 0x00 804C      |

| 18                   | UART1    | Receive register<br>DATA FULL                             | _                        | -                            | 0x00 8050      |

| 19                   | I2C      | I2C interrupt                                             | Yes                      | Yes                          | 0x00 8054      |

#### Table 10. Interrupt mapping

| Option byte no. | Description                                                  |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------|--|--|--|--|--|--|

|                 | EXTCLK: External clock selection                             |  |  |  |  |  |  |

|                 | 0: External crystal connected to OSCIN/OSCOUT                |  |  |  |  |  |  |

|                 | 1: External clock signal on OSCIN                            |  |  |  |  |  |  |

|                 | CKAWUSEL: Auto wake-up unit/clock                            |  |  |  |  |  |  |

| OPT4            | 0: LSI clock source selected for AWU                         |  |  |  |  |  |  |

| OF14            | 1: HSE clock with prescaler selected as clock source for AWU |  |  |  |  |  |  |

|                 | PRSC[1:0] AWU clock prescaler                                |  |  |  |  |  |  |

|                 | 0x: 16 MHz to 128 kHz prescaler                              |  |  |  |  |  |  |

|                 | 10: 8 MHz to 128 kHz prescaler                               |  |  |  |  |  |  |

|                 | 11: 4 MHz to 128 kHz prescaler                               |  |  |  |  |  |  |

|                 | HSECNT[7:0]: HSE crystal oscillator stabilization time       |  |  |  |  |  |  |

|                 | 0x00: 2048 HSE cycles                                        |  |  |  |  |  |  |

| OPT5            | 0xB4: 128 HSE cycles                                         |  |  |  |  |  |  |

|                 | 0xD2: 8 HSE cycles                                           |  |  |  |  |  |  |

|                 | 0xE1: 0.5 HSE cycles                                         |  |  |  |  |  |  |

# 8.1 Alternate function remapping bits

#### Table 13. STM8S903K3 alternate function remapping bits [7:2] for 32-pin packages

| Option byte no. | Description <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT2            | <ul> <li>AFR7 Alternate function remapping option 7</li> <li>0: AFR7 remapping option inactive: Default alternate functions.<sup>(2)</sup></li> <li>1: Port C3 alternate function = TIM1_CH1N;<br/>port C4 alternate function = TIM1_CH2N.</li> <li>AFR6 Alternate function remapping option 6</li> <li>0: AFR6 remapping option inactive: Default alternate function.<sup>(2)</sup></li> <li>1: Port D7 alternate function = TIM1_CH4.</li> <li>AFR5 Alternate function remapping option 5</li> <li>0: AFR5 remapping option inactive: Default alternate function.<sup>(2)</sup></li> <li>1: Port D0 alternate function = CLK_CCO.</li> <li>AFR4 Alternate function remapping option 4</li> <li>0: AFR4 remapping option inactive: Default alternate functions.<sup>(2)</sup></li> <li>1: Port B4 alternate function = ADC_ETR;<br/>port B5 alternate function = TIM1_BKIN.</li> <li>AFR3 Alternate function = TIM1_BKIN.</li> <li>AFR3 Alternate function = TLI.</li> <li>AFR2 Alternate function = TLI.</li> <li>AFR2 Alternate function = AIN2; port D2 alternate functions.<sup>(2)</sup></li> <li>1: Port C4 alternate function = AIN2; port D2 alternate function = AIN3; port D4 alternate function = UART1 CK</li> </ul> |

1. Do not use more than one remapping option in the same port.

|                                          | · · · · · · · · · · · · · · · · · · ·                                   |     |    |  |  |

|------------------------------------------|-------------------------------------------------------------------------|-----|----|--|--|

| Symbol                                   | Symbol Ratings                                                          |     |    |  |  |

|                                          | Injected current on NRST pin                                            | ±4  |    |  |  |

| I <sub>INJ(PIN)</sub> <sup>(3) (4)</sup> | Injected current on OSCIN pin                                           | ±4  | mA |  |  |

|                                          | Injected current on any other pin <sup>(5)</sup>                        | ±4  | ma |  |  |

| $\Sigma I_{INJ(PIN)}^{(3)}$              | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ±20 |    |  |  |

Table 19. Current characteristics (continued)

1. Guaranteed by characterization results.

- 2. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external supply.

- 3. I<sub>INJ(PIN)</sub> must never be exceeded. This condition is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true opendrain pads, there is no positive injection current allowed and the corresponding V<sub>IN</sub> maximum must always be respected.

- 4. ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for IINJ(PIN) and ΣI<sub>INJ(PIN)</sub> in the I/O port pin characteristics section does not affect the ADC accuracy.

- 5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

| Symbol           | Ratings                      | Value      | Unit |

|------------------|------------------------------|------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| TJ               | Maximum junction temperature | 150        | C    |

# 10.3 Operating conditions

| Symbol                             | Parameter                                                   | Conditions                | Min  | Max  | Unit |

|------------------------------------|-------------------------------------------------------------|---------------------------|------|------|------|

| f <sub>CPU</sub>                   | Internal CPU clock frequency                                | -                         | 0    | 16   | MHz  |

| V <sub>DD/</sub> V <sub>DDIO</sub> | Standard operating voltage                                  | -                         | 2.95 | 5.5  | V    |

|                                    | C <sub>EXT</sub> : capacitance of external capacitor        | -                         | 470  | 3300 | nF   |

| V <sub>CAP</sub> <sup>(1)</sup>    | ESR of external capacitor                                   | – at 1 MHz <sup>(2)</sup> | -    | 0.3  | Ω    |

|                                    | ESL of external capacitor                                   |                           | -    | 15   | nH   |

|                                    | Power dissipation<br>at T <sub>A</sub> = 85 °C for suffix 6 | TSSOP20                   | -    | 182  |      |

|                                    |                                                             | SO20W                     | -    | 1000 |      |

| P <sub>D</sub> <sup>(3)</sup>      |                                                             | UFQFPN20                  | -    | 198  | m)// |

| PD                                 |                                                             | LQFP32                    | -    | 333  | mW   |

|                                    |                                                             | UFQFPN32                  | -    | 526  |      |

|                                    |                                                             | SDIP32                    | -    | 333  |      |

DocID15590 Rev 11

### 10.3.5 Memory characteristics

#### RAM and hardware registers

#### Table 38. RAM and hardware registers

| Symbol   | Parameter                          | Conditions           | Min                                | Unit |

|----------|------------------------------------|----------------------|------------------------------------|------|

| $V_{RM}$ | Data retention mode <sup>(1)</sup> | Halt mode (or reset) | V <sub>IT-max</sub> <sup>(2)</sup> | V    |

1. Minimum supply voltage without losing data stored in RAM (in halt mode or under reset) or in hardware registers (only in halt mode). Guaranteed by design, not tested in production.

2. Refer to Section 10.3: Operating conditions for the value of VIT-max.

#### Flash program memory/data EEPROM memory

| Symbol             | Parameter                                                                                              | Conditions                | Min <sup>(1)</sup> | Тур | Max  | Unit      |  |

|--------------------|--------------------------------------------------------------------------------------------------------|---------------------------|--------------------|-----|------|-----------|--|

| V <sub>DD</sub>    | Operating voltage<br>(all modes, execution/write/erase)                                                | f <sub>CPU</sub> ≤ 16 MHz | 2.95               | -   | 5.5  | V         |  |

| t <sub>prog</sub>  | Standard programming time (including<br>erase) for byte/word/block<br>(1 byte/4 byte/64 byte)          | -                         | -                  | 6   | 6.6  | ms        |  |

| prog               | Fast programming time for 1 block (64 byte)                                                            | -                         | -                  | 3   | 3.33 |           |  |

| t <sub>erase</sub> | Erase time for 1 block (64 byte)                                                                       | -                         | -                  | 3   | 3.33 |           |  |

| +                  | Data retention (program and data<br>memory) after 10k erase/write cycles<br>at T <sub>A</sub> = +55 °C | T <sub>RET</sub> = 55 °C  | 20                 | -   | -    | -<br>year |  |

| t <sub>RET</sub>   | Data retention (data memory) after<br>300k erase/write cycles at<br>T <sub>A</sub> = +125°C            | T <sub>RET</sub> = 85 °C  | 1                  | -   | -    |           |  |

| I <sub>DD</sub>    | Supply current (Flash programming or erasing for 1 to 128 byte)                                        | -                         | -                  | 2   | -    | mA        |  |

#### Table 39. Flash program memory/data EEPROM memory

1. Guaranteed by characterization results.

### 10.3.6 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage, using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                                      | Parameter                                       | Conditions                                  | Min                   | Тур | Max                     | Unit |

|---------------------------------------------|-------------------------------------------------|---------------------------------------------|-----------------------|-----|-------------------------|------|

| V <sub>IL</sub>                             | Input low level voltage                         |                                             | -0.3 V                | -   | 0.3 x V <sub>DD</sub>   | V    |

| V <sub>IH</sub>                             | Input high level voltage                        | V <sub>DD</sub> = 5 V                       | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 V | v    |

| V <sub>hys</sub>                            | Hysteresis <sup>(1)</sup>                       |                                             | -                     | 700 | -                       | mV   |

| R <sub>pu</sub>                             | Pull-up resistor                                | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$         | 30                    | 55  | 80                      | kΩ   |

|                                             | Rise and fall time<br>Fast I/Os<br>Load = 50 pF |                                             | -                     | -   | 35 <sup>(2)</sup>       | 20   |

| <sup>t</sup> R <sup>, t</sup> F (10% - 90%) |                                                 | Standard and high sink I/Os<br>Load = 50 pF | -                     | -   | 125 <sup>(2)</sup>      | ns   |

|                                             | Rise and fall time                              | Fast I/Os<br>Load = 20 pF                   | -                     | -   | 20 <sup>(2)</sup>       | 20   |

| t <sub>R</sub> , t <sub>F</sub>             | (10% - 90%)                                     | Standard and high sink I/Os<br>Load = 20 pF | -                     | -   | 50 <sup>(2)</sup>       | ns   |

| I <sub>lkg</sub>                            | Digital input leakage current                   | $V_{SS} \leq V_{IN} \leq V_{DD}$            | -                     | -   | ±1 <sup>(3)</sup>       | μA   |

| I <sub>lkg ana</sub>                        | Analog input leakage current                    | $V_{SS} \le V_{IN} \le V_{DD}$              | -                     | -   | ±250 <sup>(3)</sup>     | nA   |

| l <sub>lkg(inj)</sub>                       | Leakage current in<br>adjacent I/O              | Injection current ±4 mA                     | -                     | -   | ±1 <sup>(3)</sup>       | μA   |

1. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

2. Data guaranteed by design.

3. Guaranteed by characterization results

| Symbol                                                                              | Parameter                    | Conditions <sup>(1)</sup>         | Min                      | Мах                      | Unit |

|-------------------------------------------------------------------------------------|------------------------------|-----------------------------------|--------------------------|--------------------------|------|

| t <sub>r(SCK</sub> )<br>t <sub>f(SCK)</sub>                                         | SPI clock rise and fall time | Capacitive load:<br>C = 30 pF     | -                        | 25                       |      |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                                                 | NSS setup time               | Slave mode                        | 4 * t <sub>MASTER</sub>  | -                        |      |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                                                  | NSS hold time                | Slave mode                        | 70                       | -                        |      |

| $ \begin{array}{c} t_{w(SCKH)}^{(2)} \\ t_{w(SCKL)}^{(2)} \end{array} \end{array} $ | SCK high and low time        | Master mode                       | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |      |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                                  | Data input setup time        | Master mode                       | 5                        | -                        |      |

| t <sub>su(MI)</sub> <sup>(2)</sup><br>t <sub>su(SI)</sub> <sup>(2)</sup>            | Data input setup time        | Slave mode                        | 5                        | -                        |      |

| $t_{h(MI)}^{(2)}$                                                                   | Data input hold time         | Master mode                       | 7                        | -                        |      |

| t <sub>h(MI)</sub> <sup>(2)</sup><br>t <sub>h(SI)</sub> <sup>(2)</sup>              | Data input hold time         | Slave mode                        | 10                       | -                        | ns   |

| t <sub>a(SO)</sub> <sup>(2)(3)</sup>                                                | Data output access time      | Slave mode                        | -                        | 3* t <sub>MASTER</sub>   |      |

| $t_{dis(SO)}^{(2)(4)}$                                                              | Data output disable time     | Slave mode                        | 25                       | -                        |      |

| t <sub>v(SO)</sub> <sup>(2)</sup>                                                   | Data output valid time       | Slave mode<br>(after enable edge) | -                        | 65                       |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                                   | Data output valid time       | Master mode (after enable edge)   | -                        | 30                       |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                                   | Data output hold time        | Slave mode (after<br>enable edge) | 27                       | -                        |      |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                                   | Data output hold time        | Master mode (after enable edge)   | 11                       | -                        |      |

Table 45. SPI characteristics (continued)

1. Parameters are given by selecting 10 MHz I/O output frequency.

2. Values based on design simulation and/or characterization results, and not tested in production.

3. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

4. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

| Symbol         | Parameter                                   | Conditions               | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|--------------------------|-----|--------------------|------|

|                |                                             | f <sub>ADC</sub> = 2 MHz | 1.6 | 3.5                |      |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 4 MHz | 2.2 | 4                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 2.4 | 4.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz | 1.1 | 2.5                |      |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 4 MHz | 1.5 | 3                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 1.8 | 3                  |      |

|                | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz | 1.5 | 3                  |      |

| E <sub>G</sub> |                                             | f <sub>ADC</sub> = 4 MHz | 2.1 | 3                  | LSB  |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 2.2 | 4                  |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz | 0.7 | 1.5                |      |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 4 MHz | 0.7 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 0.7 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz | 0.6 | 1.5                |      |

| E <sub>L</sub> | Integral linearity error <sup>(2)</sup>     | f <sub>ADC</sub> = 4 MHz | 0.8 | 2                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 0.8 | 2                  |      |

| Table 48. ADC | accuracy | with R <sub>AIN</sub> < | : <b>10 k</b> Ω, | $V_{DD} = 5 V$ |

|---------------|----------|-------------------------|------------------|----------------|

|---------------|----------|-------------------------|------------------|----------------|

1. Guaranteed by characterization results.

ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 10.3.6 does not affect the ADC accuracy.

| Symbol                                       | Parameter                                                    | Conditions               | Тур | Max <sup>(1)</sup> | Unit |

|----------------------------------------------|--------------------------------------------------------------|--------------------------|-----|--------------------|------|

|                                              | Total unadjusted error <sup>(2)</sup>                        | f <sub>ADC</sub> = 2 MHz | 1.6 | 3.5                |      |

| E <sub>T</sub>                               |                                                              | f <sub>ADC</sub> = 4 MHz | 1.9 | 4                  |      |

| E <sub>O</sub>   Offset error <sup>(2)</sup> | f <sub>ADC</sub> = 2 MHz                                     | 1                        | 2.5 |                    |      |

|                                              |                                                              | f <sub>ADC</sub> = 4 MHz | 1.5 | 2.5                |      |

|                                              | Gain error <sup>(2)</sup>                                    | f <sub>ADC</sub> = 2 MHz | 1.3 | 3                  | LSB  |

| E <sub>G</sub>                               |                                                              | f <sub>ADC</sub> = 4 MHz | 2   | 3                  | LOD  |

|                                              | Differential linearity error <sup>(2)</sup>                  | f <sub>ADC</sub> = 2 MHz | 0.7 | 1.0                |      |

| I⊏DI                                         | E <sub>D</sub>   Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 4 MHz | 0.7 | 1.5                |      |

|                                              | Integral linearity error <sup>(2)</sup>                      | f <sub>ADC</sub> = 2 MHz | 0.6 | 1.5                | Ī    |

| E <sub>L</sub>                               |                                                              | f <sub>ADC</sub> = 4 MHz | 0.8 | 2                  |      |

Guaranteed by characterization results. 1.

ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another 2. analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 10.3.6 does not affect the ADC accuracy.

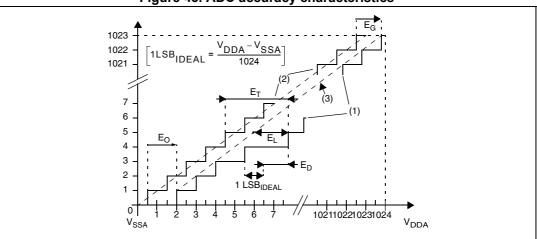

#### Figure 43. ADC accuracy characteristics

- 1. Example of an actual transfer curve

- The ideal transfer curve 2.

- End point correlation line 3.

$E_T$  = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.  $E_O$  = Offset error: deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: deviation between the last ideal transition and the last actual one.

$E_D = Differential linearity error: maximum deviation between any actual steps and the ideal one.$  $<math>E_L = Integral linearity error: maximum deviation between any actual transition and the end point correlation$ line.

# 11.2 UFQFPN32 package information

1. Drawing is not to scale.

- 2. All leads/pads should be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this backside pad to PCB ground.

- 4. Dimensions are in millimeters.

# 11.3 UFQFPN20 package information

1. Drawing is not to scale.

# Table 56. UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

| Dim. | mm    |       |       | inches <sup>(1)</sup> |        |        |

|------|-------|-------|-------|-----------------------|--------|--------|

|      | Min   | Тур   | Max   | Min                   | Тур    | Max    |

| A    | 0.500 | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1   | 0.000 | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| A3   | -     | 0.152 | -     | -                     | 0.060  | -      |

| D    | 2.900 | 3.000 | 3.100 | 0.1142                | 0.1181 | 0.1220 |

| E    | 2.900 | 3.000 | 3.100 | 0.1142                | 0.1181 | 0.1220 |

| L1   | 0.500 | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| L2   | 0.300 | 0.350 | 0.400 | 0.0118                | 0.0138 | 0.0157 |

| Table 07. Obn 02 package mechanical data (continued) |       |       |        |                       |        |        |

|------------------------------------------------------|-------|-------|--------|-----------------------|--------|--------|

| Dim.                                                 | mm    |       |        | inches <sup>(1)</sup> |        |        |

|                                                      | Min   | Тур   | Max    | Min                   | Тур    | Max    |

| eB                                                   | -     | -     | 12.700 | -                     | -      | 0.5000 |

| L                                                    | 2.540 | 3.048 | 3.810  | 0.1000                | 0.1200 | 0.1500 |

Table 57. SDIP32 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits

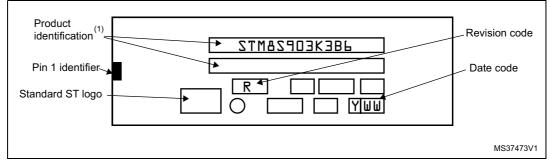

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 55. SDIP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

### **OPT4** watchdog

| PRSC<br>(check only one option) | [] for 16 MHz to 128 kHz prescaler<br>[] for 8 MHz to 128 kHz prescaler<br>[] for 4 MHz to 128 kHz prescaler |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|

| CKAWUSEL                        | [] LSI clock source selected for AWU                                                                         |

| (check only one option)         | [] HSE clock with prescaler selected as clock source for AWU                                                 |

| EXTCLK                          | [] External crystal connected to OSCIN/OSCOUT                                                                |

| (check only one option)         | [] External signal on OSCIN                                                                                  |

# OPT5 crystal oscillator stabilization HSECNT (check only one option)

[] 2048 HSE cycles

[] 128 HSE cycles

[] 8 HSE cycles

[] 0.5 HSE cycles

### **OTP6** is reserved

| Comments:                                  |  |

|--------------------------------------------|--|

| Supply operating range in the application: |  |

| Notes:                                     |  |

# 14.3 **Programming tools**

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the application board via the SWIM protocol. Additional tools include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for the STM8 programming.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.