Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | R32C/100                                                                        |

| Core Size                  | 16/32-Bit                                                                       |

| Speed                      | 50MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IEBus, UART/USART                            |

| Peripherals                | DMA, LVD, PWM, WDT                                                              |

| Number of I/O              | 84                                                                              |

| Program Memory Size        | 1MB (1M x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 8K x 8                                                                          |

| RAM Size                   | 63K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LFQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f64179dfb-ub |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Unit                                  | Function                              | Explanation                                                                                                                                                                                                                   |  |  |

|---------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Timer                                 | Timer A                               | 16-bit timer × 5<br>Timer mode, event counter mode, one-shot timer mode, pulse-width<br>modulation (PWM) mode<br>Two-phase pulse signal processing in event counter mode (two-<br>phase encoder input) × 3                    |  |  |

|                                       | Timer B                               | 16-bit timer × 6<br>Timer mode, event counter mode, pulse frequency measurement<br>mode, pulse-width measurement mode                                                                                                         |  |  |

|                                       | Three-phase<br>motor control<br>timer | Three-phase motor control timer × 1 (timers A1, A2, A4, and B2 used)<br>8-bit programmable dead time timer                                                                                                                    |  |  |

| Serial UART0 to UART8<br>Interface    |                                       | Asynchronous/synchronous serial interface × 9 channels<br>• I <sup>2</sup> C-bus (UART0 to UART6)<br>• Special mode 2 (UART0 to UART6)<br>• IEBus (optional <sup>(1)</sup> ) (UART0 to UART6)                                 |  |  |

| A/D Converter                         |                                       | 10-bit resolution × 26 channels<br>Sample and hold functionality integrated                                                                                                                                                   |  |  |

| D/A Converter                         |                                       | 8-bit resolution × 2                                                                                                                                                                                                          |  |  |

| CRC Calculato                         | r                                     | CRC-CCITT (X <sup>16</sup> + X <sup>12</sup> + X <sup>5</sup> + 1)                                                                                                                                                            |  |  |

| X-Y Converter                         |                                       | 16 bits × 16 bits                                                                                                                                                                                                             |  |  |

| Intelligent I/O                       |                                       | Time measurement (input capture): 16 bits × 16<br>Waveform generation (output compare): 16 bits × 19<br>Serial interface: Variable-length synchronous serial I/O mode, IEBus<br>mode (optional <sup>(1)</sup> )               |  |  |

| Multi-master I <sup>2</sup>           | C-bus Interface                       | 1 channel                                                                                                                                                                                                                     |  |  |

| CAN Module                            |                                       | 1 channel<br>CAN functionality compliant with ISO 11898-1<br>32 mailboxes                                                                                                                                                     |  |  |

| Flash Memory                          |                                       | Programming and erasure supply voltage: VCC = 3.0 to 5.5 V<br>Minimum endurance: 1,000 program/erase cycles<br>Security protection: ROM code protect, ID code protect<br>Debugging: On-chip debug, on-board flash programming |  |  |

| Operating Frequency/Supply<br>Voltage |                                       | 64 MHz (high speed version)/VCC = 3.0 to 5.5 V<br>50 MHz (normal speed version)/VCC = 3.0 to 5.5 V                                                                                                                            |  |  |

| Operating Temperature                 |                                       | -20°C to 85°C (N version)<br>-40°C to 85°C (D version)<br>-40°C to 85°C (P version)                                                                                                                                           |  |  |

| Current Consumption                   |                                       | 45 mA (VCC = 5.0 V, f(CPU) = 64 MHz)<br>35 mA (VCC = 5.0 V, f(CPU) = 50 MHz)<br>8 μA (VCC = 3.3 V, f(XCIN) = 32.768 kHz, in wait mode)                                                                                        |  |  |

| Package                               |                                       | 100-pin plastic molded LQFP (PLQP0100KB-A)                                                                                                                                                                                    |  |  |

#### Table 1.4 Performance Overview for the 100-pin Package (2/2)

Note:

1. Contact a Renesas Electronics sales office to use the optional features.

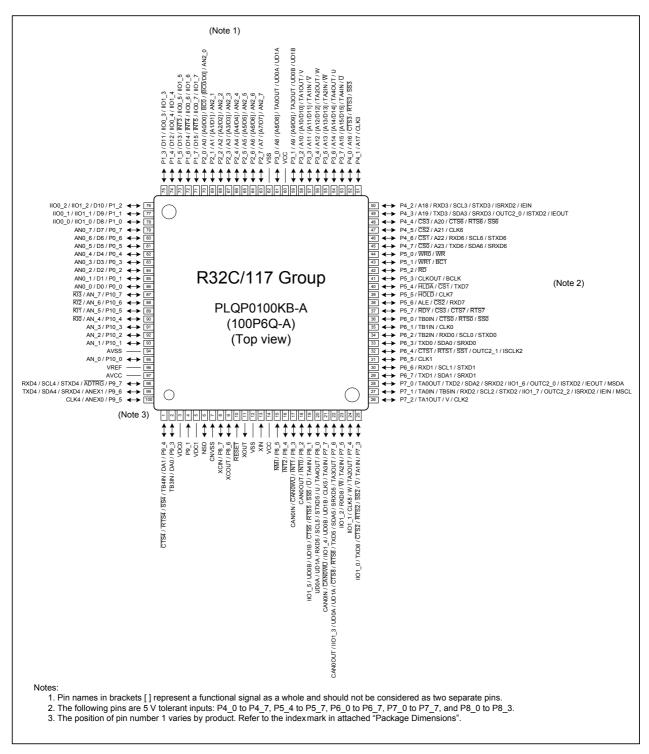

Figure 1.4 Pin Assignment for the 100-pin Package (top view)

|                        | Package      |              | Selectable Functions            |                                     |                                   |

|------------------------|--------------|--------------|---------------------------------|-------------------------------------|-----------------------------------|

| Pin Names              | 144-<br>pin  | 100-<br>pin  | Pull-up resistor <sup>(1)</sup> | N-channel open drain <sup>(2)</sup> | 5 V Tolerant Input <sup>(3)</sup> |

| P0_0 to P0_7           | $\checkmark$ | $\checkmark$ | $\checkmark$                    |                                     |                                   |

| P1_0 to P1_7           | $\checkmark$ | $\checkmark$ | $\checkmark$                    |                                     |                                   |

| P2_0 to P2_7           | $\checkmark$ | $\checkmark$ | $\checkmark$                    |                                     |                                   |

| P3_0 to P3_7           | $\checkmark$ | $\checkmark$ | $\checkmark$                    |                                     |                                   |

| P4_0 to P4_7           | $\checkmark$ | $\checkmark$ |                                 | $\checkmark$                        | $\checkmark$                      |

| P5_0 to P5_3           | $\checkmark$ | $\checkmark$ | $\checkmark$                    |                                     |                                   |

| P5_4 to P5_7           | $\checkmark$ | $\checkmark$ |                                 | $\checkmark$                        | $\checkmark$                      |

| P6_0 to P6_7           | $\checkmark$ | $\checkmark$ |                                 | $\checkmark$                        | $\checkmark$                      |

| P7_0 to P7_7           | $\checkmark$ | $\checkmark$ |                                 | $\checkmark$                        | $\checkmark$                      |

| P8_0 to P8_3           | $\checkmark$ | $\checkmark$ |                                 | $\checkmark$                        | $\checkmark$                      |

| P8_4, P8_6, P8_7       | $\checkmark$ | $\checkmark$ | $\checkmark$                    |                                     |                                   |

| P9_0 to P9_3 (144-pin) | $\checkmark$ |              | $\checkmark$                    | $\checkmark$                        |                                   |

| P9_1, P9_3 (100-pin)   |              | $\checkmark$ | $\checkmark$                    |                                     |                                   |

| P9_4 to P9_7           | $\checkmark$ | $\checkmark$ | $\checkmark$                    | $\checkmark$                        |                                   |

| P10_0 to P10_7         | $\checkmark$ | $\checkmark$ | $\checkmark$                    |                                     |                                   |

| P11_0 to P11_3         | $\checkmark$ |              | $\checkmark$                    | $\checkmark$                        |                                   |

| P11_4                  | $\checkmark$ |              | $\checkmark$                    |                                     |                                   |

| P12_0 to P12_3         | $\checkmark$ |              | $\checkmark$                    | $\checkmark$                        |                                   |

| P12_4 to P12_7         | $\checkmark$ |              | $\checkmark$                    |                                     |                                   |

| P13_0 to P13_7         | $\checkmark$ |              | $\checkmark$                    |                                     |                                   |

| P14_1, P14_3           | $\checkmark$ |              | $\checkmark$                    |                                     |                                   |

| P14_4 to P14_6         | $\checkmark$ |              | $\checkmark$                    |                                     |                                   |

| P15_0 to P15_7         | $\checkmark$ |              | $\checkmark$                    | $\checkmark$                        |                                   |

#### Table 1.18Pin Specifications

Notes:

1. Pull-up resistors are selected for the following 4-pin units: Pi\_0 to Pi\_3 and Pi\_4 to Pi\_7 (i = 0 to 15); however, they are enabled only for the input pins.

2. N-channel open drain output can be enabled on the applicable pins on a discrete pin basis.

3. 5 V tolerant input is enabled when an applicable pin is set as an input port. When it is set as an I/O port, to enable 5 V tolerant input, this pin should be set as N-channel open drain output.

## 2.1.8.5 Register Bank Select Flag (B flag)

This flag selects a register bank. It indicates 0 when register bank 0 is selected, and 1 when register bank 1 is selected.

## 2.1.8.6 Overflow Flag (O flag)

This flag becomes 1 when the result of an operation overflows; otherwise it is 0.

## 2.1.8.7 Interrupt Enable Flag (I flag)

This flag enables maskable interrupts. To disable maskable interrupts, set this flag to 0. To enable them, set this flag to 1. When an interrupt is accepted, the flag becomes 0.

## 2.1.8.8 Stack Pointer Select Flag (U flag)

To select the interrupt stack pointer (ISP), set this flag to 0. To select the user stack pointer (USP), set this flag to 1.

It becomes 0 when a hardware interrupt is accepted or when an INT instruction designated by a software interrupt number from 0 to 127 is executed.

## 2.1.8.9 Floating-point Underflow Flag (FU flag)

This flag becomes 1 when an underflow occurs in a floating-point operation; otherwise it is 0. It also becomes 1 when the operand contains invalid numbers (subnormal numbers).

## 2.1.8.10 Floating-point Overflow Flag (FO flag)

This flag becomes 1 when an overflow occurs in a floating-point operation; otherwise it is 0. It also becomes 1 when the operand contains invalid numbers (subnormal numbers).

## 2.1.8.11 Processor Interrupt Priority Level (IPL)

The processor interrupt priority level (IPL), consisting of 3 bits, selects a processor interrupt priority level from level 0 to 7. An interrupt is enabled when the interrupt request level is higher than the selected IPL.

When the processor interrupt priority level (IPL) is set to 111b (level 7), all interrupts are disabled.

### 2.1.8.12 Fixed-point Radix Point Designation Bit (DP bit)

This bit designates the radix point. It also specifies which portion of the fixed-point multiplication result to extract. It is used for the MULX instruction.

### 2.1.8.13 Floating-point Rounding Mode (RND)

The 2-bit floating-point rounding mode selects a rounding mode for floating-point calculation results.

### 2.1.8.14 Reserved

Only set this bit to 0. The read value is undefined.

| Table 4.8 S | 6FR List (8) |

|-------------|--------------|

|-------------|--------------|

| i able 4.0            | SFR LIST (0)                                            |                    |                                         |

|-----------------------|---------------------------------------------------------|--------------------|-----------------------------------------|

| Address               | Register                                                | Symbol             | Reset Value                             |

| 000170h               | Group 2 IEBus Address Register                          | IEAR               | XXXXh                                   |

| 000171h               |                                                         |                    |                                         |

| 000172h               | Group 2 IEBus Control Register                          | IECR               | 00XX X000b                              |

| 000173h               | Group 2 IEBus Transmit Interrupt Source Detect Register | IETIF              | XXX0 0000b                              |

| 000174h               | Group 2 IEBus Receive Interrupt Source Detect Register  | IERIF              | XXX0 0000b                              |

| 000175h               |                                                         |                    |                                         |

| 000176h               |                                                         |                    |                                         |

| 000177h               |                                                         |                    |                                         |

| 000178h               |                                                         |                    |                                         |

| 000179h               |                                                         |                    |                                         |

| 00017Ah               |                                                         |                    |                                         |

| 00017Bh               |                                                         |                    |                                         |

| 00017Ch               |                                                         |                    |                                         |

| 00017Dh               |                                                         |                    |                                         |

| 00017Eh               |                                                         |                    |                                         |

| 00017Eh               |                                                         |                    |                                         |

|                       | Group 0 Time Measurement/Waveform Generation Register 0 | G0TM0/G0PO0        | XXXXh                                   |

| 000181h               |                                                         |                    | 7000011                                 |

|                       | Group 0 Time Measurement/Waveform Generation Register 1 | G0TM1/G0PO1        | XXXXh                                   |

| 000183h               |                                                         |                    | 700001                                  |

|                       | Group 0 Time Measurement/Waveform Generation Register 2 | G0TM2/G0PO2        | XXXXh                                   |

| 000185h               |                                                         |                    | 700001                                  |

|                       | Group 0 Time Measurement/Waveform Generation Register 3 | G0TM3/G0PO3        | XXXXh                                   |

| 000187h               |                                                         |                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,  |

|                       | Group 0 Time Measurement/Waveform Generation Register 4 | G0TM4/G0PO4        | XXXXh                                   |

| 000189h               |                                                         |                    | 70000                                   |

|                       | Group 0 Time Measurement/Waveform Generation Register 5 | G0TM5/G0PO5        | XXXXh                                   |

| 00018Bh               |                                                         |                    | ,0000                                   |

|                       | Group 0 Time Measurement/Waveform Generation Register 6 | G0TM6/G0PO6        | XXXXh                                   |

| 00018Dh               |                                                         |                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|                       | Group 0 Time Measurement/Waveform Generation Register 7 | G0TM7/G0PO7        | XXXXh                                   |

| 00018Fh               |                                                         |                    | 70000                                   |

|                       | Group 0 Waveform Generation Control Register 0          | G0POCR0            | 0000 X000b                              |

|                       | Group 0 Waveform Generation Control Register 1          | G0POCR1            | 0X00 X000b                              |

|                       | Group 0 Waveform Generation Control Register 2          | G0POCR2            | 0X00 X000b                              |

|                       | Group 0 Waveform Generation Control Register 2          | G0POCR2            | 0X00 X000b                              |

|                       | Group 0 Waveform Generation Control Register 3          | G0POCR3<br>G0POCR4 | 0X00 X000b                              |

|                       | Group 0 Waveform Generation Control Register 5          | G0POCR4<br>G0POCR5 | 0X00 X000b                              |

|                       | Group 0 Waveform Generation Control Register 6          | G0POCR5            | 0X00 X000b                              |

|                       | Group 0 Waveform Generation Control Register 7          | G0POCR6<br>G0POCR7 | 0X00 X000b                              |

|                       | Group 0 Time Measurement Control Register 0             | G0POCR7<br>G0TMCR0 |                                         |

|                       |                                                         |                    | 00h                                     |

|                       | Group 0 Time Measurement Control Register 1             | G0TMCR1            | 00h                                     |

|                       | Group 0 Time Measurement Control Register 2             | G0TMCR2            | 00h                                     |

|                       | Group 0 Time Measurement Control Register 3             | G0TMCR3            | 00h                                     |

|                       | Group 0 Time Measurement Control Register 4             | G0TMCR4            | 00h                                     |

|                       | Group 0 Time Measurement Control Register 5             | G0TMCR5            | 00h                                     |

|                       | Group 0 Time Measurement Control Register 6             | G0TMCR6            | 00h                                     |

| 00019Fh<br>Undefine : | Group 0 Time Measurement Control Register 7             | G0TMCR7            | 00h                                     |

| Table 4.9 | SFR List (9) |

|-----------|--------------|

|-----------|--------------|

| Address     | Register                                      | Symbol           | Reset Value       |

|-------------|-----------------------------------------------|------------------|-------------------|

|             | Group 0 Base Timer Register                   | GOBT             | XXXXh             |

| 0001A01     |                                               |                  |                   |

|             | Group 0 Base Timer Control Register 0         | G0BCR0           | 0000 0000b        |

|             | Group 0 Base Timer Control Register 0         | G0BCR0<br>G0BCR1 | 0000 0000b        |

|             | Group 0 Time Measurement Prescaler Register 6 | GOTPR6           | 0000 00000<br>00h |

|             | Group 0 Time Measurement Prescaler Register 0 | G0TPR7           | 00h               |

|             | Group 0 Function Enable Register              | GOFE             | 00h               |

|             | Group 0 Function Enable Register              | GOFE             | 00h               |

| 0001A7h     |                                               | GUFS             | 0011              |

| 0001A8h     |                                               |                  |                   |

| 0001A90     |                                               |                  |                   |

|             |                                               |                  |                   |

| 0001ABh     |                                               |                  |                   |

| 0001ACh     |                                               |                  |                   |

| 0001ADh     |                                               |                  |                   |

| 0001AEh     |                                               |                  |                   |

| 0001AFh     |                                               |                  |                   |

| 0001B0h     |                                               |                  |                   |

| 0001B1h     |                                               |                  |                   |

| 0001B2h     |                                               |                  |                   |

| 0001B3h     |                                               |                  |                   |

| 0001B4h     |                                               |                  |                   |

| 0001B5h     |                                               |                  |                   |

| 0001B6h     |                                               |                  |                   |

| 0001B7h     |                                               |                  |                   |

| 0001B8h     |                                               |                  |                   |

| 0001B9h     |                                               |                  |                   |

| 0001BAh     |                                               |                  |                   |

| 0001BBh     |                                               |                  |                   |

| 0001BCh     |                                               |                  |                   |

| 0001BDh     |                                               |                  |                   |

| 0001BEh     |                                               |                  |                   |

| 0001BFh     |                                               |                  |                   |

| 0001C0h     |                                               |                  |                   |

| 0001C1h     |                                               |                  |                   |

| 0001C2h     |                                               |                  |                   |

| 0001C3h     |                                               |                  |                   |

|             | UART5 Special Mode Register 4                 | U5SMR4           | 00h               |

|             | UART5 Special Mode Register 3                 | U5SMR3           | 00h               |

|             | UART5 Special Mode Register 2                 | U5SMR2           | 00h               |

|             | UART5 Special Mode Register                   | U5SMR            | 00h               |

|             | UART5 Transmit/Receive Mode Register          | U5MR             | 00h               |

|             | UART5 Bit Rate Register                       | U5BRG            | XXh               |

|             | UART5 Transmit Buffer Register                | U5TB             | XXXXh             |

| 0001CBh     |                                               |                  |                   |

| 0001CCh     | UART5 Transmit/Receive Control Register 0     | U5C0             | 0000 1000b        |

| 0001CDh     | UART5 Transmit/Receive Control Register 1     | U5C1             | 0000 0010b        |

| 0001CEh     | UART5 Receive Buffer Register                 | U5RB             | XXXXh             |

| 0001CFh     | 1                                             |                  |                   |

| K: Undefine | d                                             |                  |                   |

|                    | ( - )                                       | •            |                           |

|--------------------|---------------------------------------------|--------------|---------------------------|

| Address            | Register                                    | Symbol       | Reset Value               |

|                    | Flash Memory Control Register 0             | FMR0         | 0X01 XX00b                |

|                    | Flash Memory Status Register 0              | FMSR0        | 1000 0000b                |

| 040002h            |                                             |              |                           |

| 040003h            |                                             |              |                           |

| 040004h            |                                             |              |                           |

| 040005h            |                                             |              |                           |

| 040006h            |                                             |              |                           |

| 040007h            |                                             |              |                           |

|                    | Flash Register Protection Unlock Register 0 | FPR0         | 00h                       |

|                    | Flash Memory Control Register 1             | FMR1         | 0000 0010b                |

|                    | Block Protect Bit Monitor Register 0        | FBPM0        | ??X? ????b <sup>(1)</sup> |

| 04000Bh            | Block Protect Bit Monitor Register 1        | FBPM1        | XXX? ????b (1)            |

| 04000Ch            |                                             |              |                           |

| 04000Dh            |                                             |              |                           |

| 04000Eh            |                                             |              |                           |

| 04000Fh            |                                             |              |                           |

| 040010h            |                                             |              |                           |

|                    | Block Protect Bit Monitor Register 2        | FBPM2        | ???? ????b <sup>(1)</sup> |

| 040012h            |                                             |              |                           |

| 040012h            |                                             |              |                           |

| 040010h            |                                             |              |                           |

| 040015h            |                                             |              |                           |

| 040016h            |                                             |              |                           |

| 040017h            |                                             |              |                           |

| 040017h<br>040018h |                                             |              |                           |

| 040018h            |                                             |              |                           |

| 040019h            |                                             |              |                           |

| 04001An<br>04001Bh |                                             |              |                           |

| 04001Bh            |                                             |              |                           |

| 04001Ch            |                                             |              |                           |

| 04001Dh<br>04001Eh |                                             |              |                           |

| 04001Eh            |                                             |              |                           |

|                    |                                             | PLC0         | 0000 0001b                |

|                    | PLL Control Register 0                      | PLC0<br>PLC1 | 0000 000 IB               |

| 040021h<br>040022h | PLL Control Register 1                      | FLUI         |                           |

|                    |                                             |              |                           |

| 040023h            |                                             |              |                           |

| 040024h            |                                             |              |                           |

| 040025h            |                                             |              |                           |

| 040026h            |                                             |              |                           |

| 040027h            |                                             |              |                           |

| 040028h            |                                             |              |                           |

| 040029h            |                                             |              |                           |

| 04002Ah            |                                             |              |                           |

| 04002Bh            |                                             |              |                           |

| 04002Ch            |                                             |              |                           |

| 04002Dh            |                                             |              |                           |

| 04002Eh            |                                             |              |                           |

| 04002Fh            |                                             |              |                           |

#### Table 4.18SFR List (18)

X: Undefined

Blanks are reserved. No access is allowed.

Note:

1. The reset value reflects the value of the protect bit for each block in the flash memory.

| Table 4.28 | SFR List (28) |  |

|------------|---------------|--|

| Table 4.20             | SFR LIST (20)                      |        |             |

|------------------------|------------------------------------|--------|-------------|

| Address                | Register                           | Symbol | Reset Value |

|                        | CAN0 Mailbox 6: Message Identifier | C0MB6  | XXXX XXXXh  |

| 047C61h                |                                    |        |             |

| 047C62h                |                                    |        |             |

| 047C63h                |                                    |        |             |

| 047C64h                |                                    |        |             |

| 047C65h                | CAN0 Mailbox 6: Data Length        |        | XXh         |

|                        | CAN0 Mailbox 6: Data Field         |        | XXXX XXXX   |

| 047C67h                |                                    |        | XXXX XXXXh  |

| 047C68h                |                                    |        |             |

| 047C69h                |                                    |        |             |

| 047C6Ah                |                                    |        |             |

| 047C6Bh                |                                    |        |             |

| 047C6Ch                |                                    |        |             |

| 047C6Dh                |                                    |        |             |

|                        | CAN0 Mailbox 6: Time Stamp         |        | XXXXh       |

| 047C6Eh                | •                                  |        |             |

|                        |                                    | C0MB7  | XXXX XXXXh  |

|                        | CAN0 Mailbox 7: Message Identifier |        |             |

| 047C71h                |                                    |        |             |

| 047C72h                |                                    |        |             |

| 047C73h                |                                    |        |             |

| 047C74h                |                                    |        |             |

|                        | CAN0 Mailbox 7: Data Length        |        | XXh         |

|                        | CAN0 Mailbox 7: Data Field         |        | XXXX XXXX   |

| 047C77h                |                                    |        | XXXX XXXXh  |

| 047C78h                |                                    |        |             |

| 047C79h                |                                    |        |             |

| 047C7Ah                |                                    |        |             |

| 047C7Bh                |                                    |        |             |

| 047C7Ch                |                                    |        |             |

| 047C7Dh                |                                    |        |             |

| 047C7Eh                | CAN0 Mailbox 7: Time Stamp         |        | XXXXh       |

| 047C7Fh                |                                    |        |             |

| 047C80h                | CAN0 Mailbox 8: Message Identifier | C0MB8  | XXXX XXXXh  |

| 047C81h                |                                    |        |             |

| 047C82h                |                                    |        |             |

| 047C83h                |                                    |        |             |

| 047C84h                |                                    |        |             |

|                        | CAN0 Mailbox 8: Data Length        |        | XXh         |

|                        | CAN0 Mailbox 8: Data Field         |        | XXXX XXXX   |

| 047C87h                |                                    |        | XXXX XXXXh  |

| 047C88h                |                                    |        |             |

| 047C89h                |                                    |        |             |

| 047C8Ah                |                                    |        |             |

| 047C8An                |                                    |        |             |

| 047C8Bh                |                                    |        |             |

|                        |                                    |        |             |

| 047C8Dh                |                                    |        | VVVVh       |

|                        | CAN0 Mailbox 8: Time Stamp         |        | XXXXh       |

| 047C8Fh<br>X: Undefine |                                    |        |             |

| Table 4.36 | SFR List (36) |

|------------|---------------|

|------------|---------------|

| 14016 4.30         | · · · ·                                                     |        |                         |

|--------------------|-------------------------------------------------------------|--------|-------------------------|

| Address            | Register                                                    | Symbol | Reset Value             |

| 047DE0h            | CAN0 Mailbox 30: Message Identifier                         | C0MB30 | XXXX XXXXh              |

| 047DE1h            |                                                             |        |                         |

| 047DE2h            |                                                             |        |                         |

| 047DE3h            |                                                             |        |                         |

| 047DE4h            |                                                             |        |                         |

| 047DE5h            | CAN0 Mailbox 30: Data Length                                |        | XXh                     |

|                    | CAN0 Mailbox 30: Data Field                                 |        | XXXX XXXX               |

| 047DE7h            |                                                             |        | XXXX XXXXh              |

| 047DE8h            |                                                             |        |                         |

| 047DE9h            |                                                             |        |                         |

| 047DEAh            |                                                             |        |                         |

| 047DEBh            |                                                             |        |                         |

| 047DECh            |                                                             |        |                         |

| 047DEDh            |                                                             |        |                         |

|                    | CAN0 Mailbox 30: Time Stamp                                 |        | XXXXh                   |

| 047DEEh            |                                                             |        |                         |

|                    | CAN0 Mailbox 31: Message Identifier                         | C0MB31 | XXXX XXXXh              |

| 047DF0h            | <b>.</b>                                                    |        |                         |

| 047DF11            |                                                             |        |                         |

| 047DF2h            |                                                             |        |                         |

| 047DF3h<br>047DF4h |                                                             |        |                         |

|                    |                                                             |        | XXh                     |

|                    | CAN0 Mailbox 31: Data Length<br>CAN0 Mailbox 31: Data Field |        |                         |

|                    |                                                             |        | XXXX XXXX<br>XXXX XXXXh |

| 047DF7h            |                                                             |        |                         |

| 047DF8h            |                                                             |        |                         |

| 047DF9h            |                                                             |        |                         |

| 047DFAh            |                                                             |        |                         |

| 047DFBh            |                                                             |        |                         |

| 047DFCh            |                                                             |        |                         |

| 047DFDh            |                                                             |        |                         |

|                    | CAN0 Mailbox 31: Time Stamp                                 |        | XXXXh                   |

| 047DFFh            |                                                             |        |                         |

|                    | CAN0 Mask Register 0                                        | C0MKR0 | XXXX XXXXh              |

| 047E01h            |                                                             |        |                         |

| 047E02h            |                                                             |        |                         |

| 047E03h            |                                                             |        |                         |

|                    | CAN0 Mask Register 1                                        | C0MKR1 | XXXX XXXXh              |

| 047E05h            |                                                             |        |                         |

| 047E06h            |                                                             |        |                         |

| 047E07h            |                                                             |        |                         |

|                    | CAN0 Mask Register 2                                        | C0MKR2 | XXXX XXXXh              |

| 047E09h            |                                                             |        |                         |

| 047E0Ah            |                                                             |        |                         |

| 047E0Bh            |                                                             |        |                         |

|                    | CAN0 Mask Register 3                                        | C0MKR3 | XXXX XXXXh              |

| 047E0Dh            |                                                             |        |                         |

| 047E0Eh            |                                                             |        |                         |

| 047E0Fh            | 1                                                           |        |                         |

| X: Undefine        | d                                                           | ÷      | ÷                       |

# Table 5.3Operating Conditions (2/5) $(V_{CC} = 3.0 \text{ to } 5.5 \text{ V}, \text{ V}_{SS} = 0 \text{ V}, \text{ and } \text{T}_{a} = \text{T}_{opr}, \text{ unless otherwise noted})$ <sup>(1)</sup>

| Symbol           | ol Characteristic                            |                          | /alue (2 | 2)   | Unit |      |

|------------------|----------------------------------------------|--------------------------|----------|------|------|------|

| Gynnoor          | Characteristic                               |                          | Min.     | Тур. | Max. | Onit |

| C <sub>VDC</sub> | Decoupling capacitance for voltage regulator | Inter-pin voltage: 1.5 V | 2.4      |      | 10.0 | μF   |

Notes:

1. The device is operationally guaranteed under these operating conditions.

2. This value should be met with due consideration to the following conditions: operating temperature, DC bias, aging, etc.

Table 5.15

**Electrical Characteristics (1/3)**

# $V_{CC}$ = 5 V

| Symbol          |                                    | Characteristic                                                                                                                                                                                                                                                                          | Measurement               | Value                 |      |                 | Unit |

|-----------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|------|-----------------|------|

| Symbol          |                                    | Characteristic                                                                                                                                                                                                                                                                          | Condition                 | Min.                  | Тур. | Max.            | Unit |

| V <sub>OH</sub> | High<br>level<br>output<br>voltage | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, P11_0 to P11_4,<br>P12_0 to P12_7, P13_0 to P13_7,<br>P14_3 to P14_6, P15_0 to P15_7 <sup>(1)</sup> | I <sub>OH</sub> = -5 mA   | V <sub>CC</sub> - 2.0 |      | V <sub>cc</sub> | V    |

|                 |                                    | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, P11_0 to P11_4,<br>P12_0 to P12_7, P13_0 to P13_7,<br>P14_3 to P14_6, P15_0 to P15_7 <sup>(1)</sup> | I <sub>OH</sub> = -200 μA | V <sub>CC</sub> - 0.3 |      | V <sub>cc</sub> | v    |

| V <sub>OL</sub> | Low<br>level<br>output<br>voltage  | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, P11_0 to P11_4,<br>P12_0 to P12_7, P13_0 to P13_7,<br>P14_3 to P14_6, P15_0 to P15_7 <sup>(1)</sup> | I <sub>OL</sub> = 5 mA    |                       |      | 2.0             | v    |

|                 |                                    | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, P11_0 to P11_4,<br>P12_0 to P12_7, P13_0 to P13_7,<br>P14_3 to P14_6, P15_0 to P15_7 <sup>(1)</sup> | I <sub>OL</sub> = 200 μΑ  |                       |      | 0.45            | v    |

## (V<sub>CC</sub> = 4.2 to 5.5 V, V<sub>SS</sub> = 0 V, $T_a = T_{opr}$ , and $f_{(CPU)} = 64$ MHz, unless otherwise noted)

Note:

1. Ports P9\_0, P9\_2, and P11 to P15 are available in the 144-pin package only. Port P9\_1 is designated as input pin in the 100-pin package.

# $V_{CC}$ = 5 V

# Timing Requirements ( $V_{CC}$ = 4.2 to 5.5 V, $V_{SS}$ = 0 V, and $T_a$ = $T_{opr}$ , unless otherwise noted)

| Symbol               | Characteristic                    | Va   | Unit |      |

|----------------------|-----------------------------------|------|------|------|

| Symbol               | Characteristic                    | Min. | Max. | Onit |

| t <sub>C(CK)</sub>   | CLKi input clock cycle time       | 200  |      | ns   |

| t <sub>w(CKH)</sub>  | CLKi input high level pulse width | 80   |      | ns   |

| t <sub>w(CKL)</sub>  | CLKi input low level pulse width  | 80   |      | ns   |

| t <sub>su(D-C)</sub> | RXDi input setup time             | 80   |      | ns   |

| t <sub>h(C-D)</sub>  | RXDi input hold time              | 90   |      | ns   |

#### Table 5.30 Serial Interface

#### Table 5.31 A/D Trigger Input

| Symbol              | Symbol Characteristic                                                               |                       | Value |      |  |

|---------------------|-------------------------------------------------------------------------------------|-----------------------|-------|------|--|

| Symbol              |                                                                                     |                       | Max.  | Unit |  |

| t <sub>w(ADH)</sub> | ADTRG input high level pulse width<br>Hardware trigger input high level pulse width | $\frac{3}{\phi_{AD}}$ |       | ns   |  |

| t <sub>w(ADL)</sub> | ADTRG input low level pulse width<br>Hardware trigger input high level pulse width  | 125                   |       | ns   |  |

#### Table 5.32 External Interrupt INTi Input

| Symbol              | Characteristia                    |                 | Value                     | ;    | Unit |

|---------------------|-----------------------------------|-----------------|---------------------------|------|------|

| Symbol              | Characteristic                    | Characteristic  |                           | Max. | Unit |

| t <sub>w(INH)</sub> | INTi input high level pulse width | Edge sensitive  | 250                       |      | ns   |

|                     |                                   | Level sensitive | t <sub>C(CPU)</sub> + 200 |      | ns   |

| t <sub>w(INL)</sub> | INTi input low level pulse width  | Edge sensitive  | 250                       |      | ns   |

|                     |                                   | Level sensitive | t <sub>C(CPU)</sub> + 200 |      | ns   |

#### Table 5.33 Intelligent I/O

| Symbol                      | Characteristic                      | Va  | Unit |      |

|-----------------------------|-------------------------------------|-----|------|------|

| Symbol                      | Characteristic                      |     | Max. | Unit |

| t <sub>c(ISCLK2)</sub>      | ISCLK2 input clock cycle time       | 600 |      | ns   |

| t <sub>w(ISCLK2H)</sub>     | ISCLK2 input high level pulse width | 270 |      | ns   |

| t <sub>w(ISCLK2L)</sub>     | ISCLK2 input low level pulse width  | 270 |      | ns   |

| t <sub>su(RXD-ISCLK2)</sub> | ISRXD2 input setup time             | 150 |      | ns   |

| t <sub>h(ISCLK2-RXD)</sub>  | ISRXD2 input hold time              | 100 |      | ns   |

# $V_{CC}$ = 5 V

# Switching Characteristics (V<sub>CC</sub> = 4.2 to 5.5 V, V<sub>SS</sub> = 0 V, and $T_a = T_{opr}$ , unless otherwise noted)

| Symbol              | Characteristic         | Measurement | Va   | Unit |      |

|---------------------|------------------------|-------------|------|------|------|

| Symbol              | Characteristic         | Condition   | Min. | Max. | Unit |

| t <sub>d(C-Q)</sub> | TXDi output delay time | Refer to    |      | 80   | ns   |

| t <sub>h(C-Q)</sub> | TXDi output hold time  | Figure 5.6  | 0    |      | ns   |

#### Table 5.37Serial Interface

#### Table 5.38 Intelligent I/O

| Symbol                     | Characteristic           | Measurement | Value |      | Unit  |

|----------------------------|--------------------------|-------------|-------|------|-------|

| Symbol                     | Characteristic           | Condition   | Min.  | Max. | Offic |

| t <sub>d(ISCLK2-TXD)</sub> | ISTXD2 output delay time | Refer to    |       | 180  | ns    |

| t <sub>h(ISCLK2-RXD)</sub> | ISTXD2 output hold time  | Figure 5.6  | 0     |      | ns    |

#### Table 5.39 Multi-master I<sup>2</sup>C-bus Interface (standard-mode)

| Symbol                    | Characteristic                                                                          | Measurement | Value                                 |                                   |      |  |

|---------------------------|-----------------------------------------------------------------------------------------|-------------|---------------------------------------|-----------------------------------|------|--|

| Symbol                    | Characteristic                                                                          | Condition   | Min.                                  | Max.                              | Unit |  |

| t <sub>f(SCL)</sub>       | MSCL output fall time                                                                   |             | 2                                     |                                   | ns   |  |

| t <sub>f(SDA)</sub>       | MSDA output fall time                                                                   |             | 2                                     |                                   | ns   |  |

| t <sub>d(SDA-SCL)S</sub>  | MSCL output delay time after START condition/repeated START condition                   |             | 20 × t <sub>c(\u00f6</sub> IIC) - 120 | $52 \times t_{c(\phi IIC)} - 40$  | ns   |  |

| t <sub>d(SCL-SDA)</sub> P | Repeated START condition/STOP<br>condition output delay time after<br>MSCL becomes high | Figure 5.6  | $20 \times t_{c(\phi IIC)} + 40$      | $52 \times t_{c(\phi IIC)} + 120$ | ns   |  |

| t <sub>d(SCL-SDA)</sub>   | MSDA output delay time                                                                  | ]           | $2 \times t_{c(\phi IIC)} + 40$       | $3 \times t_{c(\phi IIC)} + 120$  | ns   |  |

#### Table 5.40 Multi-master I<sup>2</sup>C-bus Interface (fast-mode)

| Symbol                  | Characteristic                                                                          | Measurement | Value                                   |                                  |      |  |

|-------------------------|-----------------------------------------------------------------------------------------|-------------|-----------------------------------------|----------------------------------|------|--|

| Symbol                  | Characteristic                                                                          | Condition   | Min.                                    | Max.                             | Unit |  |

| t <sub>f(SCL)</sub>     | MSCL output fall time                                                                   |             | 2 (1)                                   |                                  | ns   |  |

| t <sub>f(SDA)</sub>     | MSDA output fall time                                                                   |             | 2 (1)                                   |                                  | ns   |  |

|                         | MSCL output delay time after START condition/repeated START condition                   | Refer to    | 10 × t <sub>c(¢IIC)</sub> - 120         | $26 \times t_{c(\phi IIC)} - 40$ | ns   |  |

|                         | Repeated START condition/STOP<br>condition output delay time after<br>MSCL becomes high | Figure 5.6  | 10 × t <sub>c(∳IIC)</sub> + 40          | 26 × t <sub>c(\UC)</sub> + 120   | ns   |  |

| t <sub>d(SCL-SDA)</sub> | MSDA output delay time                                                                  |             | $2 \times t_{c(\phi \parallel C)} + 40$ | $3 \times t_{c(\phi IIC)} + 120$ | ns   |  |

Note:

1. External circuits are required to satisfy the I<sup>2</sup>C-bus specification.

# Table 5.41Electrical Characteristics (1/3) ( $V_{CC}$ = 3.0 to 3.6 V, $V_{SS}$ = 0 V, $T_a$ = $T_{opr}$ , and $f_{(CPU)}$ = 64 MHz, unless otherwise noted)

| Symbol          |                                    | Characteristic                                                                                                                                                                                                                                                                          | Measurement             | Value                 |      |                 | Unit |

|-----------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|------|-----------------|------|

| Symbol          |                                    | Characteristic                                                                                                                                                                                                                                                                          | Condition               | Min.                  | Тур. | Max.            | Unit |

| V <sub>OH</sub> | High<br>level<br>output<br>voltage | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, P11_0 to P11_4,<br>P12_0 to P12_7, P13_0 to P13_7,<br>P14_3 to P14_6, P15_0 to P15_7 <sup>(1)</sup> | I <sub>OH</sub> = -1 mA | V <sub>CC</sub> - 0.6 |      | V <sub>cc</sub> | V    |

| V <sub>OL</sub> | Low<br>level<br>output<br>voltage  | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, P11_0 to P11_4,<br>P12_0 to P12_7, P13_0 to P13_7,<br>P14_3 to P14_6, P15_0 to P15_7 <sup>(1)</sup> | I <sub>OL</sub> = 1 mA  |                       |      | 0.5             | V    |

Note:

1. Ports P9\_0, P9\_2, and P11 to P15 are available in the 144-pin package only. Port P9\_1 is designated as input pin in the 100-pin package.

| Oursels al | Characte                   | Measurement Condition                                                                               |                                                                                                                                                                                                                           | Value |      | Э    | Unit |

|------------|----------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| Symbol     | ristic                     | IVIE                                                                                                | asurement Condition                                                                                                                                                                                                       | Min.  | Тур. | Max. | Uni  |

| cc         | Power<br>supply<br>current | In single-chip mode,<br>output pins are left open<br>and others are<br>connected to V <sub>SS</sub> | $\label{eq:f_cpu} \begin{array}{l} f_{(CPU)} = 64 \; MHz, \; f_{(BCLK)} = 32 \; MHz, \\ f_{(XIN)} = 8 \; MHz, \\ Active: XIN, \; PLL, \\ Stopped: \; XCIN, \; OCO \end{array}$                                            |       | 40   | 55   | mA   |

|            |                            | XIN-XOUT<br>Drive strength: low<br>XCIN-XCOUT                                                       | $f_{(CPU)} = 50 \text{ MHz}, f_{(BCLK)} = 25 \text{ MHz},$<br>$f_{(XIN)} = 8 \text{ MHz},$<br>Active: XIN, PLL,<br>Stopped: XCIN, OCO                                                                                     |       | 32   | 45   | mA   |

|            |                            | Drive strength: low                                                                                 | f <sub>(CPU)</sub> = f <sub>SO(PLL</sub> /24 MHz,<br>Active: PLL (self-oscillation),<br>Stopped: XIN, XCIN, OCO                                                                                                           |       | 9    |      | mA   |

|            |                            |                                                                                                     | $      f_{(CPU)} = f_{(BCLK)} = f_{(XIN)}/256 \text{ MHz},                                    $                                                                                                                           |       | 670  |      | μA   |

|            |                            |                                                                                                     | f <sub>(CPU)</sub> = f <sub>(BCLK)</sub> = 32.768 kHz,<br>Active: XCIN,<br>Stopped: XIN, PLL, OCO,<br>Main regulator: shutdown                                                                                            |       | 180  |      | μA   |

|            |                            |                                                                                                     | f <sub>(CPU)</sub> = f <sub>(BCLK)</sub> = f <sub>(OCO)</sub> /4 kHz,<br>Active: OCO,<br>Stopped: XIN, PLL, XCIN,<br>Main regulator: shutdown                                                                             |       | 190  |      | μA   |

|            |                            |                                                                                                     | $\begin{split} f_{(CPU)} &= f_{(BCLK)} = f_{(XIN)}/256 \text{ MHz}, \\ f_{(XIN)} &= 8 \text{ MHz}, \\ \text{Active: XIN,} \\ \text{Stopped: PLL, XCIN, OCO,} \\ T_a &= 25^{\circ}\text{C}, \text{ Wait mode} \end{split}$ |       | 500  | 900  | μA   |

|            |                            |                                                                                                     | $f_{(CPU)} = f_{(BCLK)} = 32.768 \text{ kHz},$<br>Active: XCIN,<br>Stopped: XIN, PLL, OCO,<br>Main regulator: shutdown,<br>T <sub>a</sub> = 25°C, Wait mode                                                               |       | 8    | 140  | μA   |

|            |                            |                                                                                                     | $f_{(CPU)} = f_{(BCLK)} = f_{(OCO)}/4 \text{ kHz},$<br>Active: OCO,<br>Stopped: XIN, PLL, XCIN,<br>Main regulator: shutdown,<br>$T_a = 25^{\circ}C$ , Wait mode                                                           |       | 10   | 150  | μA   |

|            |                            |                                                                                                     | Stopped: all clocks,<br>Main regulator: shutdown,<br>T <sub>a</sub> = 25°C                                                                                                                                                |       | 5    | 70   | μA   |

# Table 5.43Electrical Characteristics (3/3) $(V_{CC} = 3.0 \text{ to } 3.6 \text{ V}, V_{SS} = 0 \text{ V}, \text{ and } T_a = T_{opr}, \text{ unless otherwise noted})$

| Table 5.44 | A/D Conversion Characteristics ( $V_{CC} = AV_{CC} = V_{REF} = 3.0$ to 3.6 V, $V_{SS} = AV_{SS} = 0$ V, |

|------------|---------------------------------------------------------------------------------------------------------|

|            | T <sub>a</sub> = T <sub>opr</sub> , and f <sub>(BCLK)</sub> = 32 MHz, unless otherwise noted)           |

| Symbol              | Characteristic                       | Magguram                                               | Measurement Condition                                                                                   |      | Value |           |      |

|---------------------|--------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-------|-----------|------|

| Symbol              | Characteristic                       | Measurement Condition                                  |                                                                                                         | Min. | Тур.  | Max.      | Unit |

| —                   | Resolution                           | V <sub>REF</sub> = V <sub>CC</sub>                     |                                                                                                         |      |       | 10        | Bits |

| _                   | Absolute error                       | V <sub>REF</sub> = V <sub>CC</sub> = 3.3 V             | AN_0 to AN_7,<br>AN0_0 to AN0_7,<br>AN2_0 to AN2_7,<br>AN15_0 to AN15_7,<br>ANEX0, ANEX1 <sup>(1)</sup> |      |       | ±5        | LSB  |

|                     |                                      |                                                        | External op-amp<br>connection mode                                                                      |      |       | ±7        | LSB  |

| INL                 | Integral non-linearity<br>error      | V <sub>REF</sub> = V <sub>CC</sub> = 3.3 V             | AN_0 to AN_7,<br>AN0_0 to AN0_7,<br>AN2_0 to AN2_7,<br>AN15_0 to AN15_7,<br>ANEX0, ANEX1 <sup>(1)</sup> |      |       | ±5        | LSB  |

|                     |                                      |                                                        | External op-amp connection mode                                                                         |      |       | ±7        | LSB  |

| DNL                 | Differential non-<br>linearity error | $V_{REF} = V_{CC} = 3.3 \text{ V}$                     |                                                                                                         |      |       | ±1        | LSB  |

| —                   | Offset error                         |                                                        |                                                                                                         |      |       | ±3        | LSB  |

| —                   | Gain error                           |                                                        |                                                                                                         |      |       | ±3        | LSB  |

| R <sub>LADDER</sub> | Resistor ladder                      | V <sub>REF</sub> = V <sub>CC</sub>                     |                                                                                                         | 4    |       | 20        | kΩ   |

| t <sub>CONV</sub>   | Conversion time<br>(10 bits)         | $\phi_{AD}$ = 10 MHz,<br>with sample and hold function |                                                                                                         | 3.3  |       |           | μs   |

| t <sub>CONV</sub>   | Conversion time<br>(8 bits)          | $\phi_{AD}$ = 10 MHz,<br>with sample and hold function |                                                                                                         | 2.8  |       |           | μs   |

| t <sub>SAMP</sub>   | Sampling time                        | φ <sub>AD</sub> = 10 MHz                               |                                                                                                         | 0.3  |       |           | μs   |

| V <sub>IA</sub>     | Analog input voltage                 |                                                        |                                                                                                         | 0    |       | $V_{REF}$ | V    |

| фар                 | Operating clock                      | Operating clock Without sample and hold function       |                                                                                                         | 0.25 |       | 10        | MHz  |

|                     | frequency                            | With sample and hold function                          |                                                                                                         | 1    |       | 10        | MHz  |

Note:

1. Pins AN15\_0 to AN15\_7 are available in the 144-pin package only.

# Timing Requirements ( $V_{CC}$ = 3.0 to 3.6 V, $V_{SS}$ = 0 V, and $T_a$ = $T_{opr}$ , unless otherwise noted)

| Symbol                          | Characteristic                              |      | Value |      |  |

|---------------------------------|---------------------------------------------|------|-------|------|--|

| Symbol                          |                                             |      | Max.  | Unit |  |

| t <sub>C(X)</sub>               | External clock input period                 | 62.5 | 250   | ns   |  |

| t <sub>w(XH)</sub>              | External clock input high level pulse width | 25   |       | ns   |  |

| t <sub>w(XL)</sub>              | External clock input low level pulse width  | 25   |       | ns   |  |

| t <sub>r(X)</sub>               | External clock input rise time              |      | 5     | ns   |  |

| t <sub>f(X)</sub>               | External clock input fall time              |      | 5     | ns   |  |

| t <sub>w</sub> / t <sub>C</sub> | External clock input duty                   | 40   | 60    | %    |  |

## Table 5.46External Clock Input

#### Table 5.47 External Bus Timing

| Symbol                | Characteristic               | Va   | Unit                          |       |  |

|-----------------------|------------------------------|------|-------------------------------|-------|--|

| Symbol                | Characteristic               | Min. | Max.                          | Offic |  |

| t <sub>su(D-R)</sub>  | Data setup time before read  | 40   |                               | ns    |  |

| t <sub>h(R-D)</sub>   | Data hold time after read    | 0    |                               | ns    |  |

| t <sub>dis(R-D)</sub> | Data disable time after read |      | $0.5 \times t_{c(Base)} + 10$ | ns    |  |

| Revision | History  |

|----------|----------|

|          | 1 notory |

# R32C/117 Group Datasheet

| Dav  | Date               |          | Description                                                                                                                                                                                                                                                                                                                                                   |

|------|--------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. |                    | Page     | Summary                                                                                                                                                                                                                                                                                                                                                       |

| 1.00 | Nov 19, 2009       | _        | Initial release                                                                                                                                                                                                                                                                                                                                               |

| 1.01 | .01 Mar 11, 2010 — |          | Second edition released                                                                                                                                                                                                                                                                                                                                       |

|      |                    | _        | Added "128 KB/20KB" and "256KB/20KB" for ROM/RAM capacity                                                                                                                                                                                                                                                                                                     |

| 1.10 | Jun 23, 2010       | _        | Third edition released                                                                                                                                                                                                                                                                                                                                        |

|      |                    |          | This manual in general                                                                                                                                                                                                                                                                                                                                        |

|      |                    | _        | <ul> <li>Applied new Renesas templates and formats to the manual</li> <li>Changed company name to "Renesas Electronics Corporation" and<br/>changed related descriptions due to business merger of Renesas<br/>Technology Corporation and NEC Electronics Corporation (under<br/>Chapters 1 and 5)</li> <li>Added specifications of 64 MHz version</li> </ul> |