#### Zilog - ZLP32300H2816C00TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | Z8                                                            |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | -                                                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, WDT                        |

| Number of I/O              | 24                                                            |

| Program Memory Size        | 16KB (16K x 8)                                                |

| Program Memory Type        | ОТР                                                           |

| EEPROM Size                | -                                                             |

| RAM Size                   | 237 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                     |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zlp32300h2816c00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# zilog

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

ISO 9001:2000 FS 507510 Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

#### **Revision History**

Each instance in the Revision History table reflects a change to this document from its previous revision. For more details, refer to the corresponding pages or appropriate link in the table.

| Date             | Revision<br>Level | Description                                             | Page<br>Number |

|------------------|-------------------|---------------------------------------------------------|----------------|

| February<br>2008 | 23                | Updated Ordering Information section.                   | 87             |

| January<br>2008  | 22                | Updated Ordering Information section.                   | 87             |

| July 2007        | 21                | Updated Disclaimer section and implemented style guide. | All            |

| February<br>2007 | 20                | Updated Low-Voltage Detection.                          | 58             |

| May<br>2006      | 19                | Updated Figure 33 with pin P22 in SMR block input.      | 52             |

| December<br>2005 | 18                | Updated Clock and Input/Output Ports sections.          | 15 and 51      |

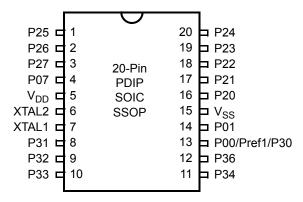

## **Pin Description**

The pin configuration for the 20-pin PDIP/SOIC/SSOP is displayed in Figure 3 and described in Table 3. The pin configuration for the 28-pin PDIP/SOIC/SSOP are depicted in Figure 4 and described in Table 4. The pin configurations for the 40-pin PDIP and 48-pin SSOP versions are displayed in Figure 5, Figure 6, and described in Table 5.

| Figure 3. 20-Pi | n PDIP/SOIC/SSOP | Pin Configuration |

|-----------------|------------------|-------------------|

|-----------------|------------------|-------------------|

| Table 3. 20-P | in PDIP/SOIC/ | SSOP Pin Id | entification |

|---------------|---------------|-------------|--------------|

|---------------|---------------|-------------|--------------|

| Pin No | Symbol          | Function                                             | Direction                                   |

|--------|-----------------|------------------------------------------------------|---------------------------------------------|

| 1–3    | P25–P27         | Port 2, Bits 5,6,7                                   | Input/Output                                |

| 4      | P07             | Port 0, Bit 7                                        | Input/Output                                |

| 5      | V <sub>DD</sub> | Power Supply                                         |                                             |

| 6      | XTAL2           | Crystal Oscillator Clock                             | Output                                      |

| 7      | XTAL1           | Crystal Oscillator Clock                             | Input                                       |

| 8–10   | P31–P33         | Port 3, Bits 1,2,3                                   | Input                                       |

| 11,12  | P34, P36        | Port 3, Bits 4,6                                     | Output                                      |

| 13     | P00/Pref1/P30   | Port 0, Bit 0/Analog reference input<br>Port 3 Bit 0 | Input/Output for P00<br>Input for Pref1/P30 |

| 14     | P01             | Port 0, Bit 1                                        | Input/Output                                |

| 15     | V <sub>SS</sub> | Ground                                               |                                             |

| 16–20  | P20–P24         | Port 2, Bits 0,1,2,3,4                               | Input/Output                                |

| 40-Pin PDIP No | 48-Pin SSOP No | Symbol |

|----------------|----------------|--------|

|                | 14             | NC     |

|                | 30             | NC     |

|                | 36             | NC     |

#### **Pin Functions**

#### XTAL1 Crystal 1 (Time-Based Input)

This pin connects a parallel-resonant crystal or ceramic resonator to the on-chip oscillator input. Additionally, an optional external single-phase clock can be coded to the on-chip oscillator input.

#### XTAL2 Crystal 2 (Time-Based Output)

This pin connects a parallel-resonant crystal or ceramic resonant to the on-chip oscillator output.

#### Input/Output Ports

$\wedge$

**Caution:** The CMOS input buffer for each Port 0, 1, or 2 pin is always connected to the pin, even when the pin is configured as an output. If the pin is configured as an open-drain output and no external signal is applied, a High output state can cause the CMOS input buffer to float. This might lead to excessive leakage current of more than 100  $\mu$ A. To prevent this leakage, connect the pin to an external signal with a defined logic level or ensure its output state is Low, especially during STOP mode.

Internal pull-ups are disabled on any given pin or group of port pins when programmed into output mode.

Port 0, 1, and 2 have both input and output capability. The input logic is always present no matter whether the port is configured as input or output. When doing a READ instruction, the MCU reads the actual value at the input logic but not from the output buffer. In addition, the instructions of OR, AND, and XOR have the Read-Modify-Write sequence. The MCU first reads the port, and then modifies the value and load back to the port.

Precaution must be taken if the port is configured as open-drain output or if the port is driving any circuit that makes the voltage different from the desired output logic. For example, pins P00–P07 are not connected to anything else. If it is configured as

open-drain output with output logic as ONE, it is a floating port and reads back as ZERO. The following instruction sets P00-P07 all Low.

AND P0,#%F0

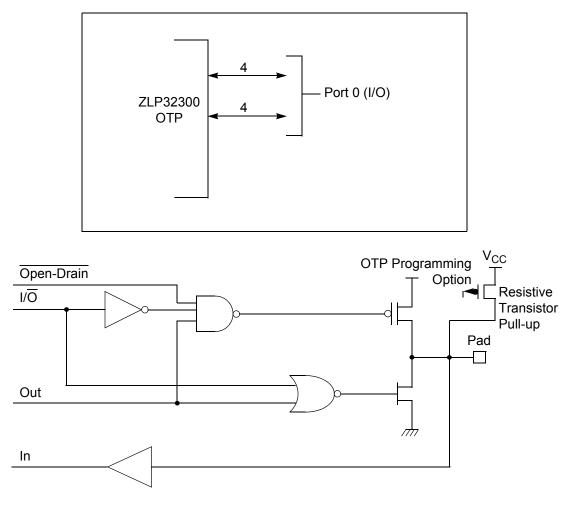

#### Port 0 (P00–P07)

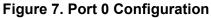

Port 0 is an 8-bit, bidirectional, CMOS-compatible port. These eight I/O lines are configured under software control as a nibble I/O port. The output drivers are push-pull or opendrain controlled by bit D2 in the PCON register.

If one or both nibbles are needed for I/O operation, they must be configured by writing to the Port 01 mode register (P01M). After a hardware reset or Stop Mode Recovery, Port 0 is configured as an input port.

An optional pull-up transistor is available as a OTP option bit on all Port 0 bits with nibble select.

**Note:** *The Port 0 direction is reset to be input following an SMR.*

#### Port 1 (P17–P10)

Port 1 can be configured for standard port input or output mode (see Figure 8). After POR or Stop Mode Recovery, Port 1 is configured as an input port. The output drivers are either push-pull or open-drain and are controlled by bit D1 in the PCON register.

- **Notes:** 1. *The Port 1 direction is reset to be input following an SMR.*

- 2. In 20- and 28-pin packages, Port 1 is reserved. A write to this register will have no effect and will always read FF.

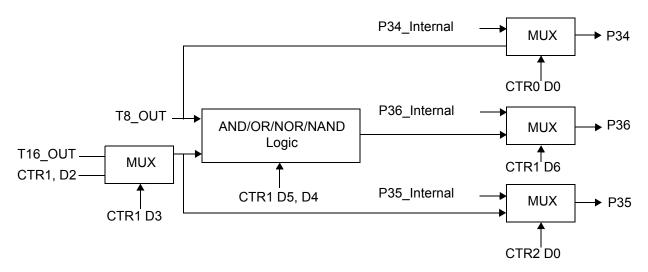

Figure 11. Port 3 Counter/Timer Output Configuration

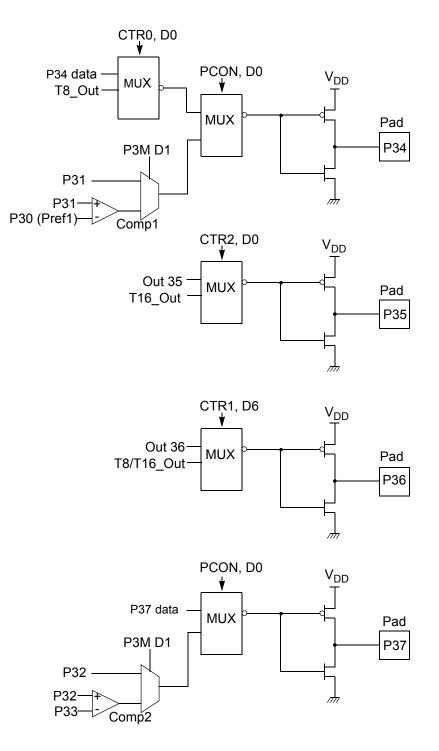

Figure 22. DEMODULATION Mode Flowchart

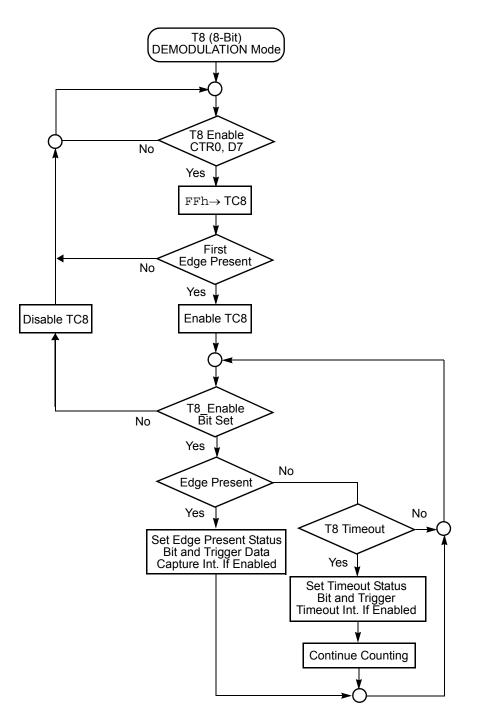

## Crimzon<sup>®</sup> ZLP32300 **Product Specification** zilog Do not load these registers at the time the values are to be loaded into the counter/timer Caution: to ensure known operation. An initial count of 1 is not allowed. An initial count of 0causes T16 to count from 0 to FFFFh to FFFFh. Transition from 0 to FFFFh is not a timeout condition. -TC16H\*256+TC16L Counts "Counter Enable" Command T16 OUT Toggles, T16 OUT Switches to Its Timeout Interrupt Initial Value (CTR1 D0) Figure 24. T16 OUT in SINGLE-PASS Mode TC16H\*256+TC16L TC16H\*256+TC16L

#### Figure 25. T16\_OUT in MODULO-N Mode

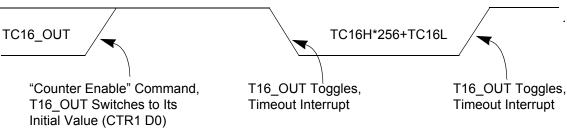

#### **T16 DEMODULATION Mode**

You must program TC16L and TC16H to FFh. After T16 is enabled, and the first edge (rising, falling, or both depending on CTR1 D5; D4) is detected, T16 captures H116 and LO16, reloads, and begins counting.

#### If D6 of CTR2 Is 0

When a subsequent edge (rising, falling, or both depending on CTR1, D5; D4) is detected during counting, the current count in T16 is complemented and put into HI16 and LO16. When data is captured, one of the edge detect status bits (CTR1, D1; D0) is set, and an interrupt is generated if enabled (CTR2, D2). T16 is loaded with FFFFh and starts again.

#### Initiating PING-PONG Mode

First, make sure both counter/timers are not running. Set T8 into SINGLE-PASS mode (CTR0, D6), set T16 into SINGLE-PASS mode (CTR2, D6), and set the PING-PONG mode (CTR1, D2; D3). These instructions can be in random order. Finally, start PING-PONG mode by enabling either T8 (CTR0, D7) or T16 (CTR2, D7), see Figure 26.

Figure 27. Output Circuit

The initial value of T8 or T16 must not be 1. If you stop the timer and restart the timer, reload the initial value to avoid an unknown previous value.

#### **During PING-PONG Mode**

The enable bits of T8 and T16 (CTR0, D7; CTR2, D7) are set and cleared alternately by hardware. The timeout bits (CTR0, D5; CTR2, D5) are set every time the counter/timers reach the terminal count.

#### **Timer Output**

The output logic for the timers is displayed in Figure 27. P34 is used to output T8-OUT when D0 of CTR0 is set. P35 is used to output the value of TI6-OUT when D0 of CTR2 is set. When D6 of CTR1 is set, P36 outputs the logic combination of T8-OUT and T16-OUT determined by D5 and D4 of CTR1.

#### Interrupts

The Crimzon ZLP32300 features six different interrupts (see Table 11 on page 45). The interrupts are maskable and prioritized (see Figure 28). The six sources are divided as follows: three sources are claimed by Port 3 lines P33–P31, two by the

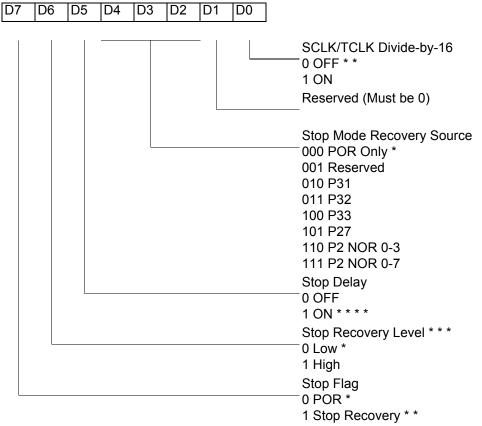

#### Stop Mode Recovery

#### Stop Mode Recovery Register (SMR)

This register selects the clock divide value and determines the mode of Stop Mode Recovery (see Figure 31). All bits are write only except bit 7, which is read only. Bit 7 is a Flag bit that is hardware set on the condition of Stop recovery and reset by a power-on cycle. Bit 6 controls whether a low level or a high level at the XOR-gate input (see Figure 33 on page 52) is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits D2, D3, and D4 of the SMR register specify the source of the Stop Mode Recovery signal. Bits D0 determines if SCLK/TCLK are divided by 16 or not. The SMR is located in Bank F of the Expanded Register Group at address OBh.

\*Default after Power-On Reset or Watchdog Reset

- \* \*Default setting after Reset and Stop Mode Recovery.

- \* \* \*At the XOR gate input

- \* \* \* \*Default setting after reset. Must be 1 if using a crystal or resonator clock source.

#### Figure 31. Stop Mode Recovery Register

#### WDT Time Select (D0, D1)

This bit selects the WDT time period. It is configured as indicated in Table 15.

#### Table 15. Watchdog Timer Time Select

| D1 | D0 | Timeout of Internal RC-Oscillator |

|----|----|-----------------------------------|

| 0  | 0  | 5 ms min                          |

| 0  | 1  | 10 ms min                         |

| 1  | 0  | 20 ms min                         |

| 1  | 1  | 80 ms min                         |

#### WDTMR During Halt (D2)

This bit determines whether or not the WDT is active during HALT mode. A 1 indicates active during HALT. The default is 1, see Figure 36.

| 7    | D6      | D5       | D4      | D3 | D2 | D1 | D0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|---------|----------|---------|----|----|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |         |          |         |    |    |    |    | TRANSMIT Mode*         R/W 0 T16_OUT is 0 initially*         1 T16_OUT is 1 initially         DEMODULATION Mode         R 0 No Falling Edge Detection         R 1 Falling Edge Detection         W 0 No Effect         W 1 Reset Flag to 0         TRANSMIT Mode*         R/W 0 T8_OUT is 0 initially*         1 T8_OUT is 1 initially         DEMODULATION Mode         R/W 0 T8_OUT is 0 initially*         1 T8_OUT is 1 initially         DEMODULATION Mode         R 0 No Rising Edge Detection         R 1 Rising Edge Detection         R 0 No Effect         W 1 Reset Flag to 0         TRANSMIT Mode*         0 No No Effect         W 1 Reset Flag to 0         TRANSMIT Mode*         0 0 Normal Operation*         0 1 PING-PONG Mode         1 0 T16_OUT = 0         1 1 T16_OUT = 1         DEMODULATION Mode         0 0 No Filter         0 1 4 SCLK Cycle Filter         1 0 8 SCLK Cycle Filter |

| Defa | ult set | ing afte | r resel |    |    |    |    | 1       1       Reserved         TRANSMIT Mode/T8/T16 Logic       0       0       AND**         0       1       OR       1       0         1       0       NOR       1       1       NAND         DEMODULATION Mode       0       0       Falling Edge Detection         1       1       NAND         DEMODULATION Mode       0       Falling Edge Detection         1       1       Reserved         TRANSMIT Mode       0       P36 as Port Output *         1       P36 as T8/T16_OUT         DEMODULATION Mode       0         0       P31 as Demodulator Ing         1       P20 as Demodulator Ing         1       P20 as Demodulator Ing         0       TRANSMIT/DEMODULATION Mode         0       TRANSMIT Mode *                                                                                                                                                                                         |

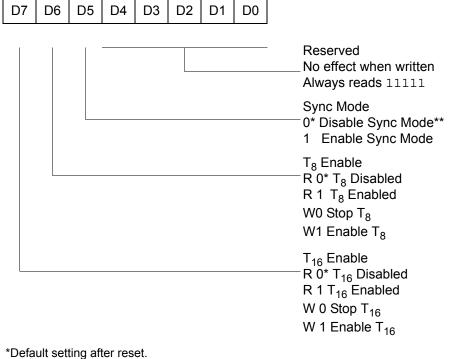

#### CTR3(0D)03H

\*\*Default setting after reset. Not reset with a Stop Mode Recovery.

#### Figure 40. T8/T16 Control Register (0D)03H: Read/Write (Except Where Noted)

**Note:** If Sync Mode is enabled, the first pulse of T8 carrier is always synchronized with T16 (demodulated signal). It can always provide a full carrier pulse.

## **Electrical Characteristics**

#### **Absolute Maximum Ratings**

Stresses greater than those listed in Table 18 might cause permanent damage to the device. This rating is a stress rating only. Functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period might affect device reliability.

Table 17. Absolute Maximum Ratings

| Parameter                                                                           | Minimum         | Maximun | n Units | Notes |

|-------------------------------------------------------------------------------------|-----------------|---------|---------|-------|

| Ambient temperature under bias                                                      | 0               | +70     | С       |       |

| Storage temperature                                                                 | -65             | +150    | С       |       |

| Voltage on any pin with respect to $V_{SS}$                                         | -0.3            | +5.5    | V       | 1     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$                                    | -0.3            | +3.6    | V       |       |

| Maximum current on input and/or inactive output pin                                 | -5              | +5      | μA      |       |

| Maximum output current from active output pin                                       | -25             | +25     | mA      |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$                                    |                 | 75      | mA      |       |

| <sup>1</sup> This voltage applies to all pins except the following: $V_{DD}$ , P32, | , P33 and RESET |         |         |       |

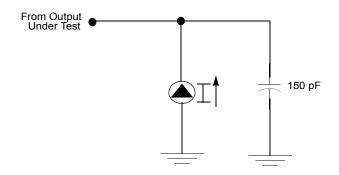

#### **Standard Test Conditions**

The characteristics listed in this product specification apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (see Figure 56).

Figure 56. Test Load Diagram

#### Capacitance

Table 18 lists the capacitances.

#### Table 18. Capacitance

| Parameter                                                                            | Maximum               |

|--------------------------------------------------------------------------------------|-----------------------|

| Input capacitance                                                                    | 12 pF                 |

| Output capacitance                                                                   | 12 pF                 |

| I/O capacitance                                                                      | 12 pF                 |

| $T_A = 25 \text{ °C}, V_{CC} = GND = 0 \text{ V}, \text{ f}$<br>pins returned to GND | = 1.0 MHz, unmeasured |

#### **DC Characteristics**

Table 19 describes the DC characteristics.

#### **Table 19. DC Characteristics**

|                     |                                                |                 | T <sub>A</sub> = 0 °C | to +70             | °C                       |       |                                       |       |

|---------------------|------------------------------------------------|-----------------|-----------------------|--------------------|--------------------------|-------|---------------------------------------|-------|

| Symbol              | Parameter                                      | V <sub>cc</sub> | Min                   | Тур <sup>(7)</sup> | Мах                      | Units | Conditions                            | Notes |

| V <sub>CC</sub>     | Supply Voltage                                 |                 | 2.0                   |                    | 3.6                      | V     | See Notes                             | 5     |

| V <sub>CH</sub>     | Clock Input High<br>Voltage                    | 2.0-3.6         | 0.8 V <sub>CC</sub>   |                    | V <sub>CC</sub> +0.3     | V     | Driven by External<br>Clock Generator |       |

| V <sub>CL</sub>     | Clock Input Low<br>Voltage                     | 2.0-3.6         | V <sub>SS</sub> -0.3  |                    | 0.4                      | V     | Driven by External<br>Clock Generator |       |

| V <sub>IH</sub>     | Input High Voltage                             | 2.0-3.6         | 0.7 V <sub>CC</sub>   |                    | V <sub>CC</sub> +0.3     | V     |                                       |       |

| V <sub>IL</sub>     | Input Low Voltage                              | 2.0-3.6         | V <sub>SS</sub> -0.3  |                    | $0.2 V_{CC}$             | V     |                                       |       |

| V <sub>OH1</sub>    | Output High Voltage                            | 2.0-3.6         | V <sub>CC</sub> -0.4  |                    |                          | V     | I <sub>OH</sub> = -0.5 mA             |       |

| V <sub>OH2</sub>    | Output High Voltage<br>(P36, P37, P00,<br>P01) | 2.0-3.6         | V <sub>CC</sub> -0.8  |                    |                          | V     | I <sub>OH</sub> = -7 mA               |       |

| V <sub>OL1</sub>    | Output Low Voltage                             | 2.0-3.6         |                       |                    | 0.4                      | V     | I <sub>OL</sub> = 4.0 mA              |       |

| V <sub>OL2</sub>    | Output Low Voltage<br>(P00, P01, P36,<br>P37)  | 2.0-3.6         |                       |                    | 0.8                      | V     | I <sub>OL</sub> = 10 mA               |       |

| V <sub>OFFSET</sub> | Comparator Input<br>Offset Voltage             | 2.0-3.6         |                       |                    | 25                       | mV    |                                       |       |

| V <sub>REF</sub>    | Comparator<br>Reference<br>Voltage             | 2.0-3.6         | 0                     |                    | V <sub>CC</sub><br>-1.75 | V     |                                       |       |

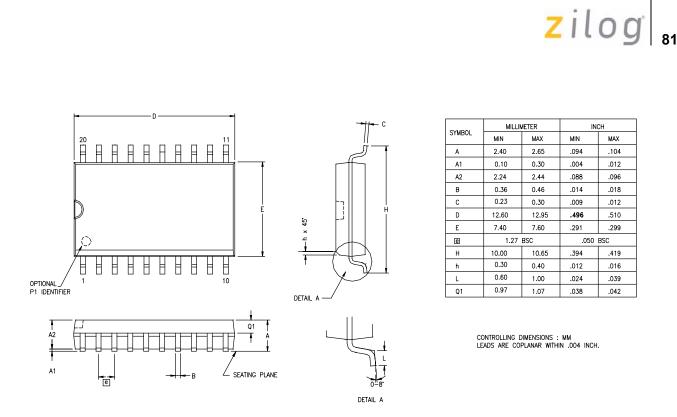

Figure 59. 20-Pin SOIC Package Diagram

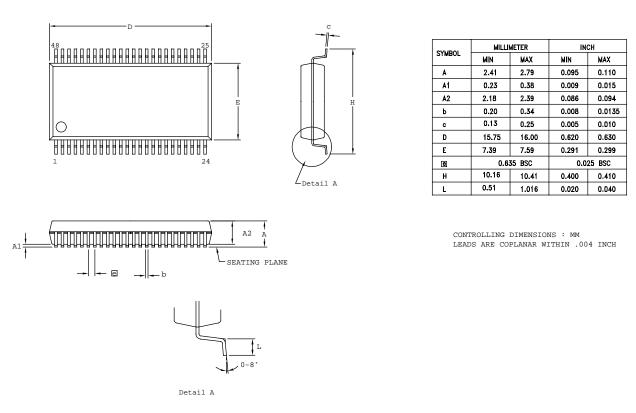

Figure 65. 48-Pin SSOP Package Design

**Note:** Contact  $Zilog^{\mathbb{R}}$  on the actual bonding diagram and coordinate for chip-on-board assembly.

#### 93

#### 0

oscillator configuration 46 output circuit, counter/timer 43

#### Ρ

package information 20-pin DIP package diagram 80 20-pin SSOP package diagram 82 28-pin DIP package diagram 84 28-pin SOIC package diagram 83 28-pin SSOP package diagram 85 40-pin DIP package diagram 85 48-pin SSOP package diagram 86 part number format 89 pin configuration 20-pin DIP/SOIC/SSOP 5 28-pin DIP/SOIC/SSOP 6 40- and 48-pin 8 40-pin DIP **7** 48-pin SSOP 8 pin functions port 0 (P07 - P00) 11 port 0 (P17 - P10) 12 port 0 configuration 12 port 1 configuration 13 port 2 (P27 - P20) 13 port 2 (P37 - P30) 14 port 2 configuration 14 port 3 configuration 15 port 3 counter/timer configuration 17 reset) 18 XTAL1 (time-based input 10 XTAL2 (time-based output) 10 port 0 configuration 12 port 0 pin function 11 port 1 configuration 13 port 1 pin function 12 port 2 configuration 14 port 2 pin function 13 port 3 configuration 15 port 3 pin function 14 port 3counter/timer configuration 17 port configuration register 48

power connections 1 power supply 5 program memory 19 map 20

#### R

ratings, absolute maximum 75 register 54 CTR(D)01h 28 CTR0(D)00h 27 CTR2(D)02h 31 CTR3(D)03h 33 flag 73 HI16(D)09h 26 HI8(D)0Bh 25 interrupt priority 71 interrupt request 72 interruptmask 72 L016(D)08h 26 L08(D)0Ah 26 LVD(D)0Ch 58 pointer 73 port 0 and 1 70 port 2 configuration 69 port 3 mode 69 port configuration 48, 69 SMR2(F)0Dh 33 stack pointer high 74 stack pointer low 74 stop mode recovery 49 stop mode recovery 2 54 stop mode recovery 66 stop mode recovery 2 67 T16 control 62 T8 and T16 common control functions 61 T8/T16 control 63 TC16H(D)07h 26 TC16L(D)06h 26 TC8 control 60 TC8H(D)05h 27 TC8L(D)04h 27 voltage detection 64 watch-dog timer 68

## **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <a href="http://www.zilog.com/kb">http://www.zilog.com/kb</a>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.