# E. Analog Devices Inc./Maxim Integrated - <u>ZLP32300P2808G Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                           |

| Core Processor             | Z8                                                                 |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | -                                                                  |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, WDT                             |

| Number of I/O              | 24                                                                 |

| Program Memory Size        | 8KB (8K x 8)                                                       |

| Program Memory Type        | OTP                                                                |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 237 x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                          |

| Data Converters            | -                                                                  |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                    |

| Mounting Type              | Through Hole                                                       |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                           |

| Supplier Device Package    | 28-PDIP                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/zlp32300p2808g |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

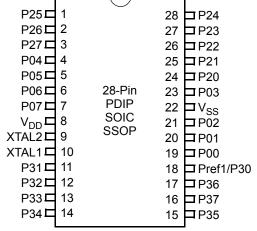

| Pin No | Symbol          | Direction                               | Description                  |  |  |

|--------|-----------------|-----------------------------------------|------------------------------|--|--|

| 1-3    | P25-P27         | Input/Output                            | Port 2, Bits 5, 6, 7         |  |  |

| 4-7    | P04-P07         | 07 Input/Output Port 0, Bits 4, 5, 6, 7 |                              |  |  |

| 8      | V <sub>DD</sub> |                                         | Power supply                 |  |  |

| 9      | XTAL2           | Output                                  | Crystal, oscillator clock    |  |  |

| 10     | XTAL1           | Input                                   | Crystal, oscillator clock    |  |  |

| 11-13  | P31-P33         | Input                                   | Port 3, Bits 1, 2, 3         |  |  |

| 14     | P34             | Output                                  | Port 3, Bit 4                |  |  |

| 15     | P35             | Output                                  | Port 3, Bit 5                |  |  |

| 16     | P37             | Output                                  | Port 3, Bit 7                |  |  |

| 17     | P36             | Output                                  | Port 3, Bit 6                |  |  |

| 18     | Pref1/P30       | Input                                   | Analog ref input; connect to |  |  |

|        | Port 3 Bit 0    |                                         | V <sub>CC</sub> if not used  |  |  |

|        |                 |                                         | Input for Pref1/P30          |  |  |

| 19-21  | P00-P02         | Input/Output                            | Port 0, Bits 0, 1, 2         |  |  |

| 22     | V <sub>SS</sub> |                                         | Ground                       |  |  |

| 23     | P03             | Input/Output                            | Port 0, Bit 3                |  |  |

| 24-28  | P20-P24         | Input/Output                            | Port 2, Bits 0–4             |  |  |

Table 4. 28-Pin PDIP/SOIC/SSOP Pin Identification

| 40-Pin PDIP No | 48-Pin SSOP No | Symbol          |

|----------------|----------------|-----------------|

| 32             | 39             | P12             |

| 33             | 40             | P13             |

| 8              | 9              | P14             |

| 9              | 10             | P15             |

| 12             | 15             | P16             |

| 13             | 16             | P17             |

| 35             | 42             | P20             |

| 36             | 43             | P21             |

| 37             | 44             | P22             |

| 38             | 45             | P23             |

| 39             | 46             | P24             |

| 2              | 2              | P25             |

| 3              | 3              | P26             |

| 4              | 4              | P27             |

| 16             | 19             | P31             |

| 17             | 20             | P32             |

| 18             | 21             | P33             |

| 19             | 22             | P34             |

| 22             | 26             | P35             |

| 24             | 28             | P36             |

| 23             | 27             | P37             |

| 20             | 23             | NC              |

| 40             | 47             | NC              |

| 1              | 1              | NC              |

| 21             | 25             | RESET           |

| 15             | 18             | XTAL1           |

| 14             | 17             | XTAL2           |

| 11             | 12, 13         | V <sub>DD</sub> |

| 31             | 24, 37, 38     | V <sub>SS</sub> |

| 25             | 29             | Pref1/P30       |

|                | 48             | NC              |

|                | 6              | NC              |

#### Table 5. 40- and 48-Pin Configuration (Continued)

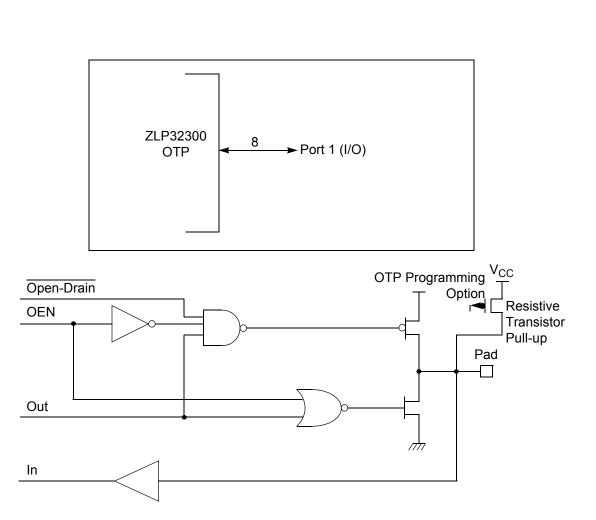

#### Port 2 (P27-P20)

Port 2 is an 8-bit, bidirectional, CMOS-compatible I/O port (see Figure 9). These eight I/O lines can be independently configured under software control as inputs or outputs. Port 2 is always available for I/O operation. A EPROM option bit is available to connect eight pull-up transistors on this port. Bits programmed as outputs are globally programmed as either push-pull or open-drain. The POR resets with the eight bits of Port 2 configured as inputs.

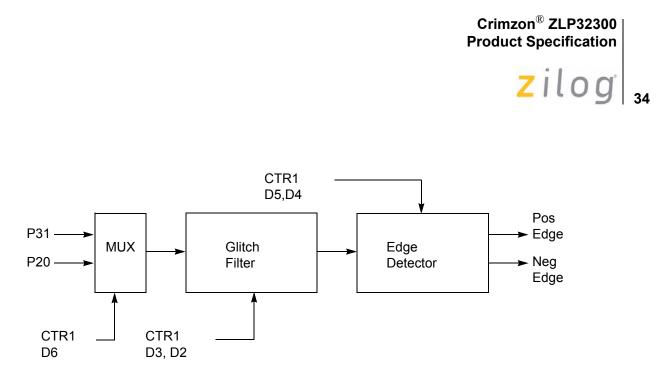

Port 2 also has an 8-bit input OR and AND gate, which can be used to wake up the part. P20 can be programmed to access the edge-detection circuitry in DEMODULATION mode.

Crimzon<sup>®</sup> ZLP32300 Product Specification

zilog

(see T8 and T16 Common Functions—CTR1(0D)01h on page 28). Other edge detect and IRQ modes are described in Table 6.

**Note:** Comparators are powered down by entering STOP mode. For P31–P33 to be used in a Stop Mode Recovery source, these inputs must be placed into DIGITAL mode.

| Pin       | I/O | Counter/Timers | Comparator | Interrupt |

|-----------|-----|----------------|------------|-----------|

| Pref1/P30 | IN  |                | RF1        |           |

| P31       | IN  | IN             | AN1        | IRQ2      |

| P32       | IN  |                | AN2        | IRQ0      |

| P33       | IN  |                | RF2        | IRQ1      |

| P34       | OUT | Т8             | AO1        |           |

| P35       | OUT | T16            |            |           |

| P36       | OUT | T8/16          |            |           |

| P37       | OUT |                | AO2        |           |

| P20       | I/O | IN             |            |           |

Table 6. Port 3 Pin Function Summary

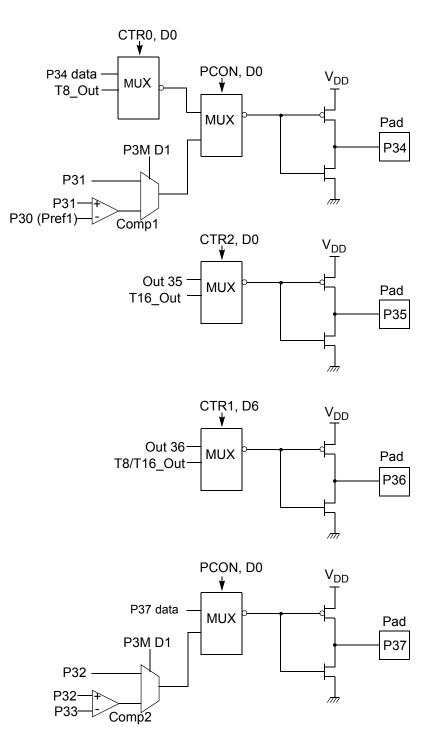

Port 3 also provides output for each of the counter/timers and the AND/OR Logic (see Figure 11). Control is performed by programming bits D5–D4 of CTR1, bit 0 of CTR0, and bit 0 of CTR2.

16

Figure 11. Port 3 Counter/Timer Output Configuration

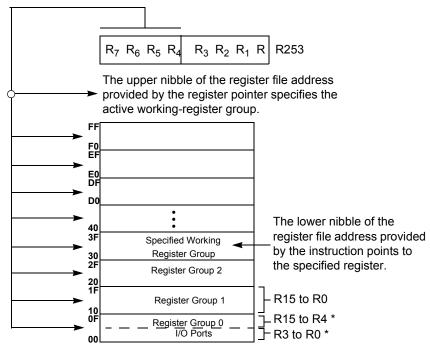

register RP select the working register group. Bits 3–0 of register RP select the expanded register file bank.

**Note:** An expanded register bank is also referred to as an expanded register group (see Figure 13).

\* RP = 00: Selects Register Bank 0, Working Register Group 0

Figure 15. Register Pointer—Detail

#### Stack

The internal register file is used for the stack. An 8-bit Stack Pointer SPL (R255) is used for the internal stack that resides in the general-purpose registers (R4–R239). SPH (R254) can be used as a general-purpose register.

#### Timers

#### T8\_Capture\_HI—HI8(D)0Bh

This register holds the captured data from the output of the 8-bit Counter/Timer0. Typically, this register holds the number of counts when the input signal is 1.

| Field         | Bit Position |     | Description             |  |  |

|---------------|--------------|-----|-------------------------|--|--|

| T8_Capture_HI | [7:0]        | R/W | Captured Data—No Effect |  |  |

### Table 8. CTR1(0D)01h T8 and T16 Common Functions

| Field             | <b>Bit Position</b> |     | Value | Description           |

|-------------------|---------------------|-----|-------|-----------------------|

| Mode              | 7                   | R/W | 0*    | TRANSMIT Mode         |

|                   |                     |     | 1     | DEMODULATION Mode     |

| P36_Out/          | -б                  | R/W |       | TRANSMIT Mode         |

| Demodulator Input |                     |     | 0*    | Port Output           |

|                   |                     |     | 1     | T8/T16 Output         |

|                   |                     |     |       | DEMODULATION Mode     |

|                   |                     |     | 0*    | P31                   |

|                   |                     |     | 1     | P20                   |

| T8/T16_Logic/     | 54                  | R/W |       | TRANSMIT Mode         |

| Edge _Detect      |                     |     | 00**  | AND                   |

| <b>5 –</b>        |                     |     | 01    | OR                    |

|                   |                     |     | 10    | NOR                   |

|                   |                     |     | 11    | NAND                  |

|                   |                     |     |       | DEMODULATION Mode     |

|                   |                     |     | 00**  | Falling Edge          |

|                   |                     |     | 01    | Rising Edge           |

|                   |                     |     | 10    | Both Edges            |

|                   |                     |     | 11    | Reserved              |

| Transmit_Submode/ | 32                  | R/W |       | TRANSMIT Mode         |

| Glitch_Filter     |                     |     | 00*   | Normal Operation      |

|                   |                     |     | 01    | PING-PONG Mode        |

|                   |                     |     | 10    | T16_Out = 0           |

|                   |                     |     | 11    | T16_Out = 1           |

|                   |                     |     |       | DEMODULATION Mode     |

|                   |                     |     | 00*   | No Filter             |

|                   |                     |     | 01    | 4 SCLK Cycle          |

|                   |                     |     | 10    | 8 SCLK Cycle          |

|                   |                     |     | 11    | Reserved              |

| Initial_T8_Out/   | 1-                  |     |       | TRANSMIT Mode         |

| Rising Edge       |                     | R/W | 0*    | T8_OUT is 0 Initially |

|                   |                     |     | 1     | T8_OUT is 1 Initially |

|                   |                     |     |       | DEMODULATION Mode     |

|                   |                     | R   | 0*    | No Rising Edge        |

|                   |                     |     | 1     | Rising Edge Detected  |

|                   |                     | W   | 0     | No Effect             |

|                   |                     |     | 1     | Reset Flag to 0       |

#### **T8 TRANSMIT Mode**

Before T8 is enabled, the output of T8 depends on CTR1, D1. If it is 0, T8\_OUT is 1; if it is 1, T8\_OUT is 0. See Figure 17.

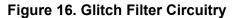

#### SCLK/TCLK Divide-by-16 Select (D0)

D0 of the SMR controls a divide-by-16 prescaler of SCLK/TCLK (see Figure 32). This control selectively reduces device power consumption during normal processor execution (SCLK control) and/or HALT mode (where TCLK sources interrupt logic). After Stop Mode Recovery, this bit is set to a 0.

Figure 32. SCLK Circuit

#### Stop Mode Recovery Source (D2, D3, and D4)

These three bits of the SMR specify the wake-up source of the Stop recovery (see Figure 33 and Table 14).

#### Stop Mode Recovery Register 2—SMR2(F)0Dh

Table 13 lists and briefly describes the fields for this register.

| Field             | Bit Position | Value               | Description          |

|-------------------|--------------|---------------------|----------------------|

| Reserved          | 7            | 0                   | Reserved (Must be 0) |

| Recovery<br>Level | -6 W         | 0 <sup>†</sup><br>1 | Low<br>High          |

| Reserved          | 5            | 0                   | Reserved (Must be 0) |

# zilog ,

### Table 13. SMR2(F)0Dh:Stop Mode Recovery Register 2\* (Continued)

| Field           | <b>Bit Position</b>   | Value              | Description                  |

|-----------------|-----------------------|--------------------|------------------------------|

| Source          | 432 \                 | N 000 <sup>†</sup> | A. POR Only                  |

|                 |                       | 001                | B. NAND of P23–P20           |

|                 |                       | 010                | C. NAND of P27–P20           |

|                 |                       | 011                | D. NOR of P33–P31            |

|                 |                       | 100                | E. NAND of P33–P31           |

|                 |                       | 101                | F. NOR of P33–P31, P00, P07  |

|                 |                       | 110                | G. NAND of P33–P31, P00, P07 |

|                 |                       | 111                | H. NAND of P33–P31, P22–P20  |

| Reserved        | 10                    | 00                 | Reserved (Must be 0)         |

| *Port pins cont | figured as outputs ar | e ignored          | as an SMR recovery source.   |

<sup>†</sup>Indicates the value upon Power-On Reset.

51

#### WDT Time Select (D0, D1)

This bit selects the WDT time period. It is configured as indicated in Table 15.

#### Table 15. Watchdog Timer Time Select

| D1 | D0 | Timeout of Internal RC-Oscillator |

|----|----|-----------------------------------|

| 0  | 0  | 5 ms min                          |

| 0  | 1  | 10 ms min                         |

| 1  | 0  | 20 ms min                         |

| 1  | 1  | 80 ms min                         |

#### WDTMR During Halt (D2)

This bit determines whether or not the WDT is active during HALT mode. A 1 indicates active during HALT. The default is 1, see Figure 36.

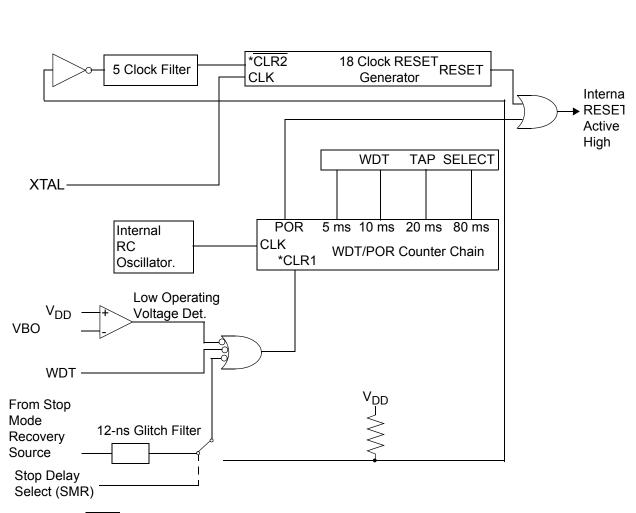

\* CLR1 and CLR2 enable the WDT/POR and 18 Clock Reset timers respectively upon a Low-to-High

#### Figure 36. Resets and WDT

#### WDTMR During STOP (D3)

This bit determines whether or not the WDT is active during STOP mode. A 1 indicates active during Stop. The default is 1.

#### **EPROM Selectable Options**

There are seven EPROM Selectable Options to choose from based on ROM code requirements. These are listed in Table 16.

Crimzon<sup>®</sup> ZLP32300 Product Specification

zilog

Ensure to differentiate the TRANSMIT mode from DEMODULATION 1. mode. Depending on which of these two modes is operating, the CTR1 bit has different functions.

2. Changing from one mode to another cannot be performed without disabling the counter/timers.

#### CTR2(0D)02H

| D7 | D6                         | D5      | D4 | D3 | D2      | D1       | D0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----|----------------------------|---------|----|----|---------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                            |         |    |    |         |          |         | <ul> <li>0 P35 is Port Output *</li> <li>1 P35 is TC16 Output</li> <li>0 Disable T16 Timeout Interrupt*</li> <li>1 Enable T16 Timeout Interrupt</li> <li>0 Disable T16 Data Capture Interrupt**</li> <li>1 Enable T16 Data Capture Interrupt</li> <li>0 0 SCLK on T16**</li> <li>0 1 SCLK/2 on T16</li> <li>1 0 SCLK/4 on T16</li> <li>1 1 SCLK/8 on T16</li> <li>R 0 No T16 Timeout**</li> <li>R 1 T16 Timeout Occurs</li> <li>W 0 No Effect</li> <li>W 1 Reset Flag to 0</li> </ul> |

|    | ult set<br>ault se<br>Reco | tting a |    |    | t reset | t with a | Stop Mo | TRANSMIT Mode<br>0 Modulo-N for T16*<br>1 Single Pass for T16<br>DEMODULATOR Mode<br>0 T16 Recognizes Edge<br>1 T16 Does Not Recognize Edge<br>R 0 T16 Disabled *<br>R 1 T16 Enabled<br>W 0 Stop T16<br>W 1 Enable T16                                                                                                                                                                                                                                                                |

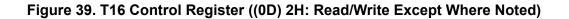

#### R249 IPR(F9H)

#### Figure 49. Interrupt Priority Register (F9H: Write Only)

zilog <sub>79</sub>

|    |                  | T <sub>A</sub> =0 °C to +70 °C<br>8.0 MHz |                 |                         |      |       |       | Watchdog<br>Timer<br>Mode |  |

|----|------------------|-------------------------------------------|-----------------|-------------------------|------|-------|-------|---------------------------|--|

| No | Symbol           | Parameter                                 | v <sub>cc</sub> | / <sub>CC</sub> Minimum |      | Units | Notes | Register                  |  |

| 1  | ТрС              | Input Clock Period                        | 2.0–3.6         | 121                     | DC   | ns    | 1     |                           |  |

| 2  | TrC,TfC          | Clock Input Rise and Fall Times           | 2.0–3.6         |                         | 25   | ns    | 1     |                           |  |

| 3  | TwC              | Input Clock Width                         | 2.0–3.6         | 37                      |      | ns    | 1     |                           |  |

| 4  | TwTinL           | Timer Input<br>Low Width                  | 2.0<br>3.6      | 100<br>70               |      | ns    | 1     |                           |  |

| 5  | TwTinH           | Timer Input High<br>Width                 | 2.0–3.6         | 3TpC                    |      |       | 1     |                           |  |

| 6  | TpTin            | Timer Input Period                        | 2.0–3.6         | 8TpC                    |      |       | 1     |                           |  |

| 7  | TrTin,TfTin      | Timer Input Rise and Fall Timers          | 2.0–3.6         |                         | 100  | ns    | 1     |                           |  |

| 8  | TwIL             | Interrupt Request<br>Low Time             | 2.0<br>3.6      | 100<br>70               |      | ns    | 1, 2  |                           |  |

| 9  | TwlH             | Interrupt Request<br>Input High Time      | 2.0–3.6         | 5TpC                    |      |       | 1, 2  |                           |  |

| 10 | Twsm             | Stop Mode Recovery<br>Width Spec          | 2.0–3.6         | 12                      |      | ns    | 3     |                           |  |

|    |                  | ·                                         |                 | 10TpC                   |      |       | 4     |                           |  |

| 11 | Tost             | Oscillator<br>Start-Up Time               | 2.0–3.6         |                         | 5TpC |       | 4     |                           |  |

| 12 | Twdt             | Watchdog Timer                            | 2.0–3.6         | 5                       |      | ms    |       | 0, 0                      |  |

|    |                  | Delay Time                                | 2.0–3.6         | 10                      |      | ms    |       | 0, 1                      |  |

|    |                  |                                           | 2.0–3.6         | 20                      |      | ms    |       | 1, 0                      |  |

|    |                  |                                           | 2.0–3.6         | 80                      |      | ms    |       | 1, 1                      |  |

| 13 | T <sub>POR</sub> | Power-on reset                            | 2.0–3.6         | 2.5                     | 10   | ms    |       |                           |  |

#### **Table 20. AC Characteristics**

Notes

1. Timing Reference uses 0.9  $V_{CC}$  for a logic 1 and 0.1  $V_{CC}$  for a logic 0. 2. Interrupt request through Port 3 (P33–P31).

3. SMR–D5 = 1.

4. SMR–D5 = 0.

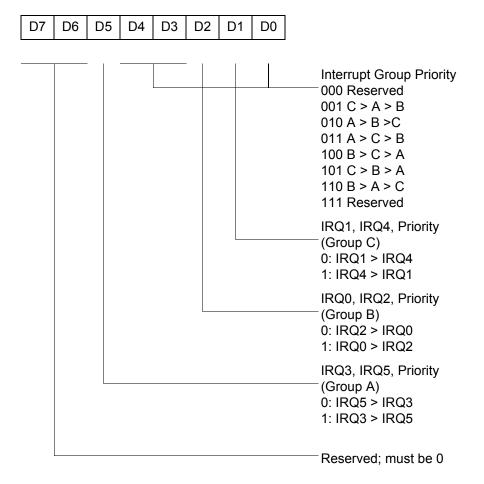

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

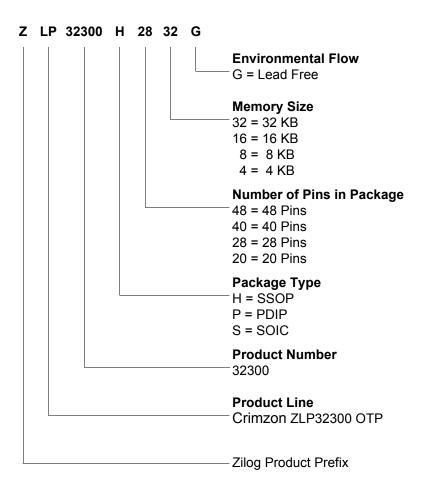

# **Part Number Description**

Zilog<sup>®</sup> part numbers consist of a number of components, as shown below. ZLP32300H2832G is a Crimzon ZLP32300 OTP product in a 28-pin SSOP package, with 32 KB of OTP and built with lead-free solder.

#### 93

## 0

oscillator configuration 46 output circuit, counter/timer 43

#### Ρ

package information 20-pin DIP package diagram 80 20-pin SSOP package diagram 82 28-pin DIP package diagram 84 28-pin SOIC package diagram 83 28-pin SSOP package diagram 85 40-pin DIP package diagram 85 48-pin SSOP package diagram 86 part number format 89 pin configuration 20-pin DIP/SOIC/SSOP 5 28-pin DIP/SOIC/SSOP 6 40- and 48-pin 8 40-pin DIP **7** 48-pin SSOP 8 pin functions port 0 (P07 - P00) 11 port 0 (P17 - P10) 12 port 0 configuration 12 port 1 configuration 13 port 2 (P27 - P20) 13 port 2 (P37 - P30) 14 port 2 configuration 14 port 3 configuration 15 port 3 counter/timer configuration 17 reset) 18 XTAL1 (time-based input 10 XTAL2 (time-based output) 10 port 0 configuration 12 port 0 pin function 11 port 1 configuration 13 port 1 pin function 12 port 2 configuration 14 port 2 pin function 13 port 3 configuration 15 port 3 pin function 14 port 3counter/timer configuration 17 port configuration register 48

power connections 1 power supply 5 program memory 19 map 20

## R

ratings, absolute maximum 75 register 54 CTR(D)01h 28 CTR0(D)00h 27 CTR2(D)02h 31 CTR3(D)03h 33 flag 73 HI16(D)09h 26 HI8(D)0Bh 25 interrupt priority 71 interrupt request 72 interruptmask 72 L016(D)08h 26 L08(D)0Ah 26 LVD(D)0Ch 58 pointer 73 port 0 and 1 70 port 2 configuration 69 port 3 mode 69 port configuration 48, 69 SMR2(F)0Dh 33 stack pointer high 74 stack pointer low 74 stop mode recovery 49 stop mode recovery 2 54 stop mode recovery 66 stop mode recovery 2 67 T16 control 62 T8 and T16 common control functions 61 T8/T16 control 63 TC16H(D)07h 26 TC16L(D)06h 26 TC8 control 60 TC8H(D)05h 27 TC8L(D)04h 27 voltage detection 64 watch-dog timer 68

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <a href="http://www.zilog.com/kb">http://www.zilog.com/kb</a>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.