Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betails                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                 |

| Core Processor             | 80C52                                                                                    |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 24MHz                                                                                    |

| Connectivity               | EBI/EMI, Serial Port                                                                     |

| Peripherals                | POR, WDT                                                                                 |

| Number of I/O              | 36                                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1.25K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 44-BQFP                                                                                  |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w78l516a24fl |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Pin Description, continued

| SYMBOL        | TYPE | DESCRIPTIONS                                                                                                                                                                |

|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |      | <b>PORT 3:</b> Port 3 is a bi-directional I/O port with internal pull-ups. All bits have alternate functions, which are described below:                                    |

|               |      | RXD(P3.0) : Serial Port 0 input                                                                                                                                             |

|               |      | TXD(P3.1) : Serial Port 0 output                                                                                                                                            |

|               |      | INT0 (P3.2) : External Interrupt 0                                                                                                                                          |

| P3.0–P3.7 I/O | I/O  | INT1 (P3.3) : External Interrupt 1                                                                                                                                          |

|               |      | T0(P3.4) : Timer 0 External Input                                                                                                                                           |

|               |      | T1(P3.5) : Timer 1 External Input                                                                                                                                           |

|               |      | WR (P3.6) : External Data Memory Write Strobe                                                                                                                               |

|               |      | RD (P3.7) : External Data Memory Read Strobe                                                                                                                                |

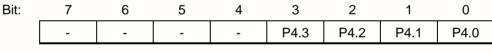

|               |      | PORT 4: Port 4 is a 4-bit bi-directional I/O port. The P4.0 also provides the                                                                                               |

| P4.0-P4.3     | I/O  | alternate function $\overline{\text{WAIT}}$ which is the wait state control signal. The P4.3 also provide the alternate function /REBOOT which is H/W reboot from LD flash. |

\* Note: TYPE I: input, O: output, I/O: bi-directional.

#### Timers

The W77L516A has three 16-bit timers that are functionally similar to the timers of the 8052 family. When used as timers, they can be set to run at either 4 clocks or 12 clocks per count, thus providing the user with the option of operating in a mode that emulates the timing of the original 8052. The W77L516A has an additional feature, the watchdog timer. This timer is used as a System Monitor or as a very long time period timer.

#### Interrupts

The Interrupt structure in the W77L516A is slightly different from that of the standard 8052. Due to the presence of additional features and peripherals, the number of interrupt sources and vectors has been increased. The W77L516A provides 12 interrupt resources with two priority level, including six external interrupt sources, timer interrupts, serial I/O interrupts.

#### **Data Pointers**

The original 8052 had only one 16-bit Data Pointer (DPL, DPH). In the W77L516A, there is an additional 16-bit Data Pointer (DPL1, DPH1). This new Data Pointer uses two SFR locations which were unused in the original 8052. In addition there is an added instruction, DEC DPTR (op-code A5H), which helps in improving programming flexibility for the user.

#### **Power Management**

Like the standard 80C52, the W77L516A also has IDLE and POWER DOWN modes of operation. The W77L516A provides a new Economy mode which allow user to switch the internal clock rate divided by either 4, 64 or 1024. In the IDLE mode, the clock to the CPU core is stopped while the timers, serial ports and interrupts clock continue to operate. In the POWER DOWN mode, all the clock are stopped and the chip operation is completely stopped. This is the lowest power consumption state.

### **On-chip Data SRAM**

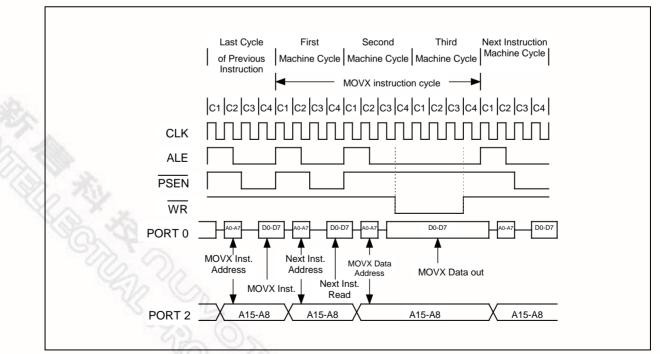

The W77L516A has 1K Bytes of data space SRAM which is read/write accessible and is memory mapped. This on-chip MOVX SRAM is reached by the MOVX instruction. It is not used for executable program memory. There is no conflict or overlap among the 256 bytes Scratchpad RAM and the 1K Bytes MOVX SRAM as they use different addressing modes and separate instructions. The on-chip MOVX SRAM is enabled by setting the DME0 bit in the PMR register. After a reset, the DME0 bit is cleared such that the on-chip MOVX SRAM is disabled, and all data memory spaces 0000H–FFFFH access to the external memory.

- 7 -

### W77L516A

# nuvoTon

| M1, M0: | Mode | Select | bits: |

|---------|------|--------|-------|

|---------|------|--------|-------|

#### M1 M0 Mode

- 0 0 Mode 0: 8-bits with 5-bit prescale.

- 0 1 Mode 1: 16-bits, no prescale.

- 1 0 Mode 2: 8-bits with auto-reload from THx

- 1 Mode 3: (Timer 0) TL0 is an 8-bit timer/counter controlled by the standard Timer 0 control bits. TH0 is a 8-bit timer only controlled by Timer 1 control bits. (Timer 1) Timer/counter is stopped.

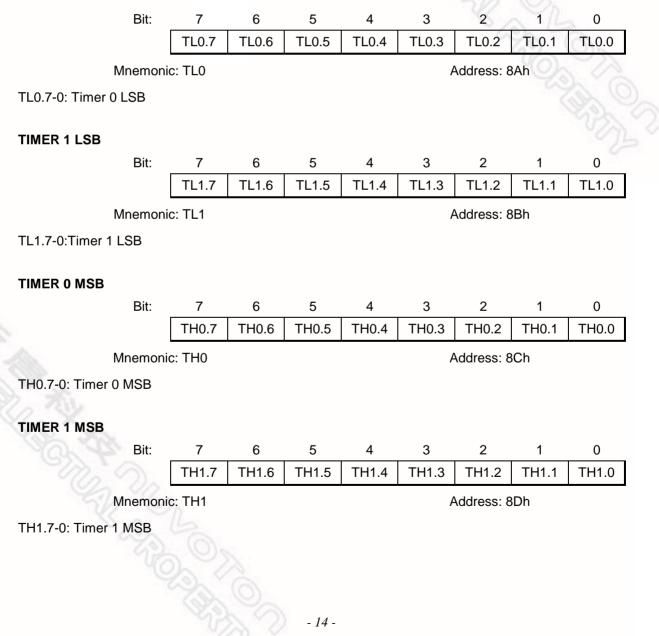

#### TIMER 0 LSB

| BIT NAME         | FUNCTION                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

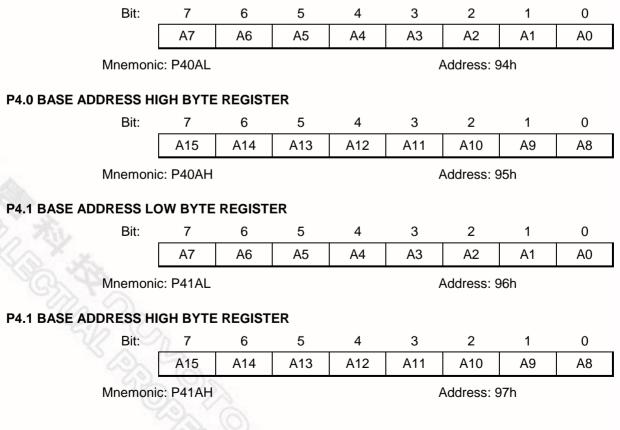

|                  | Port 4 alternate modes.                                                                                                                          |

|                  | =00: Mode 0. P4.x is a general purpose I/O port which is the same as Port 1.                                                                     |

| P4xM1, P4xM0     | =01: Mode 1. P4.x is a Read Strobe signal for chip select purpose. The address range depends on the SFR P4xAH, P4xAL and bits P4xC1, P4xC0.      |

| r4xivi1, r4xivi0 | =10: Mode 2. P4.x is a Write Strobe signal for chip select purpose. The address range depends on the SFR P4xAH, P4xAL and bits P4xC1, P4xC0.     |

|                  | =11: Mode 3. P4.x is a Read/Write Strobe signal for chip select purpose. The address range depends on the SFR P4xAH, P4xAL and bits P4xC1, P4xC0 |

|                  | Port 4 Chip-select Mode address comparison:                                                                                                      |

|                  | =00: Compare the full address (16 bits length) with the base address registers P4xAH and P4xAL.                                                  |

| P4xC1,P4xC0      | =01: Compare the 15 high bits (A15-A1) of address bus with the base address registers P4xAH and P4xAL.                                           |

|                  | =10: Compare the 14 high bits (A15-A2) of address bus with the base address registers P4xAH and P4xAL.                                           |

|                  | =11: Compare the 8 high bits (A15-A8) of address bus with the base address registers P4xAH and P4xAL.                                            |

### P4.0 BASE ADDRESS LOW BYTE REGISTER

Publication Release Date: December 4, 2008 Revision A9

words, device is not indeed in IDLE mode is set bit PCON.1 while ISP is enabled. Clear this bit to disable ISP mode, device get back to normal operation including IDLE state.

#### **Software Reset**

Set CHPCON = 0X83, timer and enter IDLE mode. CPU will reset and restart from APFLASH after time out.

#### PORT 2

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | P2.7 | P2.6 | P2.5 | P2.4 | P2.3 | P2.2 | P2.1 | P2.0 |

|      |      |      |      |      |      | ON S | (Ja  |      |

Mnemonic: P2

Address: A0h

P2.7-0: Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides the upper address bits for accesses to external memory.

#### PORT 4 CHIP-SELECT POLARITY

| Bit: | 7      | 6      | 5      | 4      | 3 | 2 | 123 | 0      |

|------|--------|--------|--------|--------|---|---|-----|--------|

|      | P43INV | P42INV | P42INV | P40INV | - | - | -   | POUP   |

|      |        |        |        |        |   |   |     | VI PAC |

Mnemonic: P4CSIN

Address: A2h

P4xINV: The active polarity of P4.x when set it as chip-select signal. High = Active High. Low = Active Low.

POUP: Enable Port 0 weak pull up.

#### PORT 4

Mnemonic: P4

Address: A5h

P4.3-0: Port 4 is a bi-directional I/O port with internal pull-ups. Port 4 can not use bit-addressable instruction (SETB or CLR).

#### **INTERRUPT ENABLE**

| Bit: | 7  | 6   | 5   | 4  | 3   | 2   | 1   | 0   |

|------|----|-----|-----|----|-----|-----|-----|-----|

|      | EA | ES1 | ET2 | ES | ET1 | EX1 | ET0 | EX0 |

#### Mnemonic: IE

Address: A8h

- EA: Global enable. Enable/disable all interrupts except for PFI.

- ES1: Enable Serial Port 1 interrupt.

- ET2: Enable Timer 2 interrupt.

- ES: Enable Serial Port 0 interrupt.

- ET1: Enable Timer 1 interrupt

- EX1: Enable external interrupt 1

- ET0: Enable Timer 0 interrupt

- EX0: Enable external interrupt 0

Revision A9

- 21 -

#### **SERIAL PORT CONTROL 1**

| Bit: | 7          | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|------|------------|-------|-------|-------|-------|-------|------|------|

|      | SM0_1/FE_1 | SM1_1 | SM2_1 | REN_1 | TB8_1 | RB8_1 | TI_1 | RI_1 |

|      |            |       |       | 1/23  |       |       |      |      |

Mnemonic: SCON1

Address: C0h

SM0\_1/FE\_1: Serial port 1, Mode 0 bit or Framing Error Flag 1: The SMOD0 bit in PCON SFR determines whether this bit acts as SM0\_1 or as FE\_1. the operation of SM0\_1 is described below. When used as FE\_1, this bit will be set to indicate an invalid stop bit. This bit must be manually cleared in software to clear the FE\_1 condition.

SM1\_1: Serial port 1 Mode bit 1:

| SM0_1 | SM1_1 | Mode | Description  | Length | Baud rate  |

|-------|-------|------|--------------|--------|------------|

| 0     | 0     | 0    | Synchronous  | 8      | 4/12 Tclk  |

| 0     | 1     | 1    | Asynchronous | 10     | variable   |

| 1     | 0     | 2    | Asynchronous | 11     | 64/32 Tclk |

| 1     | 1     | 3    | Asynchronous | 11     | variable   |

- SM2\_1: Multiple processors communication. Setting this bit to 1 enables the multiprocessor communication feature in mode 2 and 3. In mode 2 or 3, if SM2\_1 is set to 1, then RI\_1 will not be activated if the received 9th data bit (RB8\_1) is 0. In mode 1, if SM2\_1 = 1, then RI\_1 will not be activated if a valid stop bit was not received. In mode 0, the SM2\_1 bit controls the serial port 1 clock. If set to 0, then the serial port 1 runs at a divide by 12 clock of the oscillator. This gives compatibility with the standard 8052. When set to 1, the serial clock become divide by 4 of the oscillator clock. This results in faster synchronous serial communication.

- REN\_1: Receive enable: When set to 1 serial reception is enabled, otherwise reception is disabled.

- TB8\_1: This is the 9th bit to be transmitted in modes 2 and 3. This bit is set and cleared by software as desired.

- RB8\_1: In modes 2 and 3 this is the received 9th data bit. In mode 1, if SM2\_1 = 0, RB8\_1 is the stop bit that was received. In mode 0 it has no function.

- TI\_1: Transmit interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or at the beginning of the stop bit in all other modes during serial transmission. This bit must be cleared by software.

- RI\_1: Receive interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or halfway through the stop bits time in the other modes during serial reception. However the restrictions of SM2\_1 apply to this bit. This bit can be cleared only by software.

- 24 -

#### **TIMED ACCESS**

| -       |       |      |      |      |      |            |      |       |

|---------|-------|------|------|------|------|------------|------|-------|

| Bit:    | 7     | 6    | 5    | 4    | 3    | 2          | 1    | 0     |

|         | TA.7  | TA.6 | TA.5 | TA.4 | TA.3 | TA.2       | TA.1 | TfA.0 |

| Mnemoni | c: TA |      | 1    | 22   | ŀ    | Address: C | C7h  |       |

TA: The Timed Access register controls the access to protected bits. To access protected bits, the user must first write AAH to the TA. This must be immediately followed by a write of 55H to TA. Now a window is opened in the protected bits for three machine cycles, during which the user can write to these bits.

#### **TIMER 2 CONTROL**

| Bit:  | 7          | 6    | 5    | 4    | 3     | 2        | 12     | 0      |

|-------|------------|------|------|------|-------|----------|--------|--------|

|       | TF2        | EXF2 | RCLK | TCLK | EXEN2 | TR2      | C / T2 | CP/RL2 |

| Mnemo | onic: T2CC | N    |      |      |       | Address: | C8h    | 0/     |

- TF2: Timer 2 overflow flag: This bit is set when Timer 2 overflows. It is also set when the count is equal to the capture register in down count mode. It can be set only if RCLK and TCLK are both 0. It is cleared only by software. Software can also set or clear this bit.

- EXF2: Timer 2 External Flag: A negative transition on the T2EX pin (P1.1) or timer 2 overflow will cause this flag to set based on the CP/RL2, EXEN2 and DCEN bits. If set by a negative transition, this flag must be cleared by software. Setting this bit in software or detection of a negative transition on T2EX pin will force a timer interrupt if enabled.

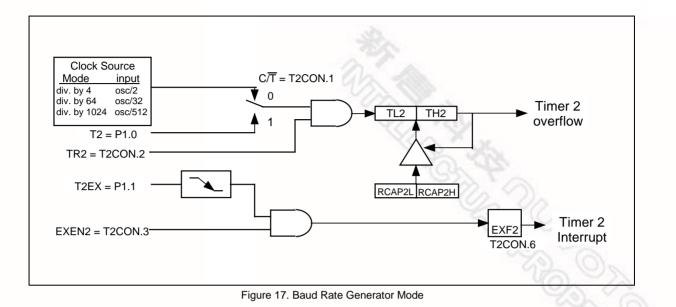

- RCLK: Receive Clock Flag: This bit determines the serial port 0 time-base when receiving data in serial modes 1 or 3. If it is 0, then timer 1 overflow is used for baud rate generation, otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.

- TCLK: Transmit Clock Flag: This bit determines the serial port 0 time-base when transmitting data in modes 1 and 3. If it is set to 0, the timer 1 overflow is used to generate the baud rate clock otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.

- EXEN2: Timer 2 External Enable. This bit enables the capture/reload function on the T2EX pin if Timer 2 is not generating baud clocks for the serial port. If this bit is 0, then the T2EX pin will be ignored, otherwise a negative transition detected on the T2EX pin will result in capture or reload.

- TR2: Timer 2 Run Control. This bit enables/disables the operation of timer 2. Clearing this bit will halt the timer 2 and preserve the current count in TH2, TL2.

- C / T2: Counter/Timer Select. This bit determines whether timer 2 will function as a timer or a counter. Independent of this bit, the timer will run at 2 clocks per tick when used in baud rate generator mode. If it is set to 0, then timer 2 operates as a timer at a speed depending on T2M bit (CKCON.5), otherwise it will count negative edges on T2 pin.

- CP / RL2: Capture/Reload Select. This bit determines whether the capture or reload function will be used for timer 2. If either RCLK or TCLK is set, this bit will be ignored and the timer will function in an auto-reload mode following each overflow. If the bit is 0 then auto-reload will occur when timer 2 overflows or a falling edge is detected on T2EX pin if EXEN2 = 1. If this

- 34 -

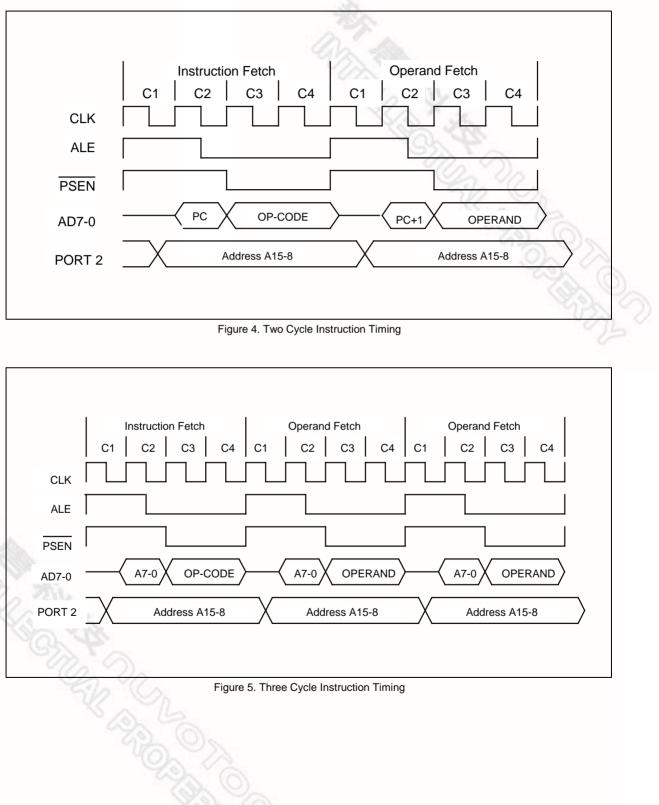

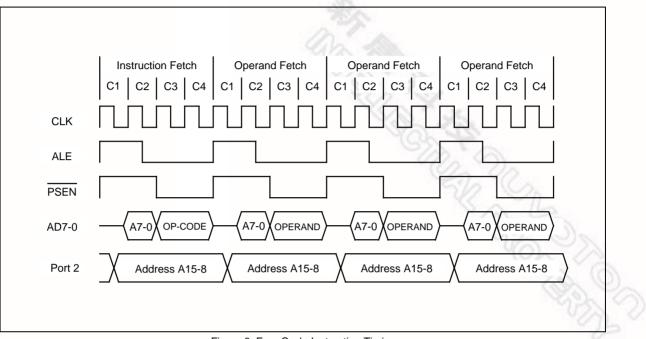

Figure 6. Four Cycle Instruction Timing

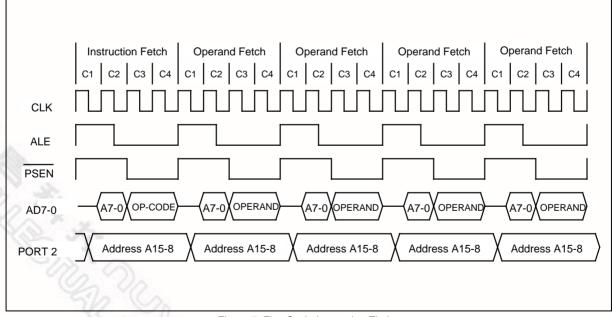

Figure 7. Five Cycle Instruction Timing

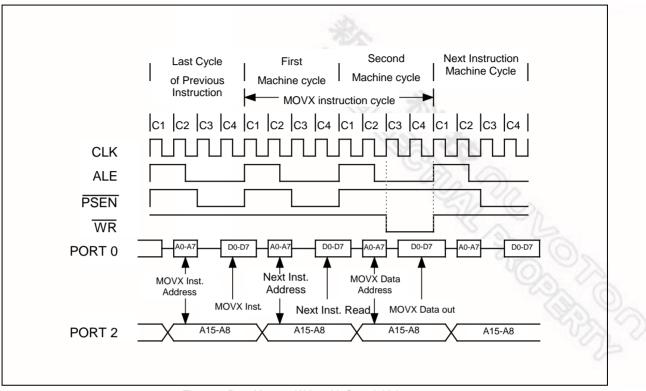

Figure 8. Data Memory Write with Stretch Value = 0

Figure 9. Data Memory Write with Stretch Value = 1

Publication Release Date: December 4, 2008 Revision A9

### 9. POWER MANAGEMENT

The W77L516A has several features that help the user to control the power consumption of the device. The power saving features are basically the POWER DOWN mode, ECONOMY mode and the IDLE mode of operation.

#### Idle Mode

The user can put the device into idle mode by writing 1 to the bit PCON.0. The instruction that sets the idle bit is the last instruction that will be executed before the device goes into Idle Mode. In the Idle mode, the clock to the CPU is halted, but not to the Interrupt, Timer, Watchdog timer and Serial port blocks. This forces the CPU state to be frozen; the Program counter, the Stack Pointer, the Program Status Word, the Accumulator and the other registers hold their contents. The ALE and PSEN pins are held high during the Idle state. The port pins hold the logical states they had at the time Idle was activated. The Idle mode can be terminated in two ways. Since the interrupt controller is still active, the activation of any enabled interrupt can wake up the processor. This will automatically clear the Idle bit, terminate the Idle mode, and the Interrupt Service Routine(ISR) will be executed. After the ISR, execution of the program will continue from the instruction which put the device into Idle mode.

The Idle mode can also be exited by activating the reset. The device can be put into reset either by applying a high on the external RST pin, a Power on reset condition or a Watchdog timer reset. The external reset pin has to be held high for at least two machine cycles i.e. 8 clock periods to be recognized as a valid reset. In the reset condition the program counter is reset to 0000h and all the SFRs are set to the reset condition. Since the clock is already running there is no delay and execution starts immediately. In the Idle mode, the Watchdog timer continues to run, and if enabled, a time-out will cause a watchdog timer interrupt which will wake up the device. The software must reset the Watchdog timer in order to preempt the reset which will occur after 512 clock periods of the time-out. When the W77L516A is exiting from an Idle mode with a reset, the instruction following the one which put the device into Idle mode is not executed. So there is no danger of unexpected writes.

#### **Economy Mode**

The power consumption of microcontroller relates to operating frequency. The W77L516A offers a Economy mode to reduce the internal clock rate dynamically without external components. By default, one machine cycle needs 4 clocks. In Economy mode, software can select 4, 64 or 1024 clocks per machine cycle. It keeps the CPU operating at a acceptable speed but eliminates the power consumption. In the Idle mode, the clock of the core logic is stopped, but all clocked peripherals such as watchdog timer are still running at a rate of clock/4. In the Economy mode, all clocked peripherals run at the same reduced clocks rate as in core logic. So the Economy mode may provide a lower power consumption than idle mode.

Software invokes the Economy mode by setting the appropriate bits in the SFRs. Setting the bits CD0(PMR.6), CD1(PMR.7) decides the instruction cycle rate as below:

### CD1 CD0 clocks/machine cycle

| 0 | 0  | Reserved    |

|---|----|-------------|

| 0 | 10 | 4 (default) |

| 1 | 0  | 64<br>1024  |

| 1 | 1  | 1024        |

|   |    |             |

|   |    |             |

|   |    |             |

|   |    |             |

|   |    |             |

|   |    |             |

|   |    |             |

### 12. PROGRAMMABLE TIMERS/COUNTERS

The W77L516A has three 16-bit programmable timer/counters and one programmable Watchdog timer. The Watchdog timer is operationally quite different from the other two timers.

### **TIMER/COUNTERS 0 & 1**

The W77L516A has two 16-bit Timer/Counters. Each of these Timer/Counters has two 8 bit registers which form the 16 bit counting register. For Timer/Counter 0 they are TH0, the upper 8 bits register, and TL0, the lower 8 bit register. Similarly Timer/Counter 1 has two 8 bit registers, TH1 and TL1. The two can be configured to operate either as timers, counting machine cycles or as counters counting external inputs.

When configured as a "Timer", the timer counts clock cycles. The timer clock can be programmed to be thought of as 1/12 of the system clock or 1/4 of the system clock. In the "Counter" mode, the register is incremented on the falling edge of the external input pin, T0 in case of Timer 0, and T1 for Timer 1. The T0 and T1 inputs are sampled in every machine cycle at C4. If the sampled value is high in one machine cycle and low in the next, then a valid high to low transition on the pin is recognized and the count register is incremented. Since it takes two machine cycles to recognize a negative transition on the pin, the maximum rate at which counting will take place is 1/24 of the master clock frequency. In either the "Timer" or "Counter" mode, the count register will be updated at C3. Therefore, in the "Timer" mode, the recognized negative transition on pin T0 and T1 can cause the count register value to be updated only in the machine cycle following the one in which the negative edge was detected.

The "Timer" or "Counter" function is selected by the " $C/\overline{T}$ " bit in the TMOD Special Function Register. Each Timer/Counter has one selection bit for its own; bit 2 of TMOD selects the function for Timer/Counter 0 and bit 6 of TMOD selects the function for Timer/Counter 1. In addition each Timer/Counter can be set to operate in any one of four possible modes. The mode selection is done by bits M0 and M1 in the TMOD SFR.

#### **Time-Base Selection**

The W77L516A gives the user two modes of operation for the timer. The timers can be programmed to operate like the standard 8051 family, counting at the rate of 1/12 of the clock speed. This will ensure that timing loops on the W77L516A and the standard 8051 can be matched. This is the default mode of operation of the W77L516A timers. The user also has the option to count in the turbo mode, where the timers will increment at the rate of 1/4 clock speed. This will straight-away increase the counting speed three times. This selection is done by the T0M and T1M bits in CKCON SFR. A reset sets these bits to 0, and the timers then operate in the standard 8051 mode. The user should set these bits to 1 if the timers are to operate in turbo mode.

### MODE 0

In Mode 0, the timer/counters act as a 8 bit counter with a 5 bit, divide by 32 pre-scale. In this mode we have a 13 bit timer/counter. The 13 bit counter consists of 8 bits of THx and 5 lower bits of TLx. The upper 3 bits of TLx are ignored.

The negative edge of the clock increments the count in the TLx register. When the fifth bit in TLx moves from 1 to 0, then the count in the THx register is incremented. When the count in THx moves from FFh to 00h, then the overflow flag TFx in TCON SFR is set. The counted input is enabled only if TRx is set and either GATE = 0 or  $\overline{INTx}$  = 1. When C /  $\overline{T}$  is set to 0, then it will count clock cycles, and

if  $C/\overline{T}$  is set to 1, then it will count 1 to 0 transitions on T0 (P3.4) for timer 0 and T1 (P3.5) for timer 1. When the 13 bit count reaches 1FFFh the next count will cause it to roll-over to 0000h. The timer overflow flag TFx of the relevant timer is set and if enabled an interrupts will occur. Note that when

### **PROGRAMMABLE CLOCK-OUT**

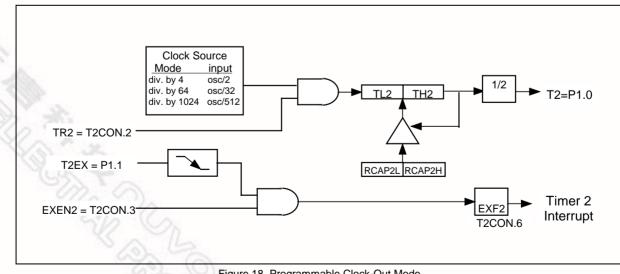

Timer 2 is equipped with a new clock-out feature which outputs a 50% duty cycle clock on P1.0. It can be invoked as a programmable clock generator. To configure Timer 2 with clock-out mode, software must initiate it by setting bit T2OE = 1, C/T2 = 0 and CP/RL = 0. Setting bit TR2 will start the timer. This mode is similar to the baud rate generator mode, it will not generate an interrupt while Timer 2 overflow. So it is possible to use Timer 2 as a baud rate generator and a clock generator at the same time. The clock-out frequency is determined by the following equation:

### The Clock-Out Frequency = Oscillator Frequency / [4 X (65536-RCAP2H, RCAP2L)]

Figure 18. Programmable Clock-Out Mode

Publication Release Date: December 4, 2008 Revision A9

Example 5: Invalid Access

| MOV  | TA, #0AAh | 3 M/C |

|------|-----------|-------|

| NOP  |           | 1 M/C |

| MOV  | TA, #055h | 3 M/C |

| SETB | EWT       | 2 M/C |

In the first two examples, the writing to the protected bits is done before the 3 machine cycle window closes. In Example 3, however, the writing to the protected bit occurs after the window has closed, and so there is effectively no change in the status of the protected bit. In Example 4, the second write to TA occurs 4 machine cycles after the first write, therefore the timed access window in not opened at all, and the write to the protected bit fails.

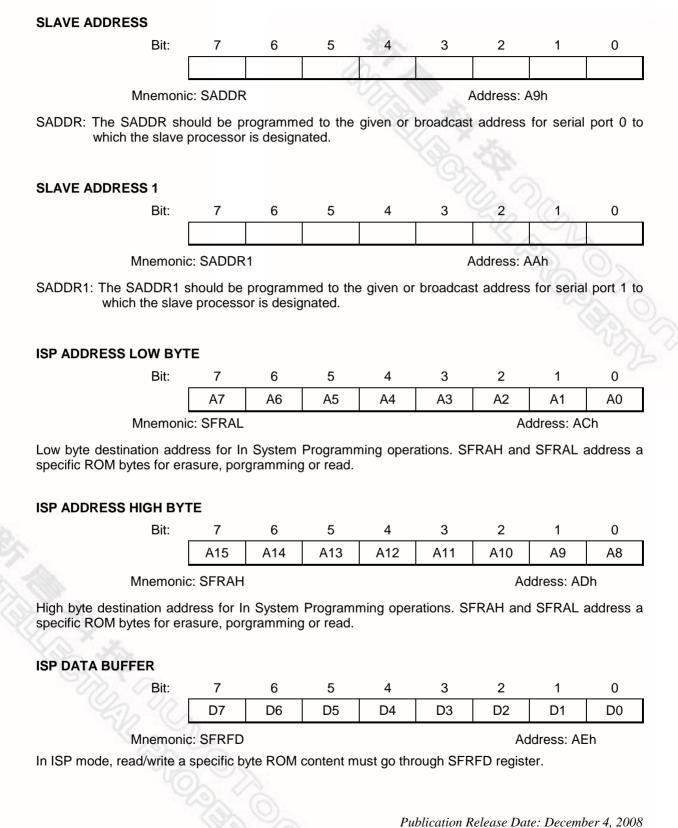

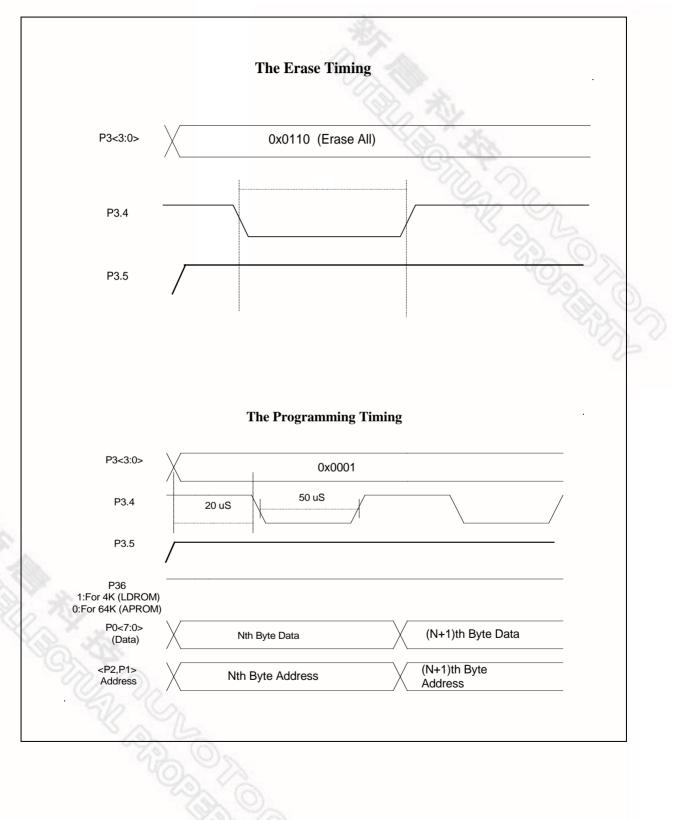

### **15. IN-SYSTEM PROGRAMMING**

### 15.1 The Loader Program locates at LDFLASH memory.

CPU is Free Run at APFLASH memory. CHPCON register had been set #03H value before CPU has entered idle state. CPU will switch to LDFLASH memory and execute a reset action. H/W reboot mode will switch to LDFLASH memory, too. Set SFRCN register where it locates at user's loader program to update APFLASH memory. Set a SWRESET (CHPCON = #83H) to switch back APFLASH after CPU has updated APFLASH program. CPU will restart to run program from reset state.

### 15.2 The Loader Program locates at APFLASH memory.

CPU is Free Run at APFLASH memory. CHPCON register had been set #01H value before CPU has entered idle state. Set SFRCN register to update LDFLASH. CPU will continue to run user's APFLASH program after CPU has updated program. Please refer demonstrative code to understand other detail description.

|    | -  | -  |                  |                      |

|----|----|----|------------------|----------------------|

| M2 | M1 | MO | MOVX CYCLES      | T <sub>MCS</sub>     |

| 0  | 0  | 0  | 2 machine cycles | 0                    |

| 0  | 0  | 1  | 3 machine cycles | 4 t <sub>CLCL</sub>  |

| 0  | 1  | 0  | 4 machine cycles | 8 t <sub>CLCL</sub>  |

| 0  | 1  | 1  | 5 machine cycles | 12 t <sub>CLCL</sub> |

| 1  | 0  | 0  | 6 machine cycles | 16 t <sub>CLCL</sub> |

| 1  | 0  | 1  | 7 machine cycles | 20 t <sub>CLCL</sub> |

| 1  | 1  | 0  | 8 machine cycles | 24 t <sub>CLCL</sub> |

| 1  | 1  | 1  | 9 machine cycles | 28 t <sub>CLCL</sub> |

### **EXPLANATION OF LOGIC SYMBOLS**

In order to maintain compatibility with the original 8051 family, this device specifies the same parameter for each device, using the same symbols. The explanation of the symbols is as follows.

| t | Time                    | А | Address         |

|---|-------------------------|---|-----------------|

| С | Clock                   | D | Input Data      |

| Н | Logic level high        | L | Logic level low |

| I | Instruction             | Р | PSEN            |

| Q | Output Data             | R | RD signal       |

| V | Valid                   | W | WR signal       |

| Х | No longer a valid state | Z | Tri-state       |

# ηυνοτοη

| MOV TA, #AAH<br>MOV TA, #55H<br>MOV CHPCON, #03H<br>MOV SFRCN, #0H<br>MOV TCON, #00H<br>MOV TMOD, #01H<br>MOV IP, #00H<br>MOV IP, #00H<br>MOV IE, #82H<br>MOV R6, #F0H<br>MOV R6, #F0H<br>MOV R7, #FFH<br>MOV TL0, R6<br>MOV TH0, R7<br>MOV TCON, #10H<br>MOV PCON, #01H | ; CHPCON = 03H, ENABLE IN-SYSTEM PROGRAMMING.<br>; TCON = 00H, TR = 0 TIMER0 STOP<br>; TMOD = 01H, SET TIMER0 A 16BIT TIMER<br>; IP = 00H<br>; IE = 82H, TIMER0 INTERRUPT ENABLED<br>; TCON = 10H, TR0 = 1, GO<br>; ENTER IDLE MODE |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPDATE_64K:                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                     |

| MOV TCON,#00H<br>MOV IP, #00H<br>MOV IE, #82H<br>MOV TMOD, #01H<br>MOV R6, #D0H<br>MOV R7, #8AH<br>MOV TL0, R6<br>MOV TH0, R7                                                                                                                                            | ; TCON = 00H , TR = 0 TIM0 STOP<br>; IP = 00H<br>; IE = 82H, TIMER0 INTERRUPT ENABLED<br>; TMOD = 01H, MODE1<br>; SET WAKE-UP TIME FOR ERASE OPERATION, ABOUT 15 ms<br>DEPENDING ON USER'S SYSTEM CLOCK RATE.                       |

|                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                     |

| ERASE_P_4K:<br>MOV_SFRCN, #22H                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                     |

| MOV SFRON, #22H<br>MOV TCON, #10H<br>MOV PCON, #01H                                                                                                                                                                                                                      | ; SFRCN = 22H, ERASE 64K_APFLASH<br>; TCON = 10H, TR0 = 1,GO<br>; ENTER IDLE MODE (FOR ERASE OPERATION)                                                                                                                             |

| •*************************************                                                                                                                                                                                                                                   | ********************                                                                                                                                                                                                                |

| ;* BLANK CHECK                                                                                                                                                                                                                                                           | ************                                                                                                                                                                                                                        |

| ,<br>MOV SFRCN, #0H<br>MOV SFRAH, #0H<br>MOV SFRAL, #0H<br>MOV R6, #FDH<br>MOV R7, #FFH<br>MOV TL0, R6<br>MOV TH0, R7                                                                                                                                                    | ; SFRCN = 00H, READ 64KB APFLASH<br>; START ADDRESS = 0H<br>; SET TIMER FOR READ OPERATION, ABOUT 1.5 μS.                                                                                                                           |

| BLANK_CHECK_LOOP:                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                     |

| SETB TR0<br>MOV PCON, #01H<br>MOV A, SFRFD<br>CJNE A, #FFH, BLANK<br>INC SFRAL<br>MOV A, SFRAL<br>JNZ BLANK_CHECK_I<br>INC SFRAH<br>MOV A, SFRAH<br>CJNE A, #0H, BLANK_C<br>JMP PROGRAM_64KR                                                                             | ; NEXT ADDRESS<br>_OOP<br>CHECK_LOOP ; END ADDRESS = FFFFH                                                                                                                                                                          |

| BLANK_CHECK_ERROR:                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                     |

| JMP \$                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                          | - 86 -                                                                                                                                                                                                                              |