Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

-XE

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Active                                                                      |

| Architecture            | MCU, FPGA                                                                   |

| Core Processor          | ARM® Cortex®-M3                                                             |

| Flash Size              | 512KB                                                                       |

| RAM Size                | 64KB                                                                        |

| Peripherals             | DMA, POR, WDT                                                               |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                        |

| Speed                   | 80MHz                                                                       |

| Primary Attributes      | ProASIC®3 FPGA, 500K Gates, 11520 D-Flip-Flops                              |

| Operating Temperature   | -55°C ~ 125°C (TJ)                                                          |

| Package / Case          | 256-LBGA                                                                    |

| Supplier Device Package | 256-FPBGA (17x17)                                                           |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f500m3g-fgg256m |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Microsemi**

Military Grade SmartFusion Customizable System-on-Chip (cSoC)

## SmartFusion cSoC Family Product Table

| SmartFusion <sup>®</sup> cSoC      |                                             | A2F060        | A2F500          |  |  |  |

|------------------------------------|---------------------------------------------|---------------|-----------------|--|--|--|

| FPGA Fabric                        | System Gates                                | 60,000        | 500,000         |  |  |  |

|                                    | Tiles (D-flip-flops)                        | 1,536         | 11,520          |  |  |  |

|                                    | RAM Blocks (4,608 bits)                     | 8             | 24              |  |  |  |

| Microcontroller<br>Subsystem (MSS) | Flash (Kbytes)                              | 128           | 512             |  |  |  |

|                                    | SRAM (Kbytes)                               | 16            | 64              |  |  |  |

|                                    | Cortex-M3 with memory protection unit (MPU) | Ye            | es              |  |  |  |

|                                    | 10/100 Ethernet MAC                         | No            | Yes             |  |  |  |

|                                    | External Memory Controller (EMC)            | 24-bit addres | s,16-bit data   |  |  |  |

|                                    | DMA                                         | 8 (           | Ch              |  |  |  |

|                                    | l <sup>2</sup> C                            | 2             |                 |  |  |  |

|                                    | SPI                                         | 2             |                 |  |  |  |

|                                    | 16550 UART                                  | 2             | 2               |  |  |  |

|                                    | 32-Bit Timer                                | 2             | 2               |  |  |  |

|                                    | PLL                                         | 1             | 2 <sup>1</sup>  |  |  |  |

|                                    | 32 KHz Low Power Oscillator                 | 1             |                 |  |  |  |

|                                    | 100 MHz On-Chip RC Oscillator               | 1             |                 |  |  |  |

|                                    | Main Oscillator (32 KHz to 20 MHz)          | 1             |                 |  |  |  |

| Programmable Analog                | ADCs (8-/10-/12-bit SAR)                    | 1             | 3 <sup>3</sup>  |  |  |  |

|                                    | DACs (12-bit sigma-delta)                   | 1             | 3 <sup>3</sup>  |  |  |  |

|                                    | Signal Conditioning Blocks (SCBs)           | 1             | 5 <sup>3</sup>  |  |  |  |

|                                    | Comparator <sup>2</sup>                     | 2             | 10 <sup>3</sup> |  |  |  |

|                                    | Current Monitors <sup>2</sup>               | 1             | 5 <sup>3</sup>  |  |  |  |

|                                    | Temperature Monitors <sup>2</sup>           | 1             | 5 <sup>3</sup>  |  |  |  |

|                                    | Bipolar High Voltage Monitors <sup>2</sup>  | 2             | 10 <sup>3</sup> |  |  |  |

Notes:

Two PLLs are available in FG484 (one PLL in FG256).

These functions share I/O pins and may not all be available at the same time. See the "Analog Front-End Overview" section in the SmartFusion Programmable Analog User's Guide for details.

3. Available on FG484 only.

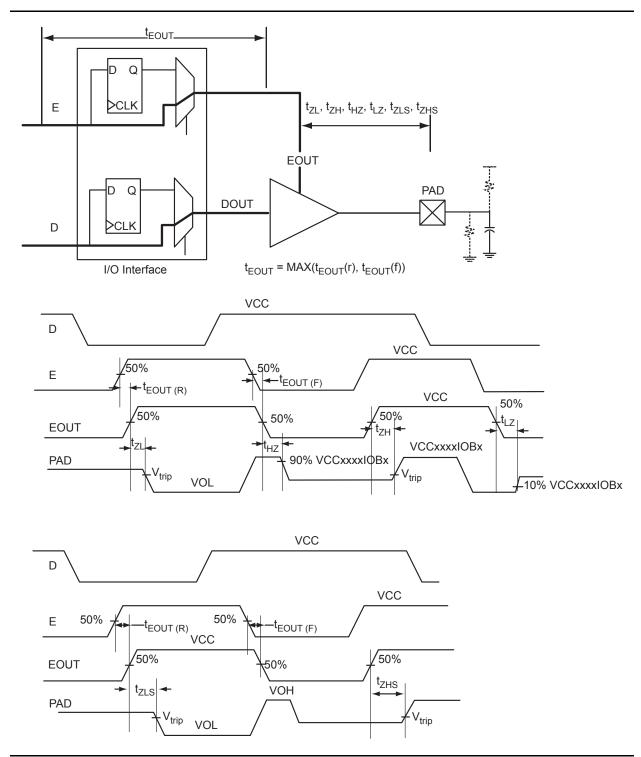

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (example)

### **Overview of I/O Performance**

# Summary of I/O DC Input and Output Levels – Default I/O Software Settings

#### Table 2-19 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Military Conditions—Software Default Settings Applicable to FPGA I/O Banks

|                               |                  |                        | VIL  |                       | VIH                  |           | VOL                   | VOH                   | IOL <sup>1</sup> | IOH <sup>1</sup> |  |  |

|-------------------------------|------------------|------------------------|------|-----------------------|----------------------|-----------|-----------------------|-----------------------|------------------|------------------|--|--|

| I/O Standard                  | Drive<br>Strgth. |                        |      | Max.<br>V             | Min.<br>V            | Max.<br>V | Max.<br>V             | Min.<br>V             | mA               | mA               |  |  |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA            | High                   | -0.3 | 0.8                   | 2                    | 3.6       | 0.4                   | 2.4                   | 12               | 12               |  |  |

| 2.5 V LVCMOS                  | 12 mA            | High                   | -0.3 | 0.7                   | 1.7                  | 3.6       | 0.7                   | 1.7                   | 12               | 12               |  |  |

| 1.8 V LVCMOS                  | 12 mA            | High                   | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                  | VCCxxxxIOBx<br>- 0.45 | 12               | 12               |  |  |

| 1.5 V LVCMOS                  | 12 mA            | High                   | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25 *<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 12               | 12               |  |  |

| 3.3 V PCI                     |                  | Per PCI specifications |      |                       |                      |           |                       |                       |                  |                  |  |  |

| 3.3 V PCI-X                   |                  |                        |      |                       | Per PCI-X spe        | ecifica   | tions                 |                       |                  |                  |  |  |

Notes:

1. Currents are measured at 125°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

# Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Military Conditions—Software Default Settings Applicable to MSS I/O Banks

|                               |                  |              |      | VIL                  | VIH                  |           | VOL                  | VOH                   | IOL <sup>1</sup> | IOH <sup>1</sup> |

|-------------------------------|------------------|--------------|------|----------------------|----------------------|-----------|----------------------|-----------------------|------------------|------------------|

| I/O Standard                  | Drive<br>Strgth. | Slew<br>Rate |      | Max.<br>V            | Min.<br>V            | Max.<br>V | Max.<br>V            | Min.<br>V             | mA               | mA               |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA             | High         | -0.3 | 0.8                  | 2                    | 3.6       | 0.4                  | 2.4                   | 8                | 8                |

| 2.5 V LVCMOS                  | 8 mA             | High         | -0.3 | 0.7                  | 1.7                  | 3.6       | 0.7                  | 1.7                   | 8                | 8                |

| 1.8 V LVCMOS                  | 4 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                 | VCCxxxxIOBx<br>- 0.45 | 4                | 4                |

| 1.5 V LVCMOS                  | 2 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25*<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 2                | 2                |

Notes:

1. Currents are measured at 125°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

|                            | Military* |     |  |  |  |  |  |

|----------------------------|-----------|-----|--|--|--|--|--|

|                            | IIL       | IIH |  |  |  |  |  |

| DC I/O Standards           | μΑ        | μA  |  |  |  |  |  |

| 3.3 V LVTTL / 3.3 V LVCMOS | 15        | 15  |  |  |  |  |  |

| 2.5 V LVCMOS               | 15        | 15  |  |  |  |  |  |

| 1.8 V LVCMOS               | 15        | 15  |  |  |  |  |  |

| 1.5 V LVCMOS               | 15        | 15  |  |  |  |  |  |

| 3.3 V PCI                  | 15        | 15  |  |  |  |  |  |

| 3.3 V PCI-X                | 15        | 15  |  |  |  |  |  |

## Table 2-21 • Summary of Maximum and Minimum DC Input Levels Applicable to Military Conditions in all I/O Bank Types

Note: \*Military temperature Range: –55°C to 125°C.

# Summary of I/O Timing Characteristics – Default I/O Software Settings

| Table 2-22 • | Summary of AC Measuring Points Applicable to All I/O Bank Types |

|--------------|-----------------------------------------------------------------|

|--------------|-----------------------------------------------------------------|

| Standard                   | Measuring Trip Point (V <sub>trip</sub> ) |  |  |  |  |

|----------------------------|-------------------------------------------|--|--|--|--|

| 3.3 V LVTTL / 3.3 V LVCMOS | 1.4 V                                     |  |  |  |  |

| 2.5 V LVCMOS               | 1.2 V                                     |  |  |  |  |

| 1.8 V LVCMOS               | 0.90 V                                    |  |  |  |  |

| 1.5 V LVCMOS               | 0.75 V                                    |  |  |  |  |

| 3.3 V PCI                  | 0.285 * VCCxxxxIOBx (RR)                  |  |  |  |  |

|                            | 0.615 * VCCxxxxlOBx (FF)                  |  |  |  |  |

| 3.3 V PCI-X                | 0.285 * VCCxxxxIOBx (RR)                  |  |  |  |  |

|                            | 0.615 * VCCxxxxlOBx (FF)                  |  |  |  |  |

| LVDS                       | Cross point                               |  |  |  |  |

| LVPECL                     | Cross point                               |  |  |  |  |

#### Table 2-23 • I/O AC Parameter Definitions

| Parameter         | Parameter Definition                                                        |  |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| t <sub>DP</sub>   | Data to pad delay through the output buffer                                 |  |  |  |  |  |  |  |

| t <sub>PY</sub>   | Pad to data delay through the input buffer                                  |  |  |  |  |  |  |  |

| t <sub>DOUT</sub> | Data to output buffer delay through the I/O interface                       |  |  |  |  |  |  |  |

| t <sub>EOUT</sub> | Enable to output buffer tristate control delay through the I/O interface    |  |  |  |  |  |  |  |

| t <sub>DIN</sub>  | Input buffer to data delay through the I/O interface                        |  |  |  |  |  |  |  |

| t <sub>HZ</sub>   | Enable to pad delay through the output buffer—High to Z                     |  |  |  |  |  |  |  |

| t <sub>ZH</sub>   | Enable to pad delay through the output buffer—Z to High                     |  |  |  |  |  |  |  |

| t <sub>LZ</sub>   | Enable to pad delay through the output buffer—Low to Z                      |  |  |  |  |  |  |  |

| t <sub>ZL</sub>   | Enable to pad delay through the output buffer—Z to Low                      |  |  |  |  |  |  |  |

| t <sub>ZHS</sub>  | Enable to pad delay through the output buffer with delayed enable—Z to High |  |  |  |  |  |  |  |

| t <sub>ZLS</sub>  | Enable to pad delay through the output buffer with delayed enable—Z to Low  |  |  |  |  |  |  |  |

#### Timing Characteristics

Table 2-51 •1.8 V LVCMOS High Slew<br/>Worst Military-Case Conditions: TJ = 125°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCxxxxIOBx = 1.7 V<br/>Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.62              | 11.85           | 0.04             | 1.22            | 0.41              | 9.22            | 11.85           | 2.80            | 1.70            | 11.42            | 14.05            | ns    |

|                   | -1             | 0.52              | 9.87            | 0.03             | 1.02            | 0.34              | 7.68            | 9.87            | 2.33            | 1.42            | 9.52             | 11.71            | ns    |

| 4 mA              | Std.           | 0.62              | 6.91            | 0.04             | 1.22            | 0.41              | 5.92            | 6.91            | 3.26            | 2.85            | 8.13             | 9.12             | ns    |

|                   | -1             | 0.52              | 5.76            | 0.03             | 1.02            | 0.34              | 4.94            | 5.76            | 2.72            | 2.38            | 6.77             | 7.60             | ns    |

| 6 mA              | Std.           | 0.62              | 4.46            | 0.04             | 1.22            | 0.41              | 4.27            | 4.46            | 3.58            | 3.40            | 6.48             | 6.66             | ns    |

|                   | -1             | 0.52              | 3.71            | 0.03             | 1.02            | 0.34              | 3.56            | 3.71            | 2.98            | 2.84            | 5.40             | 5.55             | ns    |

| 8 mA              | Std.           | 0.62              | 3.95            | 0.04             | 1.22            | 0.41              | 4.02            | 3.93            | 3.65            | 3.55            | 6.23             | 6.14             | ns    |

|                   | -1             | 0.52              | 3.29            | 0.03             | 1.02            | 0.34              | 3.35            | 3.28            | 3.04            | 2.96            | 5.19             | 5.12             | ns    |

| 12 mA             | Std.           | 0.62              | 3.62            | 0.04             | 1.22            | 0.41              | 3.68            | 3.06            | 3.75            | 4.09            | 5.89             | 5.26             | ns    |

|                   | -1             | 0.52              | 3.01            | 0.03             | 1.02            | 0.34              | 3.07            | 2.55            | 3.12            | 3.41            | 4.91             | 4.39             | ns    |

| 16 mA             | Std.           | 0.62              | 3.62            | 0.04             | 1.22            | 0.41              | 3.68            | 3.06            | 3.75            | 4.09            | 5.89             | 5.26             | ns    |

|                   | -1             | 0.52              | 3.01            | 0.03             | 1.02            | 0.34              | 3.07            | 2.55            | 3.12            | 3.41            | 4.91             | 4.39             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-52 • 1.8 V LVCMOS Low Slew

#### Worst Military-Case Conditions: $T_J$ = 125°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.62              | 15.25           | 0.04             | 1.22            | 0.41              | 14.43           | 15.25           | 2.80            | 1.65            | 16.63            | 17.46            | ns    |

|                   | -1             | 0.52              | 12.71           | 0.03             | 1.02            | 0.34              | 12.02           | 12.71           | 2.34            | 1.37            | 13.86            | 14.55            | ns    |

| 4 mA              | Std.           | 0.62              | 10.43           | 0.04             | 1.22            | 0.41              | 10.62           | 10.31           | 3.27            | 2.75            | 12.82            | 12.51            | ns    |

|                   | -1             | 0.52              | 8.69            | 0.03             | 1.02            | 0.34              | 8.85            | 8.59            | 2.72            | 2.29            | 10.69            | 10.42            | ns    |

| 6 mA              | Std.           | 0.62              | 8.21            | 0.04             | 1.22            | 0.41              | 8.36            | 7.75            | 3.58            | 3.30            | 10.57            | 9.96             | ns    |

|                   | -1             | 0.52              | 6.84            | 0.03             | 1.02            | 0.34              | 6.97            | 6.46            | 2.98            | 2.75            | 8.81             | 8.30             | ns    |

| 8 mA              | Std.           | 0.62              | 7.66            | 0.04             | 1.22            | 0.41              | 7.80            | 7.22            | 3.65            | 3.44            | 10.01            | 9.43             | ns    |

|                   | -1             | 0.52              | 6.38            | 0.03             | 1.02            | 0.34              | 6.50            | 6.02            | 3.04            | 2.87            | 8.34             | 7.86             | ns    |

| 12 mA             | Std.           | 0.62              | 7.24            | 0.04             | 1.22            | 0.41              | 7.38            | 7.23            | 3.75            | 3.96            | 9.58             | 9.43             | ns    |

|                   | -1             | 0.52              | 6.04            | 0.03             | 1.02            | 0.34              | 6.15            | 6.02            | 3.13            | 3.30            | 7.98             | 7.86             | ns    |

| 16 mA             | Std.           | 0.62              | 7.24            | 0.04             | 1.22            | 0.41              | 7.38            | 7.23            | 3.75            | 3.96            | 9.58             | 9.43             | ns    |

|                   | -1             | 0.52              | 6.04            | 0.03             | 1.02            | 0.34              | 6.15            | 6.02            | 3.13            | 3.30            | 7.98             | 7.86             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

## 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

# Table 2-53 • 1.8 V LVCMOS High Slew<br/>Worst Military-Case Conditions: T<sub>J</sub> = 125°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCxxxxIOBx = 1.7 V<br/>Applicable to MSS I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 4 mA              | Std.           | 0.23              | 2.97            | 0.09             | 1.17            | 1.75             | 0.23              | 3.02            | 2.92            | 2.36            | 2.41            | ns    |

|                   | -1             | 0.19              | 2.47            | 0.08             | 0.98            | 1.46             | 0.19              | 2.52            | 2.43            | 1.97            | 2.00            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

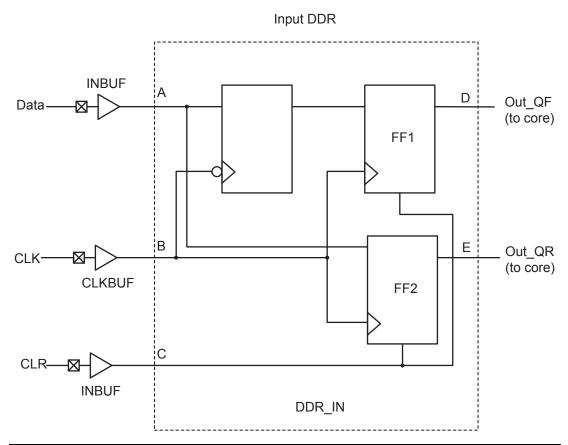

## **DDR Module Specifications**

#### Input DDR Module

#### Figure 2-20 • Input DDR Timing Model

#### Table 2-75 • Parameter Definitions

| Parameter Name          | Parameter Definition         | Measuring Nodes (from, to) |

|-------------------------|------------------------------|----------------------------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR          | B, D                       |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF          | B, E                       |

| t <sub>DDRISUD</sub>    | Data Setup Time of DDR input | A, B                       |

| t <sub>DDRIHD</sub>     | Data Hold Time of DDR input  | A, B                       |

| t <sub>DDRICLR2Q1</sub> | Clear-to-Out Out_QR          | C, D                       |

| t <sub>DDRICLR2Q2</sub> | Clear-to-Out Out_QF          | C, E                       |

| t <sub>DDRIREMCLR</sub> | Clear Removal                | С, В                       |

| t <sub>DDRIRECCLR</sub> | Clear Recovery               | С, В                       |

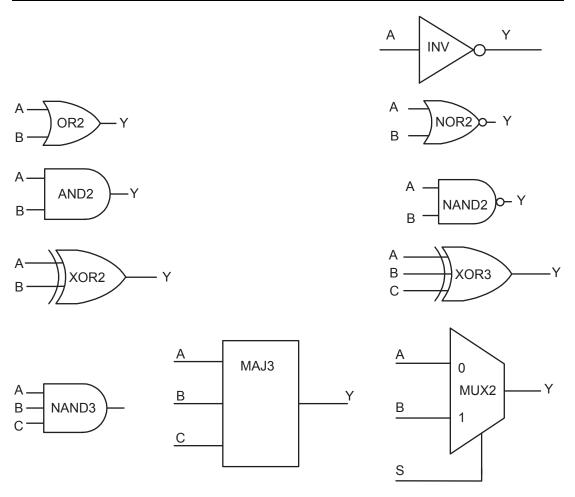

## **VersaTile Characteristics**

### VersaTile Specifications as a Combinatorial Module

The SmartFusion library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *IGLOO/e, Fusion, ProASIC3/E, and SmartFusion Macro Library Guide*.

Figure 2-24 • Sample of Combinatorial Cells

## **Clock Conditioning Circuits**

## **CCC Electrical Specifications**

**Timing Characteristics**

#### Table 2-86 • SmartFusion CCC/PLL Specification

| Parameter                                                                 | Minir                    | mum  | Тур    | ical           | Maxir            | num      | Un          | its   |  |

|---------------------------------------------------------------------------|--------------------------|------|--------|----------------|------------------|----------|-------------|-------|--|

| Clock Conditioning Circuitry Input Frequency fIN_CCC                      | 1.                       | .5   |        |                | 35               | 0        | MI          | Hz    |  |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub>        | , 0.7                    | 75   |        |                | 350 <sup>1</sup> |          | MHz         |       |  |

| Delay Increments in Programmable Delay Blocks <sup>2, 3</sup>             |                          |      | 16     | 0 <sup>4</sup> |                  |          | р           | S     |  |

| Number of Programmable Values in Each<br>Programmable Delay Block         |                          |      |        |                | 32               | 2        |             |       |  |

| Input Period Jitter                                                       |                          |      |        |                | 1.               | 5        | n           | s     |  |

| Acquisition Time                                                          |                          |      |        |                |                  |          |             |       |  |

| LockControl = 0                                                           |                          |      |        |                | 30               | 0        | μ           | s     |  |

| LockControl = 1                                                           |                          |      |        |                | 6.               | 6.0      |             | IS    |  |

| Tracking Jitter <sup>5</sup>                                              |                          |      |        |                |                  |          |             |       |  |

| LockControl = 0                                                           |                          |      |        |                | 1.               | 3 ns     |             | s     |  |

| LockControl = 1                                                           |                          |      |        |                | 0.               | 0.8      |             | s     |  |

| Output Duty Cycle                                                         | 48                       | 5.5  |        |                | 5.15 %           |          | 6           |       |  |

| Delay Range in Block: Programmable Delay 1 <sup>2,3</sup>                 | 0.                       | .6   |        |                | 5.56 ns          |          | s           |       |  |

| Delay Range in Block: Programmable Delay 2 <sup>2,3</sup>                 | 0.0                      | 25   |        |                | 5.56 ns          |          | s           |       |  |

| Delay Range in Block: Fixed Delay <sup>2,3</sup>                          |                          |      | 2.     | .2             |                  |          | n           | ns    |  |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> <sup>6.7</sup> |                          | Ma   | aximum | Peak-to        | -Peak F          | Period J | itter       |       |  |

|                                                                           | <b>SSO</b> ≤ 2 <b>SS</b> |      | ) ≤ 4  | $SSO \leq 8$   |                  | SSO      | ≤ <b>16</b> |       |  |

|                                                                           | FG/CS                    | PQ   | FG/CS  | PQ             | FG/CS            | PQ       | FG/CS       | PQ    |  |

| 0.75 MHz to 50 MHz                                                        | 0.5%                     | 1.6% | 0.9%   | 1.6%           | 0.9%             | 1.6%     | 0.9%        | 1.8%  |  |

| 50 MHz to 250 MHz                                                         | 1.75%                    | 3.5% | 9.3%   | 9.3%           | 9.3%             | 17.9%    | 10.0%       | 17.9% |  |

| 250 MHz to 350 MHz                                                        | 2.5%                     | 5.2% | 13.0%  | 13.0%          | 13.0%            | 25.0%    | 14.0%       | 25.0% |  |

Notes:

- 1. One of the CCC outputs (GLA0) is used as an MSS clock and is limited to 100 MHz (maximum) by software. Details regarding CCC/PLL are in the "PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators" chapter of the SmartFusion Microcontroller Subsystem User's Guide.

- 2. This delay is a function of voltage and temperature. See Table 2-7 on page 2-9 for deratings.

3.  $T_J = 25^{\circ}C$ , VCC = 1.5 V

- 4. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to SmartGen online help for more information.

- 5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

- 6. Measurement done with LVTTL 3.3 V 12 mA I/O drive strength and High slew rate. VCC/VCCPLL = 1.425 V, VCCI = 3.3V, 20 pF output load. All I/Os are placed outside of the PLL bank.

- 7. SSOs are outputs that are synchronous to a single clock domain and have their clock-to-out within ± 200 ps of each other.

- VCO output jitter is calculated as a percentage of the VCO frequency. The jitter (in ps) can be calculated by multiplying the VCO period by the % jitter. The VCO jitter (in ps) applies to CCC\_OUT regardless of the output divider settings. For example, if the jitter on VCO is 300 ps, the jitter on CCC\_OUT is also 300 ps.

#### FIFO

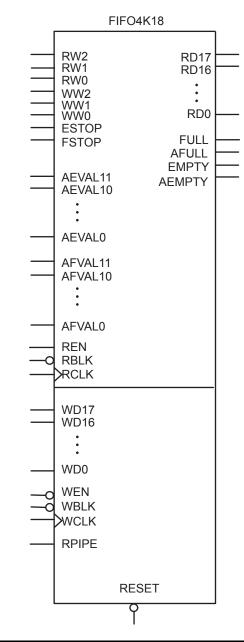

Figure 2-36 • FIFO Model

SmartFusion DC and Switching Characteristics

#### **Timing Waveforms**

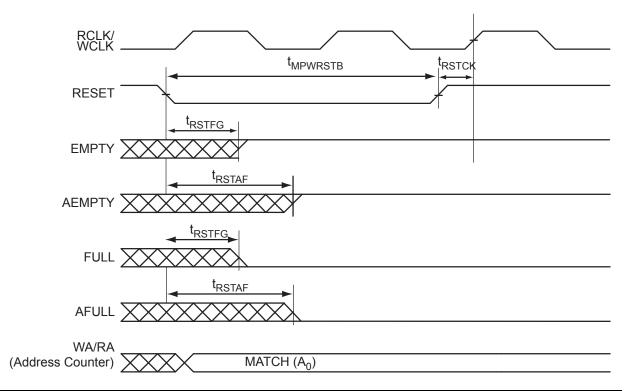

#### Figure 2-37 • FIFO Reset

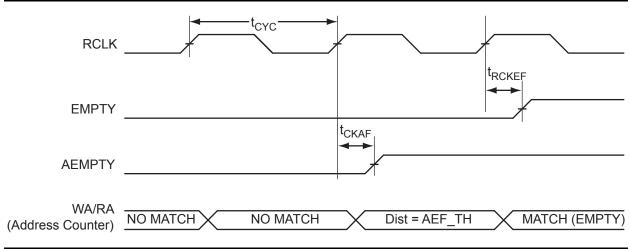

Figure 2-38 • FIFO EMPTY Flag and AEMPTY Flag Assertion

## Embedded FlashROM (eFROM)

### **Electrical Characteristics**

Table 2-91 describes the eFROM maximum performance

| Table 2-01 . | ElashPOM Access Time | Worso Militar   | Caso Conditions: T   | 」= 125°C, VCC = 1.425 V  |

|--------------|----------------------|-----------------|----------------------|--------------------------|

|              | FIDSHRUW ACCess Time | , worse williar | y-case conultions. I | j - 125 C, VCC - 1.425 V |

| Parameter        | Description             | -1    | Std.  | Units |

|------------------|-------------------------|-------|-------|-------|

| F <sub>max</sub> | Maximum Clock frequency | 15.00 | 15.00 | MHz   |

## **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-20 for more details.

#### Timing Characteristics

#### *Table 2-92* • JTAG 1532

#### Worst Military-Case Conditions: T<sub>J</sub> = 125°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | -1    | Std.  | Units |

|----------------------|-----------------------------|-------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 0.53  | 0.63  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 1.07  | 1.25  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 0.53  | 0.63  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 1.07  | 1.25  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 5.33  | 6.27  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 21.31 | 25.07 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 26.00 | 30.59 | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.00  | 0.00  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.21  | 0.25  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

Military Grade SmartFusion Customizable System-on-Chip (cSoC)

## Analog-to-Digital Converter (ADC)

Unless otherwise noted, ADC direct input performance is specified at 25°C with nominal power supply voltages, with the output measured using the external voltage reference with the internal ADC in 12-bit mode and 500 KHz sampling frequency, after trimming and digital compensation.

| Specification                                                | Test Conditions                                                                | Min. | Тур. | Max. | Units |  |

|--------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|------|-------|--|

| Input voltage range (for driving ADC over its full range)    |                                                                                |      | 2.56 |      | V     |  |

| Gain error                                                   |                                                                                |      | ±0.4 | ±0.7 | %     |  |

|                                                              | –55°C to +125°C                                                                |      | ±0.4 | ±0.7 | %     |  |

| Input referred offset voltage                                |                                                                                |      | ±1   | ±2   | mV    |  |

|                                                              | –55°C to +125°C                                                                |      | ±1   | ±4   | mV    |  |

| Integral non-linearity (INL)                                 | RMS deviation from BFSL                                                        |      |      |      |       |  |

|                                                              | 12-bit mode                                                                    |      | 1.71 |      | LSB   |  |

|                                                              | 10-bit mode                                                                    |      | 0.60 | 1.00 | LSB   |  |

|                                                              | 8-bit mode                                                                     |      | 0.2  | 0.33 | LSB   |  |

| Differential non-linearity (DNL)                             | 12-bit mode                                                                    |      | 2.4  |      | LSB   |  |

|                                                              | 10-bit mode                                                                    |      | 0.80 | 0.94 | LSB   |  |

|                                                              | 8-bit mode                                                                     |      | 0.2  | 0.23 | LSB   |  |

| Signal to noise ratio                                        |                                                                                | 62   | 64   |      | dB    |  |

| Effective number of bits (ENOB)                              | -1 dBFS input                                                                  |      |      |      |       |  |

| $ENOB = \frac{SINAD - 1.76 \text{ dB}}{6.02 \text{ dB/bit}}$ | 12-bit mode 10 KHz                                                             | 9.9  | 10   |      | Bits  |  |

| 6.02 dB/bit                                                  | 12-bit mode 100 KHz                                                            | 9.9  | 10   |      | Bits  |  |

| EQ 10                                                        | 10-bit mode 10 KHz                                                             | 9.5  | 9.6  |      | Bits  |  |

|                                                              | 10-bit mode 100 KHz                                                            | 9.5  | 9.6  |      | Bits  |  |

|                                                              | 8-bit mode 10 KHz                                                              | 7.8  | 7.9  |      | Bits  |  |

|                                                              | 8-bit mode 100 KHz                                                             | 7.8  | 7.9  |      | Bits  |  |

| Full power bandwidth                                         | At –3 dB; –1 dBFS input                                                        | 300  |      |      | KHz   |  |

| Analog settling time                                         | To 0.1% of final value (with 1 Kohm source impedance and with ADC load)        |      | 2    |      | μs    |  |

| Input capacitance                                            | Switched capacitance (ADC sample capacitor)                                    |      | 12   | 15   | pF    |  |

|                                                              | Cs: Static capacitance (Figure 2-43 on page 2-82)                              |      |      |      |       |  |

|                                                              | CM[n] input                                                                    |      | 5    | 7    | pF    |  |

|                                                              | TM[n] input                                                                    |      | 5    | 7    | pF    |  |

|                                                              | ADC[n] input                                                                   |      | 5    | 7    | pF    |  |

| Input resistance                                             | Rin: Series resistance (Figure 2-43)                                           |      | 2    |      | KΩ    |  |

|                                                              | Rsh: Shunt resistance, exclusive of switched capacitance effects (Figure 2-43) | 10   |      |      | MΩ    |  |

Table 2-95 • ADC Specifications

Note: All 3.3 V supplies are tied together and varied from 3.0 V to 3.6 V. 1.5 V supplies are held constant.

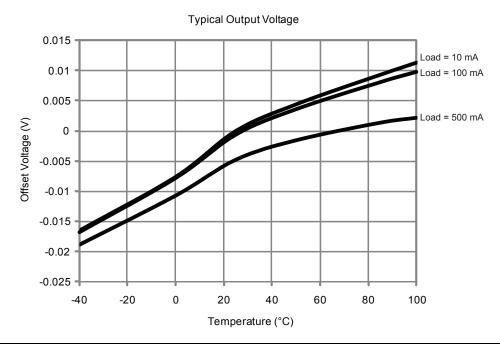

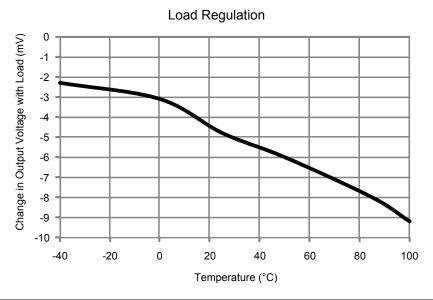

Figure 2-45 • Typical Output Voltage

Figure 2-46 • Load Regulation

Flash File System (RL-Flash) allows your embedded applications to create, save, read, and modify files in standard storage devices such as ROM, RAM, or FlashROM, using a standard serial peripheral interface (SPI). Many ARM-based microcontrollers have a practical requirement for a standard file system. With RL-FlashFS you can implement new features in embedded applications such as data logging, storing program state during standby modes, or storing firmware upgrades.

Micrium, in addition to  $\mu$ C/OS-III<sup>®</sup>, offers the following support for SmartFusion cSoC:

- µC/TCP-IP<sup>™</sup> is a compact, reliable, and high-performance stack built from the ground up by Micrium and has the quality, scalability, and reliability that translates into a rapid configuration of network options, remarkable ease-of-use, and rapid time-to-market.

- µC/Probe<sup>™</sup> is one of the most useful tools in embedded systems design and puts you in the driver's seat, allowing you to take charge of virtually any variable, memory location, and I/O port in your embedded product, while your system is running.

## **Special Function Pins**

| Name     | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC       |      |                   | No connect<br>This pin is not connected to circuitry within the device. These pins can<br>be driven to any voltage or can be left floating with no effect on the<br>operation of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DC       |      |                   | Do not connect.<br>This pin should not be connected to any signals on the PCB. These<br>pins should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LPXIN    | In   | 1                 | Low power 32 KHz crystal oscillator.<br>Input from the 32 KHz oscillator. Pin for connecting a low power 32 KHz watch crystal. If not used, the LPXIN pin can be left floating. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .                                                                                                                                                                                                                                                                                      |

| LPXOUT   | In   | 1                 | Low power 32 KHz crystal oscillator.<br>Output to the 32 KHz oscillator. Pin for connecting a low power 32 KHz<br>watch crystal. If not used, the LPXOUT pin can be left floating. For<br>more information, see the PLLs, Clock Conditioning Circuitry, and On-<br>Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller</i><br><i>Subsystem User's Guide</i> .                                                                                                                                                                                                                                                                  |

| MAINXIN  | In   | 1                 | Main crystal oscillator circuit.<br>Input to the crystal oscillator circuit. Pin for connecting an external crystal, ceramic resonator, or RC network. When using an external crystal or ceramic oscillator, external capacitors are also recommended. Refer to documentation from the crystal oscillator manufacturer for proper capacitor value.<br>If using an external RC network or clock input, MAINXIN should be grounded for better noise immunity. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .          |

| MAINXOUT | Out  | 1                 | Main crystal oscillator circuit.<br>Output from the crystal oscillator circuit. Pin for connecting external<br>crystal or ceramic resonator. When using an external crystal or ceramic<br>oscillator, external capacitors are also recommended. Refer to<br>documentation from the crystal oscillator manufacturer for proper<br>capacitor value.<br>If using external RC network or clock input, MAINXIN should be<br>grounded and MAINXOUT left unconnected. For more information, see<br>the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators<br>section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| NCAP     |      | 1                 | Negative capacitor connection.<br>This is the negative terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. Analog charge pump capacitors are not needed if none of the analog SCB features are used and none of the SDDs are used. In that case it should be left unconnected.                                                                                                                                                                                                                                                                                          |

Military Grade SmartFusion Customizable System-on-Chip (cSoC)

## Analog Front-End Pin-Level Function Multiplexing

Table 5-2 describes the relationships between the various internal signals found in the analog front-end (AFE) and how they are multiplexed onto the external package pins. Note that, in general, only one function is available for those pads that have numerous functions listed. The exclusion to this rule is when a comparator is used; the ADC can still convert either input side of the comparator.

| Pin   | ADC<br>Channel | DirIn<br>Option | Prescaler | Current<br>Mon. | Temp.<br>Mon. | Compar. | LVTTL      | SDD MUX   | SDD      |

|-------|----------------|-----------------|-----------|-----------------|---------------|---------|------------|-----------|----------|

| ABPS0 | ADC0_CH1       |                 | ABPS0_IN  |                 |               |         |            |           |          |

| ABPS1 | ADC0_CH2       |                 | ABPS1_IN  |                 |               |         |            |           |          |

| ABPS2 | ADC0_CH5       |                 | ABPS2_IN  |                 |               |         |            |           |          |

| ABPS3 | ADC0_CH6       |                 | ABPS3_IN  |                 |               |         |            |           |          |

| ABPS4 | ADC1_CH1       |                 | ABPS4_IN  |                 |               |         |            |           |          |

| ABPS5 | ADC1_CH2       |                 | ABPS5_IN  |                 |               |         |            |           |          |

| ABPS6 | ADC1_CH5       |                 | ABPS6_IN  |                 |               |         |            |           |          |

| ABPS7 | ADC1_CH6       |                 | ABPS7_IN  |                 |               |         |            |           |          |

| ABPS8 | ADC2_CH1       |                 | ABPS8_IN  |                 |               |         |            |           |          |

| ABPS9 | ADC2_CH2       |                 | ABPS9_IN  |                 |               |         |            |           |          |

| ADC0  | ADC0_CH9       | Yes             |           |                 |               | CMP1_P  | LVTTL0_IN  |           |          |

| ADC1  | ADC0_CH10      | Yes             |           |                 |               | CMP1_N  | LVTTL1_IN  | SDDM0_OUT |          |

| ADC2  | ADC0_CH11      | Yes             |           |                 |               | CMP3_P  | LVTTL2_IN  |           |          |

| ADC3  | ADC0_CH12      | Yes             |           |                 |               | CMP3_N  | LVTTL3_IN  | SDDM1_OUT |          |

| ADC4  | ADC1_CH9       | Yes             |           |                 |               | CMP5_P  | LVTTL4_IN  |           |          |

| ADC5  | ADC1_CH10      | Yes             |           |                 |               | CMP5_N  | LVTTL5_IN  | SDDM2_OUT |          |

| ADC6  | ADC1_CH11      | Yes             |           |                 |               | CMP7_P  | LVTTL6_IN  |           |          |

| ADC7  | ADC1_CH12      | Yes             |           |                 |               | CMP7_N  | LVTTL7_IN  | SDDM3_OUT |          |

| ADC8  | ADC2_CH9       | Yes             |           |                 |               | CMP9_P  | LVTTL8_IN  |           |          |

| ADC9  | ADC2_CH10      | Yes             |           |                 |               | CMP9_N  | LVTTL9_IN  | SDDM4_OUT |          |

| ADC10 | ADC2_CH11      | Yes             |           |                 |               |         | LVTTL10_IN |           |          |

| ADC11 | ADC2_CH12      | Yes             |           |                 |               |         | LVTTL11_IN |           |          |

| CM0   | ADC0_CH3       | Yes             |           | CM0_H           |               | CMP0_P  |            |           |          |

| CM1   | ADC0_CH7       | Yes             |           | CM1_H           |               | CMP2_P  | 1          |           |          |

| CM2   | ADC1_CH3       | Yes             |           | CM2_H           |               | CMP4_P  | 1          |           |          |

| CM3   | ADC1_CH7       | Yes             |           | CM3_H           |               | CMP6_P  | 1          |           |          |

| CM4   | ADC2_CH3       | Yes             |           | CM4_H           |               | CMP8_P  | 1          |           |          |

| SDD0  | ADC0_CH15      |                 |           |                 |               |         | 1          |           | SDD0_OUT |

| SDD1  | ADC1_CH15      |                 |           |                 |               |         | 1          |           | SDD1_OUT |

#### Table 5-2 • Relationships Between Signals in the Analog Front-End

Notes:

1. ABPSx\_IN: Input to active bipolar prescaler channel x.

2. CMx\_H/L: Current monitor channel x, high/low side.

3. TMx\_IO: Temperature monitor channel x.

4. CMPx\_P/N: Comparator channel x, positive/negative input.

5. LVTTLx\_IN: LVTTL I/O channel x.

6. SDDMx\_OUT: Output from sigma-delta DAC MUX channel x.

7. SDDx\_OUT: Direct output from sigma-delta DAC channel x.

## 🌜 Microsemi.

Military Grade SmartFusion Customizable System-on-Chip (cSoC)

|               | FG484                 |

|---------------|-----------------------|

| Pin<br>Number | A2F500 Function       |

| W5            | MAC_TXD[1]/IO64RSB4V0 |

| W6            | SDD2                  |

| W7            | GNDA                  |

| W8            | ТМО                   |

| W9            | ABPS2                 |

| W10           | GND33ADC0             |

| W11           | VCC15ADC1             |

| W12           | ABPS6                 |

| W13           | CM4                   |

| W14           | ABPS9                 |

| W15           | VCC33ADC2             |

| W16           | GNDA                  |

| W17           | PU_N                  |

| W18           | GNDSDD1               |

| W19           | SPI_0_CLK/GPIO_18     |

| W20           | GND                   |

| W21           | SPI_1_SS/GPIO_27      |

| W22           | UART_1_RXD/GPIO_29    |

| Y1            | GPIO_3/IO53RSB4V0     |

| Y2            | VCCMSSIOB4            |

| Y3            | GPIO_15/IO43RSB4V0    |

| Y4            | MAC_TXEN/IO61RSB4V0   |

| Y5            | VCCMSSIOB4            |

| Y6            | GNDSDD0               |

| Y7            | CM0                   |

| Y8            | GNDTM0                |

| Y9            | ADC0                  |

| Y10           | VCC15ADC0             |

| Y11           | ABPS7                 |

| Y12           | TM3                   |

| Y13           | ABPS8                 |

| Y14           | GND33ADC2             |

| Y15           | VCC15ADC2             |

| Y16           | VCCMAINXTAL           |

| Y17           | SDD1                  |

| Y18           | PTEM                  |

| Y19           | VCC33A                |

| 1             |                       |

| FG484         |                    |  |  |  |  |

|---------------|--------------------|--|--|--|--|

| Pin<br>Number | A2F500 Function    |  |  |  |  |

| Y20           | SPI_0_SS/GPIO_19   |  |  |  |  |

| Y21           | VCCMSSIOB2         |  |  |  |  |

| Y22           | UART_0_TXD/GPIO_20 |  |  |  |  |

# 6 – Datasheet Information

## **List of Changes**

The following table lists critical changes that were made in each revision of the SmartFusion datasheet.

| Revision | Changes                                                                                                                                | Page |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|------|

|          | Updated information about unused MSS I/O configuration in "User I/O Naming Conventions" (SAR 62994).                                   | 5-6  |

|          | The status was changed from Preliminary to Production for A2F060 and A2F500 in the "SmartFusion cSoC Device Status" table (SAR 41135). | III  |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.