Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | \$12Z                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | LINbus, SCI, SPI                                                        |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                 |

| Number of I/O              | 15                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 5x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvmba6f0vlf |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Rev. No.<br>(Item No.) | Date (Submitted<br>By) | Sections<br>Affected   | Substantial Change(s) |

|------------------------|------------------------|------------------------|-----------------------|

| V03.10                 | 16 Sep 2015            | 2.1.1/2-68<br>2.2/2-71 | Corrections           |

| V03.11                 | 23 Nov 2015            | 2.4.6/2-<br>110        | Corrections           |

| V03.12                 | 23 Mar 2016            |                        | Corrections           |

# 2.1 Introduction

### 2.1.1 Overview

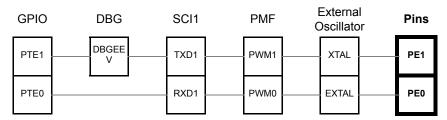

The S12ZVMB-family port integration module establishes the interface between the peripheral modules and the I/O pins for all ports. It controls the electrical pin properties as well as the signal prioritization and multiplexing on shared pins.

This document covers:

• Port E

• Port AD

| GPIO/KWU | ADC0    | SPI0 | GDU | PTU | Pins |

|----------|---------|------|-----|-----|------|

| PTADH0   | _ AN0_8 |      |     |     | PAD8 |

| PTADL7   | _ AN0_7 |      |     |     | PAD7 |

| PTADL6 — | _ AN0_6 |      |     |     | PAD6 |

| PTADL5   | _ AN0_5 |      |     |     | PAD5 |

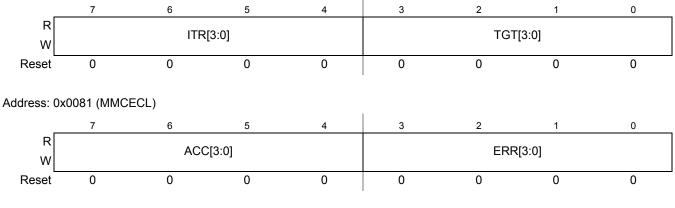

### 3.3.2.2 Error Code Register (MMCECH, MMCECL)

Address: 0x0080 (MMCECH)

#### Figure 3-5. Error Code Register (MMCEC)

Read: Anytime

Write: Write of 0xFFFF to MMCECH:MMCECL resets both registers to 0x0000

|                          | Table 3-5. MMCECH and MMCECL Field Descriptions                                                                                                                                                                                                                                                   |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field                    | Description                                                                                                                                                                                                                                                                                       |

| 7-4 (MMCECH)<br>ITR[3:0] | Initiator Field — The ITR[3:0] bits capture the initiator which caused the access violation. The initiator is captured in form of a 4 bit value which is assigned as follows:<br>0: none (no error condition detected)<br>1: S12ZCPU<br>2: reserved<br>3: ADC<br>4-15: reserved                   |

| 3-0 (MMCECH)<br>TGT[3:0] | Target Field — The TGT[3:0] bits capture the target of the faulty access. The target is captured in form of a 4 bit value which is assigned as follows:         0: none         1: register space         2: RAM         3: EEPROM         4: program flash         5: IFR         6-15: reserved |

#### Table 3-5. MMCECH and MMCECL Field Descriptions

### 6.4.2.1 Exact Address Comparator Match

With range comparisons disabled, the match condition is an exact equivalence of address bus with the value stored in the comparator address registers. Qualification of the type of access (R/W) is also possible.

Code may contain various access forms of the same address, for example a 16-bit access of ADDR[n] or byte access of ADDR[n+1] both access n+1. The comparators ensure that any access of the address defined by the comparator address register generates a match, as shown in the example of Table 6-27. Thus if the comparator address register contains ADDR[n+1] any access of ADDR[n+1] matches. This means that a 16-bit access of ADDR[n] or 32-bit access of ADDR[n-1] also match because they also access ADDR[n+1]. The right hand columns show the contents of DBGxA that would match for each access.

| Access | Address   | ADDR[n]  | ADDR[n+1] | ADDR[n+2] | ADDR[n+3] |

|--------|-----------|----------|-----------|-----------|-----------|

| 32-bit | ADDR[n]   | Match    | Match     | Match     | Match     |

| 16-bit | ADDR[n]   | Match    | Match     | No Match  | No Match  |

| 16-bit | ADDR[n+1] | No Match | Match     | Match     | No Match  |

| 8-bit  | ADDR[n]   | Match    | No Match  | No Match  | No Match  |

Table 6-27. Comparator Address Bus Matches

If the comparator INST bit is set, the comparator address register contents are compared with the PC, the data register contents and access type bits are ignored. The comparator address register must be loaded with the address of the first opcode byte.

### 6.4.2.2 Address and Data Comparator Match

Comparator A features data comparators, for data access comparisons. The comparators do not evaluate if accessed data is valid. Accesses across aligned 32-bit boundaries are split internally into consecutive accesses. The data comparator mapping to accessed addresses for the CPU is shown in Table 6-28, whereby the Address column refers to the lowest 2 bits of the lowest accessed address. This corresponds to the most significant data byte.

| Address[1:0] | Data Comparator |

|--------------|-----------------|

| 00           | DBGxD0          |

| 01           | DBGxD1          |

| 10           | DBGxD2          |

| 11           | DBGxD3          |

The fixed mapping of data comparator bytes to addresses within a 32-bit data field ensures data matches independent of access size. To compare a single data byte within the 32-bit field, the other bytes within that field must be masked using the corresponding data mask registers. This ensures that any access of that byte (32-bit,16-bit or 8-bit) with matching data causes a match. If no bytes are masked then the data comparator always compares all 32-bits and can only generate a match on a 32-bit access with correct 32-bit data value. In this case, 8-bit or 16-bit accesses within the 32-bit field cannot generate a match even if

| NDB | DBGADM | Comment                                     |  |  |  |

|-----|--------|---------------------------------------------|--|--|--|

| 0   | 0      | Do not compare data bus bit.                |  |  |  |

| 0   | 1      | Compare data bus bit. Match on equivalence. |  |  |  |

| 1   | 0      | Do not compare data bus bit.                |  |  |  |

| 1   | 1      | Compare data bus bit. Match on difference.  |  |  |  |

#### Table 6-30. NDB and MASK bit dependency

### 6.4.2.4 Range Comparisons

Range comparisons are accurate to byte boundaries. Thus for data access comparisons a match occurs if at least one byte of the access is in the range (inside range) or outside the range (outside range). For opcode comparisons only the address of the first opcode byte is compared with the range.

When using the AB comparator pair for a range comparison, the data bus can be used for qualification by using the comparator A data and data mask registers. The DBGACTL RW and RWE bits can be used to qualify the range comparison on either a read or a write access. The corresponding DBGBCTL bits are ignored. The DBGACTL COMPE/INST bits are used for range comparisons. The DBGBCTL COMPE/INST bits are ignored in range modes.

### 6.4.2.4.1 Inside Range (CompA\_Addr $\leq$ address $\leq$ CompB\_Addr)

In the Inside Range comparator mode, comparator pair A and B can be configured for range comparisons by the control register (DBGC2). The match condition requires a simultaneous valid match for both comparators. A match condition on only one comparator is not valid.

### 6.4.2.4.2 Outside Range (address < CompA\_Addr or address > CompB\_Addr)

In the Outside Range comparator mode, comparator pair A and B can be configured for range comparisons. A single match condition on either of the comparators is recognized as valid. Outside range mode in combination with opcode address matches can be used to detect if opcodes are from an unexpected range.

#### NOTE

When configured for data access matches, an outside range match would typically occur at any interrupt vector fetch or register access. This can be avoided by setting the upper or lower range limit to \$FFFFFF or \$000000 respectively. Interrupt vector fetches do not cause opcode address matches.

### 6.4.3 Events

Events are used as qualifiers for a state sequencer change of state. The state control register for the current state determines the next state for each event. An event can immediately initiate a transition to the next state sequencer state whereby the corresponding flag in DBGSR is set.

| Address<br>Offset | Register<br>Name      |        | Bit 7   | 6       | 5        | 4       | 3       | 2       | 1        | Bit 0  |

|-------------------|-----------------------|--------|---------|---------|----------|---------|---------|---------|----------|--------|

| 0x000E            | RESERVED              | R      | 0       | 0       | 0        | 0       | 0       | 0       | 0        | 0      |

| UXUUUL            | CPMUTEST1             | W      |         |         |          |         |         |         |          |        |

| 0x000F            | CPMU                  | R      |         | 0       | 0        | 0       | 0       | 0       | 0        | 0      |

|                   | ARMCOP                | W      | Bit 7   | Bit 6   | Bit 5    | Bit 4   | Bit 3   | Bit 2   | Bit 1    | Bit 0  |

| 0x0010            | CPMU<br>HTCTL         | R<br>W | ATEMPEN | 0       | VSEL     | 0       | HTE     | HTDS    | HTIE     | HTIF   |

| 0x0011            | CPMU                  | R      | 0       | 0       | 0        | 0       | 0       | LVDS    | LVIE     | LVIF   |

|                   | LVCTL                 | W      |         |         |          |         |         |         |          |        |

| 0x0012            | CPMU<br>APICTL        | R<br>W | APICLK  | 0       | 0        | APIES   | APIEA   | APIFE   | APIE     | APIF   |

| 0x0013            | CPMUACLKTR            | R<br>W | ACLKTR5 | ACLKTR4 | ACLKTR3  | ACLKTR2 | ACLKTR1 | ACLKTR0 | 0        | 0      |

| 0x0014            | CPMUAPIRH             | R<br>W | APIR15  | APIR14  | APIR13   | APIR12  | APIR11  | APIR10  | APIR9    | APIR8  |

| 0x0015            | CPMUAPIRL             | R<br>W | APIR7   | APIR6   | APIR5    | APIR4   | APIR3   | APIR2   | APIR1    | APIR0  |

| 0x0016            | RESERVED              | R      | 0       | 0       | 0        | 0       | 0       | 0       | 0        | 0      |

| 0,0010            |                       | W      |         |         |          |         |         |         |          |        |

| 0x0017            | CPMUHTTR              | R<br>W | HTOE    | 0       | 0        | 0       | HTTR3   | HTTR2   | HTTR1    | HTTR0  |

| 0x0018            | CPMU<br>IRCTRIMH      | R<br>W |         |         |          |         |         |         |          | M[9:8] |

| 0x0019            | CPMU<br>IRCTRIML      | R<br>W |         |         |          | IRCTRI  | M[7:0]  |         |          |        |

| 0x001A            | CPMUOSC               | R<br>W | OSCE    | 0       | Reserved | 0       | 0       | 0       | 0        | 0      |

|                   |                       | R      | 0       | 0       | 0        | 0       | 0       | 0       | 0        |        |

| 0x001B            | CPMUPROT              | W      |         |         |          |         |         |         |          | PROT   |

| 0x001C            | RESERVED<br>CPMUTEST2 | R<br>W | 0       | 0       | 0        | 0       | 0       | 0       | 0        | 0      |

| 0x001D            | CPMU<br>VREGCTL       | R<br>W | 0       | 0       | 0        | 0       | 0       | 0       | EXTXON   | INTXON |

| 0x001E            | CPMUOSC2              | R<br>W | 0       | 0       | 0        | 0       | 0       | 0       | OMRE     | OSCMOD |

|                   |                       | R      | 0       | 0       | 0        | 0       | 0       | 0       | 0        | 0      |

| 0x001F            | RESERVED              | W      |         | 5       | ,        | ,       | ,       | ,<br>,  | <b>,</b> | ÿ      |

|                   |                       |        |         |         |          |         |         |         |          |        |

Chapter 8 S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV\_V11)

= Unimplemented or Reserved

Figure 8-3. CPMU Register Summary

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>PORF  | <ul> <li>Power on Reset Flag — PORF is set to 1 when a power on reset occurs. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 Power on reset has not occurred.</li> <li>1 Power on reset has occurred.</li> </ul>                                                                                                                                                         |

| 5<br>LVRF  | <ul> <li>Low Voltage Reset Flag — LVRF is set to 1 when a low voltage reset occurs on the VDD, VDDF or VDDX domain. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 Low voltage reset has not occurred.</li> <li>1 Low voltage reset has occurred.</li> </ul>                                                                                                             |

| 3<br>COPRF | <ul> <li>COP Reset Flag — COPRF is set to 1 when a COP (Computer Operating Properly) reset occurs. Refer to 8.5.5, "Computer Operating Properly Watchdog (COP) Reset and 8.3.2.12, "S12CPMU_UHV_V11 COP Control Register (CPMUCOP) for details. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 COP reset has not occurred.</li> <li>1 COP reset has occurred.</li> </ul> |

| 1<br>OMRF  | Oscillator Clock Monitor Reset Flag — OMRF is set to 1 when a loss of oscillator (crystal) clock occurs. Refer<br>to8.5.3, "Oscillator Clock Monitor Reset for details. This flag can only be cleared by writing a 1. Writing a 0 has<br>no effect.<br>0 Loss of oscillator clock reset has not occurred.<br>1 Loss of oscillator clock reset has occurred.                                                   |

| 0<br>PMRF  | <ul> <li>PLL Clock Monitor Reset Flag — PMRF is set to 1 when a loss of PLL clock occurs. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 Loss of PLL clock reset has not occurred.</li> <li>1 Loss of PLL clock reset has occurred.</li> </ul>                                                                                                                           |

#### Table 8-2. CPMURFLG Field Descriptions

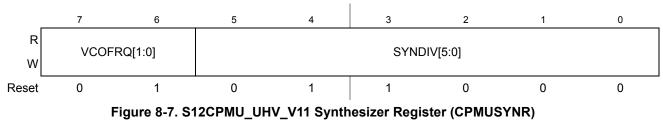

### 8.3.2.4 S12CPMU\_UHV\_V11 Synthesizer Register (CPMUSYNR)

The CPMUSYNR register controls the multiplication factor of the PLL and selects the VCO frequency range.

Module Base + 0x0004

#### Read: Anytime

Write: If PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register), then write anytime. Else write has no effect.

NOTE

Writing to this register clears the LOCK and UPOSC status bits.

### 8.3.2.11 S12CPMU\_UHV\_V11 RTI Control Register (CPMURTI)

This register selects the time-out period for the Real Time Interrupt.

The clock source for the RTI is either IRCCLK or OSCCLK depending on the setting of the RTIOSCSEL bit. In Stop Mode with PSTP=1 (Pseudo Stop Mode) and RTIOSCSEL=1 the RTI continues to run, else the RTI counter halts in Stop Mode.

Module Base + 0x000B

| _      | 7     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|-------|------|------|------|------|------|------|------|

| R<br>W | RTDEC | RTR6 | RTR5 | RTR4 | RTR3 | RTR2 | RTR1 | RTR0 |

| Reset  | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Figure 8-14. S12CPMU\_UHV\_V11 RTI Control Register (CPMURTI)

Read: Anytime

Write: Anytime

#### NOTE

A write to this register starts the RTI time-out period. A change of the RTIOSCSEL bit (writing a different value or loosing UPOSC status) restarts the RTI time-out period.

| Table 8-11. | <b>CPMURTI</b> Field | Descriptions |

|-------------|----------------------|--------------|

|-------------|----------------------|--------------|

| Field           | Description                                                                                                                                                                                                                                  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTDEC      | <ul> <li>Decimal or Binary Divider Select Bit — RTDEC selects decimal or binary based prescaler values.</li> <li>0 Binary based divider value. See Table 8-12</li> <li>1 Decimal based divider value. See Table 8-13</li> </ul>              |

| 6–4<br>RTR[6:4] | <b>Real Time Interrupt Prescale Rate Select Bits</b> — These bits select the prescale rate for the RTI.See Table 8-<br>12 and Table 8-13.                                                                                                    |

| 3–0<br>RTR[3:0] | <b>Real Time Interrupt Modulus Counter Select Bits</b> — These bits select the modulus counter target value to provide additional granularity. Table 8-12 and Table 8-13 show all possible divide values selectable by the CPMURTI register. |

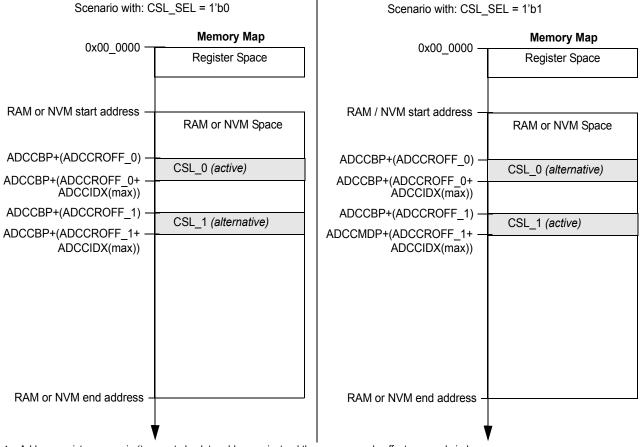

### 9.6.3.2.2 Introduction of the two Command Sequence Lists (CSLs)

The two Command Sequence Lists (CSLs) can be referred to via the Command Base Pointer Register plus the Command and Result Offset Registers plus the Command Index Register (ADCCBP, ADCCROFF 0/1, ADCCIDX).

The final address for conversion command loading is calculated by the sum of these registers (e.g.: ADCCBP+ADCCROFF\_0+ADCCIDX or ADCCBP+ADCCROFF\_1+ADCCIDX).

Bit CSL\_BMOD selects if the CSL is used in double buffer or single buffer mode. In double buffer mode, the CSL can be swapped by flow control bits LDOK and RSTA. For detailed information about when and how the CSL is swapped, please refer to Section 9.6.3.2.5, "The four ADC conversion flow control bits - description of Restart Event + CSL Swap, Section 9.9.7.1, "Initial Start of a Command Sequence List and Section 9.9.7.3, "Restart CSL execution with new/other CSL (alternative CSL becomes active CSL) — CSL swapping

Which list is actively used for ADC command loading is indicated by bit CSL\_SEL. The register to define the CSL start addresses (ADCCBP) can be set to any even location of the system RAM or NVM area. It is the user's responsibility to make sure that the different ADC lists do not overlap or exceed the system RAM or the NVM area, respectively. The error flag IA\_EIF will be set for accesses to ranges outside system RAM area and cause an error interrupt if enabled.

Note: Address register names in () are not absolute addresses instead they are a sample offset or sample index

#### Figure 9-31. Command Sequence List Schema in Double Buffer Mode

| Field      | Description                                                                                                                                                          |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>BVHIF | BATS Interrupt Flag High Detect — The flag is set to 1 when BVHC status bit changes.                                                                                 |

|            | <ul><li>0 No change of the BVHC status bit since the last clearing of the flag.</li><li>1 BVHC status bit has changed since the last clearing of the flag.</li></ul> |

| 0<br>BVLIF | BATS Interrupt Flag Low Detect — The flag is set to 1 when BVLC status bit changes.                                                                                  |

|            | <ul><li>0 No change of the BVLC status bit since the last clearing of the flag.</li><li>1 BVLC status bit has changed since the last clearing of the flag.</li></ul> |

#### Table 10-5. BATIF Register Field Descriptions

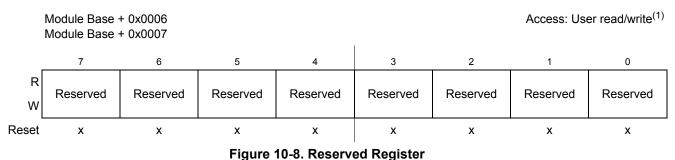

### 10.3.2.5 Reserved Register

1. Read: Anytime

Write: Only in special mode

#### NOTE

These reserved registers are designed for factory test purposes only and are not intended for general user access. Writing to these registers when in special mode can alter the module's functionality.

# 10.4 Functional Description

### 10.4.1 General

The BATS module allows measuring the voltage on the VSUP pin. The voltage at the VSUP pin can be routed via an internal voltage divider to an internal Analog to Digital Converter Channel. Also the BATS module can be configured to generate a low and high voltage interrupt based on VSUP. The trigger level of the high and low interrupt are selectable.

### 10.4.2 Interrupts

This section describes the interrupt generated by the BATS module. The interrupt is only available in CPU run mode. Entering and exiting CPU stop mode has no effect on the interrupt flags.

To make sure the interrupt generation works properly the bus clock frequency must be higher than the Voltage Warning Low Pass Filter frequency ( $f_{VWLP}$  filter).

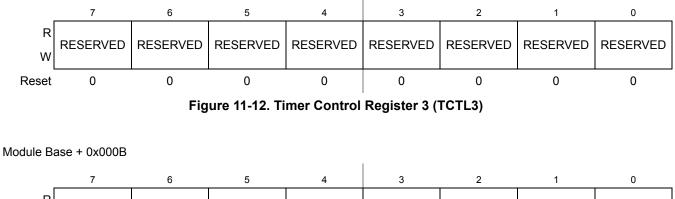

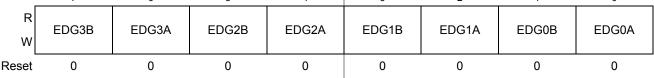

### 11.3.2.7 Timer Control Register 3/Timer Control Register 4 (TCTL3 and TCTL4)

Module Base + 0x000A

Figure 11-13. Timer Control Register 4 (TCTL4)

Read: Anytime

Write: Anytime.

#### Table 11-8. TCTL3/TCTL4 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field                 | Description                                                                                                              |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>EDGnB<br>EDGnA | <b>Input Capture Edge Control</b> — These four pairs of control bits configure the input capture edge detector circuits. |

#### Table 11-9. Edge Detector Circuit Configuration

| EDGnB | EDGnA | Configuration                           |

|-------|-------|-----------------------------------------|

| 0     | 0     | Capture disabled                        |

| 0     | 1     | Capture on rising edges only            |

| 1     | 0     | Capture on falling edges only           |

| 1     | 1     | Capture on any edge (rising or falling) |

Chapter 12 Pulse Width Modulator with Fault Protection (PMF15B6CV4)

buffered mode. In addition, if restart is enabled (RSTRTx=1), the commutation event generates both "PWM reload event" and "PWM reload-is-asynchronous event" simultaneously.

# 12.2.6 Commutation Event Edge Select Signal — async\_event\_edge\_sel[1:0]

These device-internal PMF input signals select the active edge for the async\_event input. Refer to the device overview section to determine if the selection is user configurable or tied constant at integration level.

| async_event_edge-sel[1:0] | async_event active edge |

|---------------------------|-------------------------|

| 00                        | direct input            |

| 01                        | rising edge             |

| 10                        | falling edge            |

| 11                        | both edges              |

Table 12-5. Commutation Event Edge Selection

### 12.2.7 PWM Reload Event Signals — pmf\_reloada,b,c

These device-internal PMF output signals assert once per control cycle and can serve as triggers for other implemented IP modules. Signal pmf\_reloadb and pmf\_reloadc are related to time base B and C, respectively, while signal pmf\_reloada is off out of reset and can be programmed for time base A, B, or C. Refer to the device overview section to determine the signal connections.

### 12.2.8 PWM Reload-Is-Asynchronous Signal — pmf\_reload\_is\_async

This device-internal PMF output signal serves as a qualifier to the PMF reload event signal pmf\_reloada. Whenever the async\_event signal causes pmf\_reloada output to assert also the pmf\_reload\_is\_async output asserts for the same duration, except if asynchronous event and generated PWM reload event occur in the same cycle.

# 12.3 Memory Map and Registers

### 12.3.1 Module Memory Map

A summary of the registers associated with the PMF module is shown in Figure 12-2. Detailed descriptions of the registers and bits are given in the subsections that follow.

#### NOTE

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Address<br>Offset | Register<br>Name |        | Bit 7                       | 6      | 5       | 4       | 3       | 2       | 1       | Bit 0   |

|-------------------|------------------|--------|-----------------------------|--------|---------|---------|---------|---------|---------|---------|

| 0x0000            | PMFCFG0          | R<br>W | WP                          | MTG    | EDGEC   | EDGEB   | EDGEA   | INDEPC  | INDEPB  | INDEPA  |

| 0x0001            | PMFCFG1          | R<br>W | 0                           | ENCE   | BOTNEGC | TOPNEGC | BOTNEGB | TOPNEGB | BOTNEGA | TOPNEGA |

| 0x0002            | PMFCFG2          | R<br>W | REV1                        | REV0   | MSK5    | MSK4    | MSK3    | MSK2    | MSK1    | MSK0    |

| 0x0003            | PMFCFG3          | R<br>W | PMFWAI                      | PMFFRZ | 0       | VLM     | ODE     | PINVC   | PINVB   | PINVA   |

| 0x0004            | PMFFEN           | R<br>W | 0                           | FEN5   | 0       | FEN4    | FEN3    | FEN2    | FEN1    | FEN0    |

| 0x0005            | PMFFMOD          | R<br>W | 0                           | FMOD5  | 0       | FMOD4   | FMOD3   | FMOD2   | FMOD1   | FMOD0   |

| 0x0006            | PMFFIE           | R<br>W | 0                           | FIE5   | 0       | FIE4    | FIE3    | FIE2    | FIE1    | FIE0    |

| 0x0007            | PMFFIF           | R<br>W | 0                           | FIF5   | 0       | FIF4    | FIF3    | FIF2    | FIF1    | FIF0    |

| 0x0008            | PMFQSMP0         | R<br>W | 0 0                         |        | 0       | 0       | QSI     | MP5     | QSI     | MP4     |

| 0x0009            | PMFQSMP1         | R<br>W | QSMP3                       |        | QSI     | MP2     | QSI     | MP1     | QSI     | MP0     |

| 0x000A-<br>0x000B | Reserved         | R<br>W | 0 0                         |        | 0       | 0       | 0       | 0       | 0       | 0       |

|                   |                  |        | = Unimplemented or Reserved |        |         |         |         |         |         |         |

Figure 12-2. Quick Reference to PMF Registers (Sheet 1 of 5)

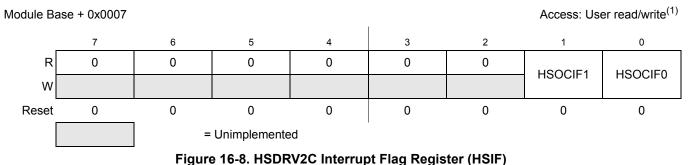

# 16.3.9 HSDRV2C Interrupt Flag Register (HSIF)

1. Read: Anytime

Write: Write 1 to clear, writing 0 has no effect

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0<br>HSOCIFx | <ul> <li>HSDRV2C Over-Current Interrupt Flags</li> <li>These flags are set when an over-current event occurs on the associated high-side driver (  I<sub>HS</sub>   &gt;   I<sub>OCTHSX</sub></li> <li> ). While set the associated high-side driver is turned off.</li> <li>Once the flag is cleared, the driver is controlled again by the source selected in PIM module.</li> <li>0 No over-current event occurred since last clearing of flag</li> <li>1 An over-current event occurred since last clearing of flag</li> </ul> |

# 16.4 Functional Description

### 16.4.1 General

The HSDRV2C module provides two high-side drivers able to drive LED or resistive loads. The drivers can be controlled directly through register bits or alternatively by dedicated timer or PWM channels. See PIM chapter for routing details.

The following sub-section describes the open-load and over-current detection features for both drivers.

### 16.4.2 Open Load Detection

A "High-load resistance Open Load Detection" can be enabled for the driver by setting the associated HSCR[HSEOLx] bit (refer to Section 16.3.4, "HSDRV2C Configuration Register (HSCR)". This detection is only active when the associated driver is enabled and it is not being driven. To detect an open-load condition a small current  $I_{HVOLDC}$  will flow through the load. If the driving pin HS[x] stays at a voltage above an internal threshold then an open load will be detected for the associated high-side driver.

The open-load condition is flagged in the HSDRV Status Register (HSSR).

#### Chapter 17 LIN Physical Layer (S12LINPHYV2)

Please note that if the bit time is smaller than the parameter t<sub>OCLIM</sub> (please refer to electricals), then no overcurrent is reported nor does an overcurrent shutdown occur. However, the current limitation is always engaged in case of a failure.

### 17.4.3 Modes

Figure 17-11 shows the possible mode transitions depending on control bits, stop mode, and error conditions.

### 17.4.3.1 Shutdown Mode

The LIN Physical Layer is fully disabled. No wake-up functionality is available. The internal pullup resistor is high ohmic only (330 k $\Omega$ ) to maintain the LIN Bus pin in the recessive state. LPTxD is not monitored in this mode for a TxD-dominant timeout. All the registers are accessible.

Setting LPE causes the module to leave the shutdown mode and to enter the normal mode or receive only mode (if RXONLY bit is set).

Clearing LPE causes the module to leave the normal or receive only modes and go back to shutdown mode.

### 17.4.3.2 Normal Mode

The full functionality is available. Both receiver and transmitter are enabled. The internal pullup resistor can be chosen to be high ohmic (330 k $\Omega$ ) if LPPUE = 0, or LIN compliant (34 k $\Omega$ ) if LPPUE = 1.

If RXONLY is set, the module leaves normal mode to enter receive only mode.

If the MCU enters stop mode, the LIN Physical Layer enters standby mode.

### 17.4.3.3 Receive Only Mode

Entering this mode disables the transmitter and immediately stops any on-going transmission. LPTxD is not monitored in this mode for a TxD-dominant timeout.

The receiver is running in full performance mode in all cases.

To return to normal mode, the RXONLY bit must be cleared.

If the device enters stop mode, the module leaves receive only mode to enter standby mode.

### 17.4.3.4 Standby Mode with Wake-Up Feature

The transmitter of the LIN Physical Layer is disabled and the receiver enters a low power mode.

#### NOTE

Before entering standby mode, ensure no transmissions are ongoing.

If LPWUE is not set, no wake up feature is available and the standby mode has the same electrical properties as the shutdown mode. This allows a low-power consumption of the device in stop mode if the wake-up feature is not needed.

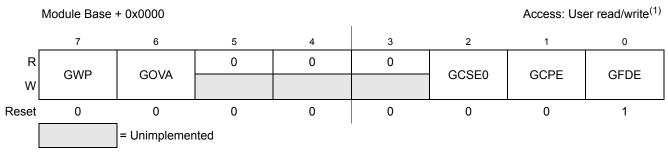

### 18.3.2.1 GDU Module Enable Register (GDUE)

1. Read: Anytime

#### Figure 18-3. GDU Module Enable Register (GDUE)

Write: Anytime, write protected bits only if GWP=0. On entry in stop mode bits GCSE0, GCPE and GFDE are cleared. After exit from stop mode write protected bits GCPE and GFDE can be written once when GWP=1.

#### Table 18-2. GDUE Register Field Description

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>GWP   | <ul> <li>GDU Write Protect— This bit enables write protection to be used for the write protectable bits. While clear, GWP allows write protectable bits to be written. When set GWP prevents any further writes to write protectable bits. Once set , GWP is cleared by reset.</li> <li>0 Write-protectable bits may be written</li> <li>1 Write-protectable bits cannot be written</li> </ul>                             |

| 6<br>GOVA  | <ul> <li>GDU Overvoltage Action — This bit cannot be modified after GWP bit is set.</li> <li>If an overvoltage condition on GHD pin occurs and GHHDF is set the high-side FET pre-drivers are turned off and the low-side FET pre-drivers are turned on.</li> <li>If an overvoltage condition on GHD pin occurs and GHHDF is set the high-side FET pre-drivers and the low-side FET pre-drivers are turned off.</li> </ul> |

| 2<br>GCSE0 | GDU Current Sense Amplifier 0 Enable— This bit enables the current sense amplifier. See Section 18.4.8,"Current Sense Amplifier and Overcurrent Comparator00Current sense amplifier 0 is disabled1Current sense amplifier 0 is enabled                                                                                                                                                                                     |

| 1<br>GCPE  | <ul> <li>GDU Charge Pump Enable — This bit enables the charge pump. This bit cannot be modified after GWP bit is set. See Section 18.4.4, "Charge Pump</li> <li>0 Charge pump is disabled</li> <li>1 Charge pump is enabled</li> </ul>                                                                                                                                                                                     |

| 0<br>GFDE  | GDU FET Pre-Driver Enable — This bit enables the low-side and high-side FET pre-drivers. This bit cannot be modified after GWP bit is set.See Section 18.4.2, "Low-Side FET Pre-Drivers and Section 18.4.3, "High-Side FET Pre-Driver.         0 Low-side and high-side drivers are disabled         1 Low-side and high-side drivers are enabled                                                                          |

|            | NOTE                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | It is not allowed to set and clear GFDE bit periodically in order<br>to switch on and off the FET pre-drivers. In order to switch on<br>and off the FET pre-drivers the PMF module has to be used to<br>mask and un-mask the PWM channels.                                                                                                                                                                                 |

#### Table 19-5. Program IFR Fields

| Global Address        | Size<br>(Bytes) | Field Description                                                       |

|-----------------------|-----------------|-------------------------------------------------------------------------|

| 0x1F_C000 - 0x1F_C007 | 8               | Reserved                                                                |

| 0x1F_C008 - 0x1F_C0B5 | 174             | Reserved                                                                |

| 0x1F_C0B6 - 0x1F_C0B7 | 2               | Version ID <sup>(1)</sup>                                               |

| 0x1F_C0B8 - 0x1F_C0BF | 8               | Reserved                                                                |

| 0x1F_C0C0 - 0x1F_C0FF | 64              | Program Once Field<br>Refer to Section 19.4.7.6, "Program Once Command" |

1. Used to track firmware patch versions, see Section 19.4.2

### Table 19-6. Memory Controller Resource Fields (NVM Resource Area<sup>(1)</sup>)

| Global Address        | Size<br>(Bytes) | Description                  |

|-----------------------|-----------------|------------------------------|

| 0x1F_4000 - 0x1F_41FF | 512             | Reserved                     |

| 0x1F_4200 - 0x1F_7FFF | 15,872          | Reserved                     |

| 0x1F_8000 - 0x1F_97FF | 6,144           | Reserved                     |

| 0x1F_9800 - 0x1F_BFFF | 10,240          | Reserved                     |

| 0x1F_C000 - 0x1F_C0FF | 256             | P-Flash IFR (see Table 19-5) |

| 0x1F_C100 - 0x1F_C1FF | 256             | Reserved.                    |

| 0x1F_C200 - 0x1F_FFFF | 15,872          | Reserved.                    |

1. See Section 19.4.4 for NVM Resources Area description.

Chapter 19 Flash Module (S12ZFTMRZ)

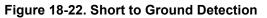

Figure 19-30. Generic Flash Command Write Sequence Flowchart

# Appendix K Ordering Information

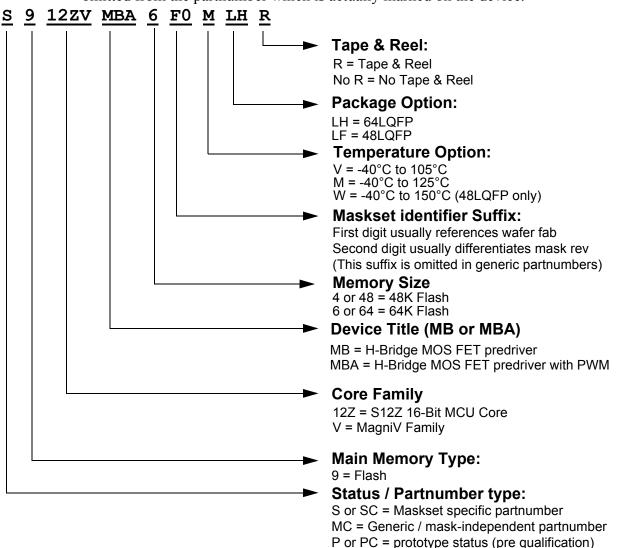

Customers can choose either the mask-specific partnumber or the generic, mask-independent partnumber. Ordering a mask-specific partnumber enables the customer to specify which particular maskset they receive whereas ordering the generic partnumber means that the currently preferred maskset (which may change over time) is shipped. In either case, the marking on the device always shows the generic, maskindependent partnumber and the mask set number. To order specific partnumbers, please contact your local sales office. The below figure illustrates the structure of a typical mask-specific ordering number.

### NOTES

Not every combination is offered. Device overview section lists available derivatives.

The mask identifier suffix and the Tape & Reel suffix are always both omitted from the partnumber which is actually marked on the device.

# L.9 0x0500-x053F PMF15B6C

| Address | Name           |        | Bit 7 6 5 4 |         |     |          |           | 2      | 1          | Bit 0   |  |  |

|---------|----------------|--------|-------------|---------|-----|----------|-----------|--------|------------|---------|--|--|

| 0x0523  | PMFCNTA        | R<br>W |             |         |     | PMF      | CNTA      |        |            |         |  |  |

|         |                |        |             |         |     |          |           |        |            |         |  |  |

| 0x0524  | 0x0524 PMFMODA |        | 0 PMFMODA   |         |     |          |           |        |            |         |  |  |

|         |                | W      |             |         |     |          |           |        |            |         |  |  |

| 0x0525  | PMFMODA        | R<br>W |             | PMFMODA |     |          |           |        |            |         |  |  |

|         |                |        |             |         |     |          |           |        |            |         |  |  |

| 0x0526  | PMFDTMA        | R<br>W | 0           | 0       | 0   | 0        |           | PMFD   | DTMA       |         |  |  |

|         |                | R      |             |         |     |          |           |        |            |         |  |  |

| 0x0527  | PMFDTMA        | W      |             |         |     | PMF      | DTMA      |        |            |         |  |  |

|         |                | R      |             |         | 0   | 0        | 0         |        |            |         |  |  |

| 0x0528  | PMFENCB        | w      | PWMENB      | GLDOKB  |     |          |           | RSTRTB | LDOKB      | PWMRIEB |  |  |

| 0 0500  |                |        |             | R       |     |          |           |        |            |         |  |  |

| 0x0529  | PMFFQCB        | W      |             | LDFQB   |     |          | HALFB PRS |        | SCB PWMRFB |         |  |  |

| 0x052A  | PMFCNTB        | R      | 0 PMFCNTB   |         |     |          |           |        |            |         |  |  |

| 0X032A  | FINIFCINTB     | W      |             |         |     |          |           |        |            |         |  |  |

| 0x052B  | PMFCNTB        | R      |             |         |     | PMF      | CNTB      |        |            |         |  |  |

| UNCOLD  |                | W      |             |         |     |          |           |        |            |         |  |  |

| 0x052C  | 52C PMEMODB    | R      | 0           |         |     |          | PMFMODB   |        |            |         |  |  |

|         |                | W      |             |         |     |          |           |        |            |         |  |  |

| 0x052D  | PMFMODB        | R<br>W |             |         |     | PMFN     | NODB      |        |            |         |  |  |

|         |                |        |             |         |     |          | 1         |        |            |         |  |  |

| 0x052E  | PMFDTMB        | R<br>W | 0           | 0       | 0   | 0        |           | PMF    | отмв       |         |  |  |

|         |                |        |             |         |     |          |           |        |            |         |  |  |

| 0x052F  | PMFDTMB        | R<br>W | PMEDIMB     |         |     |          |           |        |            |         |  |  |

|         | 0x0530 PMFENCC |        |             |         | 0   | 0        | 0         |        |            |         |  |  |

| 0x0530  |                |        | PWMENC      | GLDOKC  |     | <u> </u> | <u> </u>  | RSTRTC | LDOKC      | PWMRIEC |  |  |

|         |                | R      |             |         |     |          |           |        |            |         |  |  |

| 0x0531  | PMFFQCC        | w      |             | LDF     | FQC |          | HALFC     | PRS    | SCC        | PWMRFC  |  |  |