# E·XFL

### NXP USA Inc. - SPC5602PEF0VLH6 Datasheet

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 45                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 16                                                                 |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

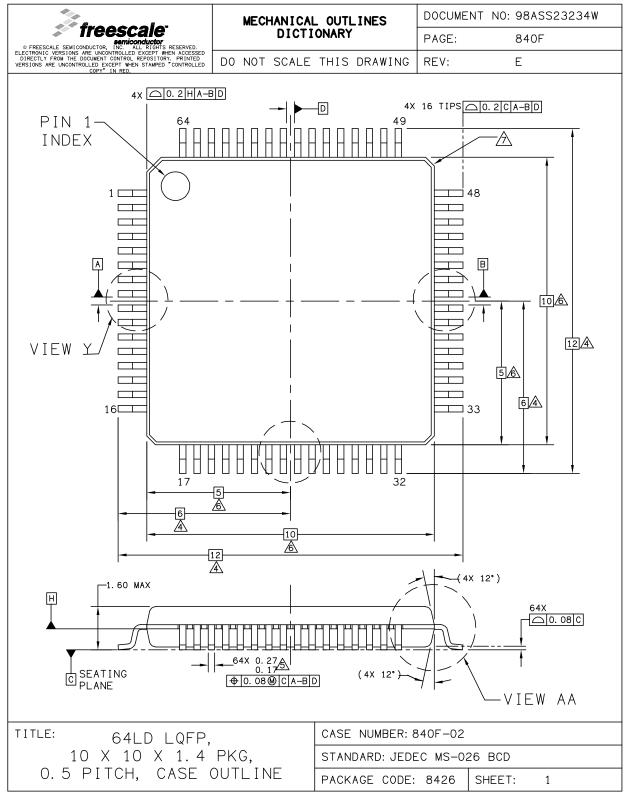

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5602pef0vlh6 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

# 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5601P/2P series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications—specifically, electrical hydraulic power steering (EHPS) and electric power steering (EPS)—as well as airbag applications.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture<sup>®</sup> technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

# 1.3 Device comparison

Table 1 provides a summary of different members of the MPC5602P family and their features to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

| Feature                                              | MPC5601P                    | MPC5602P                        |  |  |

|------------------------------------------------------|-----------------------------|---------------------------------|--|--|

| Code flash memory (with ECC)                         | 192 KB                      | 256 KB                          |  |  |

| Data flash memory / EE option (with ECC)             | 64 KB (optio                | onal feature)                   |  |  |

| SRAM (with ECC)                                      | 12 KB                       | 20 KB                           |  |  |

| Processor core                                       | 32-bit e                    | 200z0h                          |  |  |

| Instruction set                                      | VLE (variable le            | ength encoding)                 |  |  |

| CPU performance                                      | 0–64 MHz                    |                                 |  |  |

| FMPLL (frequency-modulated phase-locked loop) module | 1                           |                                 |  |  |

| INTC (interrupt controller) channels                 | 120                         |                                 |  |  |

| PIT (periodic interrupt timer)                       | 1 (with four 32-bit timers) |                                 |  |  |

| eDMA (enhanced direct memory access) channels        | 16                          |                                 |  |  |

| FlexCAN (controller area network)                    | 1 <sup>1,2</sup>            | 2 <sup>1,2</sup>                |  |  |

| Safety port                                          | Yes (via FlexCAN module)    | Yes (via second FlexCAN module) |  |  |

| FCU (fault collection unit)                          | Yes                         |                                 |  |  |

| CTU (cross triggering unit)                          | No                          | Yes                             |  |  |

| eTimer                                               | 1 (16-bit, 6                | channels)                       |  |  |

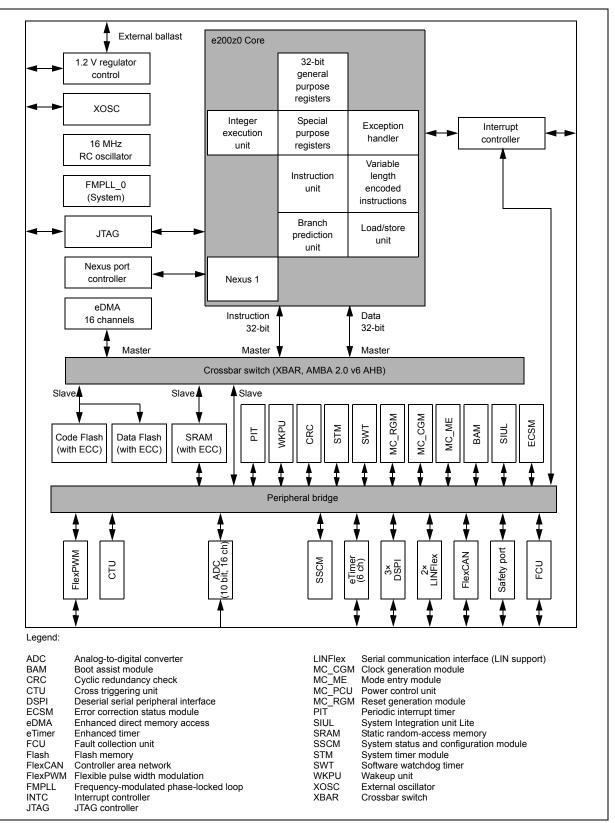

Figure 1. MPC5602P block diagram

- Clock frequency same as that used for e200z0h core

- PWM outputs can operate as complementary pairs or independent channels

- Can accept signed numbers for PWM generation

- Independent control of both edges of each PWM output

- Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half cycle reload capability

- Multiple ADC trigger events can be generated per PWM cycle via hardware

- Write protection for critical registers

- Fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Independent top and bottom deadtime insertion

- Each complementary pair can operate with its own PWM frequency and deadtime values

- Individual software-control for each PWM output

- All outputs can be programmed to change simultaneously via a "Force Out" event

- PWMX pin can optionally output a third PWM signal from each submodule

- Channels not used for PWM generation can be used for buffered output compare functions

- Channels not used for PWM generation can be used for input capture functions

- Enhanced dual-edge capture functionality

- eDMA support with automatic reload

- 2 fault inputs

- · Capture capability for PWMA, PWMB, and PWMX channels not supported

## 1.5.25 eTimer

The MPC5602P includes one eTimer module which provides six 16-bit general purpose up/down timer/counter units with the following features:

- Clock frequency same as that used for the e200z0h core

- Individual channel capability

- Input capture trigger

- Output compare

- Double buffer (to capture rising edge and falling edge)

- Separate prescaler for each counter

- Selectable clock source

- 0–100% pulse measurement

- Rotation direction flag (quad decoder mode)

- Maximum count rate

- External event counting: max. count rate = peripheral clock/2

- Internal clock counting: max. count rate = peripheral clock

- Counters are:

- Cascadable

- Preloadable

- Programmable count modulo

- Quadrature decode capabilities

- ACCESS\_AUX\_TAP\_ONCE

- 3 test data registers:

- Bypass register

- Boundary scan register (size parameterized to support a variety of boundary scan chain lengths)

- Device identification register

- TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry

# 1.5.31 On-chip voltage regulator (VREG)

The on-chip voltage regulator module provides the following features:

- Uses external NPN (negative-positive-negative) transistor

- Regulates external 3.3 V/5.0 V down to 1.2 V for the core logic

- Low voltage detection on the internal 1.2 V and I/O voltage 3.3 V

# 2 Package pinouts and signal descriptions

# 2.1 Package pinouts

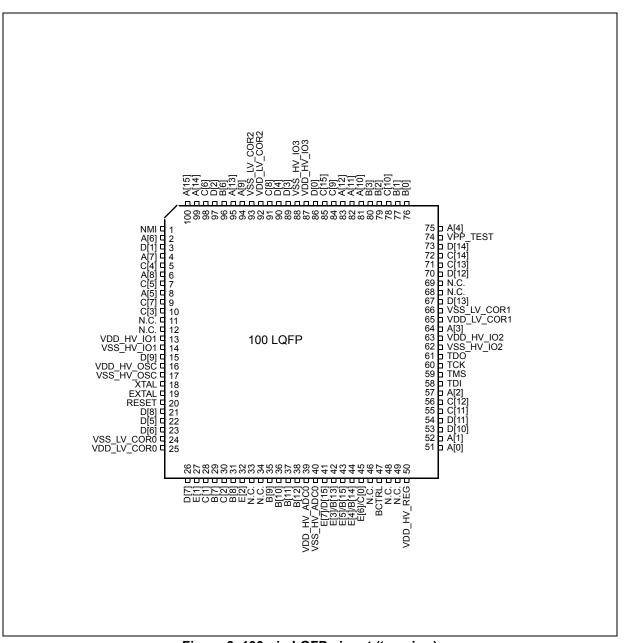

The LQFP pinouts are shown in the following figures. For pin signal descriptions, please refer to Table 5.

Figure 3. 100-pin LQFP pinout (top view)

# 2.2 Pin description

The following sections provide signal descriptions and related information about the functionality and configuration of the MPC5602P devices.

## 2.2.1 Power supply and reference voltage pins

Table 3 lists the power supply and reference voltage for the MPC5602P devices.

# 2.2.2 System pins

Table 4 and Table 5 contain information on pin functions for the MPC5602P devices. The pins listed in Table 4 are single-function pins. The pins shown in Table 5 are multi-function pins, programmable via their respective pad configuration register (PCR) values.

| Symbol   | Description                                                                                                                                                                     | Direction     | Pad s   | peed <sup>1</sup> | Pin    |         |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|-------------------|--------|---------|--|

| Symbol   | Description                                                                                                                                                                     | Direction     | SRC = 0 | SRC = 1           | 64-pin | 100-pin |  |

|          | Dedicated p                                                                                                                                                                     | pins          | •       | 1                 |        |         |  |

| NMI      | Non-maskable Interrupt                                                                                                                                                          | Input only    | Slow    | —                 | 1      | 1       |  |

| XTAL     | Analog output of the oscillator amplifier<br>circuit—needs to be grounded if oscillator is<br>used in bypass mode                                                               | _             | _       | _                 | 11     | 18      |  |

| EXTAL    | Analog input of the oscillator amplifier circuit,<br>when the oscillator is not in bypass mode<br>Analog input for the clock generator when the<br>oscillator is in bypass mode | _             | _       | _                 | 12     | 19      |  |

| TDI      | JTAG test data input                                                                                                                                                            | Input only    | Slow    | —                 | 35     | 58      |  |

| TMS      | JTAG state machine control                                                                                                                                                      | Input only    | Slow    | —                 | 36     | 59      |  |

| TCK      | JTAG clock                                                                                                                                                                      | Input only    | Slow    | —                 | 37     | 60      |  |

| TDO      | JTAG test data output                                                                                                                                                           | Output only   | Slow    | Fast              | 38     | 61      |  |

|          | Reset pir                                                                                                                                                                       | ı             |         |                   | •      |         |  |

| RESET    | Bidirectional reset with Schmitt trigger<br>characteristics and noise filter                                                                                                    | Bidirectional | Medium  | _                 | 13     | 20      |  |

|          | Test pin                                                                                                                                                                        |               | ·       | -                 |        |         |  |

| VPP_TEST | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                    | —             | _       | _                 | 47     | 74      |  |

### Table 4. System pins

<sup>1</sup> SRC values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

## 2.2.3 Pin multiplexing

Table 5 defines the pin list and muxing for the MPC5602P devices.

Each row of Table 5 shows all the possible ways of configuring each pin, via alternate functions. The default function assigned to each pin after reset is the ALTO function.

MPC5602P devices provide three main I/O pad types, depending on the associated functions:

- Slow pads are the most common, providing a compromise between transition time and low electromagnetic emission.

- *Medium pads* provide fast enough transition for serial communication channels with controlled current to reduce electromagnetic emission.

- Fast pads provide maximum speed. They are used for improved NEXUS debugging capability.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance. For more information, see "Pad AC Specifications" in the device data sheet.

\_\_\_\_\_

| Port  | PCR      | Alternate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Functions                                                 | Peripheral <sup>3</sup>                                    | I/O                                                   | Pad     | speed <sup>5</sup> | Р      | in      |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------|---------|--------------------|--------|---------|

| pin   | register | function <sup>1,2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Functions                                                 | Periprierar                                                | direction <sup>4</sup>                                | SRC = 0 | SRC = 1            | 64-pin | 100-pin |

| A[8]  | PCR[8]   | ALT0<br>ALT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GPIO[8]<br>—                                              | SIUL<br>—                                                  | I/O<br>—                                              | Slow    | Medium             | 4      | 6       |

|       |          | ALT2<br>ALT3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <br>SIN                                                   | <br><br>DSPI_1                                             | —<br>—<br>—                                           |         |                    |        |         |

|       |          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EIRQ[8]                                                   | SIUL                                                       | i                                                     |         |                    |        |         |

| A[9]  | PCR[9]   | ALT0<br>ALT1<br>ALT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIO[9]<br>CS1<br>—                                       | SIUL<br>DSPI_2<br>—                                        | I/O<br>O<br>—                                         | Slow    | Medium             | 60     | 94      |

|       |          | ALT3<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | B[3]<br>FAULT[0]                                          | FlexPWM_0<br>FlexPWM_0                                     | 0<br>                                                 |         |                    |        |         |

| A[10] | PCR[10]  | ALT0         GPIO[10]         SIUL         I/O         Slow         Me           ALT1         CS0         DSPI_2         I/O         Slow         Me           ALT2         B[0]         FlexPWM_0         O         O         ALT3         X[2]         FlexPWM_0         O         O         I/O         I/O |                                                           | Medium                                                     | 52                                                    | 81      |                    |        |         |

| A[11] | PCR[11]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ALT1SCKDSPI_2I/OALT2A[0]FlexPWM_0OALT3A[2]FlexPWM_0O      |                                                            | Slow                                                  | Medium  | 53                 | 82     |         |

| A[12] | PCR[12]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GPIO[12]<br>SOUT<br>A[2]<br>B[2]<br>EIRQ[11]              | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL           | I/O<br>O<br>O<br>I                                    | Slow    | Medium             | 54     | 83      |

| A[13] | PCR[13]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GPIO[13]<br>—<br>B[2]<br>—<br>SIN<br>FAULT[0]<br>EIRQ[12] | SIUL<br>—<br>FlexPWM_0<br>—<br>DSPI_2<br>FlexPWM_0<br>SIUL | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>— | Slow    | Medium             | 61     | 95      |

| A[14] | PCR[14]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GPIO[14]<br>TXD<br>—<br>EIRQ[13]                          | SIUL<br>Safety Port_0<br>—<br>SIUL                         | I/O<br>O<br>—<br>I                                    | Slow    | Medium             | 63     | 99      |

| A[15] | PCR[15]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GPIO[15]<br>—<br>—<br>RXD<br>EIRQ[14]                     | SIUL<br>—<br>—<br>Safety Port_0<br>SIUL                    | I/O<br>—<br>—<br>—<br>I<br>I                          | Slow    | Medium             | 64     | 100     |

## Table 5. Pin muxing (continued)

| Port  | PCR      | Alternate                         |                                       |                                   | I/O                    | Pad     | speed <sup>5</sup> | Р      | in      |

|-------|----------|-----------------------------------|---------------------------------------|-----------------------------------|------------------------|---------|--------------------|--------|---------|

| pin   | register | function <sup>1,2</sup>           | Functions                             | Peripheral <sup>3</sup>           | direction <sup>4</sup> | SRC = 0 | SRC = 1            | 64-pin | 100-pin |

| D[4]  | PCR[52]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[52]<br><br><br>B[3]              | SIUL<br><br>FlexPWM_0             | I/O<br>—<br>—<br>O     | Slow    | Slow Medium        |        | 90      |

| D[5]  | PCR[53]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[53]<br>CS3<br>F[0]<br>—          | SIUL<br>DSPI_0<br>FCU_0<br>—      | I/O<br>O<br>O          | Slow    | Medium             |        | 22      |

| D[6]  | PCR[54]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[54]<br>CS2<br>—<br>—<br>FAULT[1] | SIUL<br>DSPI_0<br><br>FlexPWM_0   | I/O<br>O<br>—<br>I     | Slow    | Medium             | _      | 23      |

| D[7]  | PCR[55]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[55]<br>CS3<br>F[1]<br>CS4        | SIUL<br>DSPI_1<br>FCU_0<br>DSPI_0 | I/O<br>O<br>O<br>O     | Slow    | Medium             | 17     | 26      |

| D[8]  | PCR[56]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[56]<br>CS2<br>—<br>CS5           | SIUL<br>DSPI_1<br><br>DSPI_0      | 1/0<br>-<br>0          | Slow    | Medium             | 14     | 21      |

| D[9]  | PCR[57]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[57]<br>X[0]<br>TXD<br>—          | SIUL<br>FlexPWM_0<br>LIN_1<br>—   | I/O<br>O<br>O<br>—     | Slow    | Medium             | 8      | 15      |

| D[10] | PCR[58]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[58]<br>A[0]<br>—                 | SIUL<br>FlexPWM_0<br>—            | I/O<br>O<br>—          | Slow    | Medium             | _      | 53      |

| D[11] | PCR[59]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[59]<br>B[0]<br>—                 | SIUL<br>FlexPWM_0<br>—            | I/O<br>O<br>—          | Slow    | low Medium         |        | 54      |

| D[12] | PCR[60]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[60]<br>X[1]<br>—<br>RXD          | SIUL<br>FlexPWM_0<br><br>LIN_1    | I/O<br>O<br>—<br>I     | Slow    | Slow Medium        |        | 70      |

| D[13] | PCR[61]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[61]<br>A[1]<br>—                 | SIUL<br>FlexPWM_0<br>—            | I/O<br>O<br>—          | Slow    | Medium             | 44     | 67      |

| D[14] | PCR[62]  | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[62]<br>B[1]<br>—                 | SIUL<br>FlexPWM_0<br>—            | I/O<br>O<br>—          | Slow    | Medium             | 46     | 73      |

## Table 5. Pin muxing (continued)

| Port  | PCR                              | Alternate                         | Functions                             | Peripheral <sup>3</sup>          | I/O                    | Pad s   | speed <sup>5</sup> | Р      | in      |

|-------|----------------------------------|-----------------------------------|---------------------------------------|----------------------------------|------------------------|---------|--------------------|--------|---------|

| pin   | register function <sup>1,2</sup> |                                   | Functions                             | Peripheral                       | direction <sup>4</sup> | SRC = 0 | SRC = 1            | 64-pin | 100-pin |

| D[15] | PCR[63]                          | ALT0<br>ALT1                      | GPIO[63]<br>—                         | SIUL                             | Input only             | —       | _                  | —      | 41      |

|       |                                  | ALT2<br>ALT3                      | _                                     | _                                |                        |         |                    |        |         |

|       |                                  | —                                 | AN[10]<br>emu. AN[4]                  | ADC_0<br>emu. ADC_1 <sup>6</sup> |                        |         |                    |        |         |

|       |                                  |                                   |                                       | Port E (16-                      | bit)                   |         |                    |        |         |

| E[1]  | PCR[65]                          | ALT0<br>ALT1<br>ALT2              | GPIO[65]<br>—<br>—                    | SIUL<br>—<br>—                   | Input only             | —       | _                  | 18     | 27      |

|       |                                  | ALT3<br>—                         | <br>AN[4]                             | ADC_0                            |                        |         |                    |        |         |

| E[2]  | PCR[66]                          | ALT0<br>ALT1<br>ALT2<br>ALT3      | GPIO[66]<br>—<br>—<br>—<br>AN[5]      | SIUL<br>—<br>—<br>—<br>ADC_0     | Input only             | —       | _                  | 23     | 32      |

| E[3]  | PCR[67]                          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[67]<br>—<br>—<br>—<br>—<br>AN[6] |                                  | Input only             | _       | _                  | 30     | 42      |

| E[4]  | PCR[68]                          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[68]<br>—<br>—<br>—<br>AN[7]      | SIUL<br>—<br>—<br>—<br>ADC_0     | Input only             |         | _                  | _      | 44      |

| E[5]  | PCR[69]                          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[69]<br>—<br>—<br>—<br>AN[8]      | SIUL<br>—<br>—<br>ADC_0          | Input only             | —       | _                  | _      | 43      |

| E[6]  | PCR[70]                          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[70]<br>—<br>—<br>—<br>AN[9]      | SIUL<br>—<br>—<br>               | Input only             | —       | _                  | _      | 45      |

| E[7]  | PCR[71]                          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[71]<br>—<br>—<br>—<br>AN[10]     | SIUL<br>—<br>—<br>—<br>ADC_0     | Input only             | —       | _                  | _      | 41      |

## Table 5. Pin muxing (continued)

<sup>1</sup> ALT0 is the primary (default) function for each port after reset.

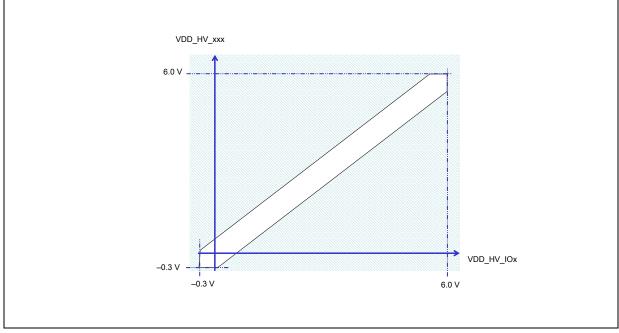

- 1 Functional operating conditions are given in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device.

- <sup>2</sup> The difference between each couple of voltage supplies must be less than 300 mV,  $|V_{DD_{HV_{IOy}}} V_{DD_{HV_{IOx}}}| < 300 mV.$ <sup>3</sup> Guaranteed by device validation.

- <sup>4</sup> Minimum value of TV<sub>DD</sub> must be guaranteed until V<sub>DD\_HV\_REG</sub> reaches 2.6 V (maximum value of V<sub>PORH</sub>)

- $^5\,$  Only when V\_DD  $\,_{HV}\,_{IOx}$  < 5.2 V

Figure 4 shows the constraints of the different power supplies.

Figure 4. Power supplies constraints (–0.3 V  $\leq$  V<sub>DD HV IOx</sub>  $\leq$  6.0 V)

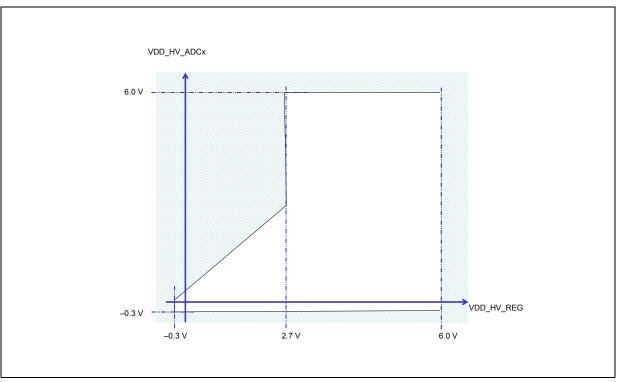

The MPC5602P supply architecture allows the ADC supply to be managed independently from the standard V<sub>DD HV</sub> supply. Figure 5 shows the constraints of the ADC power supply.

Figure 5. Independent ADC supply (–0.3 V  $\leq$  V\_{DD\_HV\_REG}  $\leq$  6.0 V)

# 3.4 Recommended operating conditions

| Querrate a l                        |    | Demonstern                                              | O an all the ma                       | Val                          | ue                           | 11   |

|-------------------------------------|----|---------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

| Symbol                              |    | Parameter Conditions                                    |                                       | Min                          | Max <sup>1</sup>             | Unit |

| V <sub>SS</sub>                     | SR | Device ground                                           | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>2</sup> | SR | 5.0 V input/output supply voltage                       | _                                     | 4.5                          | 5.5                          | V    |

| V <sub>SS_HV_IOx</sub>              | SR | Input/output ground voltage                             | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_OSC</sub>              | SR | 5.0 V crystal oscillator                                | —                                     | 4.5                          | 5.5                          | V    |

|                                     |    | amplifier supply voltage                                | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | $V_{DD_HV_IOx} + 0.1$        |      |

| V <sub>SS_HV_OSC</sub>              | SR | 5.0 V crystal oscillator<br>amplifier reference voltage | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_REG</sub>              | SR | 5.0 V voltage regulator                                 | —                                     | 4.5                          | 5.5                          | V    |

|                                     |    | supply voltage                                          | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>DD_HV_ADC0</sub>             | SR | 5.0 V ADC_0 supply and                                  | —                                     | 4.5                          | 5.5                          | V    |

|                                     |    | high reference voltage                                  | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> - 0.1 | —                            |      |

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using Equation 3:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D})$$

Eqn. 3

where:

$T_T$  = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

References:

- Semiconductor Equipment and Materials International 3081 Zanker Road San Jose, CA 95134U.S.A. (408) 943-6900

- MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at (800) 854-7179 or (303) 397-7956.

- JEDEC specifications are available on the WEB at http://www.jedec.org.

- C.E. Triplett and B. Joiner, *An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module*, Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53–58, March 1998.

- B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

LVDLVCOR monitors low voltage digital power domain

| Table 15. Low voltage monitor electrical characteristics |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Symbol                   | с | Parameter                                     | Conditions <sup>1</sup> | Va   | Unit  |      |

|--------------------------|---|-----------------------------------------------|-------------------------|------|-------|------|

| Symbol                   | C | Farameter                                     | Conditions              | Min  | Max   | Onit |

| V <sub>PORH</sub>        | Т | Power-on reset threshold                      | —                       | 1.5  | 2.7   | V    |

| V <sub>PORUP</sub>       | Ρ | Supply for functional POR module              | T <sub>A</sub> = 25 °C  | 1.0  | —     | V    |

| V <sub>REGLVDMOK_H</sub> | Ρ | Regulator low voltage detector high threshold | _                       | —    | 2.95  | V    |

| V <sub>REGLVDMOK_L</sub> | Ρ | Regulator low voltage detector low threshold  | —                       | 2.6  | —     | V    |

| V <sub>FLLVDMOK_H</sub>  | Ρ | Flash low voltage detector high threshold     | —                       | _    | 2.95  | V    |

| V <sub>FLLVDMOK_L</sub>  | Ρ | Flash low voltage detector low threshold      | —                       | 2.6  | —     | V    |

| V <sub>IOLVDMOK_H</sub>  | Ρ | I/O low voltage detector high threshold       | —                       | _    | 2.95  | V    |

| V <sub>IOLVDMOK_L</sub>  | Ρ | I/O low voltage detector low threshold        | —                       | 2.6  | —     | V    |

| V <sub>IOLVDM5OK_H</sub> | Ρ | I/O 5 V low voltage detector high threshold   | —                       | —    | 4.4   | V    |

| V <sub>IOLVDM5OK_L</sub> | Ρ | I/O 5 V low voltage detector low threshold    | —                       | 3.8  | —     | V    |

| V <sub>MLVDDOK_H</sub>   | Ρ | Digital supply low voltage detector high      | _                       |      | 1.145 | V    |

| V <sub>MLVDDOK_L</sub>   | Ρ | Digital supply low voltage detector low       | —                       | 1.08 | —     | V    |

$^1$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = –40 °C to T<sub>A MAX</sub>, unless otherwise specified

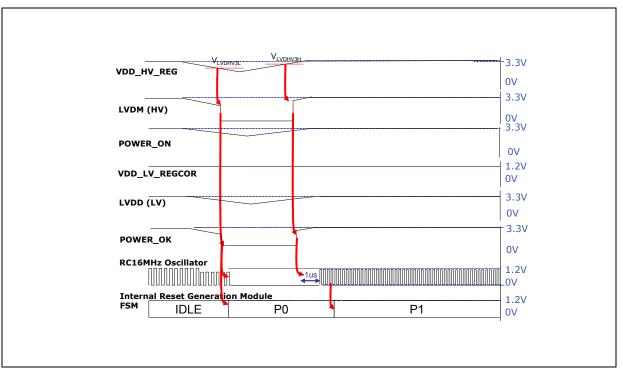

# 3.9 Power up/down sequencing

To prevent an overstress event or a malfunction within and outside the device, the MPC5602P implements the following sequence to ensure each module is started only when all conditions for switching it ON are available:

- A POWER\_ON module working on voltage regulator supply controls the correct start-up of the regulator. This is a key module ensuring safe configuration for all voltage regulator functionality when supply is below 1.5 V. Associated POWER\_ON (or POR) signal is active low.

- Several low voltage detectors, working on voltage regulator supply monitor the voltage of the critical modules (voltage regulator, I/Os, flash memory and low voltage domain). LVDs are gated low when POWER\_ON is active.

- A POWER\_OK signal is generated when all critical supplies monitored by the LVD are available. This signal is active high and released to all modules including I/Os, flash memory and 16 MHz RC oscillator needed during power-up phase and reset phase. When POWER\_OK is low the associated modules are set into a safe state.

Figure 11. Brown-out typical sequence

# 3.10 DC electrical characteristics

## 3.10.1 NVUSRO register

Portions of the device configuration, such as high voltage supply and watchdog enable/disable after reset are controlled via bit values in the non-volatile user options (NVUSRO) register.

For a detailed description of the NVUSRO register, please refer to the device reference manual.

## 3.10.1.1 NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. Table 16 shows how NVUSRO[PAD3V5V] controls the device configuration.

| Value <sup>1</sup> | Description                  |  |  |  |

|--------------------|------------------------------|--|--|--|

| 0                  | High voltage supply is 5.0 V |  |  |  |

| 1                  | High voltage supply is 3.3 V |  |  |  |

Table 16. PAD3V5V field description

Default manufacturing value before flash initialization is '1' (3.3 V).

# 3.10.2 DC electrical characteristics (5 V)

Table 17 gives the DC electrical characteristics at 5 V (4.5 V < V<sub>DD HV IOx</sub> < 5.5 V, NVUSRO[PAD3V5V] = 0).

# 3.15.3 Start-up/Switch-off timings

| Table 33. Start-up time/Switch-off time |

|-----------------------------------------|

|-----------------------------------------|

| Symbol (                |    | С | Parameter                                      | Conditions <sup>1</sup> | Value |     |     | Unit     |

|-------------------------|----|---|------------------------------------------------|-------------------------|-------|-----|-----|----------|

|                         |    | Ŭ |                                                | Conditione              | Min   | Тур | Мах | <b>U</b> |

| T <sub>FLARSTEXIT</sub> | СС | Т | Delay for Flash module to exit reset mode      | Code flash memory       | —     | -   | 125 | μs       |

|                         |    | Т |                                                | Data flash memory       |       | —   | 125 |          |

| T <sub>FLALPEXIT</sub>  | СС | D | Delay for Flash module to exit low-power mode  | Code flash memory       |       | —   | 0.5 |          |

| T <sub>FLAPDEXIT</sub>  | СС | Т | Delay for Flash module to exit power-down      | Code flash memory       | _     | —   | 30  |          |

|                         |    | Т | mode                                           | Data flash memory       |       | —   | 30  |          |

| T <sub>FLALPENTRY</sub> | СС | D | Delay for Flash module to enter low-power mode | Code flash memory       | _     | —   | 0.5 |          |

$^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified.

# 3.16 AC specifications

# 3.16.1 Pad AC specifications

| Table 34. | Output   | pin | transition | times |

|-----------|----------|-----|------------|-------|

|           | - aip ai | P   |            |       |

| Symbol          |    | с | Parameter                                      | Conditions <sup>1</sup>                                   |                                  | Value |     |     | Unit   |

|-----------------|----|---|------------------------------------------------|-----------------------------------------------------------|----------------------------------|-------|-----|-----|--------|

| - Cynn          |    | Ŭ | i didineter                                    | Conditions                                                |                                  | Min   | Тур | Мах | - Cint |

| t <sub>tr</sub> | CC | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF                                    | $V_{DD} = 5.0 V \pm 10\%$ ,      |       |     | 50  | ns     |

|                 |    | Т | SLOW configuration                             | C <sub>L</sub> = 50 pF                                    | PAD3V5V = 0                      |       |     | 100 |        |

|                 |    | D |                                                | C <sub>L</sub> = 100 pF                                   |                                  |       |     | 125 |        |

|                 |    | D |                                                | C <sub>L</sub> = 25 pF                                    | $V_{DD} = 3.3 V \pm 10\%$ ,      |       |     | 40  |        |

|                 |    | Т |                                                | C <sub>L</sub> = 50 pF                                    | PAD3V5V = 1                      |       |     | 50  |        |

|                 |    | D |                                                | C <sub>L</sub> = 100 pF                                   |                                  |       |     | 75  |        |

| t <sub>tr</sub> | CC | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF                                    | $V_{DD} = 5.0 V \pm 10\%,$       |       |     | 10  | ns     |

|                 |    | Т | IEDIUM configuration                           | C <sub>L</sub> = 50 pF                                    | PAD3V5V = 0<br>SIUL.PCRx.SRC = 1 |       |     | 20  | -      |

|                 |    | D |                                                | C <sub>L</sub> = 100 pF                                   |                                  |       |     | 40  |        |

|                 |    | D |                                                | $C_L = 25 \text{ pF}$ $V_{DD} = 3.3 \text{ V} \pm 10\%$ , |                                  |       | _   | 12  |        |

|                 |    | Т |                                                | C <sub>L</sub> = 50 pF                                    | PAD3V5V = 1<br>SIUL.PCRx.SRC = 1 | _     | _   | 25  |        |

|                 |    | D |                                                | C <sub>L</sub> = 100 pF                                   | 1                                | —     | —   | 40  |        |

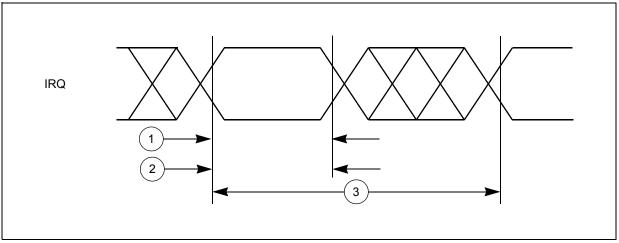

Figure 26. External interrupt timing

# 3.17.5 DSPI timing

| No  | No. Symb          |     | с | Parameter                  | Conditions                                                | Va                     | Unit                   |      |

|-----|-------------------|-----|---|----------------------------|-----------------------------------------------------------|------------------------|------------------------|------|

| NU. | Sym               | 001 | C | Falameter                  | Conditions                                                | Min                    | Max                    | Unit |

| 1   | t <sub>SCK</sub>  | CC  | D | DSPI cycle time            | Master (MTFE = 0)                                         | 60                     | —                      | ns   |

|     |                   |     |   |                            | Slave (MTFE = 0)                                          | 60                     | —                      |      |

| 2   | t <sub>CSC</sub>  | CC  | D | CS to SCK delay            | 16                                                        |                        | —                      | ns   |

| 3   | t <sub>ASC</sub>  | CC  | D | After SCK delay            | _                                                         | 26                     | —                      | ns   |

| 4   | t <sub>SDC</sub>  | CC  | D | SCK duty cycle             | _                                                         | 0.4 * t <sub>SCK</sub> | 0.6 * t <sub>SCK</sub> | ns   |

| 5   | t <sub>A</sub>    | CC  | D | Slave access time          | SS active to SOUT valid   —   30                          |                        | 30                     | ns   |

| 6   | t <sub>DIS</sub>  | СС  | D | Slave SOUT disable time    | SS inactive to SOUT high   —     impedance or invalid   — |                        | 16                     | ns   |

| 7   | t <sub>PCSC</sub> | CC  | D | PCSx to PCSS time          | — 13                                                      |                        | —                      | ns   |

| 8   | t <sub>PASC</sub> | CC  | D | PCSS to PCSx time          | _                                                         | 13                     | —                      | ns   |

| 9   | t <sub>SUI</sub>  | CC  | D | Data setup time for inputs | Master (MTFE = 0)                                         | 35                     | —                      | ns   |

|     |                   |     |   |                            | Slave                                                     | 4                      | —                      |      |

|     |                   |     |   |                            | Master (MTFE = 1, CPHA = 0)                               | 35                     | —                      |      |

|     |                   |     |   |                            | Master (MTFE = 1, CPHA = 1)                               | 35                     | —                      |      |

| 10  | t <sub>HI</sub>   | CC  | D | Data hold time for inputs  | Master (MTFE = 0)                                         | -5                     | —                      | ns   |

|     |                   |     |   |                            | Slave                                                     | 4                      | —                      |      |

|     |                   |     |   |                            | Master (MTFE = 1, CPHA = 0)                               | 11                     | —                      |      |

|     |                   |     |   |                            | Master (MTFE = 1, CPHA = 1)                               | -5                     | —                      |      |

## Table 39. DSPI timing<sup>1</sup>

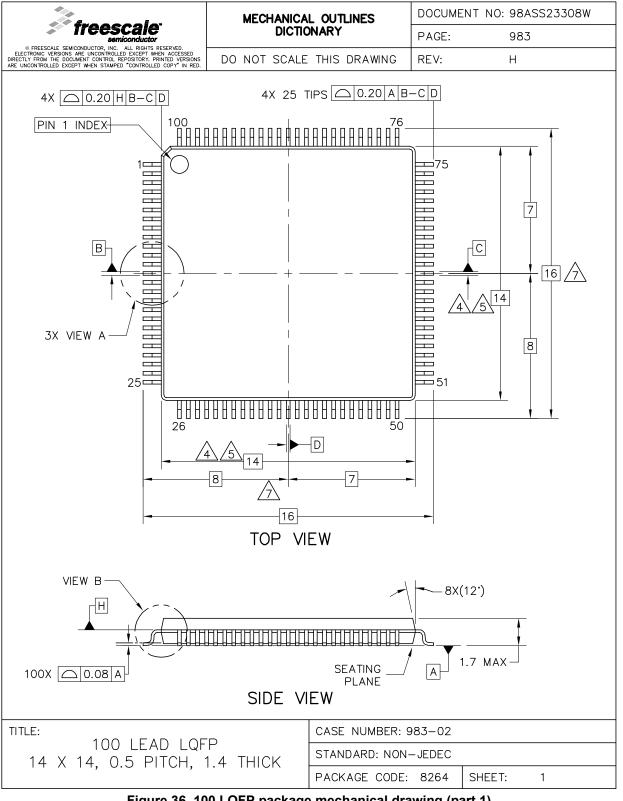

Figure 36. 100 LQFP package mechanical drawing (part 1)

Figure 39. 64 LQFP package mechanical drawing (part 1)

| Table 40. Revision history (continue |

|--------------------------------------|

|--------------------------------------|

| Revision         | Date        | Description of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>(continued) | 16 Dec 2010 | <ul> <li>*Program and erase specifications" table:</li> <li>T<sub>wprogram</sub>: updated initial max and max values</li> <li>T<sub>BKPRG</sub>, 64 KB: updated initial max and max values</li> <li>added information about "erase time" for Data Flash</li> <li>*Flash module life" table:</li> <li>P/E, 32 KB: added typ value</li> <li>P/E, 128 KB: added typ value</li> <li>Replaced "Pad AC specifications (5.0 V, NVUSRO[PAD3V5V] = 0)" and "Pad AC specifications (3.3 V, INVUSRO[PAD3V5V] = 1)" tables with "Output pin transition times" table</li> <li>*JTAG pin AC electrical characteristics" table:</li> <li>t<sub>TDOV</sub>: updated max value</li> <li>t<sub>TDOHZ</sub>: added min value and removed max value</li> <li>*Nexus debug port timing" table: removed the rows "t<sub>MCYC</sub>", "t<sub>MDOV</sub>", "t<sub>MSEOV</sub>", and "t<sub>EVTOV</sub>"</li> <li>Updated "External interrupt timing (IRQ pin)" table</li> <li>Updated "DSPI timing" table</li> <li>Updated "Ordering information" section</li> </ul> |

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MPC5602P Rev. 6 12/2012 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2011-2013. All rights reserved.