Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1717-e-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 28-PIN ALLOCATION TABLE (PIC16(L)F1718) TABLE 1:

| I/O <sup>(2)</sup> | SPDIP,SOIC,<br>SSOP | QFN, UQFN | ADC  | Reference          | Comparator       | Op Amp  | DAC                  | Zero Cross | Timers                        |    | CCL               | NCO | PWM | 900  |                   | MSSP                   | EUSART | CLC                   | Interrupt                 | Pull-up | Basic          |

|--------------------|---------------------|-----------|------|--------------------|------------------|---------|----------------------|------------|-------------------------------|----|-------------------|-----|-----|------|-------------------|------------------------|--------|-----------------------|---------------------------|---------|----------------|

| RA0                | 2                   | 27        | AN0  |                    | C1IN0-<br>C2IN0- |         |                      |            |                               |    |                   |     |     |      |                   |                        |        | CLCIN0 <sup>(1)</sup> | IOC                       | Y       |                |

| RA1                | 3                   | 28        | AN1  |                    | C1IN1-<br>C2IN1- | OPA1OUT |                      |            |                               |    |                   |     |     |      |                   |                        |        | CLCIN1 <sup>(1)</sup> | юс                        | Y       |                |

| RA2                | 4                   | 1         | AN2  | V <sub>REF</sub> - | C1IN0+<br>C2IN0+ |         | DAC1OUT1             |            |                               |    |                   |     |     |      |                   |                        |        |                       | юс                        | Y       |                |

| RA3                | 5                   | 2         | AN3  | V <sub>REF</sub> + | C1IN1+           |         |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Υ       |                |

| RA4                | 6                   | 3         |      |                    |                  | OPA1IN+ |                      |            | T0CKI <sup>(1)</sup>          |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Y       |                |

| RA5                | 7                   | 4         | AN4  |                    |                  | OPA1IN- | DAC2OUT1             |            |                               |    |                   |     |     |      |                   | nSS <sup>(1)</sup>     |        |                       | IOC                       | Υ       |                |

| RA6                | 10                  | 7         |      |                    |                  |         |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | юс                        | Y       | OSC2<br>CLKOUT |

| RA7                | 9                   | 6         |      |                    |                  |         |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | юс                        | Y       | OSC1<br>CLKIN  |

| RB0                | 21                  | 18        | AN12 |                    | C2IN1+           |         |                      | ZCD        |                               |    |                   |     |     | COG1 | IN <sup>(1)</sup> |                        |        |                       | INT <sup>(1)</sup><br>IOC | Y       |                |

| RB1                | 22                  | 19        | AN10 |                    | C1IN3-<br>C2IN3- | OPA2OUT |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Y       |                |

| RB2                | 23                  | 20        | AN8  |                    |                  | OPA2IN- |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Υ       |                |

| RB3                | 24                  | 21        | AN9  |                    | C1IN2-<br>C2IN2- | OPA2IN+ |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | юс                        | Y       |                |

| RB4                | 25                  | 22        | AN11 |                    |                  |         |                      |            |                               |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Y       |                |

| RB5                | 26                  | 23        | AN13 |                    |                  |         |                      |            | T1G <sup>(1)</sup>            |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Υ       |                |

| RB6                | 27                  | 24        |      |                    |                  |         |                      |            |                               |    |                   |     |     |      |                   |                        |        | CLCIN2 <sup>(1)</sup> | IOC                       | Υ       | ICSPCLK        |

| RB7                | 28                  | 25        |      |                    |                  |         | DAC1OUT2<br>DAC2OUT2 |            |                               |    |                   |     |     |      |                   |                        |        | CLCIN3 <sup>(1)</sup> | юс                        | Y       | ICSPDAT        |

| RC0                | 11                  | 8         |      |                    |                  |         |                      |            | T1CKI <sup>(1)</sup><br>SOSCO |    |                   |     |     |      |                   |                        |        |                       | IOC                       | Y       |                |

| RC1                | 12                  | 9         |      |                    |                  |         |                      |            | sosci                         | СС | P2 <sup>(1)</sup> |     |     |      |                   |                        |        |                       | .IOC                      | Υ       |                |

| RC2                | 13                  | 10        | AN14 |                    |                  |         |                      |            |                               | СС | P1 <sup>(1)</sup> |     |     |      |                   |                        |        |                       | - IOC                     | Υ       |                |

| RC3                | 14                  | 11        | AN15 |                    |                  |         |                      |            | · · · ·                       |    |                   |     |     |      |                   | SCL/SCK <sup>(1)</sup> |        |                       | IOC .                     | Υ       |                |

DS40001740B-page 4

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: Alternate outputs are excluded from solid shaded areas.

5: Alternate inputs are excluded from dot shaded areas.

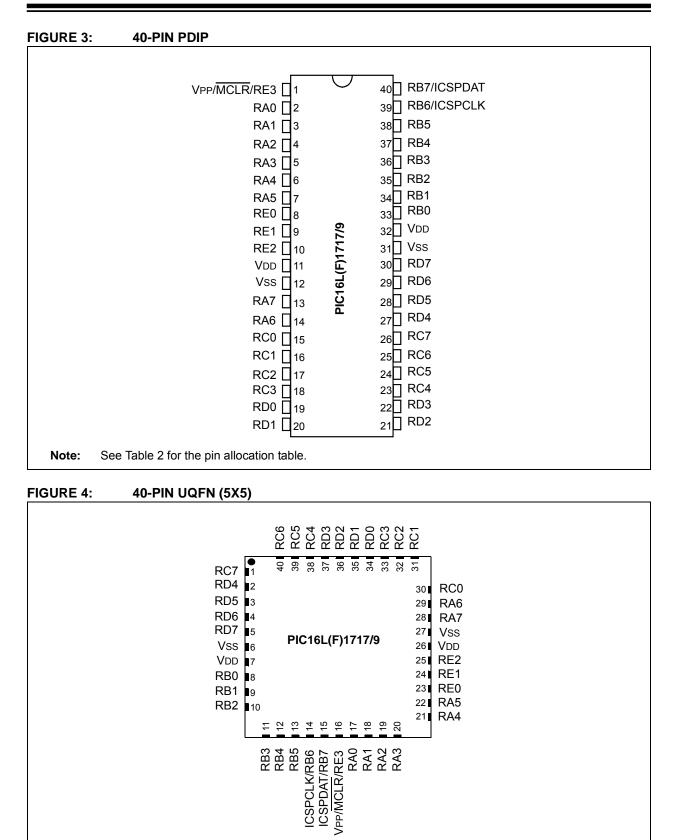

**Note:** See Table 2 for the pin allocation table.

# **Table of Contents**

| 1.0  | Device Overview                                                           |     |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Enhanced Mid-Range CPU                                                    |     |

| 3.0  | Memory Organization                                                       |     |

| 4.0  | Device Configuration                                                      | 55  |

| 5.0  | Resets                                                                    | 60  |

| 6.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 7.0  | Interrupts                                                                | 86  |

| 8.0  | Power-Down Mode (Sleep)                                                   |     |

| 9.0  | Watchdog Timer (WDT)                                                      | 102 |

| 10.0 | Flash Program Memory Control                                              | 106 |

| 11.0 |                                                                           |     |

| 12.0 |                                                                           | 150 |

| 13.0 | Interrupt-On-Change                                                       | 156 |

| 14.0 | Fixed Voltage Reference (FVR)                                             | 163 |

| 15.0 | Temperature Indicator Module                                              | 166 |

|      | Comparator Module                                                         |     |

| 17.0 | Pulse Width Modulation (PWM)                                              | 177 |

| 18.0 | Complementary Output Generator (COG) Module                               |     |

| 19.0 |                                                                           |     |

| 20.0 | Numerically Controlled Oscillator (NCO) Module                            | 233 |

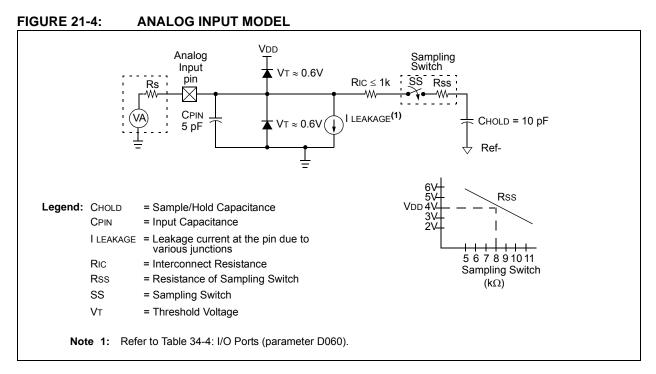

| 21.0 | Analog-to-Digital Converter (ADC) Module                                  |     |

| 22.0 |                                                                           | 255 |

| 23.0 | 8-Bit Digital-to-Analog Converter (DAC1) Module                           | 258 |

|      | · · · · · · · · · · · · · · · · · · ·                                     |     |

| 25.0 | Zero-Cross Detection (ZCD) Module                                         |     |

| 26.0 | Timer0 Module                                                             |     |

| 27.0 | Timer1 Module with Gate Control                                           |     |

| 28.0 |                                                                           |     |

| 29.0 | Capture/Compare/PWM Modules                                               |     |

| 30.0 | Master Synchronous Serial Port (MSSP) Module                              |     |

| 31.0 | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 351 |

| 32.0 | In-Circuit Serial Programming (ICSP™)                                     | 381 |

| 33.0 | Instruction Set Summary                                                   | 383 |

| 34.0 | Electrical Specifications                                                 | 397 |

| 35.0 | DC and AC Characteristics Graphs and Charts                               | 432 |

| 36.0 | Development Support                                                       | 454 |

| 37.0 | Packaging Information                                                     | 458 |

| Appe | endix A: Data Sheet Revision History                                      | 479 |

# 1.0 DEVICE OVERVIEW

The PIC16(L)F1717/8/9 devices are described within this data sheet. They are available in the following package configurations:

- 28-pin SPDIP, SSOP, SOIC, QFN and UQFN

- 40-pin PDIP and UQFN

- 44-pin TQFP

Figure 1-1 and Figure 1-2 show block diagrams of the PIC16(L)F1717/8/9 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

## TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                        |                | PIC16(L)F1717 | PIC16(L)F1718 | PIC16(L)F1719                         |

|---------------------------------------------------|----------------|---------------|---------------|---------------------------------------|

| Analog-to-Digital Conve                           | rter (ADC)     | ٠             | ٠             | •                                     |

| Fixed Voltage Reference                           | e (FVR)        | ٠             | ٠             | •                                     |

| Zero-Cross Detection (Z                           | ZCD)           | ٠             | •             | •                                     |

| Temperature Indicator                             |                | ٠             | ٠             | •                                     |

| Complementary Output                              | Generator (C   | OG)           |               |                                       |

|                                                   | COG            | •             | ٠             | •                                     |

| Numerically Controlled                            | Oscillator (NC | O)            |               |                                       |

|                                                   | NCO            | •             | ٠             | •                                     |

| Digital-to-Analog Conve                           | rter (DAC)     | -             |               |                                       |

|                                                   | DAC1           | •             | ٠             | •                                     |

|                                                   | DAC2           | •             | ٠             | •                                     |

| Capture/Compare/PWM                               | I (CCP/ECCP    | ) Mod         | ules          |                                       |

| · · ·                                             | CCP1           | •             | •             | •                                     |

|                                                   | CCP2           | •             | ٠             | •                                     |

| Comparators                                       |                |               |               |                                       |

|                                                   | C1             | •             | ٠             | •                                     |

|                                                   | C2             | •             | ٠             | •                                     |

| Configurable Logic Cell                           | (CLC)          |               |               |                                       |

|                                                   | CLC1           | •             | •             | •                                     |

|                                                   | CLC2           | •             | ٠             | •                                     |

|                                                   | CLC3           | •             | ٠             | •                                     |

|                                                   | CLC4           | •             | ٠             | •                                     |

| Enhanced Universal Syn<br>Receiver/Transmitter (E |                | ynchr         | onous         | 3                                     |

|                                                   | EUSART         | ٠             | ٠             | •                                     |

| Master Synchronous Se                             | erial Ports    |               |               |                                       |

|                                                   | MSSP           | •             | ٠             | •                                     |

| Op Amp                                            |                |               |               |                                       |

|                                                   | Op Amp 1       | •             | ٠             | •                                     |

|                                                   | Op Amp 2       | •             | ٠             | •                                     |

| Pulse-Width Modulator                             | (PWM)          |               |               |                                       |

|                                                   | PWM3           | •             | •             | •                                     |

|                                                   | PWM4           | •             | ٠             | •                                     |

| Timers                                            |                |               |               |                                       |

|                                                   | Timer0         | •             | •             | •                                     |

|                                                   | Timer1         | •             | ٠             | •                                     |

|                                                   | Timer2         | •             | ٠             | •                                     |

|                                                   |                | 1             |               | · · · · · · · · · · · · · · · · · · · |

| Name               | Function           | Input<br>Type | Output<br>Type | Description                                        |

|--------------------|--------------------|---------------|----------------|----------------------------------------------------|

| OUT <sup>(2)</sup> | C1OUT              |               | CMOS           | Comparator 1 output.                               |

|                    | C2OUT              |               | CMOS           | Comparator 2 output.                               |

|                    | CCP1               |               | CMOS           | Compare/PWM1 output.                               |

|                    | CCP2               |               | CMOS           | Compare/PWM2 output.                               |

|                    | NCO10UT            |               | CMOS           | Numerically controlled oscillator output.          |

|                    | PWM3OUT            |               | CMOS           | PWM3 output.                                       |

|                    | PWM4OUT            |               | CMOS           | PWM4 output.                                       |

|                    | COG1A              |               | CMOS           | Complementary output generator output A.           |

|                    | COG1B              |               | CMOS           | Complementary output generator output B.           |

|                    | COG1C              |               | CMOS           | Complementary output generator output C.           |

|                    | COG1D              |               | CMOS           | Complementary output generator output D.           |

|                    | SDA <sup>(3)</sup> |               | OD             | I <sup>2</sup> C Data output.                      |

|                    | SCK                |               | CMOS           | SPI clock output.                                  |

|                    | SCL <sup>(3)</sup> |               | OD             | I <sup>2</sup> C clock output.                     |

|                    | SDO                |               | CMOS           | SPI data output.                                   |

|                    | TX/CK              |               | CMOS           | EUSART asynchronous TX data/synchronous clock out. |

|                    | DT <sup>(3)</sup>  |               | CMOS           | EUSART synchronous data output.                    |

|                    | CLC10UT            |               | CMOS           | Configurable Logic Cell 1 output.                  |

|                    | CLC2OUT            |               | CMOS           | Configurable Logic Cell 2 output.                  |

|                    | CLC3OUT            |               | CMOS           | Configurable Logic Cell 3 output.                  |

|                    | CLC4OUT            |               | CMOS           | Configurable Logic Cell 4 output.                  |

#### TABLE 1-3: PIC16(L)F1717/9 PINOUT DESCRIPTION (CONTINUED)

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal levels

Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

| IADLE J-C | TABLE 3-3. SUMMART OF REGISTERS ASSOCIATED WITH RESETS |        |                       |       |       |       |       |        |                     |

|-----------|--------------------------------------------------------|--------|-----------------------|-------|-------|-------|-------|--------|---------------------|

| Name      | Bit 7                                                  | Bit 6  | Bit 5                 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

| BORCON    | SBOREN                                                 | BORFS  |                       | _     |       |       | _     | BORRDY | 62                  |

| PCON      | STKOVF                                                 | STKUNF |                       | RWDT  | RMCLR | RI    | POR   | BOR    | 66                  |

| STATUS    | _                                                      |        | - TO PD Z DC          |       |       |       | С     | 28     |                     |

| WDTCON    |                                                        |        | WDTPS<4:0> SWDTEN 104 |       |       |       |       |        | 104                 |

TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

# 9.3 Time-out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

# 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- Device wakes up from Sleep

- Oscillator fail

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 9-2 for more information.

# 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See STATUS Register (Register 3-1) for more information.

#### TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT                          |  |  |

|----------------------------------------------------------|------------------------------|--|--|

| WDTE<1:0> = 00                                           |                              |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |  |

| WDTE<1:0> = 10 and enter Sleep                           | - Cleared                    |  |  |

| CLRWDT Command                                           |                              |  |  |

| Oscillator Fail Detected                                 |                              |  |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |  |

#### EXAMPLE 10-3: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. 64 bytes of data are loaded, starting at the address in DATA\_ADDR ; 2. Each word of data to be written is made up of two adjacent bytes in DATA\_ADDR, ; stored in little endian format ; 3. A valid starting address (the least significant bits = 00000) is loaded in ADDRH: ADDRL ; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM) ; BCF INTCON,GIE ; Disable ints so required sequences will execute properly ; Bank 3 BANKSEL PMADRH MOVF ADDRH,W ; Load initial address MOVWF PMADRH MOVF ADDRL,W MOVWF PMADRL LOW DATA\_ADDR ; Load initial data address MOVLW MOVWF FSROL MOVLW HIGH DATA\_ADDR ; Load initial data address MOVWF FSR0H ; PMCON1,CFGS ; Not configuration space BCF BSF PMCON1,WREN ; Enable writes PMCON1,LWLO ; Only Load Write Latches BSF LOOP MOVIW FSR0++ ; Load first data byte into lower MOVWF PMDATT. ; ; Load second data byte into upper MOVIW FSR0++ MOVWF PMDATH MOVF ; Check if lower bits of address are '00000' PMADRL,W ; Check if we're on the last of 32 addresses XORLW 0x1F ANDLW 0x1F BTFSC STATUS,Z ; Exit if last of 32 words, GOTO START\_WRITE ; MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh MOVWF PMCON2 ; Write AAh BSF ; Set WR bit to begin write PMCON1,WR NOP ; NOP instructions are forced as processor ; loads program memory write latches NOP INCF PMADRL, F ; Still loading latches Increment address GOTO LOOP ; Write next latches START\_WRITE BCF PMCON1,LWLO ; No more loading latches - Actually start Flash program ; memory write MOVLW 55h ; Start of required write sequence: MOVWF PMCON2 ; Write 55h Required Sequence MOVLW 0AAh ; MOVWF PMCON2 ; Write AAh BSF PMCON1,WR ; Set WR bit to begin write NOP ; NOP instructions are forced as processor writes ; all the program memory write latches simultaneously NOP ; to program memory. ; After NOPs, the processor ; stalls until the self-write process in complete ; after write processor continues with 3rd instruction PMCON1,WREN BCF ; Disable writes BSF INTCON,GIE ; Enable interrupts

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| IOCCP7                                  | IOCCP6  | IOCCP5            | IOCCP4  | IOCCP3                                                | IOCCP2  | IOCCP1  | IOCCP0  |  |  |

| bit 7                                   |         |                   |         |                                                       |         |         | bit 0   |  |  |

|                                         |         |                   |         |                                                       |         |         |         |  |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |  |

| R = Readable bit W = Writable bit       |         |                   |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |

#### REGISTER 13-7: IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER

bit 7-0

bit 7-0

**IOCCP<7:0>:** Interrupt-on-Change PORTC Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-8: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCCN7  | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

IOCCN<7:0>: Interrupt-on-Change PORTC Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 13-9: IOCCF: INTERRUPT-ON-CHANGE PORTC FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCCF7     | IOCCF6     | IOCCF5     | IOCCF4     | IOCCF3     | IOCCF2     | IOCCF1     | IOCCF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCCF<7:0>: Interrupt-on-Change PORTC Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.

- 0 = No change was detected, or the user cleared the detected change.

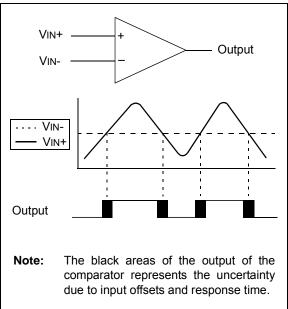

# 16.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- Programmable input selection

- Comparator output is available internally/ externally

- · Programmable output polarity

- Interrupt-on-Change

- · Wake-up from Sleep

- Programmable Speed/Power optimization

- PWM shutdown

- Programmable and Fixed Voltage Reference

### 16.1 Comparator Overview

A single comparator is shown in Figure 16-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 16-1.

| Device            | C1 | C2 |

|-------------------|----|----|

| PIC16(L)F1717/8/9 | •  | •  |

#### FIGURE 16-1: SINGLE COMPARATOR

# 17.2 Register Definitions: PWM Control

| REGISTER         | 1/-I. <b>FVVIV</b> |                         | CONTROL         | CEGISTER        |                  |                  |              |

|------------------|--------------------|-------------------------|-----------------|-----------------|------------------|------------------|--------------|

| R/W-0/0          | U-0                | R-0/0                   | R/W-0/0         | U-0             | U-0              | U-0              | U-0          |

| PWMxEN           | —                  | PWMxOUT                 | PWMxPOL         |                 | —                | —                | _            |

| bit 7            |                    |                         |                 |                 |                  |                  | bit 0        |

|                  |                    |                         |                 |                 |                  |                  |              |

| Legend:          |                    |                         |                 |                 |                  |                  |              |

| R = Readable     | e bit              | W = Writable            | bit             | U = Unimpler    | nented bit, read | d as '0'         |              |

| u = Bit is unch  | nanged             | nged x = Bit is unknown |                 | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                    | '0' = Bit is cle        | ared            |                 |                  |                  |              |

|                  |                    |                         |                 |                 |                  |                  |              |

| bit 7            | PWMxEN: P          | WM Module En            | able bit        |                 |                  |                  |              |

|                  | 1 = PWM mo         | odule is enable         | d               |                 |                  |                  |              |

|                  | 0 = PWM mo         | odule is disable        | d               |                 |                  |                  |              |

| bit 6            | Unimplemen         | ted: Read as '          | 0'              |                 |                  |                  |              |

| bit 5            | PWMxOUT:           | >WM module o            | utput level whe | en bit is read. |                  |                  |              |

| bit 4            | PWMxPOL:           | PWMx Output I           | Polarity Select | bit             |                  |                  |              |

|                  | 1 = PWM ou         | tput is active lo       | W.              |                 |                  |                  |              |

|                  | 0 = PWM ou         | tput is active hi       | gh.             |                 |                  |                  |              |

| bit 3-0          | Unimplemen         | ted: Read as '          | 0'              |                 |                  |                  |              |

# REGISTER 17-1: PWMxCON: PWM CONTROL REGISTER

# REGISTER 17-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PWMxD   | CH<7:0> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

## bit 7-0 **PWMxDCH<7:0>:** PWM Duty Cycle Most Significant bits These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

# REGISTER 17-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| PWMxDC  | CL<7:6> | —   | —   | —   | —   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | PWMxDCL<7:6>: PWM Duty Cycle Least Significant bits                                    |

|---------|----------------------------------------------------------------------------------------|

|         | These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register. |

| bit 5-0 | Unimplemented: Read as '0'                                                             |

# 18.2 Clock Sources

The COG\_clock is used as the reference clock to the various timers in the peripheral. Timers that use the COG\_clock include:

- · Rising and falling dead-band time

- Rising and falling blanking time

- · Rising and falling event phase delay

Clock sources available for selection include:

- 8 MHz HFINTOSC (active during Sleep)

- Instruction clock (Fosc/4)

- System clock (Fosc)

The clock source is selected with the GxCS<1:0> bits of the COGxCON0 register (Register 18-1).

### 18.3 Selectable Event Sources

The COG uses any combination of independently selectable event sources to generate the complementary waveform. Sources fall into two categories:

- · Rising event sources

- · Falling event sources

The rising event sources are selected by setting bits in the COGxRIS register (Register 18-3). The falling event sources are selected by setting bits in the COGxFIS register (Register 18-5). All selected sources are 'OR'd together to generate the corresponding event signal. Refer to Figure 18-7.

# 18.3.1 EDGE VS. LEVEL SENSING

Event input detection may be selected as level or edge sensitive. The detection mode is individually selectable for every source. Rising source detection modes are selected with the COGxRSIM register (Register 18-4). Falling source detection modes are selected with the COGxFSIM register (Register 18-6). A set bit enables edge detection for the corresponding event source. A cleared bit enables level detection.

In general, events that are driven from a periodic source should be edge detected and events that are derived from voltage thresholds at the target circuit should be level sensitive. Consider the following two examples:

1. The first example is an application in which the period is determined by a 50% duty cycle clock and the COG output duty cycle is determined by a voltage level fed back through a comparator. If the clock input is level sensitive, duty cycles less than 50% will exhibit erratic operation.

2. The second example is similar to the first except that the duty cycle is close to 100%. The feedback comparator high-to-low transition trips the COG drive off, but almost immediately the period source turns the drive back on. If the off cycle is short enough, the comparator input may not reach the low side of the hysteresis band precluding an output change. The comparator output stays low and without a high-to-low transition to trigger the edge sense, the drive of the COG output will be stuck in a constant drive-on condition. See Figure 18-14.

## FIGURE 18-14: EDGE VS LEVEL SENSE

| Rising (CCP1)   |

|-----------------|

| Falling (C1OUT) |

| C1IN- hyst I    |

| COGOUT          |

| Edge Sensitive  |

| Rising (CCP1)   |

| Falling (C1OUT) |

| C1IN- hyst      |

| COGOUT          |

| Level Sensitive |

## 18.3.2 RISING EVENT

The rising event starts the PWM output active duty cycle period. The rising event is the low-to-high transition of the rising\_event output. When the rising event phase delay and dead-band time values are zero, the primary output starts immediately. Otherwise, the primary output is delayed. The rising event source causes all the following actions:

- · Start rising event phase delay counter (if enabled).

- · Clear complementary output after phase delay.

- Start falling event input blanking (if enabled).

- · Start dead-band delay (if enabled).

- · Set primary output after dead-band delay expires.

#### 18.3.3 FALLING EVENT

The falling event terminates the PWM output active duty cycle period. The falling event is the high-to-low transition of the falling\_event output. When the falling event phase delay and dead-band time values are zero, the complementary output starts immediately. Otherwise, the complementary output is delayed. The falling event source causes all the following actions:

- Start falling event phase delay counter (if enabled).

- · Clear primary output.

- Start rising event input blanking (if enabled).

- Start falling event dead-band delay (if enabled).

- Set complementary output after dead-band delay expires.

| R/W-x/u                 | R/W-x/u                                                                          | R/W-x/u                                          | R/W-x/u        | R/W-x/u        | R/W-x/u                           | R/W-x/u          | R/W-x/u     |  |  |  |

|-------------------------|----------------------------------------------------------------------------------|--------------------------------------------------|----------------|----------------|-----------------------------------|------------------|-------------|--|--|--|

| LCxG3D4T                | LCxG3D4N                                                                         | LCxG3D3T                                         | LCxG3D3N       | LCxG3D2T       | LCxG3D2N                          | LCxG3D1T         | LCxG3D1N    |  |  |  |

| bit 7                   |                                                                                  |                                                  |                |                |                                   |                  | bit (       |  |  |  |

|                         |                                                                                  |                                                  |                |                |                                   |                  |             |  |  |  |

| Legend:<br>R = Readable | hit                                                                              |                                                  | h:t            | II – Unimplor  | nantad hit raad                   |                  |             |  |  |  |

| u = Bit is unch         |                                                                                  | W = Writable<br>x = Bit is unkr                  |                |                | nented bit, read<br>at POR and BO |                  | thar Dagata |  |  |  |

|                         | angeu                                                                            |                                                  |                |                | at FOR and BO                     | R/Value at all C | iner Reseis |  |  |  |

| '1' = Bit is set        |                                                                                  | '0' = Bit is clea                                | ared           |                |                                   |                  |             |  |  |  |

| bit 7                   | LCxG3D4T: (                                                                      | Gate 3 Data 4 1                                  | rue (non-inver | rted) bit      |                                   |                  |             |  |  |  |

|                         |                                                                                  | is gated into LO                                 | •              | ,              |                                   |                  |             |  |  |  |

|                         | 0 = LCxD4T                                                                       | is not gated int                                 | o LCxG3        |                |                                   |                  |             |  |  |  |

| bit 6                   | LCxG3D4N:                                                                        | Gate 3 Data 4 I                                  | Negated (inver | rted) bit      |                                   |                  |             |  |  |  |

|                         |                                                                                  | LCxD4N is gated into LCxG3                       |                |                |                                   |                  |             |  |  |  |

|                         | 0 = LCxD4N is not gated into LCxG3                                               |                                                  |                |                |                                   |                  |             |  |  |  |

| bit 5                   | LCxG3D3T: (                                                                      | <b>3T:</b> Gate 3 Data 3 True (non-inverted) bit |                |                |                                   |                  |             |  |  |  |

|                         |                                                                                  | T is gated into LCxG3                            |                |                |                                   |                  |             |  |  |  |

|                         |                                                                                  | is not gated int                                 |                |                |                                   |                  |             |  |  |  |

| bit 4                   |                                                                                  | Gate 3 Data 3 I                                  | •              | rted) bit      |                                   |                  |             |  |  |  |

|                         |                                                                                  | is gated into Lo<br>is not gated inf             |                |                |                                   |                  |             |  |  |  |

| <b>h</b> it 0           |                                                                                  | •                                                |                | ate al \ la it |                                   |                  |             |  |  |  |

| bit 3                   |                                                                                  | T: Gate 3 Data 2 True (non-inverted) bit         |                |                |                                   |                  |             |  |  |  |

|                         | 1 = LCxD2T is gated into LCxG3<br>0 = LCxD2T is not gated into LCxG3             |                                                  |                |                |                                   |                  |             |  |  |  |

| bit 2                   |                                                                                  | •                                                |                | rted) bit      |                                   |                  |             |  |  |  |

|                         | LCxG3D2N: Gate 3 Data 2 Negated (inverted) bit<br>1 = LCxD2N is gated into LCxG3 |                                                  |                |                |                                   |                  |             |  |  |  |

|                         | 0 = LCxD2N is not gated into LCxG3                                               |                                                  |                |                |                                   |                  |             |  |  |  |

| bit 1                   | LCxG3D1T: (                                                                      | Gate 3 Data 1 1                                  | rue (non-inver | rted) bit      |                                   |                  |             |  |  |  |

|                         | 1 = LCxD1T                                                                       | is gated into L0                                 | CxG3           |                |                                   |                  |             |  |  |  |

|                         | 0 = LCxD1T                                                                       | is not gated int                                 | o LCxG3        |                |                                   |                  |             |  |  |  |

| bit 0                   |                                                                                  | Gate 3 Data 1 I                                  | •              | rted) bit      |                                   |                  |             |  |  |  |

|                         |                                                                                  | is gated into L                                  |                |                |                                   |                  |             |  |  |  |

|                         | 0 = LCxD1N                                                                       | is not nated inf                                 | - 1 000        |                |                                   |                  |             |  |  |  |

# REGISTER 19-9: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

| REGISTE      | ER 21-2: A                                   | DCON1: ADC CO                                                                                                           |                                 | GISTER 1         |                  |                     |              |

|--------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|---------------------|--------------|

| R/W-0/       | 0 R/W-0/                                     | /0 R/W-0/0                                                                                                              | R/W-0/0                         | U-0              | R/W-0/0          | R/W-0/0             | R/W-0/0      |

| ADFM         | 1                                            | ADCS<2:0>                                                                                                               |                                 |                  | ADNREF           | ADPRI               | EF<1:0>      |

| bit 7        |                                              |                                                                                                                         |                                 |                  |                  |                     | bit C        |

| <u> </u>     |                                              |                                                                                                                         |                                 |                  |                  |                     |              |

| Legend:      |                                              |                                                                                                                         |                                 |                  |                  |                     |              |

| R = Read     |                                              | W = Writable I                                                                                                          |                                 |                  | mented bit, read |                     |              |

|              | unchanged                                    | x = Bit is unkn                                                                                                         |                                 | -n/n = Value     | at POR and BO    | R/Value at all      | other Resets |

| '1' = Bit is | set                                          | '0' = Bit is clea                                                                                                       | ared                            |                  |                  |                     |              |

| bit 7        | 1 = Righ<br>load                             | justified. Six Least                                                                                                    | Significant b                   |                  |                  |                     |              |

| bit 6-4      | 111 = FF<br>110 = Fc<br>101 = Fc<br>100 = Fc | osc/16<br>osc/4<br>RC (clock supplied f<br>osc/32<br>osc/8                                                              | rom an intern                   | al RC oscillato  |                  |                     |              |

| bit 3        | Unimple                                      | mented: Read as '                                                                                                       | )'                              |                  |                  |                     |              |

| bit 2        | 1 = VREF                                     | A/D Negative Volt<br>is connected to V<br>is connected to V                                                             | REF- pin                        | ce Configuration | n bit            |                     |              |

| bit 1-0      | 11 = VRE<br>10 = VRE<br>01 = Res             | <pre>E&lt;1:0&gt;: ADC Positiv<br/>EF+ is connected to<br/>EF+ is connected to<br/>served<br/>EF+ is connected to</pre> | internal Fixed<br>external VREF | l Voltage Refer  |                  | dule <sup>(1)</sup> |              |

| Note 1:      |                                              | ng the VREF+ pin as<br>exists. See Table 34                                                                             |                                 |                  |                  |                     | mum voltage  |

# REGISTER 21-2: ADCON1: ADC CONTROL REGISTER 1

|                           | U-0                                                                                                                                                                                                         | R-x/x                                                                 | R/W-0/0                                                                    | U-0                               | U-0                               | R/W-0/0      | R/W-0/0     |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------|-----------------------------------|--------------|-------------|

| ZCDxEN                    | —                                                                                                                                                                                                           | ZCDxOUT                                                               | ZCDxPOL                                                                    | —                                 | _                                 | ZCDxINTP     | ZCDxINTN    |

| bit 7                     |                                                                                                                                                                                                             |                                                                       |                                                                            |                                   |                                   |              | bit 0       |

| Lonondi                   |                                                                                                                                                                                                             |                                                                       |                                                                            |                                   |                                   |              |             |

| Legend:<br>R = Readable I | h:+                                                                                                                                                                                                         | M = Mritable                                                          | -:+                                                                        |                                   | nanted bit read                   | aa 'O'       |             |

|                           |                                                                                                                                                                                                             | W = Writable                                                          |                                                                            |                                   | nented bit, read                  |              |             |

| u = Bit is uncha          | angeo                                                                                                                                                                                                       | x = Bit is unkn                                                       |                                                                            |                                   | at POR and BOF                    |              | ther Resets |

| '1' = Bit is set          |                                                                                                                                                                                                             | '0' = Bit is clea                                                     | ared                                                                       | q = value dep                     | ends on configu                   | iration bits |             |

| bit 7                     | 1 = Zero-cros<br>0 = Zero-cros                                                                                                                                                                              | s detect is disa                                                      | bled. ZCD pir<br>abled. ZCD pir                                            | n is forced to o                  | utput to source a ording to PPS a |              |             |

| bit 6                     | Unimplemen                                                                                                                                                                                                  | ted: Read as '                                                        | )'                                                                         |                                   |                                   |              |             |

| bit 5                     | ZCDxPOL bit<br>1 = ZCD pin i<br>0 = ZCD pin i<br>ZCDxPOL bit<br>1 = ZCD pin i                                                                                                                               | s sinking curre<br>s sourcing curr<br><u>= 1</u> :<br>s sourcing curr | nt<br>rent                                                                 |                                   |                                   |              |             |

|                           | <ul> <li>0 = ZCD pin is sinking current</li> <li>ZCDxPOL: Zero-Cross Detection Logic Output Polarity bit</li> <li>1 = ZCD logic output is inverted</li> <li>0 = ZCD logic output is not inverted</li> </ul> |                                                                       |                                                                            |                                   |                                   |              |             |

| bit 4                     | <b>ZCDxPOL:</b> Ze 1 = ZCD logic                                                                                                                                                                            | ero-Cross Dete<br>c output is inve                                    | ction Logic O<br>rted                                                      | utput Polarity b                  | bit                               |              |             |

| bit 4<br>bit 3-2          | <b>ZCDxPOL:</b> Zet<br>1 = ZCD logic<br>0 = ZCD logic                                                                                                                                                       | ero-Cross Dete<br>c output is inve                                    | ction Logic O<br>rted<br>nverted                                           | utput Polarity b                  | bit                               |              |             |

|                           | <b>ZCDxPOL:</b> Ze<br>1 = ZCD logic<br>0 = ZCD logic<br><b>Unimplement</b><br><b>ZCDxINTP:</b> Z<br>1 = ZCDIF bit                                                                                           | ero-Cross Dete<br>c output is inve<br>c output is not i               | ction Logic Or<br>rted<br>nverted<br>o'<br>itive Edge Inte<br>o-high ZCDxC | errupt Enable b<br>DUT transition | it                                |              |             |

#### TABLE 25-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

| Name    | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1    | Bit 0    | Register<br>on page |

|---------|--------|-------|---------|---------|--------|--------|----------|----------|---------------------|

| PIE3    | —      | NCOIE | COGIE   | ZCDIE   | CLC4IE | CLC3IE | CLC2IE   | CLC1IE   | 93                  |

| PIR3    | —      | NCOIF | COGIF   | ZCDIF   | CLC4IF | CLC3IF | CLC2IF   | CLC1IF   | 96                  |

| ZCD1CON | ZCD1EN |       | ZCD10UT | ZCD1POL | _      |        | ZCD1INTP | ZCD1INTN | 267                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 25-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         | _       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 57                  |

|         | 7:0  | ZCDDIS  |         | _        | _        |          | PPS1WAY  | WRT     | <1:0>   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

25.9

Register Definitions: 7CD Control

| R-0/0            | R-1/1                                                                                                                    | U-0                                 | R/W-0/0                                                             | R/W-0/0          | U-0              | R/W-0/0          | R/W-0/0       |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------|------------------|------------------|------------------|---------------|--|--|

| ABDOVF           | RCIDL                                                                                                                    | _                                   | SCKP                                                                | BRG16            |                  | WUE              | ABDEN         |  |  |

| bit 7            | •                                                                                                                        |                                     |                                                                     |                  |                  | ·                | bit C         |  |  |

|                  |                                                                                                                          |                                     |                                                                     |                  |                  |                  |               |  |  |

| Legend:          |                                                                                                                          |                                     |                                                                     |                  |                  |                  |               |  |  |

| R = Readable     |                                                                                                                          |                                     | / = Writable bit U = Unimplemented bit, read as '0'                 |                  |                  |                  |               |  |  |

| u = Bit is unch  | nanged                                                                                                                   | x = Bit is unl                      | = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |                  |                  |                  |               |  |  |

| '1' = Bit is set |                                                                                                                          | '0' = Bit is cl                     | 0' = Bit is cleared                                                 |                  |                  |                  |               |  |  |

| bit 7            | ABDOVF: A                                                                                                                | uto-Baud Dete                       | ct Overflow bit                                                     |                  |                  |                  |               |  |  |

|                  |                                                                                                                          | ud timer overflo<br>ud timer did no |                                                                     |                  |                  |                  |               |  |  |

| bit 6            | <u>Asynchronou</u><br>1 = Receiver                                                                                       | is Idle<br>has been recei           | ved and the re-                                                     | ceiver is receiv | ing              |                  |               |  |  |

| bit 5            | Unimpleme                                                                                                                | nted: Read as                       | ʻ0 <b>'</b>                                                         |                  |                  |                  |               |  |  |

| bit 4            | SCKP: Synchronous Clock Polarity Select bit                                                                              |                                     |                                                                     |                  |                  |                  |               |  |  |

|                  | Asynchronous mode:                                                                                                       |                                     |                                                                     |                  |                  |                  |               |  |  |

|                  | <ul> <li>1 = Transmit inverted data to the TX/CK pin</li> <li>0 = Transmit non-inverted data to the TX/CK pin</li> </ul> |                                     |                                                                     |                  |                  |                  |               |  |  |

|                  |                                                                                                                          | locked on risin                     | g edge of the c<br>ng edge of the c                                 |                  |                  |                  |               |  |  |

| bit 3            | BRG16: 16-1                                                                                                              | oit Baud Rate                       | Generator bit                                                       |                  |                  |                  |               |  |  |

|                  |                                                                                                                          | aud Rate Gene<br>ud Rate Gener      |                                                                     |                  |                  |                  |               |  |  |

| bit 2            | Unimpleme                                                                                                                | nted: Read as                       | ʻ0 <b>'</b>                                                         |                  |                  |                  |               |  |  |

| bit 1            | WUE: Wake                                                                                                                | -up Enable bit                      |                                                                     |                  |                  |                  |               |  |  |

|                  | Asynchronous mode:                                                                                                       |                                     |                                                                     |                  |                  |                  |               |  |  |

|                  | will autor                                                                                                               | natically clear<br>is operating n   | after RCIF is se                                                    |                  | will be received | d, byte RCIF wil | l be set. WUI |  |  |

| bit 0            | ABDEN: Aut                                                                                                               | o-Baud Detect                       | Enable bit                                                          |                  |                  |                  |               |  |  |

|                  | Asynchronou                                                                                                              | us mode:                            |                                                                     |                  |                  |                  |               |  |  |

|                  |                                                                                                                          | ud Detect mod                       | le is enabled (c<br>le is disabled                                  | clears when au   | to-baud is com   | nplete)          |               |  |  |

# REGISTER 31-3: BAUD1CON: BAUD RATE CONTROL REGISTER