Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1717-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FIGURE 3-1         | PROGRAM MEMO<br>AND STACK FOR<br>PIC16(L)F1717   |                |

|--------------------|--------------------------------------------------|----------------|

| RETURI             | PC<14:0><br>L, CALLW<br>N, RETLW<br>t, RETFIE    | ]              |

|                    | Stack Level 0<br>Stack Level 1<br>Stack Level 15 |                |

|                    | Reset Vector                                     | 0000h          |

|                    | Interrupt Vector                                 | 0004h          |

| On-chip<br>Program | Page 0                                           | 0005h<br>07FFh |

| Memory             | Page 1                                           | 0800h<br>0FFFh |

|                    | Page 2                                           | 1000h<br>17FFh |

|                    | Page 3                                           | 1800h<br>1FFFh |

|                    | Rollover to Page 0                               | 2000h          |

|                    | •<br>•<br>•                                      |                |

|                    | Rollover to Page 1                               | 7FFFh          |

FIGURE 3-2:

#### PROGRAM MEMORY MAP AND STACK FOR PIC16(L)F1718/9

| PIC16(L)F1/18/9      |                    |                |  |  |  |  |  |  |  |  |

|----------------------|--------------------|----------------|--|--|--|--|--|--|--|--|

|                      | PC<14:0>           | I              |  |  |  |  |  |  |  |  |

|                      | CALL, CALLW        |                |  |  |  |  |  |  |  |  |

|                      | t, RETFIE          |                |  |  |  |  |  |  |  |  |

| Stack Level 0        |                    |                |  |  |  |  |  |  |  |  |

|                      | Stack Level 1      |                |  |  |  |  |  |  |  |  |

|                      | Stack Level 15     |                |  |  |  |  |  |  |  |  |

|                      |                    | J              |  |  |  |  |  |  |  |  |

|                      | Reset Vector       | 0000h          |  |  |  |  |  |  |  |  |

|                      | •                  |                |  |  |  |  |  |  |  |  |

| C                    | Interrupt Vector   | 0004h          |  |  |  |  |  |  |  |  |

|                      | Page 0             | 0005h          |  |  |  |  |  |  |  |  |

| On-chip<br>Program ≺ | i ago o            | 07FFh          |  |  |  |  |  |  |  |  |

| Memory               |                    | 0800h          |  |  |  |  |  |  |  |  |

|                      | Page 1             | 0FFFh          |  |  |  |  |  |  |  |  |

| C                    |                    | 1000h          |  |  |  |  |  |  |  |  |

|                      | Page 2             |                |  |  |  |  |  |  |  |  |

|                      |                    | 17FFh          |  |  |  |  |  |  |  |  |

|                      | Page 3             | 1800h          |  |  |  |  |  |  |  |  |

|                      |                    | 1FFFh          |  |  |  |  |  |  |  |  |

|                      | Page 4             | 2000h          |  |  |  |  |  |  |  |  |

|                      | Fage 4             | 27FFh          |  |  |  |  |  |  |  |  |

|                      |                    | 2800h          |  |  |  |  |  |  |  |  |

|                      | Page 5             | 2FFFh          |  |  |  |  |  |  |  |  |

|                      |                    | 3000h          |  |  |  |  |  |  |  |  |

|                      | Page 6             |                |  |  |  |  |  |  |  |  |

|                      |                    | 37FFh<br>3800h |  |  |  |  |  |  |  |  |

|                      | Page 7             | 500011         |  |  |  |  |  |  |  |  |

|                      |                    | 3FFFh          |  |  |  |  |  |  |  |  |

|                      | Rollover to Page 0 | 4000h          |  |  |  |  |  |  |  |  |

|                      |                    |                |  |  |  |  |  |  |  |  |

|                      |                    |                |  |  |  |  |  |  |  |  |

|                      |                    |                |  |  |  |  |  |  |  |  |

|                      | •                  |                |  |  |  |  |  |  |  |  |

|                      | •                  |                |  |  |  |  |  |  |  |  |

|                      |                    |                |  |  |  |  |  |  |  |  |

|                      |                    |                |  |  |  |  |  |  |  |  |

|                      | Dellever to Deve t |                |  |  |  |  |  |  |  |  |

|                      | Rollover to Page 1 | 7FFFh          |  |  |  |  |  |  |  |  |

#### 3.4.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.4.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The GPR occupies the 80 bytes after the SFR registers of selected data memory banks.

#### 3.4.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.7.2** "**Linear Data Memory**" for more information.

#### 3.4.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

FIGURE 3-3: BANKED MEMORY PARTITIONING

| 7-bit Bank Offset | Memory Region                                    |

|-------------------|--------------------------------------------------|

| 00h<br>0Bh        | Core Registers<br>(12 bytes)                     |

| 0Ch               | Special Function Registers<br>(20 bytes maximum) |

| 1Fh               |                                                  |

| 20h               | General Purpose RAM<br>(80 bytes maximum)        |

| 6Fh               |                                                  |

| 70h               | Common RAM<br>(16 bytes)                         |

| 7Fh               |                                                  |

#### 3.4.4 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-3 through Table 3-10.

# TABLE 3-5: PIC16(L)F1717 MEMORY MAP, BANK 8-23

|       | BANK 8                        |       | BANK 9                        |       | BANK 10                       |             | BANK 11                       |       | BANK 12                       |         | BANK 13                       |      | BANK 14                       |       | BANK 15                       |

|-------|-------------------------------|-------|-------------------------------|-------|-------------------------------|-------------|-------------------------------|-------|-------------------------------|---------|-------------------------------|------|-------------------------------|-------|-------------------------------|

| 400h  |                               | 480h  |                               | 500h  |                               | 580h        |                               | 600h  |                               | 680h    |                               | 700h |                               | 780h  |                               |

|       | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |             | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |         | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |

| 40Bh  |                               | 48Bh  |                               | 50Bh  |                               | 58Bh        |                               | 60Bh  |                               | 68Bh    |                               | 70Bh |                               | 78Bh  |                               |

| 40Ch  | —                             | 48Ch  |                               | 50Ch  | —                             | 58Ch        |                               | 60Ch  |                               | 68Ch    | —                             | 70Ch | —                             | 78Ch  | —                             |

| 40Dh  | _                             | 48Dh  | _                             | 50Dh  | _                             | 58Dh        | _                             | 60Dh  | _                             | 68Dh    | _                             | 70Dh | _                             | 78Dh  | —                             |

| 40Eh  | _                             | 48Eh  | —                             | 50Eh  | —                             | 58Eh        | —                             | 60Eh  | —                             | 68Eh    | —                             | 70Eh | —                             | 78Eh  | —                             |

| 40Fh  | _                             | 48Fh  | —                             | 50Fh  | —                             | 58Fh        | —                             | 60Fh  | —                             | 68Fh    | —                             | 70Fh | —                             | 78Fh  | —                             |

| 410h  | —                             | 490h  | —                             | 510h  | —                             | 590h        | _                             | 610h  | —                             | 690h    | —                             | 710h | —                             | 790h  | —                             |

| 411h  | —                             | 491h  | —                             | 511h  | OPA1CON                       | 591h        | _                             | 611h  | —                             | 691h    | COG1PHR                       | 711h | —                             | 791h  | —                             |

| 412h  | —                             | 492h  | _                             | 512h  | —                             | 592h        | _                             | 612h  | _                             | 692h    | COG1PHF                       | 712h | —                             | 792h  | —                             |

| 413h  | _                             | 493h  | _                             | 513h  | —                             | 593h        |                               | 613h  |                               | 693h    | COG1BLKR                      | 713h | —                             | 793h  | _                             |

| 414h  | -                             | 494h  | _                             | 514h  | —                             | 594h        | _                             | 614h  | _                             | 694h    | COG1BLKF                      | 714h | _                             | 794h  | —                             |

| 415h  | TMR4                          | 495h  | _                             | 515h  | OPA2CON                       | 595h        | _                             | 615h  | _                             | 695h    | COG1DBR                       | 715h | _                             | 795h  | —                             |

| 416h  | PR4                           | 496h  | —                             | 516h  |                               | 596h        | _                             | 616h  | _                             | 696h    | COG1DBF                       | 716h | _                             | 796h  | _                             |

| 417h  | T4CON                         | 497h  | _                             | 517h  | —                             | 597h        | —                             | 617h  | PWM3DCL                       | 697h    | COG1CON0                      | 717h | —                             | 797h  | _                             |

| 418h  | -                             | 498h  | NCO1ACCL                      | 518h  | —                             | 598h        | —                             | 618h  | PWM3DCH                       | 698h    | COG1CON1                      | 718h | —                             | 798h  | —                             |

| 419h  | _                             | 499h  | NCO1ACCH                      | 519h  |                               | 599h        | _                             | 619h  | PWM3CON                       | 699h    | COG1RIS                       | 719h | _                             | 799h  | _                             |

| 41Ah  | -                             | 49Ah  | NCO1ACCU                      | 51Ah  | _                             | 59Ah        | _                             | 61Ah  | PWM4DCL                       | 69Ah    | COG1RSIM                      | 71Ah | _                             | 79Ah  | _                             |

| 41Bh  | _                             | 49Bh  | NCO1INCL                      | 51Bh  |                               | 59Bh        | _                             | 61Bh  | PWM4DCH                       | 69Bh    | COG1FIS                       | 71Bh | _                             | 79Bh  | _                             |

| 41Ch  | TMR6                          | 49Ch  | NCO1INCH                      | 51Ch  | _                             | 59Ch        | _                             | 61Ch  | PWM4CON                       | 69Ch    | COG1FSIM                      | 71Ch | _                             | 79Ch  | _                             |

| 41Dh  | PR6                           | 49Dh  | NCO1INCU                      | 51Dh  | _                             | 59Dh        | _                             | 61Dh  | _                             | 69Dh    | COG1ASD0                      | 71Dh | _                             | 79Dh  | _                             |

| 41Eh  | T6CON                         | 49Eh  | NCO1CON                       | 51Eh  | _                             | 59Eh        | _                             | 61Eh  | _                             | 69Eh    | COG1ASD1                      | 71Eh | _                             | 79Eh  | _                             |

| 41Fh  | _                             | 49Fh  | NCO1CLK                       | 51Fh  | _                             | 59Fh        | _                             | 61Fh  | _                             | 69Fh    | COG1STR                       | 71Fh | _                             | 79Fh  | _                             |

| 420h  |                               | 4A0h  |                               | 520h  |                               | 5A0h        |                               | 620h  | General Purpose               | 6A0h    |                               | 720h |                               | 7A0h  |                               |

|       | General                       |       | General                       |       | General                       |             | General                       |       | Register 48 Bytes             |         |                               |      |                               |       |                               |

|       | Purpose                       |       | Purpose                       |       | Purpose                       |             | Purpose                       | 64Fh  | register to bytes             |         | Unimplemented                 |      | Unimplemented                 |       | Unimplemented                 |

|       | Register                      |       | Register                      |       | Register                      |             | Register                      | 650h  | Unimplemented                 |         | Read as '0'                   |      | Read as '0'                   |       | Read as '0'                   |

|       | 80 Bytes                      |       | 80 Bytes                      |       | 80 Bytes                      |             | 80 Bytes                      |       | Read as '0'                   |         |                               |      |                               |       |                               |

| 46Fh  |                               | 4EFh  |                               | 56Fh  |                               | 5EFh        |                               | 66Fh  |                               | 6EFh    |                               | 76Fh |                               | 7EFh  |                               |

| 470h  |                               | 4F0h  |                               | 570h  |                               | 5F0h        |                               | 670h  |                               | 6F0h    |                               | 770h |                               | 7F0h  |                               |

|       | Accesses                      |       | Accesses                      |       | Accesses                      |             | Accesses                      |       | Accesses                      |         | Accesses                      |      | Accesses                      |       | Accesses                      |

|       | 70h – 7Fh                     |       | 70h – 7Fh                     |       | 70h – 7Fh                     |             | 70h – 7Fh                     |       | 70h – 7Fh                     |         | 70h – 7Fh                     |      | 70h – 7Fh                     |       | 70h – 7Fh                     |

| 47Fh  |                               | 4FFh  |                               | 57Fh  |                               | 5FFh        |                               | 67Fh  |                               | 6FFh    |                               | 77Fh |                               | 7FFh  |                               |

|       | BANK 16                       |       | BANK 17                       |       | BANK 18                       |             | BANK 19                       |       | BANK 20                       |         | BANK 21                       |      | BANK 22                       |       | BANK 23                       |

| 800h  |                               | 880h  |                               | 900h  |                               | 980h        |                               | A00h  |                               | A80h    |                               | B00h |                               | B80h  |                               |

|       | Core Registers                |       | Core Registers                | 00011 | Core Registers                |             | Core Registers                | ,     | Core Registers                | / 10011 | Core Registers                | 200  | Core Registers                | 2000  | Core Registers                |

|       | (Table 3-2)                   |       | (Table 3-2)                   |       | (Table 3-2)                   |             | (Table 3-2)                   |       | (Table 3-2)                   |         | (Table 3-2)                   |      | (Table 3-2)                   |       | (Table 3-2)                   |

| 80Bh  | · · · ·                       | 88Bh  | , ,                           | 90Bh  | ,                             | 98Bh        | ( )                           | A0Bh  |                               | A8Bh    | , ,                           | B0Bh | , ,                           | B8Bh  | · · · ·                       |

| 80Ch  |                               | 88Ch  |                               | 90Ch  |                               | 98Ch        |                               | A0Ch  |                               | A8Ch    |                               | B0Ch |                               | B8Ch  |                               |

| 00C11 | Linimalomented                | 00011 | Unimplemented                 | 90011 | Unimplemented                 | 90011       | Unimplemented                 | AUCII | Unimplemented                 | ACCII   |                               | BUCH | Unimplemented                 | DOCII | Unimplemented                 |

|       | Unimplemented                 |       | Unimplemented                 |       |                               |             | Unimplemented                 |       | Read as '0'                   |         | Unimplemented                 |      | Unimplemented<br>Read as '0'  |       | Unimplemented                 |

|       | Read as '0'                   |       | Read as '0'                   |       | Read as '0'                   |             | Read as '0'                   |       | Reau as 0                     |         | Read as '0'                   |      | Reau as 0                     |       | Read as '0'                   |

| 86Fh  |                               | 8EFh  |                               | 96Fh  |                               | 9EFh        |                               | A6Fh  |                               | AEFh    |                               | B6Fh |                               | BEFh  |                               |

| 870h  | Accesses                      | 8F0h  | Accesses                      | 970h  | Accesses                      | 9F0h        | Accesses                      | A70h  | Accesses                      | AF0h    | Accesses                      | B70h | Accesses                      | BF0h  | Accesses                      |

|       | 70h – 7Fh                     |       | 70h – 7Fh                     |       | 70h – 7Fh                     |             | 70h – 7Fh                     |       | 70h – 7Fh                     |         | 70h – 7Fh                     |      | 70h – 7Fh                     |       | 70h – 7Fh                     |

| 87Fh  | 7011 - 7111                   | 8FFh  |                               | 97Fh  | 7011-7111                     | 9FFh        | 7011-7111                     | A7Fh  | 7011 - 7111                   | AFFh    | 7011-7111                     | B7Fh | 7011-7111                     | BFFh  | 1011 - 1111                   |

| 1     |                               |       | ad data mamaru la             |       | 1                             | · • · · · · | L                             |       | L                             |         | L                             | 1    |                               |       |                               |

Legend: = Unimplemented data memory locations, read as '0'.

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection is controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

### 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

# 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F170X Memory Programming Specification"* (DS41683).

# 4.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access**" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

# 5.0 RESETS

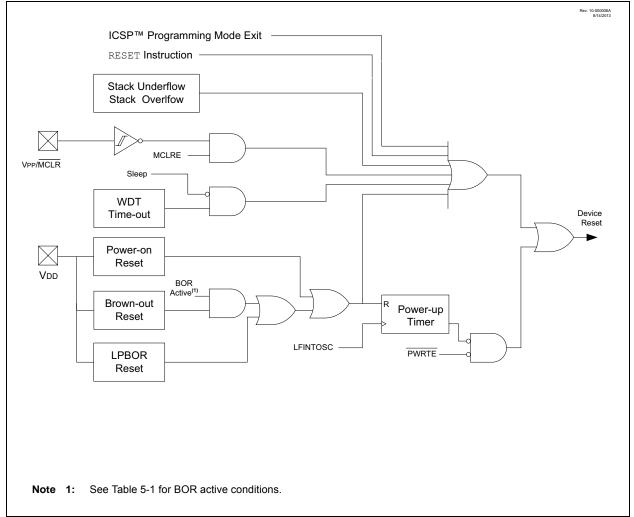

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 8.3 **Register Definitions: Voltage Regulator Control**

| U-0                               | U-0                                 | U-0                  | U-0                                | U-0                                                   | U-0 | R/W-0/0 | R/W-1/1  |  |

|-----------------------------------|-------------------------------------|----------------------|------------------------------------|-------------------------------------------------------|-----|---------|----------|--|

| —                                 | —                                   | —                    | —                                  | —                                                     | —   | VREGPM  | Reserved |  |

| bit 7                             |                                     |                      |                                    |                                                       |     |         | bit 0    |  |

|                                   |                                     |                      |                                    |                                                       |     |         |          |  |

| Legend:                           |                                     |                      |                                    |                                                       |     |         |          |  |

| R = Readable bit W = Writable bit |                                     |                      | U = Unimplemented bit, read as '0' |                                                       |     |         |          |  |

| u = Bit is unch                   | Bit is unchanged x = Bit is unknown |                      |                                    | -n/n = Value at POR and BOR/Value at all other Resets |     |         |          |  |

| '1' = Bit is set                  |                                     | '0' = Bit is cleared |                                    |                                                       |     |         |          |  |

#### VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup> **REGISTER 8-1:**

bit 7-2 Unimplemented: Read as '0'

| hit | 1 |

|-----|---|

| DIL |   |

- VREGPM: Voltage Regulator Power Mode Selection bit 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

- Draws lowest current in Sleep, slower wake-up

- 0 = Normal-Power mode enabled in Sleep<sup>(2)</sup>

- Draws higher current in Sleep, faster wake-up

bit 0 Reserved: Read as '1'. Maintain this bit set.

Note 1: PIC16F1717/8/9 only.

2: See Section 34.0 "Electrical Specifications".

#### **TABLE 8-1:** SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0    | Register<br>on Page |

|------------------------|-------|-------|-------|-------|--------|-------|--------|----------|---------------------|

| STATUS                 | _     | _     |       | TO    | PD     | Z     | DC     | С        | 28                  |

| VREGCON <sup>(1)</sup> | _     | _     | _     | _     | _      |       | VREGPM | Reserved | 101                 |

| WDTCON                 | _     |       |       | V     | SWDTEN | 104   |        |          |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode. Note 1: PIC16F1717/8/9 only.

# 17.1 PWMx Pin Configuration

All PWM outputs are multiplexed with the PORT data latch. The user must configure the pins as outputs by clearing the associated TRIS bits.

#### 17.1.1 FUNDAMENTAL OPERATION

The PWM module produces a 10-bit resolution output. Timer2 and PR2 set the period of the PWM. The PWMxDCL and PWMxDCH registers configure the duty cycle. The period is common to all PWM modules, whereas the duty cycle is independently controlled.

**Note:** The Timer2 postscaler is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

All PWM outputs associated with Timer2 are set when TMR2 is cleared. Each PWMx is cleared when TMR2 is equal to the value specified in the corresponding PWMxDCH (8 MSb) and PWMxDCL<7:6> (2 LSb) registers. When the value is greater than or equal to PR2, the PWM output is never cleared (100% duty cycle).

Note: The PWMxDCH and PWMxDCL registers are double buffered. The buffers are updated when Timer2 matches PR2. Care should be taken to update both registers before the timer match occurs.

#### 17.1.2 PWM OUTPUT POLARITY

The output polarity is inverted by setting the PWMxPOL bit of the PWMxCON register.

#### 17.1.3 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 17-1.

#### EQUATION 17-1: PWM PERIOD

PWM Period = [(PR2) + 1] • 4 • Tosc • (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWM output is active. (Exception: When the PWM duty cycle = 0%, the PWM output will remain inactive.)

- The PWMxDCH and PWMxDCL register values are latched into the buffers.

| Note: | The Timer2 postscaler has no effect on the |

|-------|--------------------------------------------|

|       | PWM operation.                             |

#### 17.1.4 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDCH and PWMxDCL register pair. The PWMxDCH register contains the eight MSbs and the PWMxDCL<7:6>, the two LSbs. The PWMxDCH and PWMxDCL registers can be written to at any time.

Equation 17-2 is used to calculate the PWM pulse width.

Equation 17-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 17-2: PULSE WIDTH

$Pulse Width = (PWMxDCH:PWMxDCL<7:6>) \bullet$

TOSC • (TMR2 Prescale Value)

Note: Tosc = 1/Fosc

# EQUATION 17-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(PWMxDCH:PWMxDCL<7:6>)}{4(PR2+1)}$

The 8-bit timer TMR2 register is concatenated with the two Least Significant bits of 1/Fosc, adjusted by the Timer2 prescaler to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

#### 17.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- 7. Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the desired pin PPS control bits.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- **2:** For operation with other peripherals only, disable PWMx pin outputs.

# 17.1.10 SETUP FOR PWM OPERATION TO OTHER DEVICE PERIPHERALS

The following steps should be taken when configuring the module for PWM operation to be used by other device peripherals:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- 7. Configure the PWM module by loading the PWMxCON register with the appropriate values.

**Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

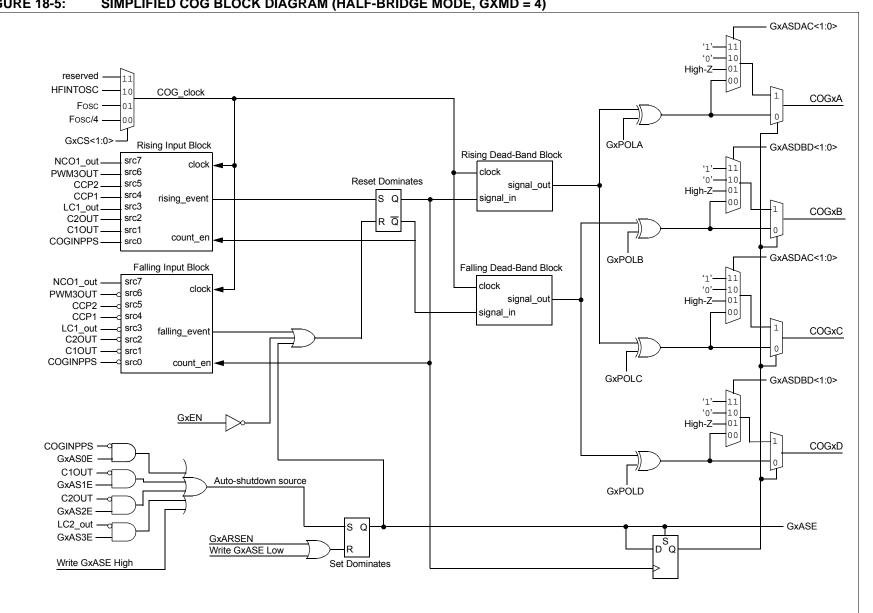

#### 18.1.3 HALF-BRIDGE MODE

In half-bridge mode, the COG generates a two output complementary PWM waveform from rising and falling event sources. In the simplest configuration, the rising and falling event sources are the same signal, which is a PWM signal with the desired period and duty cycle. The COG converts this single PWM input into a dual complementary PWM output. The frequency and duty cycle of the dual PWM output match those of the single input PWM signal. The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time immediately after the PWM transition where neither output is driven. This is referred to as dead time and is covered in **Section 18.5 "Dead-Band Control"**.

A typical operating waveform, with dead band, generated from a single CCP1 input is shown in Figure 18-9.

The primary output can be steered to either or both COGxA and COGxC. The complementary output can be steered to either or both COGxB and COGxD.

Half-Bridge mode is selected by setting the GxMD bits of the COGxCON0 register to '100'.

#### 18.1.4 PUSH-PULL MODE

In Push-Pull mode, the COG generates a single PWM output that alternates, every PWM period, between the two pairs of the COG outputs. COGxA has the same signal as COGxC. COGxB has the same signal as COGxD. The output drive activates with the rising input event and terminates with the falling event input. Each rising event starts a new period and causes the output to switch to the COG pair not used in the previous period.

The push-pull configuration is shown in Figure 18-6. A typical push-pull waveform generated from a single CCP1 input is shown in Figure 18-11.

Push-Pull mode is selected by setting the GxMD bits of the COGxCON0 register to '101'.

#### 18.1.5 EVENT DRIVEN PWM (ALL MODES)

Besides generating PWM and complementary outputs from a single PWM input, the COG can also generate PWM waveforms from a periodic rising event and a separate falling event. In this case, the falling event is usually derived from analog feedback within the external PWM driver circuit. In this configuration, high power switching transients may trigger a false falling event that needs to be blanked out. The COG can be configured to blank falling (and rising) event inputs for a period of time immediately following the rising (and falling) event drive output. This is referred to as input blanking and is covered in **Section 18.6 "Blanking Control"**. It may be necessary to guard against the possibility of circuit faults. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 18.8 "Auto-shutdown Control"**.

The COG can be configured to operate in phase delayed conjunction with another PWM. The active drive cycle is delayed from the rising event by a phase delay timer. Phase delay is covered in more detail in **Section 18.7 "Phase Delay"**.

A typical operating waveform, with phase delay and dead band, generated from a single CCP1 input is shown in Figure 18-10.

PIC16(L)F1717/8/9

#### **FIGURE 18-5:** SIMPLIFIED COG BLOCK DIAGRAM (HALF-BRIDGE MODE, GXMD = 4)

# 19.6 Register Definitions: CLC Control

| R/W-0/0                                                                                    |               | R-0/0                               | R/W-0/0         | R/W-0/0          | R/W-0/0         | R/W-0/0           | R/W-0/0     |

|--------------------------------------------------------------------------------------------|---------------|-------------------------------------|-----------------|------------------|-----------------|-------------------|-------------|

|                                                                                            |               | LCxOUT                              | LCxINTP         | LCXINTN          |                 | LCxMODE<2:0>      |             |

| bit 7                                                                                      |               |                                     |                 |                  |                 |                   | bit         |

|                                                                                            |               |                                     |                 |                  |                 |                   |             |

| Legend:                                                                                    |               |                                     |                 |                  |                 |                   |             |

| R = Readab                                                                                 | ole bit       | W = Writable                        | bit             | U = Unimpler     | nented bit, rea | d as '0'          |             |

| u = Bit is ur                                                                              | nchanged      | x = Bit is unki                     | nown            | -n/n = Value a   | at POR and BC   | DR/Value at all c | ther Resets |

| '1' = Bit is s                                                                             | et            | '0' = Bit is cle                    | ared            |                  |                 |                   |             |

|                                                                                            |               |                                     |                 |                  |                 |                   |             |

| bit 7                                                                                      | LCxEN: Cont   | figurable Logic                     | Cell Enable b   | it               |                 |                   |             |

|                                                                                            |               | able logic cell i                   |                 |                  |                 |                   |             |

| <b>h</b> # C                                                                               | •             | able logic cell i                   |                 | a has logic zero | output          |                   |             |

| bit 6                                                                                      | •             | ted: Read as '                      |                 |                  |                 |                   |             |

| bit 5                                                                                      |               | nfigurable Logi                     |                 | •                | from love out   |                   |             |

|                                                                                            | -             | gic cell output                     |                 | •                | —               |                   |             |

| bit 4                                                                                      |               | onfigurable Log                     |                 | 0 0              |                 | e bit             |             |

|                                                                                            |               | will be set wher<br>will not be set | r a rising edge | e occurs on icx  | _oui            |                   |             |

| bit 3                                                                                      | LCxINTN: Co   | onfigurable Log                     | ic Cell Negativ | ve Edae Goina    | Interrupt Enab  | ole bit           |             |

|                                                                                            |               | will be set when                    | •               | • •              | •               |                   |             |

|                                                                                            | 0 = CLCxIF    | will not be set                     |                 |                  | _               |                   |             |

| bit 2-0                                                                                    | LCxMODE<2     | 2:0>: Configura                     | ble Logic Cell  | Functional Mo    | de bits         |                   |             |

|                                                                                            |               | 1-input transpa                     |                 | h S and R        |                 |                   |             |

|                                                                                            |               | J-K flip-flop wi                    |                 |                  |                 |                   |             |

| 101 = Cell is 2-input D flip-flop with R<br>100 = Cell is 1-input D flip-flop with S and R |               |                                     |                 |                  |                 |                   |             |

|                                                                                            | 011 = Cell is | • •                                 |                 |                  |                 |                   |             |

|                                                                                            | 010 = Cell is |                                     |                 |                  |                 |                   |             |

|                                                                                            | 001 = Cell is | •                                   |                 |                  |                 |                   |             |

|                                                                                            | 000 = Cell is | AND-OR                              |                 |                  |                 |                   |             |

#### REGISTER 19-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

# 20.0 NUMERICALLY CONTROLLED OSCILLATOR (NCO) MODULE

The Numerically Controlled Oscillator (NCOx) module is a timer that uses the overflow from the addition of an increment value to divide the input frequency. The advantage of the addition method over simple counter driven timer is that the resolution of division does not vary with the divider value. The NCOx is most useful for applications that require frequency accuracy and fine resolution at a fixed duty cycle.

Features of the NCOx include:

- 20-bit increment function

- Fixed Duty Cycle (FDC) mode

- Pulse Frequency (PF) mode

- Output pulse width control

- Multiple clock input sources

- Output polarity control

- Interrupt capability

Figure 20-1 is a simplified block diagram of the NCOx module.

### 20.1 NCOx Operation

The NCOx operates by repeatedly adding a fixed value to an accumulator. Additions occur at the input clock rate. The accumulator will overflow with a carry periodically, which is the raw NCOx output (NCO\_overflow). This effectively reduces the input clock by the ratio of the addition value to the maximum accumulator value. See Equation 20-1.

The NCOx output can be further modified by stretching the pulse or toggling a flip-flop. The modified NCOx output is then distributed internally to other peripherals and optionally output to a pin. The accumulator overflow also generates an interrupt (NCO\_interrupt).

The NCOx period changes in discrete steps to create an average frequency. This output depends on the ability of the receiving circuit (i.e., CWG or external resonant converter circuitry) to average the NCOx output to reduce uncertainty.

#### 20.1.1 NCOx CLOCK SOURCES

Clock sources available to the NCOx include:

- HFINTOSC

- Fosc

- LC3\_out

The NCOx clock source is selected by configuring the NxCKS<2:0> bits in the NCOxCLK register.

#### 20.1.2 ACCUMULATOR

The accumulator is a 20-bit register. Read and write access to the accumulator is available through three registers:

- NCOxACCL

- NCOxACCH

- NCOxACCU

#### 20.1.3 ADDER

The NCOx adder is a full adder, which operates independently from the system clock. The addition of the previous result and the increment value replaces the accumulator value on the rising edge of each input clock.

#### 20.1.4 INCREMENT REGISTERS

The increment value is stored in three registers making up a 20-bit increment. In order of LSB to MSB they are:

- NCOxINCL

- NCOxINCH

- NCOxINCU

When the NCO module is enabled, the NCOxINCU and NCOxINCH registers should be written first, then the NCOxINCL register. Writing to the NCOxINCL register initiates the increment buffer registers to be loaded simultaneously on the second rising edge of the NCOx\_clk signal.

The registers are readable and writable. The increment registers are double-buffered to allow value changes to be made without first disabling the NCOx module.

When the NCO module is disabled, the increment buffers are loaded immediately after a write to the increment registers.

Note: The increment buffer registers are not user-accessible.

#### EQUATION 20-1:

FOVERFLOW= NCO Clock Frequency × Increment Value

$2^n$

n = Accumulator width in bits

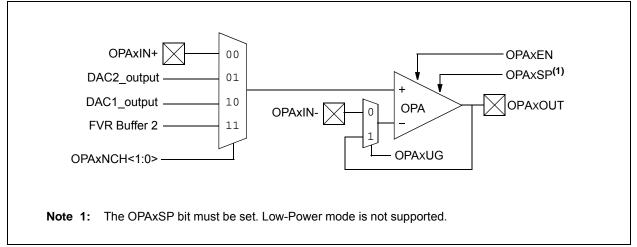

# 22.0 OPERATIONAL AMPLIFIER (OPA) MODULES

The Operational Amplifier (OPA) is a standard three-terminal device requiring external feedback to operate. The OPA module has the following features:

- External connections to I/O ports

- Low leakage inputs

- · Factory Calibrated Input Offset Voltage

# 27.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 27.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

# 27.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 27.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 27.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 27.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 27.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 27-3 for timing details.

TABLE 27-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| 1          | 1      | 1   | Counts           |

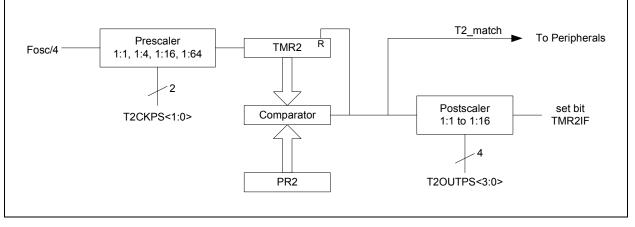

# 28.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that incorporate the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- · Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match with PR2, respectively

- Optional use as the shift clock for the MSSP module

See Figure 28-1 for a block diagram of Timer2.

Three identical Timer2 modules are implemented on this device. To maintain consistency with earlier devices, the timers are named Timer2, Timer4, and Timer6. All references to Timer2 apply as well to Timer4 and Timer6.

# PIC16(L)F1717/8/9

| FIGURE 30-9:                        | SPI N                                 | IODE W     | /AVEFO                | RM (SL                                     | AVE MC               | DE WIT           | HCKE                                   | = 0)                                             |                                                     |                                                                                   |                 |

|-------------------------------------|---------------------------------------|------------|-----------------------|--------------------------------------------|----------------------|------------------|----------------------------------------|--------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|

|                                     | ·<br>·                                |            |                       |                                            |                      |                  |                                        |                                                  |                                                     |                                                                                   | <br>            |

|                                     | -<br>-<br>-<br>-<br>-<br>-<br>-       |            | -<br>                 | ·<br>· · · · · · · · · · · · · · · · · · · |                      |                  | -<br>                                  |                                                  |                                                     | •                                                                                 | :<br>:<br>:<br> |

| 80%<br>(CKF = 1<br>(CKF = 0)        | ·<br>·<br>·<br>·                      |            |                       |                                            | ,<br>,<br>,          |                  |                                        | ,<br>                                            | ,<br>,<br>,,                                        |                                                                                   | 3<br>           |

| WERE 10<br>SEP (BUF<br>VER11<br>SEC |                                       |            |                       |                                            |                      |                  |                                        | ,<br>,<br>,<br>, , , , , , , , , , , , , , , , , | ;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>;<br>; | :<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>: | ·<br>·<br>·     |

|                                     |                                       |            | <br>;<br>;<br>;       | ,                                          | ,                    | ,                | /~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | /                                                |                                                     | , , , , , , , , , , , , , , , , , , ,                                             |                 |

| lapat<br>Secupio                    |                                       | 1941 7<br> | *<br>*<br>*<br>*<br>* | :<br>:<br>:<br>:<br>:<br>:                 | :<br>:<br>: 49:<br>: |                  | ;<br>;<br>;<br>;<br>;                  | <i>14-</i>                                       | : 33<br>:<br>:<br>:<br>:<br>:<br>:                  | 20<br>2<br>2                                                                      |                 |

|                                     |                                       |            | s<br>c<br>s<br>s      | <                                          | 2<br>2<br>2<br>2     | ;<br>;<br>,<br>, | s<br>c<br>s<br>s                       | 2<br>2<br>2<br>2                                 | ×<br>×<br><<br>&                                    | :<br>:<br>:<br>:                                                                  |                 |

| 9.891982 85<br>86919609             | · · · · · · · · · · · · · · · · · · · |            | -<br>2<br>2<br>2      | ,<br>5<br>7<br>7                           | •<br>\$<br>\$<br>•   |                  | -<br>2<br>2<br>2                       | ,<br>5<br>7<br>7                                 | s :<br>s                                            | ,<br>/p.<br>,                                                                     |                 |

| Virite Catistan<br>detection active |                                       |            |                       |                                            | ********             |                  |                                        |                                                  | *******                                             |                                                                                   |                 |

### FIGURE 30-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| $\overline{SS}$ SCK (CKP = 0 CKE = 1) SCK (CKP = 1 CKE = 1) Write to SSP1BUF Value |                                 |             |                     |        |                       |                            |             |                            |                            |             |

|------------------------------------------------------------------------------------|---------------------------------|-------------|---------------------|--------|-----------------------|----------------------------|-------------|----------------------------|----------------------------|-------------|

| SDO ——                                                                             |                                 | bit 7       | bit 6               | bit 5  | bit 4                 | bit 3                      | bit 2       | bit 1                      | bit 0                      |             |

| SDI ——                                                                             | 1<br><u>1</u><br>1              |             | $\sim$              | $\sim$ | $\sim$                |                            | $\sim$      |                            | bit 0                      |             |

| Input<br>Sample                                                                    |                                 | 1           | 1                   | 1      | 1                     | <u>↑</u>                   | 1           | 1                          | 1                          |             |

| SSP1IF<br>Interrupt<br>Flag                                                        | -<br>-<br>-<br>-<br>-<br>-<br>- |             | <br> <br> <br> <br> | 1<br>1 | 1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1 |             | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1 |             |

| SSP1SR to<br>SSP1BUF                                                               | ;<br>;<br>;<br>;                | 1<br>1<br>1 | <br> <br> <br>      | I      | 1<br>1<br>1<br>1      | 1<br>1<br>1<br>T           | 1<br>1<br>1 | 1<br>1<br>1<br>1           | 1<br>1 / /<br>1            | <u>.</u>    |

| Vote Collegion<br>Anterior polive                                                  |                                 |             |                     |        |                       | •                          | •           | •                          | •                          | ,<br>,<br>, |

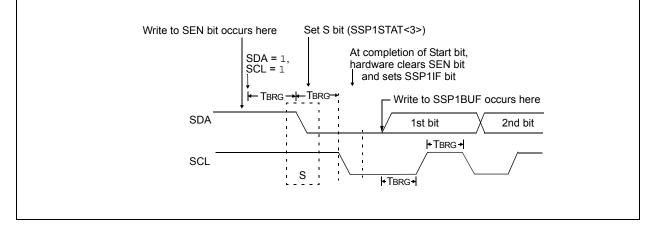

### 30.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 30-26), the user sets the Start Enable bit, SEN bit of the SSP1CON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSP1STAT register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSP1CON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCL1IF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C specification states that a bus collision cannot occur on a Start.

# FIGURE 30-26: FIRST START BIT TIMING

| R-0/0            | R-1/1                                                                                                                                                                                             | U-0                                                                      | R/W-0/0                                             | R/W-0/0          | U-0             | R/W-0/0          | R/W-0/0       |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|------------------|-----------------|------------------|---------------|--|--|--|--|--|

| ABDOVF           | RCIDL                                                                                                                                                                                             | _                                                                        | SCKP                                                | BRG16            |                 | WUE              | ABDEN         |  |  |  |  |  |

| bit 7            | •                                                                                                                                                                                                 |                                                                          | •                                                   |                  |                 |                  | bit C         |  |  |  |  |  |

|                  |                                                                                                                                                                                                   |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

| Legend:          |                                                                                                                                                                                                   |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

| R = Readable     |                                                                                                                                                                                                   |                                                                          | W = Writable bit U = Unimplemented bit, read as '0' |                  |                 |                  |               |  |  |  |  |  |

| u = Bit is unch  | 0                                                                                                                                                                                                 | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                                                     |                  |                 |                  |               |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                   | '0' = Bit is cl                                                          | '0' = Bit is cleared                                |                  |                 |                  |               |  |  |  |  |  |

| bit 7            | ABDOVF: A                                                                                                                                                                                         | uto-Baud Dete                                                            | ct Overflow bit                                     |                  |                 |                  |               |  |  |  |  |  |

|                  |                                                                                                                                                                                                   | ud timer overflo<br>ud timer did no                                      |                                                     |                  |                 |                  |               |  |  |  |  |  |

| bit 6            | <u>Asynchronou</u><br>1 = Receiver                                                                                                                                                                | is Idle<br>has been recei                                                | bit<br>ved and the rea                              | ceiver is receiv | ring            |                  |               |  |  |  |  |  |

| bit 5            | Unimpleme                                                                                                                                                                                         | n <b>ted:</b> Read as                                                    | '0'                                                 |                  |                 |                  |               |  |  |  |  |  |

| bit 4            | SCKP: Synchronous Clock Polarity Select bit                                                                                                                                                       |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

|                  | Asynchronous mode:                                                                                                                                                                                |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

|                  | <ul> <li>1 = Transmit inverted data to the TX/CK pin</li> <li>0 = Transmit non-inverted data to the TX/CK pin</li> </ul>                                                                          |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

|                  | <u>Synchronous mode</u> :<br>1 = Data is clocked on rising edge of the clock<br>0 = Data is clocked on falling edge of the clock                                                                  |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

| bit 3            | BRG16: 16-1                                                                                                                                                                                       | oit Baud Rate                                                            | Generator bit                                       |                  |                 |                  |               |  |  |  |  |  |

|                  | <ul> <li>1 = 16-bit Baud Rate Generator is used</li> <li>0 = 8-bit Baud Rate Generator is used</li> </ul>                                                                                         |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

| bit 2            | Unimpleme                                                                                                                                                                                         | nted: Read as                                                            | '0'                                                 |                  |                 |                  |               |  |  |  |  |  |

| bit 1            | WUE: Wake-up Enable bit                                                                                                                                                                           |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

|                  | Asynchronous mode:                                                                                                                                                                                |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

|                  | will autor                                                                                                                                                                                        | natically clear<br>is operating n                                        | after RCIF is se                                    |                  | will be receive | d, byte RCIF wil | l be set. WUI |  |  |  |  |  |

| bit 0            | ABDEN: Auto-Baud Detect Enable bit                                                                                                                                                                |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

|                  | Asynchronous mode:                                                                                                                                                                                |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

|                  | <ul> <li>1 = Auto-Baud Detect mode is enabled (clears when auto-baud is complete)</li> <li>0 = Auto-Baud Detect mode is disabled</li> <li><u>Synchronous mode</u>:</li> <li>Don't care</li> </ul> |                                                                          |                                                     |                  |                 |                  |               |  |  |  |  |  |

# REGISTER 31-3: BAUD1CON: BAUD RATE CONTROL REGISTER

# PIC16(L)F1717/8/9

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

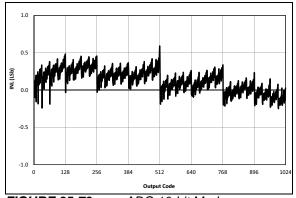

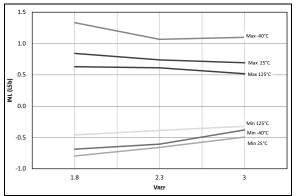

**FIGURE 35-79:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S,  $25^{\circ}$ C.

**FIGURE 35-80:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $4 \mu$ S,  $25^{\circ}$ C.

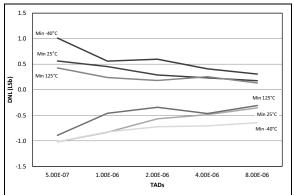

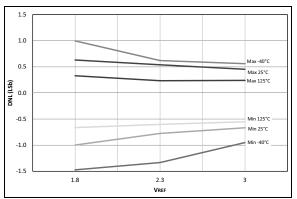

FIGURE 35-81: ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

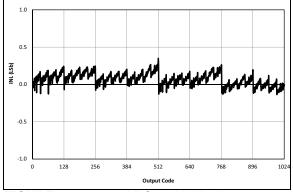

**FIGURE 35-82:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, VREF = 3.0V.

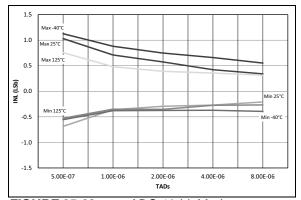

**FIGURE 35-83:** ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V, TAD =  $1 \mu$ S.

**FIGURE 35-84:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S.

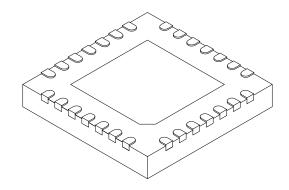

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units    |          |          |      |  |  |

|-------------------------|----------|----------|----------|------|--|--|

| Dimension               | n Limits | MIN      | NOM      | MAX  |  |  |

| Number of Pins          | Ν        |          | 28       |      |  |  |

| Pitch                   | е        |          | 0.65 BSC |      |  |  |

| Overall Height          | А        | 0.80     | 0.90     | 1.00 |  |  |

| Standoff                | A1       | 0.00     | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3       | 0.20 REF |          |      |  |  |

| Overall Width           | Е        | 6.00 BSC |          |      |  |  |

| Exposed Pad Width       | E2       | 3.65     | 3.70     | 4.70 |  |  |

| Overall Length          | D        | 6.00 BSC |          |      |  |  |

| Exposed Pad Length      | D2       | 3.65     | 3.70     | 4.70 |  |  |

| Terminal Width          | b        | 0.23     | 0.30     | 0.35 |  |  |

| Terminal Length         | L        | 0.30     | 0.40     | 0.50 |  |  |