Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1717-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

# 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1717/8/9 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

## 3.2 High-Endurance Flash

This device has a 128-byte section of high-endurance program Flash memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash **Program Memory Overview**" for more information on writing data to PFM. See Section 3.2.1.2 "Indirect Read with FSR" for more information about using the FSR registers to read byte data stored in PFM.

| Device          | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |  |

|-----------------|---------------------------------|--------------------------------|-------------------------------------------------------------|--|

| PIC16(L)F1717   | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |  |

| PIC16(L)F1718/9 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |  |

**Note 1:** High-endurance Flash applies to the low byte of each address in the range.

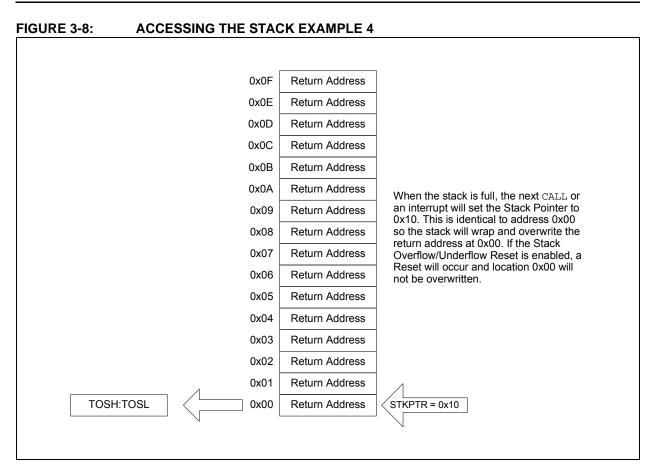

# 3.6.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### 3.7 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

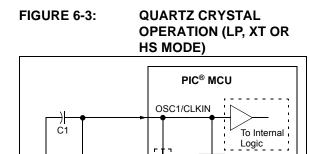

Quartz

Crystal

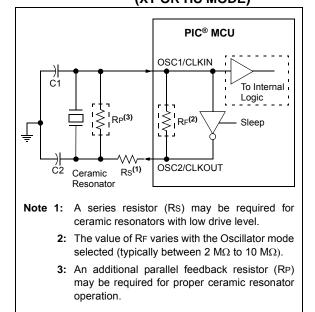

# Note 1: A series resistor (Rs) may be required for quartz crystals with low drive level. 2: The value of RF varies with the Oscillator mode selected (typically between 2 MΩ to 10 MΩ).

RF<sup>(2)</sup>

Sleep

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

## FIGURE 6-4:

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

# 6.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended, unless either FSCM or Two-Speed Start-Up are enabled. In this case, code will continue to execute at the selected INTOSC frequency while the OST is counting. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 6.4 "Two-Speed Clock Start-up Mode"**).

# 6.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Secondary Oscillator and RC).

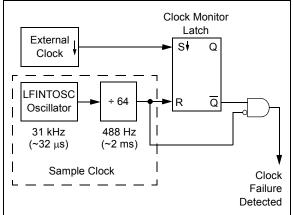

FIGURE 6-9: FSCM BLOCK DIAGRAM

#### 6.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 6-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 6.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 6.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

#### 6.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

| Note: | Due to the wide range of oscillator start-up<br>times, the Fail-Safe circuit is not active<br>during oscillator start-up (i.e., after exiting                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Reset or Sleep). After an appropriate<br>amount of time, the user should check the<br>Status bits in the OSCSTAT register to<br>verify the oscillator start-up and that the<br>system clock switchover has successfully<br>completed. |

# 11.0 I/O PORTS

Each port has six standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- INLVLx (input level control)

- ODCONx registers (open-drain)

- SLRCONx registers (slew rate)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

TABLE 11-1: PORT AVAILABILITY PER DEVICE

| Device        | PORTA | PORTB | PORTC | PORTD | PORTE |

|---------------|-------|-------|-------|-------|-------|

| PIC16(L)F1717 | ٠     | ٠     | ٠     | ٠     | •     |

| PIC16(L)F1718 | •     | ٠     | ٠     |       | •     |

| PIC16(L)F1719 | •     | •     | ٠     | ٠     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

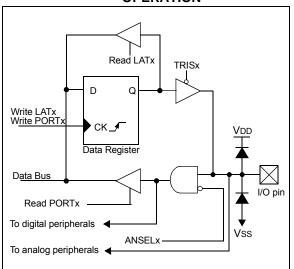

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

#### FIGURE 11-1: GENERIC I/O PORT OPERATION

# 11.1 PORTA Registers

# 11.1.1 DATA REGISTER

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 11-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 11-1 shows how to initialize PORTA.

Reading the PORTA register (Register 11-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

# 11.1.2 DIRECTION CONTROL

The TRISA register (Register 11-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 11.1.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

# 11.3 PORTB Registers

#### 11.3.1 DATA REGISTER

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

## 11.3.2 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 11.3.3 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.3.4 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

## 11.3.5 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

Note: Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 11.3.6 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 11.3.7 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information. Analog input functions, such as ADC and op amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

# 11.4 Register Definitions: PORTB

#### REGISTER 11-9: PORTB: PORTB REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| RB7                                     | RB6     | RB5               | RB4     | RB3                                                   | RB2     | RB1     | RB0     |  |

| bit 7                                   |         |                   |         |                                                       |         |         | bit 0   |  |

|                                         |         |                   |         |                                                       |         |         |         |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |

| R = Readable bit W = Writable bit       |         |                   | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

## REGISTER 11-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 11-11: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

| R/W-0/0         | R/W-0/0                           | R/W-0/0         | R/W-0/0 | R/W-0/0                                              | R/W-0/0 | R/W-0/0 | R/W-0/0     |  |

|-----------------|-----------------------------------|-----------------|---------|------------------------------------------------------|---------|---------|-------------|--|

| ODD7            | ODD6                              | ODD5            | ODD4    | ODD3                                                 | ODD2    | ODD1    | ODD0        |  |

| bit 7 bit 0     |                                   |                 |         |                                                      |         |         |             |  |

|                 |                                   |                 |         |                                                      |         |         |             |  |

| Legend:         |                                   |                 |         |                                                      |         |         |             |  |

| R = Readable    | R = Readable bit W = Writable bit |                 |         | U = Unimplemented bit, read as '0'                   |         |         |             |  |

| u = Bit is unch | anged                             | x = Bit is unkr | iown    | -n/n = Value at POR and BOR/Value at all other Reset |         |         | ther Resets |  |

#### REGISTER 11-30: ODCOND: PORTD OPEN-DRAIN CONTROL REGISTER

bit 7-0 **ODD<7:0>:** PORTD Open-Drain Enable bits For RD<7:0> pins, respectively 1 = Port pin operates as open-drain drive (sink current only) 0 = Port pin operates as standard push-pull drive (source and sink current)

'0' = Bit is cleared

#### REGISTER 11-31: SLRCOND: PORTD SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRD<7:0>: PORTD Slew Rate Enable bits

For RD<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### REGISTER 11-32: INLVLD: PORTD INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 |

| bit 7   |         |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

1' = Bit is set

INLVLD<7:0>: PORTD Input Level Select bits

For RD<7:0> pins, respectively

1 = Port pin digital input operates with ST thresholds

0 = Port pin digital input operates with TTL thresholds

# REGISTER 11-35: LATE: PORTE DATA LATCH REGISTER<sup>(1)</sup>

| — | — | _ | — | LATE2 | LATE1 | LATE0 |

|---|---|---|---|-------|-------|-------|

|   |   |   |   |       |       | bit 0 |

|   |   |   |   |       |       |       |

|   |   |   |   |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits

Note 1: PIC16(L)F1717/9 only.

#### REGISTER 11-36: ANSELE: PORTE ANALOG SELECT REGISTER<sup>(2)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | _   | ANSE2   | ANSE1   | ANSE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively<sup>(1)</sup> D =Digital I/O. Pin is assigned to port or digital special function.

1 =Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

2: PIC16(L)F1717/9 only.

| Name                 | Bit 7        | Bit 6  | Bit 5  | Bit 4   | Bit 3          | Bit 2      | Bit 1    | Bit 0  | Register<br>on Page |

|----------------------|--------------|--------|--------|---------|----------------|------------|----------|--------|---------------------|

| INTCON               | GIE          | PEIE   | TMR0IE | INTE    | IOCIE          | TMR0IF     | INTF     | IOCIF  | 90                  |

| NCO1ACCU             |              | _      | _      |         |                | NCO1AC     | C<19:16> |        | 239                 |

| NCO1ACCH             |              |        |        | NCO1AC  | C<15:8>        |            |          |        | 239                 |

| NCO1ACCL             | NC01A        |        |        | CC<7:0> |                |            |          | 238    |                     |

| NCO1CLK              | N1PWS<2:0> — |        |        | _       | _              | N1CK       | S<1:0>   | 238    |                     |

| NCO1CON              | N1EN         | _      | N1OUT  | N1POL   | —              | —          | —        | N1PFM  | 237                 |

| NCO1INCU             |              |        |        |         | NCO1INC<19:16> |            |          |        | 240                 |

| NCO1INCH             |              |        |        | NCO1IN  | IC<15:8>       |            |          |        | 240                 |

| NCO1INCL             |              |        |        | NCO1IN  | NC<7:0>        |            |          |        | 239                 |

| PIE3                 | _            | NCOIE  | COGIE  | ZCDIE   | CLC4IE         | CLC3IE     | CLC2IE   | CLC1IE | 93                  |

| PIR3                 | —            | NCOIF  | COGIF  | ZCDIF   | CLC4IF         | CLC3IF     | CLC2IF   | CLC1IF | 96                  |

| TRISA                | TRISA7       | TRISA6 | TRISA5 | TRISA4  | TRISA3         | TRISA2     | TRISA1   | TRISA0 | 124                 |

| TRISC                | TRISC7       | TRISC6 | TRISC5 | TRISC4  | TRISC3         | TRISC2     | TRISC1   | TRISC0 | 135                 |

| TRISD <sup>(1)</sup> | TRISD7       | TRISD6 | TRISD5 | TRISD4  | TRISD3         | TRISD2     | TRISD1   | TRISD0 | 140                 |

| RxyPPS               |              |        | _      |         | F              | RxyPPS<4:0 | >        |        | 153                 |

TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCOX

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for NCOx module.

Note 1: PIC16(L)F1717/9 only.

# 21.2 ADC Operation

#### 21.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 21.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

## 21.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 21.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

#### 21.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 21.2.5 AUTO-CONVERSION TRIGGER

The auto-conversion trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The auto-conversion trigger source is selected with the TRIGSEL<3:0> bits of the ADCON2 register.

Using the auto-conversion trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

#### See Table 21-2 for auto-conversion sources.

#### TABLE 21-2: AUTO-CONVERSION SOURCES

| -           |

|-------------|

| Signal Name |

| —           |

| —           |

| T0_overflow |

| T1_overflow |

| T2_match    |

| T4_match    |

| T6_match    |

| sync_C1OUT  |

| sync_C2OUT  |

| LC1_out     |

| LC2_out     |

| LC3_out     |

| LC4_out     |

|             |

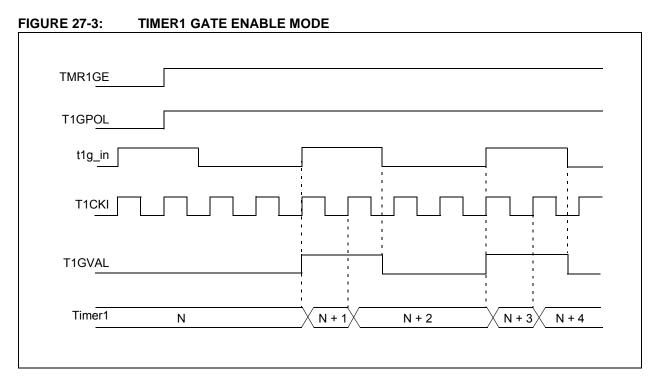

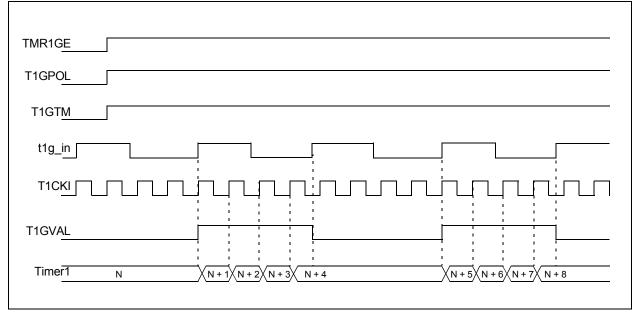

# FIGURE 27-4: TIMER1 GATE TOGGLE MODE

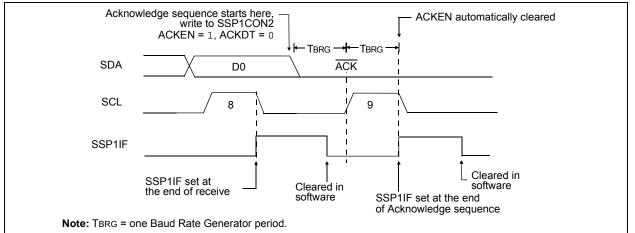

#### 30.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSP1CON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 30-30).

#### 30.6.8.1 WCOL Status Flag

If the user writes the SSP1BUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

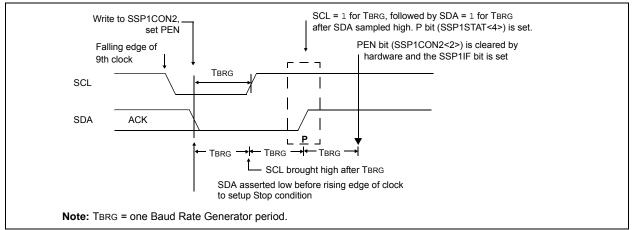

#### 30.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSP1CON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSP1STAT register is set. A TBRG later, the PEN bit is cleared and the SSP1IF bit is set (Figure 30-31).

## 30.6.9.1 WCOL Status Flag

If the user writes the SSP1BUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### FIGURE 30-30: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 30-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

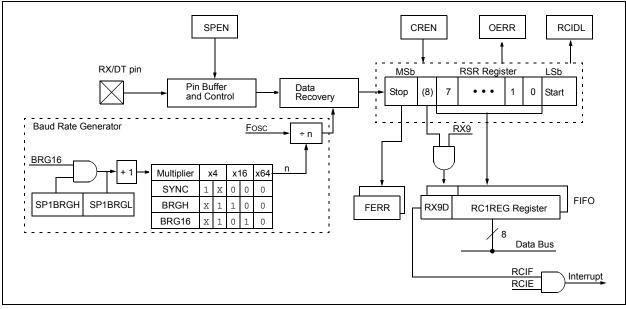

## FIGURE 31-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TX1STA)

- Receive Status and Control (RC1STA)

- Baud Rate Control (BAUD1CON)

These registers are detailed in Register 31-1, Register 31-2 and Register 31-3, respectively.

The RX and CK input pins are selected with the RXPPS and CKPPS registers, respectively. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

#### 31.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RC1STA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RC1REG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RC1STA register which resets the EUSART. Clearing the CREN bit of the RC1STA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | FIFO have framing errors, repeated reads |  |  |  |  |  |

|       | of the RC1REG will not clear the FERR    |  |  |  |  |  |

|       | bit.                                     |  |  |  |  |  |

#### 31.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RC1STA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RC1STA register or by resetting the EUSART by clearing the SPEN bit of the RC1STA register.

#### 31.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RC1STA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RC1STA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RC1REG.

#### 31.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RC1STA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

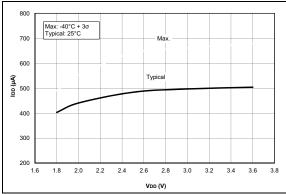

**FIGURE 35-49:** IPD, Comparator, NP Mode (CxSP = 1), PIC16LF1717/8/9 Only.

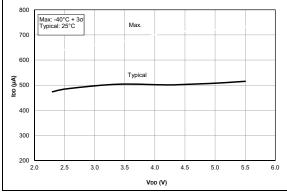

**FIGURE 35-50:** IPD, Comparator, NP Mode (CxSP = 1), PIC16F1717/8/9 Only.

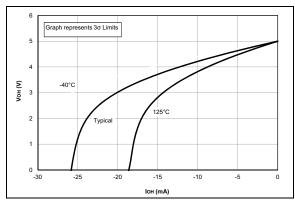

FIGURE 35-51:

VOH vs. IOH Over

Temperature, VDD = 5.0V, PIC16F1717/8/9 Only.

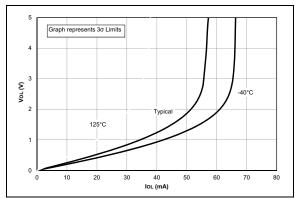

FIGURE 35-52: Vol vs. Iol Over Temperature, VDD = 5.0V, PIC16F1717/8/9 Only.

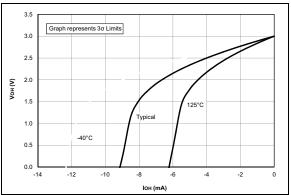

**FIGURE 35-53:** VOH vs. IOH Over Temperature, VDD = 3.0V.

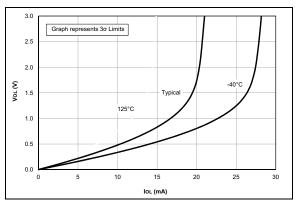

FIGURE 35-54: VOL vs. IOL Over Temperature, VDD = 3.0V.

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

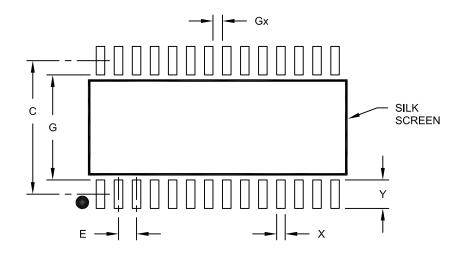

# RECOMMENDED LAND PATTERN

| Units                    |    | MILLIMETERS |      |      |

|--------------------------|----|-------------|------|------|

| Dimension Limits         |    | MIN         | NOM  | MAX  |

| Contact Pitch            | E  | 1.27 BSC    |      |      |

| Contact Pad Spacing      | С  |             | 9.40 |      |

| Contact Pad Width (X28)  | X  |             |      | 0.60 |

| Contact Pad Length (X28) | Y  |             |      | 2.00 |

| Distance Between Pads    | Gx | 0.67        |      |      |

| Distance Between Pads    | G  | 7.40        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

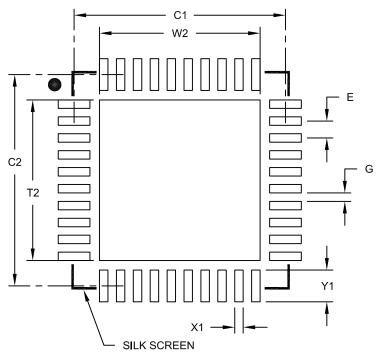

# 40-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 5x5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |  |

|----------------------------|----|-------------|------|------|--|

| Dimension Limits           |    | MIN         | NOM  | MAX  |  |

| Contact Pitch              | E  | 0.40 BSC    |      |      |  |

| Optional Center Pad Width  | W2 |             |      | 3.80 |  |

| Optional Center Pad Length | T2 |             |      | 3.80 |  |

| Contact Pad Spacing        | C1 |             | 5.00 |      |  |

| Contact Pad Spacing        | C2 |             | 5.00 |      |  |

| Contact Pad Width (X40)    | X1 |             |      | 0.20 |  |

| Contact Pad Length (X40)   | Y1 |             |      | 0.75 |  |

| Distance Between Pads      | G  | 0.20        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2156B