# Microchip Technology - PIC16F1718-I/SO Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

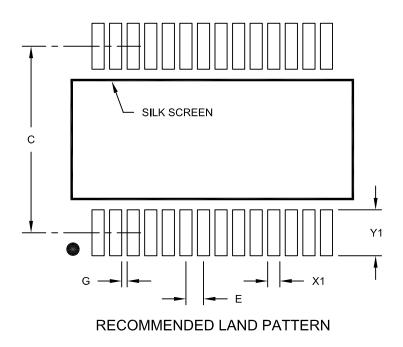

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1718-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-6: PIC16(L)F1718/9 MEMORY MAP, BANK 8-23

|               | BANK 8                        |               | BANK 9                        |              | BANK 10                       |               | BANK 11                       |              | BANK 12                       |              | BANK 13                       |              | BANK 14                       |               | BANK 15                       |

|---------------|-------------------------------|---------------|-------------------------------|--------------|-------------------------------|---------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|---------------|-------------------------------|

| 400h          |                               | 480h          |                               | 500h         |                               | 580h          |                               | 600h         |                               | 680h         |                               | 700h         |                               | 780h          |                               |

|               | Core Registers<br>(Table 3-2) |               | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |               | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |              | Core Registers<br>(Table 3-2) |               | Core Registers<br>(Table 3-2) |

| 40Bh          |                               | 48Bh          |                               | 50Bh         |                               | 58Bh          |                               | 60Bh         |                               | 68Bh         |                               | 70Bh         |                               | 78Bh          |                               |

| 40Ch          | —                             | 48Ch          | —                             | 50Ch         | _                             | 58Ch          | —                             | 60Ch         |                               | 68Ch         | —                             | 70Ch         |                               | 78Ch          | _                             |

| 40Dh          | —                             | 48Dh          | —                             | 50Dh         | —                             | 58Dh          | —                             | 60Dh         |                               | 68Dh         | —                             | 70Dh         |                               | 78Dh          | —                             |

| 40Eh          | —                             | 48Eh          | _                             | 50Eh         | —                             | 58Eh          | _                             | 60Eh         | _                             | 68Eh         |                               | 70Eh         | _                             | 78Eh          | _                             |

| 40Fh          | —                             | 48Fh          | _                             | 50Fh         | —                             | 58Fh          | _                             | 60Fh         | _                             | 68Fh         | —                             | 70Fh         | _                             | 78Fh          | _                             |

| 410h          | —                             | 490h          | _                             | 510h         |                               | 590h          | —                             | 610h         | _                             | 690h         | -                             | 710h         | _                             | 790h          | _                             |

| 411h          | _                             | 491h          |                               | 511h         | OPA1CON                       | 591h          |                               | 611h         |                               | 691h         | COG1PHR<br>COG1PHF            | 711h         |                               | 791h          |                               |

| 412h          | —                             | 492h          | _                             | 512h         | _                             | 592h          |                               | 612h         |                               | 692h         |                               | 712h         |                               | 792h          | _                             |

| 413h          | _                             | 493h          |                               | 513h         | _                             | 593h          | _                             | 613h         |                               | 693h         | COG1BLKR<br>COG1BLKF          | 713h         |                               | 793h          |                               |

| 414h          | <br>TMR4                      | 494h          |                               | 514h         | <br>OPA2CON                   | 594h          |                               | 614h         |                               | 694h         | COGIDER                       | 714h         |                               | 794h<br>795h  |                               |

| 415h          |                               | 495h          |                               | 515h         |                               | 595h          |                               | 615h         |                               | 695h         | COG1DBR                       | 715h         |                               |               |                               |

| 416h<br>417h  | PR4<br>T4CON                  | 496h<br>497h  |                               | 516h<br>517h | _                             | 596h<br>597h  | _                             | 616h<br>617h | PWM3DCL                       | 696h<br>697h | COG1CON0                      | 716h<br>717h |                               | 796h<br>797h  | _                             |

| 41711<br>418h |                               | 49711<br>498h | NC01ACCL                      | 517n<br>518h |                               | 597n<br>598h  |                               | 618h         | PWM3DCL<br>PWM3DCH            | 698h         | COG1CON0                      | 718h         |                               | 797n<br>798h  |                               |

| 41011<br>419h |                               | 49011<br>499h | NCOTACCE                      | 510h         |                               | 590h          |                               | 619h         | PWM3DCH<br>PWM3CON            | 699h         | COG1RIS                       | 719h         |                               | 7901<br>799h  |                               |

| 41911<br>41Ah |                               | 49911<br>49Ah | NCO1ACCU                      | 519h         |                               | 59911<br>59Ah |                               | 61Ah         | PWM4DCL                       | 69Ah         | COG1RSIM                      | 71Ah         |                               | 79911<br>79Ah |                               |

| 41An          |                               | 49An<br>49Bh  | NCOTINCL                      | 51An<br>51Bh |                               | 59An<br>59Bh  |                               | 61Bh         | PWM4DCL<br>PWM4DCH            | 69Bh         | COG1FIS                       | 71Bh         |                               | 79An<br>79Bh  |                               |

| 41Ch          | <br>TMR6                      | 49Ch          | NCO1INCH                      | 51Ch         |                               | 59Ch          |                               | 61Ch         | PWM4CON                       | 69Ch         | COG1FSIM                      | 71Ch         |                               | 79Ch          |                               |

| 41Dh          | PR6                           | 49Dh          | NCO1INCU                      | 51Dh         |                               | 59Dh          |                               | 61Dh         |                               | 69Dh         | COG1ASD0                      | 71Dh         |                               | 79Dh          |                               |

| 41Eh          | TECON                         | 49Eh          | NCO1CON                       | 51Eh         |                               | 59Eh          |                               | 61Eh         |                               | 69Eh         | COG1ASD1                      | 71Eh         |                               | 79Eh          |                               |

| 41Fh          | _                             | 49Fh          | NCO1CLK                       | 51Fh         |                               | 59Fh          |                               | 61Fh         |                               | 69Fh         | COG1STR                       | 71Fh         |                               | 79Eh          |                               |

| 420h          |                               | 4A0h          | NOOTOEN                       | 520h         |                               | 5A0h          |                               | 620h         |                               | 6A0h         | 00010111                      | 720h         |                               | 7A0h          |                               |

| -             | General                       | -             | General                       |              | General                       |               | General                       |              | General                       |              | General                       | _            | General                       | -             | General                       |

|               | Purpose                       |               | Purpose                       |              | Purpose                       |               | Purpose                       |              | Purpose                       |              | Purpose                       |              | Purpose                       |               | Purpose                       |

|               | Register                      |               | Register                      |              | Register                      |               | Register                      |              | Register                      |              | Register                      |              | Register                      |               | Register                      |

|               | 80 Bytes                      |               | 80 Bytes                      |              | 80 Bytes                      |               | 80 Bytes                      |              | 80 Bytes                      |              | 80 Bytes                      |              | 80 Bytes                      |               | 80 Bytes                      |

| 46Fh          |                               | 4EFh          |                               | 56Fh         |                               | 5EFh          |                               | 66Fh         |                               | 6EFh         |                               | 76Fh         |                               | 7EFh          |                               |

| 470h          |                               | 4F0h          |                               | 570h         |                               | 5F0h          |                               | 670h         |                               | 6F0h         |                               | 770h         |                               | 7F0h          |                               |

|               | Accesses                      |               | Accesses                      |              | Accesses                      |               | Accesses                      |              | Accesses                      |              | Accesses                      |              | Accesses                      |               | Accesses                      |

|               | 70h – 7Fh                     |               | 70h – 7Fh                     |              | 70h – 7Fh                     |               | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |               | 70h – 7Fh                     |

| 47Fh          |                               | 4FFh          |                               | 57Fh         |                               | 5FFh          |                               | 67Fh         |                               | 6FFh         |                               | 77Fh         |                               | 7FFh          |                               |

|               | BANK 16                       |               | BANK 17                       |              | BANK 18                       |               | BANK 19                       |              | BANK 20                       |              | BANK 21                       |              | BANK 22                       |               | BANK 23                       |

| 800h          |                               | 880h          |                               | 900h         |                               | 980h          |                               | A00h         |                               | A80h         |                               | B00h         |                               | B80h          |                               |

|               | Core Registers                |               | Core Registers                |              | Core Registers                |               | Core Registers                |              | Core Registers                |              | Core Registers                |              | Core Registers                |               | Core Registers                |

|               | (Table 3-2)                   |               | (Table 3-2)                   |              | (Table 3-2)                   |               | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |               | (Table 3-2)                   |

| 80Bh          |                               | 88Bh          |                               | 90Bh         |                               | 98Bh          |                               | A0Bh         |                               | A8Bh         |                               | B0Bh         |                               | B8Bh          |                               |

| 80Ch          | General                       | 88Ch          | General                       | 90Ch         | General                       | 98Ch          | General                       | A0Ch         | General                       | A8Ch         | General                       | B0Ch         | General                       | B8Ch          | General                       |

|               | Purpose                       | 50.011        | Purpose                       | 20011        | Purpose                       | 20011         | Purpose                       |              | Purpose                       | 1.0011       | Purpose                       | 20011        | Purpose                       | 20011         | Purpose                       |

|               | Register                      |               | Register                      |              | Register                      |               | Register                      |              | Register                      |              | Register                      |              | Register                      |               | Register                      |

|               | 80 Bytes                      | 000           | 80 Bytes                      |              | 80 Bytes                      | 9EFh          | 80 Bytes                      |              | 80 Bytes                      | AEFh         | 80 Bytes                      | DOC          | 80 Bytes                      | BEFh          | 80 Bytes                      |

| 86Fh          | <b>,</b>                      | 8EFh          | <b>,</b>                      | 96Fh         | <b>,</b>                      | -             | <b>,</b>                      | A6Fh         | ,                             |              | ,                             | B6Fh         | ,                             |               | <b>,</b>                      |

| 870h          | A                             | 8F0h          | A                             | 970h         | A                             | 9F0h          | A                             | A70h         | A                             | AF0h         | A                             | B70h         | A                             | BF0h          | A                             |

|               | Accesses<br>70h – 7Fh         |               | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |               | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |               | Accesses<br>70h – 7Fh         |

|               | /011 - /FII                   |               | /011 - /FII                   |              | /011 - /FII                   |               | 7011 - 7FII                   |              | -                             | :            | -                             |              | -                             |               | / UII - / FII                 |

| 87Fh          |                               | 8FFh          |                               | 97Fh         |                               | 9FFh          |                               | A7Fh         |                               | AFFh         |                               | B7Fh         |                               | BFFh          |                               |

Legend: = Unimplemented data memory locations, read as '0'.

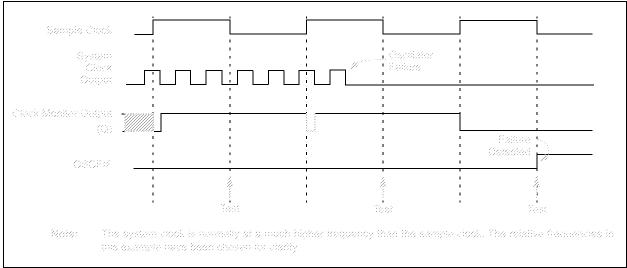

# 6.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

#### 6.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay                                |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| Sleep            | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (Twarm) <sup>(2)</sup> |

| Sleep/POR        | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                                        |

| LFINTOSC         | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each                                 |

| Sleep/POR        | Secondary Oscillator<br>LP, XT, HS <sup>(1)</sup>                             | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST)                         |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                                  |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                                 |

| Any clock source | Secondary Oscillator                                                          | 32 kHz                                          | 1024 Clock Cycles (OST)                         |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)                                  |

#### TABLE 6-1: OSCILLATOR SWITCHING DELAYS

Note 1: PLL inactive.

2: See Section 34.0 "Electrical Specifications".

# PIC16(L)F1717/8/9

# 8.2 Low-Power Sleep Mode

The PIC16F1717/8/9 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. The PIC16F1717/8/9 allows the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

# 8.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

### 8.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use only with the following peripherals:

- Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- External interrupt pin/Interrupt-on-Change pins

- Timer1 (with external clock source < 100 kHz)

- Note: The PIC16LF1717/8/9 does not have a configurable Low-Power Sleep mode. PIC16LF1717/8/9 is an unregulated device and is always in the lowest power state when in Sleep, with no wake-up time penalty. This device has a lower maximum VDD and I/O voltage than the PIC16F1717/8/9. See Section 34.0 "Electrical Specifications" for more information.

| R/W-x/u          | R/W-x/u                               | R/W-x/u           | R/W-x/u                                               | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------------|---------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| LATA7            | LATA6                                 | LATA5             | LATA4                                                 | LATA3                              | LATA2   | LATA1   | LATA0   |  |

| bit 7            |                                       |                   |                                                       |                                    |         |         | bit 0   |  |

|                  |                                       |                   |                                                       |                                    |         |         |         |  |

| Legend:          |                                       |                   |                                                       |                                    |         |         |         |  |

| R = Readable I   | R = Readable bit W = Writable bit     |                   |                                                       | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is uncha | = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set |                                       | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

#### **REGISTER 11-3: LATA: PORTA DATA LATCH REGISTER**

bit 7-0 LATA<7:0>: RA<7:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on Pins RA<5:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

# 11.10 Register Definitions: PORTE

| U-0              | U-0                                     | U-0               | U-0                                                   | R/W-x/u                            | R/W-x/u            | R/W-x/u            | R/W-x/u            |  |

|------------------|-----------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|--------------------|--------------------|--------------------|--|

| —                | —                                       | —                 | -                                                     | RE3                                | RE2 <sup>(2)</sup> | RE1 <sup>(2)</sup> | RE0 <sup>(2)</sup> |  |

| bit 7            |                                         |                   |                                                       |                                    |                    |                    | bit 0              |  |

|                  |                                         |                   |                                                       |                                    |                    |                    |                    |  |

| Legend:          |                                         |                   |                                                       |                                    |                    |                    |                    |  |

| R = Readable b   | R = Readable bit W = Writable bit       |                   |                                                       | U = Unimplemented bit, read as '0' |                    |                    |                    |  |

| u = Bit is uncha | I = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |                    |                    |                    |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared                                                  |                                    |                    |                    |                    |  |

#### **REGISTER 11-33: PORTE: PORTE REGISTER**

| bit 7-4 | Unimplemented: Read as '0'                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | <b>RE&lt;3:0&gt;</b> : PORTE General Purpose I/O Pin bits <sup>(1)</sup><br>1 = Port pin is $\geq$ VIH<br>0 = Port pin is $\leq$ VIL |

- **Note 1:** Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of actual I/O pin values.

- 2: PIC16(L)F1717/9 only.

#### REGISTER 11-34: TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | R-1    | R/W-1/1               | R/W-1/1               | R/W-1/1               |

|-------|-----|-----|-----|--------|-----------------------|-----------------------|-----------------------|

| —     | —   | —   | —   | TRISE3 | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> |

| bit 7 |     |     |     |        |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 3-0 **TRISE<3:0>:** PORTE Tri-State Control bits 1 = PORTE pin configured as an input (tri-stated) 0 = PORTE pin configured as an output

Note 1: PIC16(L)F1717/9 only.

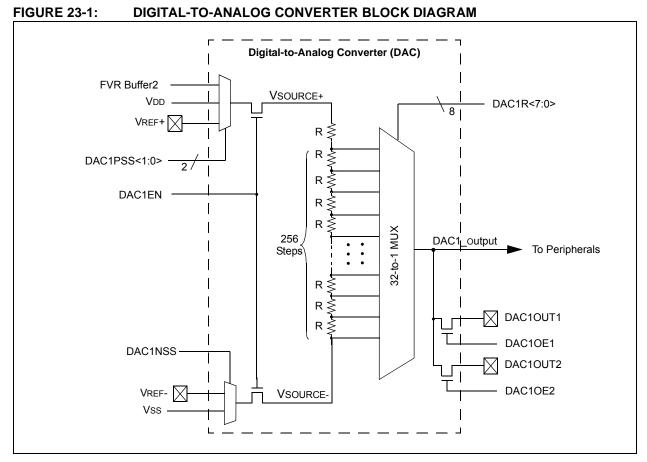

#### 16.6 Comparator Positive Input Selection

Configuring the CxPCH<2:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- CxIN+ analog pin

- DAC output

- FVR (Fixed Voltage Reference)

- Vss (Ground)

See **Section 14.0** "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 23.0 "8-Bit Digital-to-Analog Converter (DAC1) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

# 16.7 Comparator Negative Input Selection

The CxNCH<2:0> bits of the CMxCON1 register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- CxIN- pin

- FVR (Fixed Voltage Reference)

- Analog Ground

Some inverting input selections share a pin with the operational amplifier output function. Enabling both functions at the same time will direct the operational amplifier output to the comparator inverting input.

Note: To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

# 16.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 34-18: Comparator Specifications for more details.

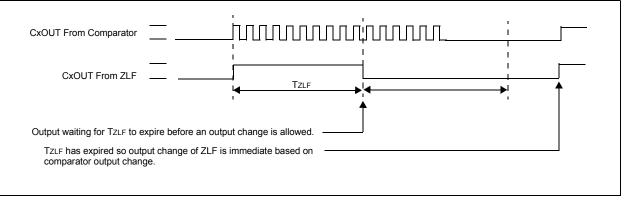

# 16.9 Zero Latency Filter

In high-speed operation, and under proper circuit conditions, it is possible for the comparator output to oscillate. This oscillation can have adverse effects on the hardware and software relying on this signal. Therefore, a digital filter has been added to the comparator output to suppress the comparator output oscillation. Once the comparator output changes, the output is prevented from reversing the change for a nominal time of 20 ns. This allows the comparator output to stabilize without affecting other dependent devices. Refer to Figure 16-3.

# FIGURE 16-3: COMPARATOR ZERO LATENCY FILTER OPERATION

#### 18.8 Auto-shutdown Control

Auto-shutdown is a method to immediately override the COG output levels with specific overrides that allow for safe shutdown of the circuit.

The shutdown state can be either cleared automatically or held until cleared by software. In either case, the shutdown overrides remain in effect until the first rising event after the shutdown is cleared.

#### 18.8.1 SHUTDOWN

The shutdown state can be entered by either of the following two mechanisms:

- · Software generated

- External Input

#### 18.8.1.1 Software Generated Shutdown

Setting the GxASE bit of the COGxASD0 register (Register 18-7) will force the COG into the shutdown state.

When auto-restart is disabled, the shutdown state will persist until the first rising event after the GxASE bit is cleared by software.

When auto-restart is enabled, the GxASE bit will clear automatically and resume operation on the first rising event after the shutdown input clears. See Figure 18-15 and **Section 18.8.3.2** "**Auto-Restart**".

#### 18.8.1.2 External Shutdown Source

External shutdown inputs provide the fastest way to safely suspend COG operation in the event of a Fault condition. When any of the selected shutdown inputs goes true, the output drive latches are reset and the COG outputs immediately go to the selected override levels without software delay.

Any combination of the input sources can be selected to cause a shutdown condition. Shutdown occurs when the selected source is low. Shutdown input sources include:

- Any input pin selected with the COGxPPS control

- C2OUT

- C10UT

- CLC2OUT

Shutdown inputs are selected independently with bits of the COGxASD1 register (Register 18-8).

| Note: | Shutdown inputs are level sensitive, n<br>edge sensitive. The shutdown state cann<br>be cleared as long as the shutdown inp |                       |     |     |    |       |       |

|-------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|----|-------|-------|

|       |                                                                                                                             | persists,<br>hutdown, | exc | ept | by | disab | oling |

#### 18.8.2 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown is active, are controlled by the GxASDAC<1:0> and GxASDBC<1:0> bits of the COGxASD0 register (Register 18-7). GxASDAC<1:0> controls the COGxA and COGxC override levels and GxASDBC<1:0> controls the COGxB and COGxD override levels. There are four override options for each output pair:

- · Forced low

- · Forced high

- Tri-state

- PWM inactive state (same state as that caused by a falling event)

Note: The polarity control does not apply to the forced low and high override levels but does apply to the PWM inactive state.

# 18.8.3 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the GxARSEN bit of the COGxASD0 register. Waveforms of a software controlled automatic restart are shown in Figure 18-15.

#### 18.8.3.1 Software Controlled Restart

When the GxARSEN bit of the COGxASD0 register is cleared, software must clear the GxASE bit to restart COG operation after an auto-shutdown event.

The COG will resume operation on the first rising event after the GxASE bit is cleared. Clearing the shutdown state requires all selected shutdown inputs to be false, otherwise, the GxASE bit will remain set.

#### 18.8.3.2 Auto-Restart

When the GxARSEN bit of the COGxASD0 register is set, the COG will restart from the auto-shutdown state automatically.

The GxASE bit will clear automatically and the COG will resume operation on the first rising event after all selected shutdown inputs go false.

| R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0/0           | R/W-0/0 | R/W-0/0         | R/W-0/0           | U-0               | U-0          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|-----------------|-------------------|-------------------|--------------|

| GxASE                                                                                                                                                                                                                                                                                                                                                                                                                           | GxARSEN                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GxASDBD<1:0>      |         | GxASDAC<1:0>    |                   | —                 |              |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |         |                 |                   |                   | bit 0        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |         |                 |                   |                   |              |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |         |                 |                   |                   |              |

| R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                    | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                             | W = Writable      | bit     | U = Unimpleme   | ented bit, read a | as 'O'            |              |

| u = Bit is unch                                                                                                                                                                                                                                                                                                                                                                                                                 | nanged                                                                                                                                                                                                                                                                                                                                                                                                                                                            | x = Bit is unkr   | iown    | -n/n = Value at | POR and BOR       | /Value at all oth | ner Resets   |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '0' = Bit is clea | ared    | q = Value depe  | ends on conditio  | n                 |              |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 7 <b>GxASE:</b> Auto-Shutdown Event Status bit<br>1 = COG is in the shutdown state<br>0 = COG is either not in the shutdown state or will exit the shutdown state on the next rising event                                                                                                                                                                                                                                                                    |                   |         |                 |                   |                   |              |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                           | GxARSEN: Auto-Restart Enable bit<br>1 = Auto-restart is enabled<br>0 = Auto-restart is disabled                                                                                                                                                                                                                                                                                                                                                                   |                   |         |                 |                   |                   |              |

| bit 5-4                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>bit 5-4 GxASDBD&lt;1:0&gt;: COGxB and COGxD Auto-shutdown Override Level Select bits</li> <li>11 = A logic '1' is placed on COGxB and COGxD when shutdown is active</li> <li>10 = A logic '0' is placed on COGxB and COGxD when shutdown is active</li> <li>01 = COGxB and COGxD are tri-stated when shutdown is active</li> <li>00 = The inactive state of the pin, including polarity, is placed on COGxB and COGxD when shutdown is active</li> </ul> |                   |         |                 |                   |                   |              |

| bit 3-2 <b>GxASDAC&lt;1:0&gt;:</b> COGxA and COGxC Auto-shutdown Override Level Select bits<br>11 = A logic '1' is placed on COGxA and COGxC when shutdown is active<br>10 = A logic '0' is placed on COGxA and COGxC when shutdown is active<br>01 = COGxA and COGxC are tri-stated when shutdown is active<br>00 = The inactive state of the pin, including polarity, is placed on COGxA and COGxC when shutdown<br>is active |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |         |                 |                   |                   | hen shutdown |

| bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                         | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ted: Read as '    | )'      |                 |                   |                   |              |

# REGISTER 18-7: COGxASD0: COG AUTO-SHUTDOWN CONTROL REGISTER 0

| R/W-x/u                 | R/W-x/u                                                                           | R/W-x/u                              | R/W-x/u        | R/W-x/u         | R/W-x/u          | R/W-x/u  | R/W-x/u     |  |  |

|-------------------------|-----------------------------------------------------------------------------------|--------------------------------------|----------------|-----------------|------------------|----------|-------------|--|--|

| LCxG3D4T                | LCxG3D4N                                                                          | LCxG3D3T                             | LCxG3D3N       | LCxG3D2T        | LCxG3D2N         | LCxG3D1T | LCxG3D1N    |  |  |

| bit 7                   |                                                                                   |                                      | •              |                 |                  |          | bit (       |  |  |

|                         |                                                                                   |                                      |                |                 |                  |          |             |  |  |

| Legend:<br>R = Readable | hit                                                                               | W = Writable                         | bit            | II = I Inimpler | nented bit, read | as '0'   |             |  |  |

| u = Bit is unch         |                                                                                   | x = Bit is unkr                      |                |                 | at POR and BO    |          | ther Resets |  |  |

| '1' = Bit is set        | anged                                                                             | '0' = Bit is clea                    |                |                 |                  |          |             |  |  |

|                         |                                                                                   |                                      | areu           |                 |                  |          |             |  |  |

| bit 7                   | LCxG3D4T: (                                                                       | Gate 3 Data 4 1                      | rue (non-inver | rted) bit       |                  |          |             |  |  |

|                         |                                                                                   | is gated into L0                     | •              | ,               |                  |          |             |  |  |

|                         |                                                                                   | is not gated int                     |                |                 |                  |          |             |  |  |

| bit 6                   | LCxG3D4N:                                                                         | Gate 3 Data 4 I                      | Negated (inver | ted) bit        |                  |          |             |  |  |

|                         | 1 = LCxD4N                                                                        | is gated into L                      | CxG3           |                 |                  |          |             |  |  |

|                         | 0 = LCxD4N                                                                        | is not gated inf                     | o LCxG3        |                 |                  |          |             |  |  |

| bit 5                   | LCxG3D3T: 0                                                                       | Gate 3 Data 3 1                      | rue (non-inver | rted) bit       |                  |          |             |  |  |

|                         |                                                                                   | is gated into L0                     |                |                 |                  |          |             |  |  |

|                         |                                                                                   | is not gated int                     |                |                 |                  |          |             |  |  |

| bit 4                   | LCxG3D3N:                                                                         | Gate 3 Data 3                        | Negated (inver | ted) bit        |                  |          |             |  |  |

|                         |                                                                                   | is gated into L                      |                |                 |                  |          |             |  |  |

|                         |                                                                                   | is not gated inf                     |                |                 |                  |          |             |  |  |

| bit 3                   |                                                                                   | Sate 3 Data 2 1                      |                | rted) bit       |                  |          |             |  |  |

|                         |                                                                                   | is gated into L0<br>is not gated int |                |                 |                  |          |             |  |  |

| bit 2                   |                                                                                   | Gate 3 Data 2                        |                | tod) bit        |                  |          |             |  |  |

|                         |                                                                                   | is gated into L                      | •              | ted) bit        |                  |          |             |  |  |

|                         |                                                                                   | is not gated into L                  |                |                 |                  |          |             |  |  |

| bit 1                   |                                                                                   | •                                    |                | rted) bit       |                  |          |             |  |  |

|                         | LCxG3D1T: Gate 3 Data 1 True (non-inverted) bit<br>1 = LCxD1T is gated into LCxG3 |                                      |                |                 |                  |          |             |  |  |

|                         |                                                                                   | is not gated int                     |                |                 |                  |          |             |  |  |

| bit 0                   | LCxG3D1N:                                                                         | Gate 3 Data 1 I                      | Negated (inver | ted) bit        |                  |          |             |  |  |

|                         | 1 = LCxD1N                                                                        | is gated into L                      | CxG3           |                 |                  |          |             |  |  |

|                         | 0 = LCxD1N                                                                        |                                      |                |                 |                  |          |             |  |  |

# REGISTER 19-9: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

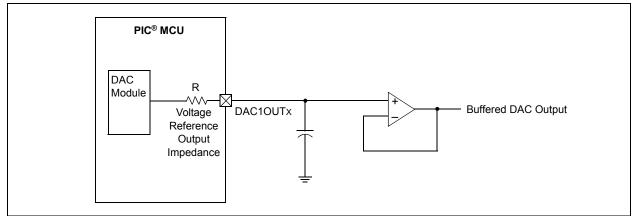

#### FIGURE 23-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

### 23.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

### 23.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled

- DAC output voltage is removed from the DAC1OUT pin

- The DAC1R<7:0> range select bits are cleared

# 26.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

# 26.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |  |  |

### 26.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in Table 34-12: Timer0 and Timer1 External Clock Requirements.

### 26.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

# PIC16(L)F1717/8/9

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1', the<br>result is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<6:3> $\rightarrow PC < 14:11>$                                                                                                                     |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1', the<br>result is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                        |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                             | IORWF            | Inclusive OR W with f                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                        | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                         | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                     | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                       | Status Affected: | Z                                                                                                                                                               |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1', the<br>result is placed back in register 'f'. | Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |

# 34.2 Standard Operating Conditions

| The standard operating co | conditions for any device are defined as:     |        |

|---------------------------|-----------------------------------------------|--------|

| Operating Voltage:        | $VDDMIN \leq VDD \leq VDDMAX$                 |        |

| Operating Temperature:    |                                               |        |

| VDD — Operating Supply    | bly Voltage <sup>(1)</sup>                    |        |

| PIC16LF1717/8/9           | )                                             |        |

| Vddmin (F                 | (Fosc $\leq$ 16 MHz)                          | +1.8V  |

| Vddmin (F                 | (Fosc > 16 MHz)                               | +2.5V  |

| VDDMAX                    |                                               | +3.6V  |

| PIC16F1717/8/9            |                                               |        |

| Vddmin (F                 | (Fosc $\leq$ 16 MHz)                          | +2.3V  |

| Vddmin (>                 | (> 16 MHz)                                    | +2.5V  |

| VDDMAX                    |                                               | +5.5V  |

| TA — Operating Ambien     | nt Temperature Range                          |        |

| Industrial Temperat       | ature                                         |        |

| TA_MIN                    |                                               | 40°C   |

| Та_мах                    |                                               | +85°C  |

| Extended Tempera          | ature                                         |        |

| TA_MIN                    |                                               | 40°C   |