Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1718-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

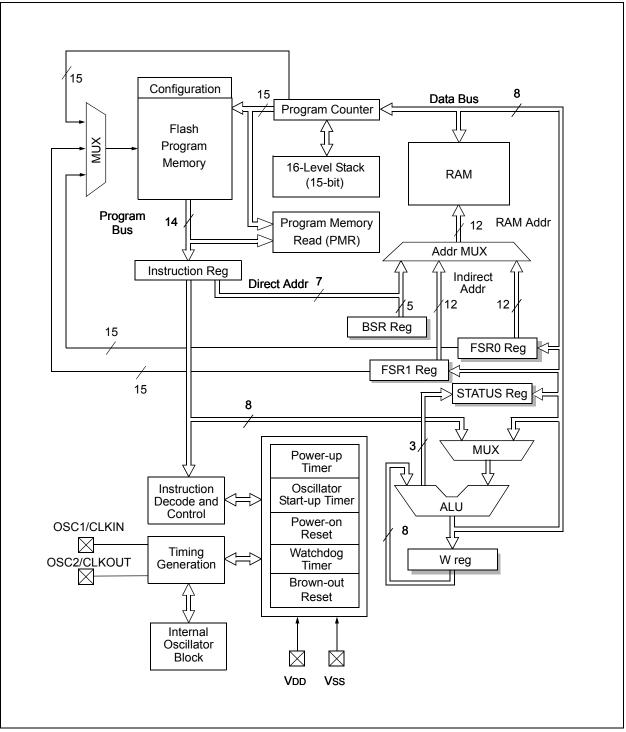

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contains an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

## FIGURE 2-1: CORE BLOCK DIAGRAM

| U-0              | U-0           | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|---------------|------------------|------------------|------------------|------------------|----------------|--------------|

|                  | _             |                  |                  | TUN              | <5:0>            |                |              |

| bit 7            |               | -                |                  |                  |                  |                | bit (        |

|                  |               |                  |                  |                  |                  |                |              |

| Legend:          |               |                  |                  |                  |                  |                |              |

| R = Readable     | e bit         | W = Writable     | bit              | U = Unimpler     | nented bit, read | d as '0'       |              |

| u = Bit is unch  | nanged        | x = Bit is unkr  | nown             | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |               | '0' = Bit is cle | ared             |                  |                  |                |              |

|                  |               |                  |                  |                  |                  |                |              |

| bit 7-6          | Unimpleme     | nted: Read as '  | 0'               |                  |                  |                |              |

| bit 5-0          | TUN<5:0>: F   | Frequency Tuni   | ng bits          |                  |                  |                |              |

|                  | 100000 = N    | linimum freque   | ncy              |                  |                  |                |              |

|                  | •             |                  |                  |                  |                  |                |              |

|                  | •             |                  |                  |                  |                  |                |              |

|                  | •<br>111111 = |                  |                  |                  |                  |                |              |

|                  |               | scillator module | e is running at  | the factory-cali | brated frequen   | cv             |              |

|                  | 000001 =      |                  | s is i anning at |                  |                  | .,             |              |

|                  | •             |                  |                  |                  |                  |                |              |

|                  | •             |                  |                  |                  |                  |                |              |

|                  | •             |                  |                  |                  |                  |                |              |

|                  | 011110 =      | Aavimum froque   |                  |                  |                  |                |              |

|                  | OTTTTT - N    | laximum freque   | ncy              |                  |                  |                |              |

#### REGISTER 6-3: OSCTUNE: OSCILLATOR TUNING REGISTER

| -       |        |        |           |                        |        |        |        |        |                     |

|---------|--------|--------|-----------|------------------------|--------|--------|--------|--------|---------------------|

| Name    | Bit 7  | Bit 6  | Bit 5     | Bit 4                  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

| OSCCON  | SPLLEN |        | IRCF<3:0> |                        |        |        | SCS    | 83     |                     |

| OSCSTAT | SOSCR  | PLLR   | OSTS      | HFIOFR                 | HFIOFL | MFIOFR | LFIOFR | HFIOFS | 84                  |

| OSCTUNE | _      | _      |           | TUN<5:0>               |        |        |        | 85     |                     |

| PIR2    | OSFIF  | C2IF   | C1IF      | _                      | BCL1IF | TMR6IF | TMR4IF | CCP2IF | 95                  |

| PIE2    | OSFIE  | C2IE   | C1IE      | _                      | BCL1IE | TMR6IE | TMR4IE | CCP2IE | 92                  |

| T1CON   | TMR1C  | S<1:0> | T1CKP     | T1CKPS<1:0> T1OSCEN T1 |        |        | —      | TMR10N | 279                 |

|         |        |        |           |                        |        |        |        |        |                     |

## TABLE 6-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

## TABLE 6-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2   | Bit 9/1  | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|------------|----------|---------|---------------------|

| CONFIG1 | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0> |          |         | 55                  |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | F          | OSC<2:0> |         | 55                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

| U-0                  | R/W-0/0            | R/W-0/0                             | R/W-0/0        | R/W-0/0      | REGISTER 3       | R/W-0/0  | R/W-0/0     |

|----------------------|--------------------|-------------------------------------|----------------|--------------|------------------|----------|-------------|

| _                    | NCOIE              | COGIE                               | ZCDIE          | CLC4IE       | CLC3IE           | CLC2IE   | CLC1IE      |

| bit 7                |                    |                                     |                |              |                  |          | bit (       |

| Legend:              |                    |                                     |                |              |                  |          |             |

| R = Reada            | ıble bit           | W = Writable                        | bit            | U = Unimpler | nented bit, read | l as '0' |             |

| u = Bit is unchanged |                    | x = Bit is unki                     |                | •            | at POR and BO    |          | ther Resets |

| '1' = Bit is :       | •                  | '0' = Bit is cle                    |                |              |                  |          |             |

|                      |                    |                                     |                |              |                  |          |             |

| bit 7                | Unimplemer         | nted: Read as '                     | o'             |              |                  |          |             |

| bit 6                |                    | D Interrupt Enat                    | ole bit        |              |                  |          |             |

|                      |                    | errupt enabled errupt disabled      |                |              |                  |          |             |

| bit 5                |                    | G Auto-Shutdov                      | n Interrupt Er | nable bit    |                  |          |             |

|                      |                    | errupt enabled                      | -              |              |                  |          |             |

|                      | 0 = COG int        | errupt disabled                     |                |              |                  |          |             |

| bit 4                |                    | -Cross Detectio                     | n Interrupt Er | able bit     |                  |          |             |

|                      |                    | errupt enabled                      |                |              |                  |          |             |

| L:1 0                |                    | errupt disabled                     | -  -  - :4     |              |                  |          |             |

| bit 3                |                    | C4 Interrupt Ena                    | adie dit       |              |                  |          |             |

|                      |                    | terrupt enabled<br>terrupt disabled |                |              |                  |          |             |

| bit 2                |                    | C3 Interrupt Ena                    |                |              |                  |          |             |

|                      |                    | terrupt enabled                     |                |              |                  |          |             |

|                      | 0 = CLC3 in        | terrupt disabled                    |                |              |                  |          |             |

| bit 1                | CLC2IE: CLC        | C2 Interrupt Ena                    | able bit       |              |                  |          |             |

|                      |                    | terrupt enabled                     |                |              |                  |          |             |

|                      |                    | terrupt disabled                    |                |              |                  |          |             |

| bit 0                |                    | C1 Interrupt Ena                    | able bit       |              |                  |          |             |

|                      |                    | terrupt enabled<br>terrupt disabled |                |              |                  |          |             |

|                      |                    | ion upi disabled                    |                |              |                  |          |             |

| Note:                | Bit PEIE of the IN | ITCON register                      | must be        |              |                  |          |             |

|                      | set to enable any  | peripheral inter                    | rupt.          |              |                  |          |             |

## REGISTER 7-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

# PIC16(L)F1717/8/9

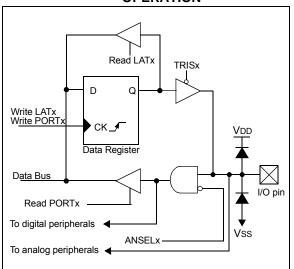

## 11.0 I/O PORTS

Each port has six standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- INLVLx (input level control)

- ODCONx registers (open-drain)

- SLRCONx registers (slew rate)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

TABLE 11-1: PORT AVAILABILITY PER DEVICE

| Device        | PORTA | PORTB | PORTC | PORTD | PORTE |

|---------------|-------|-------|-------|-------|-------|

| PIC16(L)F1717 | ٠     | ٠     | ٠     | ٠     | ٠     |

| PIC16(L)F1718 | •     | ٠     | ٠     |       | •     |

| PIC16(L)F1719 | •     | •     | ٠     | ٠     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

#### FIGURE 11-1: GENERIC I/O PORT OPERATION

## 11.1 PORTA Registers

## 11.1.1 DATA REGISTER

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 11-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 11-1 shows how to initialize PORTA.

Reading the PORTA register (Register 11-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

## 11.1.2 DIRECTION CONTROL

The TRISA register (Register 11-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

## 11.1.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

## REGISTER 11-35: LATE: PORTE DATA LATCH REGISTER<sup>(1)</sup>

| — | — | _ | — | LATE2 | LATE1 | LATE0 |

|---|---|---|---|-------|-------|-------|

|   |   |   |   |       |       | bit 0 |

|   |   |   |   |       |       |       |

|   |   |   |   |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits

Note 1: PIC16(L)F1717/9 only.

### REGISTER 11-36: ANSELE: PORTE ANALOG SELECT REGISTER<sup>(2)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | _   | ANSE2   | ANSE1   | ANSE0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively<sup>(1)</sup> D =Digital I/O. Pin is assigned to port or digital special function.

1 =Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

2: PIC16(L)F1717/9 only.

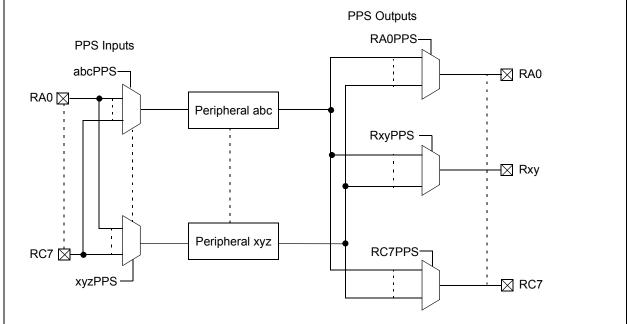

## 12.0 PERIPHERAL PIN SELECT (PPS) MODULE

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 12-1.

## 12.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Multiple peripherals can operate from the same source simultaneously. Port reads always return the pin level regardless of peripheral PPS selection. If a pin also has associated analog functions, the ANSEL bit for that pin must be cleared to enable the digital input buffer.

Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 12-1.

## 12.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- · COG (auto-shutdown)

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 12-2.

**Note:** The notation "Rxy" is a place holder for the pin identifier. For example, RA0PPS.

**Note:** The notation "xxx" in the register name is a place holder for the peripheral identifier. For example, CLC1PPS.

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|

| IOCCP7                                  | IOCCP6  | IOCCP5            | IOCCP4  | IOCCP3                                                | IOCCP2  | IOCCP1  | IOCCP0  |  |  |  |

| bit 7                                   |         |                   |         |                                                       |         |         | bit 0   |  |  |  |

|                                         |         |                   |         |                                                       |         |         |         |  |  |  |

| Legend:                                 | Legend: |                   |         |                                                       |         |         |         |  |  |  |

| R = Readable                            | bit     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |  |

#### REGISTER 13-7: IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER

bit 7-0

bit 7-0

**IOCCP<7:0>:** Interrupt-on-Change PORTC Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-8: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCCN7  | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

IOCCN<7:0>: Interrupt-on-Change PORTC Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 13-9: IOCCF: INTERRUPT-ON-CHANGE PORTC FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCCF7     | IOCCF6     | IOCCF5     | IOCCF4     | IOCCF3     | IOCCF2     | IOCCF1     | IOCCF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCCF<7:0>: Interrupt-on-Change PORTC Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.

- 0 = No change was detected, or the user cleared the detected change.

## 16.11 Register Definitions: Comparator Control

| R/W-0/0          | R-0/0                    | U-0                                      | R/W-0/0         | R/W-0/0                             | R/W-1/1          | R/W-0/0        | R/W-0/0      |

|------------------|--------------------------|------------------------------------------|-----------------|-------------------------------------|------------------|----------------|--------------|

| CxON             | CxOUT                    | _                                        | CxPOL           | CxZLF                               | CxSP             | CxHYS          | CxSYNC       |

| bit 7            |                          |                                          |                 |                                     |                  |                | bit (        |

|                  |                          |                                          |                 |                                     |                  |                |              |

| Legend:          |                          |                                          |                 |                                     |                  |                |              |

| R = Readable     | e bit                    | W = Writable                             | bit             | U = Unimpler                        | mented bit, read | d as '0'       |              |

| u = Bit is uncl  | hanged                   | x = Bit is unk                           | nown            | -n/n = Value a                      | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |                          | '0' = Bit is cle                         | ared            |                                     |                  |                |              |

| bit 7            | CYON: Com                | parator Enable                           | bit             |                                     |                  |                |              |

|                  | -                        | ator is enabled                          | bit             |                                     |                  |                |              |

|                  | •                        |                                          | and consumes    | no active pow                       | er               |                |              |

| bit 6            | CxOUT: Con               | nparator Outpu                           | t bit           |                                     |                  |                |              |

|                  |                          | (inverted pola                           | <u>rity):</u>   |                                     |                  |                |              |

|                  | 1 = CxVP <<br>0 = CxVP > |                                          |                 |                                     |                  |                |              |

|                  |                          | (non-inverted                            | polarity):      |                                     |                  |                |              |

|                  | 1 = CxVP >               | •                                        | <u></u>         |                                     |                  |                |              |

|                  | 0 = CxVP <               | CxVN                                     |                 |                                     |                  |                |              |

| bit 5            | -                        | nted: Read as                            |                 |                                     |                  |                |              |

| bit 4            |                          | nparator Outpu                           |                 | ct bit                              |                  |                |              |

|                  |                          | ator output is in<br>ator output is no   |                 |                                     |                  |                |              |

| bit 3            | CxZLF: Com               | parator Zero L                           | atency Filter E | nable bit                           |                  |                |              |

|                  |                          | ator output is fill<br>ator output is ur |                 |                                     |                  |                |              |

| bit 2            | CxSP: Comp               | parator Speed/F                          | Power Select b  | it                                  |                  |                |              |

|                  | •                        | ator operates in<br>ator operates in     | •               | , higher speed ı<br>w-speed mode    | mode             |                |              |

| bit 1            | CxHYS: Con               | nparator Hyste                           | resis Enable bi | t                                   |                  |                |              |

|                  |                          | ator hysteresis<br>ator hysteresis       |                 |                                     |                  |                |              |

| bit 0            | CxSYNC: Co               | omparator Outp                           | out Synchronou  | is Mode bit                         |                  |                |              |

|                  | 1 = Compara              | ator output to <sup>.</sup>              | Timer1 and I/C  | ) pin is synchro<br>Timer1 clock so |                  | ges on Timer1  | clock source |

|                  | 0 = Compara              | ator output to T                         | ïmer1 and I/O   | pin is asynchro                     | nous.            |                |              |

|                  |                          |                                          |                 |                                     |                  |                |              |

## REGISTER 16-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

### REGISTER 16-3: CMOUT: COMPARATOR OUTPUT REGISTER

| MC2OUT         MC1OUT           bit 7           bit 0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------------------------------------------------------|-----|-----|-----|-----|-----|-----|--------|--------|

| bit 7 bit 0                                           | —   | _   | _   | —   | —   | _   | MC2OUT | MC10UT |

|                                                       |     |     |     |     |     |     |        |        |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 7-2 Unimplemented: Read as '0'

- bit 1 MC2OUT: Mirror Copy of C2OUT bit

bit 0 MC10UT: Mirror Copy of C10UT bit

### TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name                 | Bit 7  | Bit 6  | Bit 5   | Bit 4      | Bit 3  | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|--------|--------|---------|------------|--------|-----------------------|-----------------------|-----------------------|---------------------|

| ANSELA               | —      | —      | ANSA5   | ANSA4      | ANSA3  | ANSA2                 | ANSA1                 | ANSA0                 | 125                 |

| ANSELB               | —      | —      | ANSB5   | ANSB4      | ANSB3  | ANSB2                 | ANSB1                 | ANSB0                 | 131                 |

| CM1CON0              | C10N   | C1OUT  | —       | C1POL      | C1ZLF  | C1SP                  | C1HYS                 | C1SYNC                | 174                 |

| CM2CON0              | C2ON   | C2OUT  | —       | C2POL      | C2ZLF  | C2SP                  | C2HYS                 | C2SYNC                | 174                 |

| CM1CON1              | C1NTP  | C1INTN | C       | C1PCH<2:0> |        |                       | C1NCH<2:0             | >                     | 175                 |

| CM2CON1              | C2NTP  | C2INTN | 0       | 2PCH<2:0>  |        |                       | C2NCH<2:0             | >                     | 175                 |

| CMOUT                | —      | —      | —       | _          | _      | —                     | MC2OUT                | MC10UT                | 176                 |

| FVRCON               | FVREN  | FVRRDY | TSEN    | TSRNG      | CDAF\  | /R<1:0>               | ADFV                  | R<1:0>                | 165                 |

| DAC1CON0             | DAC1EN | —      | DAC10E1 | DAC10E2    | DAC1P  | SS<1:0>               |                       | DAC1NSS               | 260                 |

| DAC1CON1             |        |        |         | DAC1R<     | 7:0>   |                       |                       |                       | 260                 |

| INTCON               | GIE    | PEIE   | TMR0IE  | INTE       | IOCIE  | TMR0IF                | INTF                  | IOCIF                 | 90                  |

| PIE2                 | OSFIE  | C2IE   | C1IE    | _          | BCL1IE | TMR6IE                | TMR4IE                | CCP2IE                | 92                  |

| PIR2                 | OSFIF  | C2IF   | C1IF    | _          | BCL1IF | TMR6IF                | TMR4IF                | CCP2IF                | 95                  |

| TRISA                | TRISA7 | TRISA6 | TRISA5  | TRISA4     | TRISA3 | TRISA2                | TRISA1                | TRISA0                | 124                 |

| TRISB                | TRISB7 | TRISB6 | TRISB5  | TRISB4     | TRISB3 | TRISB2                | TRISB1                | TRISB0                | 130                 |

| TRISC                | TRISC7 | TRISC6 | TRISC5  | TRISC4     | TRISC3 | TRISC2                | TRISC1                | TRISC0                | 135                 |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6 | TRISD5  | TRISD4     | TRISD3 | TRISD2                | TRISD1                | TRISD0                | 140                 |

| TRISE                | —      | —      | —       | _          | TRISE3 | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 145                 |

| RxyPPS               | —      | _      | —       |            |        | RxyPPS<4:0            | )>                    |                       | 153                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

Note 1: PIC16(L)F1717/9 only.

## 22.1 OPA Module Performance

Common AC and DC performance specifications for the OPA module:

- Common Mode Voltage Range

- Leakage Current

- Input Offset Voltage

- Open Loop Gain

- Gain Bandwidth Product

**Common mode voltage range** is the specified voltage range for the OPA+ and OPA- inputs, for which the OPA module will perform to within its specifications. The OPA module is designed to operate with input voltages between Vss and VDD. Behavior for Common mode voltages greater than VDD, or below Vss, are not guaranteed.

**Leakage current** is a measure of the small source or sink currents on the OPA+ and OPA- inputs. To minimize the effect of leakage currents, the effective impedances connected to the OPA+ and OPA- inputs should be kept as small as possible and equal.

**Input offset voltage** is a measure of the voltage difference between the OPA+ and OPA- inputs in a closed loop circuit with the OPA in its linear region. The offset voltage will appear as a DC offset in the output equal to the input offset voltage, multiplied by the gain of the circuit. The input offset voltage is also affected by the Common mode voltage. The OPA is factory calibrated to minimize the input offset voltage of the module.

**Open loop gain** is the ratio of the output voltage to the differential input voltage, (OPA+) - (OPA-). The gain is greatest at DC and falls off with frequency.

**Gain Bandwidth Product** or GBWP is the frequency at which the open loop gain falls off to 0 dB.

## 22.1.1 **OPA Module Control**

The OPA module is enabled by setting the OPAxEN bit of the OPAxCON register. When enabled, the OPA forces the output driver of OPAxOUT pin into tri-state to prevent contention between the driver and the OPA output.

Note: When the OPA module is enabled, the OPAxOUT pin is driven by the op amp output, not by the PORT digital driver. Refer to Table 34-17: Operational Amplifier (OPA) for the op amp output drive capability.

## 22.1.2 UNITY GAIN MODE

The OPAxUG bit of the OPAxCON register selects the Unity Gain mode. When unity gain is selected, the OPA output is connected to the inverting input and the OPAxIN pin is relinquished, releasing the pin for general purpose input and output.

## 22.2 Effects of Reset

A device Reset forces all registers to their Reset state. This disables the OPA module.

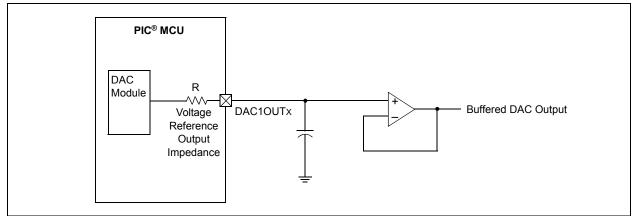

#### FIGURE 23-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

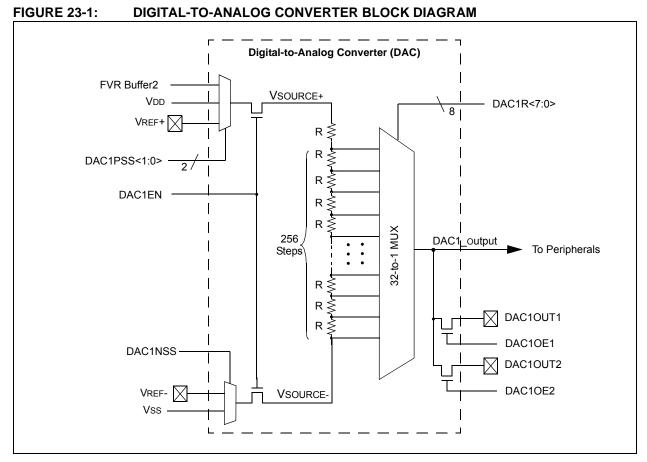

## 23.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 23.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled

- DAC output voltage is removed from the DAC1OUT pin

- The DAC1R<7:0> range select bits are cleared

## 27.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 27-1 displays the Timer1 enable selections.

| TABLE 27-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

## 27.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 27-2 displays the clock source selections.

#### 27.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

#### 27.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

#### TABLE 27-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | T10SCEN | Clock Source                   |

|-------------|---------|--------------------------------|

| 11          | x       | LFINTOSC                       |

| 10          | 0       | External Clocking on T1CKI Pin |

| 01          | x       | System Clock (Fosc)            |

| 00          | x       | Instruction Clock (Fosc/4)     |

# PIC16(L)F1717/8/9

| FIGURE 27-5:           | TIMER1 GATE SINGLE-PULSE MODE                         |                                          |

|------------------------|-------------------------------------------------------|------------------------------------------|

|                        |                                                       |                                          |

| TMR1GE                 |                                                       |                                          |

| T1GPOL                 |                                                       |                                          |

| T1GSPM                 |                                                       |                                          |

| T1GG <u>O/</u><br>DONE | Cleared by falling edge                               | hardware on<br>of T1GVAL                 |

| t1g_in                 | rising edge of T1G                                    |                                          |

| T1CKI                  |                                                       |                                          |

| T1GVAL                 |                                                       |                                          |

| Timer1                 | N N + 1 N + 2                                         |                                          |

| TMR1GIF                | Cleared by software     Set by hard-     falling edge | ware on Cleared by<br>of T1GVAL software |

## 29.4 Register Definitions: CCP Control

#### U-0 U-0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 DCxB<1:0> CCPxM<3:0> \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n/n = Value at POR and BOR/Value at all other Reset u = Bit is unchanged x = Bit is unknown '1' = Bit is set '0' = Bit is cleared bit 7-6 Unimplemented: Read as '0' bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits Capture mode: Unused Compare mode: Unused PWM mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL. bit 3-0 CCPxM<3:0>: CCPx Mode Select bits 11xx = PWM mode 1011 = Compare mode: Auto-conversion Trigger (sets CCPxIF bit), starts ADC conversion if TRIGSEL = CCPx (see Register 21-3) 1010 = Compare mode: generate software interrupt only 1001 = Compare mode: clear output on compare match (set CCPxIF) 1000 = Compare mode: set output on compare match (set CCPxIF) 0111 = Capture mode: every 16th rising edge 0110 = Capture mode: every 4th rising edge 0101 = Capture mode: every rising edge 0100 = Capture mode: every falling edge 0011 = Reserved 0010 = Compare mode: toggle output on match 0001 = Reserved 0000 = Capture/Compare/PWM off (resets CCPx module)

#### **REGISTER 29-1: CCPxCON: CCPx CONTROL REGISTER**

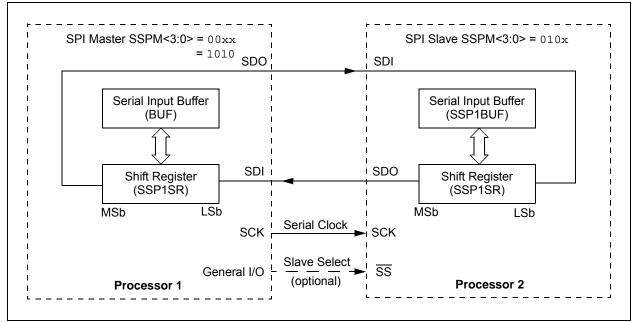

The MSSP consists of a transmit/receive shift register (SSP1SR) and a buffer register (SSP1BUF). The SSP1SR shifts the data in and out of the device, MSb first. The SSP1BUF holds the data that was written to the SSP1SR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSP1BUF register. Then, the Buffer Full detect bit, BF of the SSP1STAT register, and the interrupt flag bit, SSP1IF, are set. This double-buffering of the received data (SSP1BUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSP1BUF register during transmission/reception of data will be ignored and the Write Collision Detect bit WCOL of the SSP1CON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSP1BUF register to complete successfully.

When the application software is expecting to receive valid data, the SSP1BUF should be read before the next byte of data to transfer is written to the SSP1BUF. The Buffer Full bit, BF of the SSP1STAT register, indicates when SSP1BUF has been loaded with the received data (transmission is complete). When the SSP1BUF is read, the BF bit is cleared. This data may be irrelevant if the SP1 is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSP1SR is not directly readable or writable and can only be accessed by addressing the SSP1BUF register. Additionally, the SSP1STAT register indicates the various status conditions.

#### FIGURE 30-5: SPI MASTER/SLAVE CONNECTION

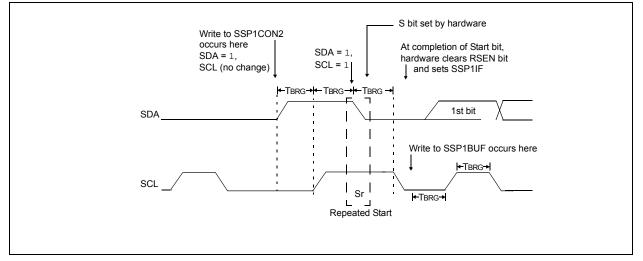

## 30.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 30-27) occurs when the RSEN bit of the SSP1CON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSP1CON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL

pins, the S bit of the SSP1STAT register will be set. The SSP1IF bit will not be set until the Baud Rate Generator has timed out.

Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.2: A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## FIGURE 30-27: REPEATED START CONDITION WAVEFORM

| Name      | Bit 7                                                    | Bit 6   | Bit 5  | Bit 4          | Bit 3       | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>Page |

|-----------|----------------------------------------------------------|---------|--------|----------------|-------------|--------|--------|--------|----------------------------|

| ANSELB    | —                                                        | _       | ANSB5  | ANSB4          | ANSB3       | ANSB2  | ANSB1  | ANSB0  | 131                        |

| ANSELC    | ANSC7                                                    | ANSC6   | ANSC5  | ANSC4          | ANSC4 ANSC3 |        | —      | —      | 136                        |

| INTCON    | GIE                                                      | PEIE    | TMR0IE | INTE           | IOCIE       | TMR0IF | INTF   | IOCIF  | 90                         |

| PIE1      | TMR1GIE                                                  | ADIE    | RCIE   | TXIE           | SSP1IE      | CCP1IE | TMR2IE | TMR1IE | 91                         |

| PIE2      | OSFIE                                                    | C2IE    | C1IE   | _              | BCL1IE      | TMR6IE | TMR4IE | CCP2IE | 92                         |

| PIR1      | TMR1GIF                                                  | ADIF    | RCIF   | TXIF           | SSP1IF      | CCP1IF | TMR2IF | TMR1IF | 94                         |

| PIR2      | OSFIF                                                    | C2IF    | C1IF   | _              | BCL1IF      | TMR6IF | TMR4IF | CCP2IF | 95                         |

| RxyPPS    | _                                                        |         |        |                | 153         |        |        |        |                            |

| SSPCLKPPS | _                                                        | _       | —      |                | 152         |        |        |        |                            |

| SSPDATPPS | —                                                        | _       | _      | SSPDATPPS<4:0> |             |        |        |        | 152                        |

| SSP1ADD   | ADD<7:0>                                                 |         |        |                |             |        | 350    |        |                            |

| SSP1BUF   | Synchronous Serial Port Receive Buffer/Transmit Register |         |        |                |             |        |        | 299*   |                            |

| SSP1CON1  | WCOL                                                     | SSPOV   | SSPEN  | CKP SSPM<3:0>  |             |        |        |        | 346                        |

| SSP1CON2  | GCEN                                                     | ACKSTAT | ACKDT  | ACKEN          | RCEN        | PEN    | RSEN   | SEN    | 348                        |

| SSP1CON3  | ACKTIM                                                   | PCIE    | SCIE   | BOEN           | SDAHT       | SBCDE  | AHEN   | DHEN   | 349                        |

| SSP1MSK   | MSK<7:0>                                                 |         |        |                |             |        |        | 350    |                            |

| SSP1STAT  | SMP                                                      | CKE     | D/A    | Р              | S           | R/W    | UA     | BF     | 345                        |

| TRISB     | TRISB7                                                   | TRISB6  | TRISB5 | TRISB4         | TRISB3      | TRISB2 | TRISB1 | TRISB0 | 130                        |

| TRISC     | TRISC7                                                   | TRISC6  | TRISC5 | TRISC4         | TRISC3      | TRISC2 | TRISC1 | TRISC0 | 135                        |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in I<sup>2</sup>C mode. \* Page provides register information.

## PIC16(L)F1717/8/9

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)         |                                                                        |

|-------------------------------------------------|------------------------------------------------------------------------|

| TX/CK pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                        |

| SREN bit                                        | .º,                                                                    |

| RCIF bit<br>(Interrupt) ———<br>Read             |                                                                        |

| RC1REG<br>Note: Timing diag                     | gram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |

## FIGURE 31-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## TABLE 31-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name     | Bit 7                        | Bit 6  | Bit 5  | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|------------------------------|--------|--------|-------------|--------|--------|--------|--------|---------------------|

| ANSELB   | _                            | _      | ANSB5  | ANSB4       | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 131                 |

| ANSELC   | ANSC7                        | ANSC6  | ANSC5  | ANSC4       | ANSC3  | ANSC2  | —      | —      | 136                 |

| BAUD1CON | ABDOVF                       | RCIDL  | —      | SCKP        | BRG16  | _      | WUE    | ABDEN  | 362                 |

| INTCON   | GIE                          | PEIE   | TMR0IE | INTE        | IOCIE  | TMR0IF | INTF   | IOCIF  | 90                  |

| PIE1     | TMR1GIE                      | ADIE   | RCIE   | TXIE        | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIR1     | TMR1GIF                      | ADIF   | RCIF   | TXIF        | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 94                  |

| RC1REG   | EUSART Receive Data Register |        |        |             |        |        |        | 356*   |                     |

| RC1STA   | SPEN                         | RX9    | SREN   | CREN        | ADDEN  | FERR   | OERR   | RX9D   | 361                 |

| RXPPS    | _                            | —      | —      |             | 152    |        |        |        |                     |

| RxyPPS   | _                            | _      | _      | RxyPPS<4:0> |        |        |        |        | 153                 |

| SP1BRGL  | SP1BRG<7:0>                  |        |        |             |        |        |        | 363*   |                     |

| SP1BRGH  | SP1BRG<15:8>                 |        |        |             |        |        |        | 363*   |                     |

| TRISB    | TRISB7                       | TRISB6 | TRISB5 | TRISB4      | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 130                 |

| TRISC    | TRISC7                       | TRISC6 | TRISC5 | TRISC4      | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 135                 |

| TX1STA   | CSRC                         | TX9    | TXEN   | SYNC        | SENDB  | BRGH   | TRMT   | TX9D   | 360                 |

|          |                              |        |        |             |        |        |        |        |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception. \* Page provides register information.

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                     |      |       |                                                          |  |  |  |

|---------------|---------------------------------------------------------|-------------------------------------|------|-------|----------------------------------------------------------|--|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                      | Тур. | Units | Conditions                                               |  |  |  |

| ТН01 θја      | θJA                                                     | Thermal Resistance Junction to      | 60.0 | °C/W  | 28-pin SPDIP package                                     |  |  |  |

|               |                                                         | Ambient                             | 80.3 | °C/W  | 28-pin SOIC package                                      |  |  |  |

|               |                                                         |                                     | 90.0 | °C/W  | 28-pin SSOP package                                      |  |  |  |

|               |                                                         |                                     | 36.0 | °C/W  | 28-pin QFN 6x6 mm package                                |  |  |  |

|               |                                                         |                                     | 48.0 | °C/W  | 28-pin UQFN 4x4 mm package                               |  |  |  |

|               |                                                         |                                     | 47.2 | °C/W  | 40-pin PDIP package                                      |  |  |  |

|               |                                                         |                                     | 46.0 | °C/W  | 44-pin TQFP                                              |  |  |  |

|               |                                                         |                                     | 41.0 | °C/W  | 40-pin UQFN 5x5 mm package                               |  |  |  |

| ΤΗ02 θ        | θJC                                                     | Thermal Resistance Junction to Case | 31.4 | °C/W  | 28-pin SPDIP package                                     |  |  |  |

|               |                                                         |                                     | 24.0 | °C/W  | 28-pin SOIC package                                      |  |  |  |

|               |                                                         |                                     | 24.0 | °C/W  | 28-pin SSOP package                                      |  |  |  |

|               |                                                         |                                     | 6.0  | °C/W  | 28-pin QFN 6x6 mm package                                |  |  |  |

|               |                                                         |                                     | 12.0 | °C/W  | 28-pin UQFN 4x4 mm package                               |  |  |  |

|               |                                                         |                                     | 24.7 | °C/W  | 40-pin PDIP package                                      |  |  |  |

|               |                                                         |                                     | 14.5 | °C/W  | 44-pin TQFP                                              |  |  |  |

|               |                                                         |                                     | 50.5 | °C/W  | 40-pin UQFN 5x5 mm package                               |  |  |  |

| TH03          | Тјмах                                                   | Maximum Junction Temperature        | 150  | °C    | —                                                        |  |  |  |

| TH04          | PD                                                      | Power Dissipation                   | _    | W     | PD = PINTERNAL + PI/O                                    |  |  |  |

| TH05          | PINTERNAL                                               | Internal Power Dissipation          | —    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |  |

| TH06          | PI/O                                                    | I/O Power Dissipation               | —    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |  |

| TH07          | Pder                                                    | Derated Power                       |      | W     | Pder = PDmax (Τj - Τa)/θja <sup>(2)</sup>                |  |  |  |

## TABLE 34-6: THERMAL CHARACTERISTICS

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

## PIC16(L)F1717/8/9

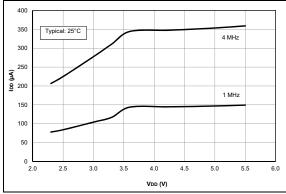

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

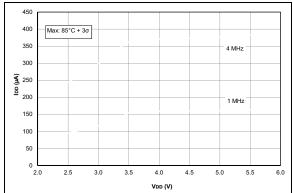

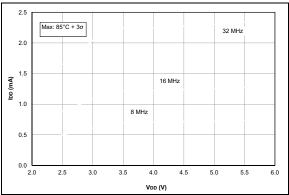

FIGURE 35-13: IDD Typical, EC Oscillator MP Mode, PIC16F1717/8/9 Only.

FIGURE 35-14: IDD Maximum, EC Oscillator MP Mode, PIC16F1717/8/9 Only.

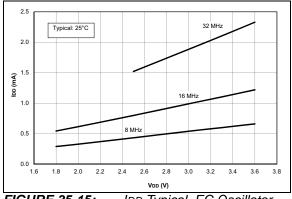

FIGURE 35-15: IDD Typical, EC Oscillator HP Mode, PIC16LF1717/8/9 Only.

FIGURE 35-16: IDD Maximum, EC Oscillator HP Mode, PIC16LF1717/8/9 Only.

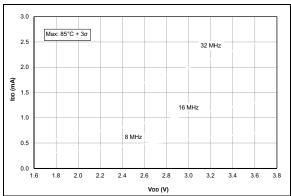

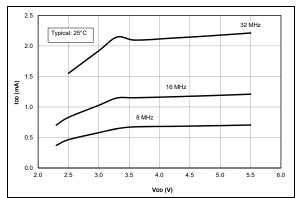

FIGURE 35-17: IDD Typical, EC Oscillator HP Mode, PIC16F1717/8/9 Only.

FIGURE 35-18: IDD Maximum, EC Oscillator HP Mode, PIC16F1717/8/9 Only.