Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1718t-i-mv |

TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC16(L)F1717/9)

| I/O <sup>(2)</sup> | PDIP | TQFP | UQFN | ADC  | Reference          | Comparator       | Ор Атр  | DAC                  | Zero Cross |      | Timers           |          | CCP                 | NCO | MMd | 900       |     | MSSP   |                  | EUSART | CLC                                     | Interrupt          | Pullup | Basic          |

|--------------------|------|------|------|------|--------------------|------------------|---------|----------------------|------------|------|------------------|----------|---------------------|-----|-----|-----------|-----|--------|------------------|--------|-----------------------------------------|--------------------|--------|----------------|

| RA0                | 2    | 19   | 17   | AN0  |                    | C1IN0-<br>C2IN0- |         |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        | CLCINO <sup>(1)</sup>                   | IOC                | Υ      |                |

| RA1                | 3    | 20   | 18   | AN1  |                    | C1IN1-<br>C2IN1- | OPA1OUT |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        | CLCIN1 <sup>(1)</sup>                   | ЮС                 | Υ      |                |

| RA2                | 4    | 21   | 19   | AN2  | V <sub>REF</sub> - | C1IN0+<br>C2IN0+ |         | DAC1OUT1             |            |      |                  |          |                     |     |     |           |     |        |                  |        |                                         | IOC                | Υ      |                |

| RA3                | 5    | 22   | 20   | AN3  | V <sub>REF</sub> + | C1IN1+           |         |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        | 1                                       | IOC                | Υ      |                |

| RA4                | 6    | 23   | 21   |      |                    |                  | OPA1IN+ |                      |            | . TO | CKI <sup>(</sup> | 1)       |                     |     |     |           |     |        |                  |        | 1.1.1.1                                 | IOC                | Υ      |                |

| RA5                | 7    | 24   | 22   | AN4  |                    |                  | OPA1IN- | DAC2OUT1             |            |      |                  |          |                     |     |     |           |     | nSS    | S <sup>(1)</sup> |        | 131 131                                 | IOC                | Υ      |                |

| RA6                | 14   | 31   | 29   |      |                    |                  |         |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        |                                         | IOC                | Υ      | OSC2<br>CLKOUT |

| RA7                | 13   | 30   | 28   |      |                    |                  |         |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        |                                         | ЮС                 | Υ      | OSC1<br>CLKIN  |

| RB0                | 33   | 8    | 8    | AN12 |                    | C2IN1+           |         |                      | ZCD        |      |                  |          |                     |     |     | COG1IN    | (1) |        |                  |        |                                         | INT <sup>(1)</sup> | Υ      |                |

| RB1                | 34   | 9    | 9    | AN10 |                    | C1IN3-<br>C2IN3- | OPA2OUT |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        |                                         | ЮС                 | Υ      |                |

| RB2                | 35   | 10   | 10   | AN8  |                    |                  | OPA2IN- |                      |            |      | -::              |          |                     |     |     |           |     |        |                  |        | 141111111111111111111111111111111111111 | IOC                | Υ      |                |

| RB3                | 36   | 11   | 11   | AN9  |                    | C1IN2-<br>C2IN2- | OPA2IN+ |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        |                                         | ЮС                 | Υ      |                |

| RB4                | 37   | 14   | 12   | AN11 |                    |                  |         |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        |                                         | IOC                | Υ      |                |

| RB5                | 38   | 15   | 13   | AN13 |                    |                  |         |                      |            | į    | 1G <sup>(</sup>  | I)       |                     |     |     |           |     |        | : ::             |        |                                         | IOC                | Υ      |                |

| RB6                | 39   | 16   | 14   |      |                    |                  |         |                      |            |      |                  |          |                     |     |     |           |     |        |                  |        | CLCIN2 <sup>(1)</sup>                   | IOC                | Υ      | ICSPCLK        |

| RB7                | 40   | 17   | 15   |      |                    |                  |         | DAC1OUT2<br>DAC2OUT2 |            |      |                  |          |                     |     |     |           |     |        |                  |        | CLCIN3 <sup>(1)</sup>                   | ЮС                 | Υ      | ICSPDAT        |

| RC0                | 15   | 32   | 30   |      |                    |                  |         |                      |            | SC   | CKI              | j :      |                     |     |     |           |     |        |                  |        |                                         | IOC                | Υ      |                |

| RC1                | 16   | 35   | 31   |      |                    |                  |         |                      |            | S    | os¢              | [·]      | CCP2 <sup>(1)</sup> |     |     |           |     |        | :::              |        | 1::1::                                  | : IQ¢-             | Υ      |                |

| RC2                | 17   | 36   | 32   | AN14 |                    |                  |         |                      |            |      | Ţ.               |          | CCP1 <sup>(1)</sup> |     |     | • . • . • |     |        |                  |        |                                         | IOC                | Υ      |                |

| RC3                | 18   | 37   | 33   | AN15 |                    |                  |         |                      | ,          |      |                  | $\vdots$ |                     |     |     |           |     | SCL/SC | K <sup>(1)</sup> |        |                                         | IOC.               | Υ      |                |

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

<sup>2:</sup> All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

<sup>3:</sup> These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

<sup>4:</sup> Alternate outputs are excluded from solid shaded areas.

<sup>5:</sup> Alternate inputs are excluded from dot shaded areas.

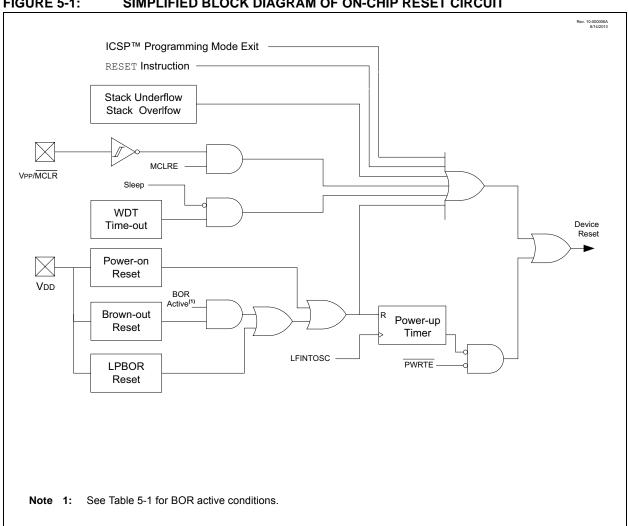

#### 5.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- · Stack Overflow

- · Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|-----|---------|---------|---------|---------|

| OSFIF   | C2IF    | C1IF    | _   | BCL1IF  | TMR6IF  | TMR4IF  | CCP2IF  |

| bit 7   |         |         |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| lator Fail Interrupt Flag bit       |

|-------------------------------------|

| is pending                          |

| is not pending                      |

| arator C2 Interrupt Flag bit        |

| is pending                          |

| is not pending                      |

| arator C1 Interrupt Flag bit        |

| is pending                          |

| is not pending                      |

| nted: Read as '0'                   |

| SP Bus Collision Interrupt Flag bit |

| is pending                          |

| is not pending                      |

| er6 to PR6 Interrupt Flag bit       |

| is pending                          |

| is not pending                      |

| er4 to PR4 Interrupt Flag bit       |

| is pending                          |

| is not pending                      |

| P2 Interrupt Flag bit               |

| is pending                          |

| is not pending                      |

|                                     |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

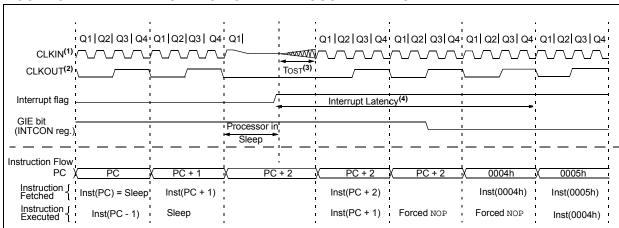

#### FIGURE 8-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

- Note 1: External clock. High, Medium, Low mode assumed.

- 2: CLKOUT is shown here for timing reference.

- 3: Tost = 1024 Tosc. This delay does not apply to EC, RC and INTOSC Oscillator modes or Two-Speed Start-up (see Section 6.4 "Two-Speed Clock Start-up Mode".

- 4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

### 11.2 Register Definitions: PORTA

#### **REGISTER 11-1: PORTA: PORTA REGISTER**

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|---------|---------|-------|---------|---------|---------|

| RA7     | RA6     | RA5     | RA4     | RA3   | RA2     | RA1     | RA0     |

| bit 7   |         |         |         |       |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup>

1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-2: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

#### REGISTER 11-20: ANSELC: PORTC ANALOG SELECT REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0   |

|---------|---------|---------|---------|---------|---------|-----|-------|

| ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | _   | _     |

| bit 7   |         |         |         | •       |         |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-2 ANSC<7:2>: Analog Select between Analog or Digital Function on Pins RC<7:2>, respectively(1)

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

bit 1-0 **Unimplemented:** Read as '0'

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

### REGISTER 11-21: WPUC: WEAK PULL-UP PORTC REGISTER (1,2)

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits

1 = Pull-up enabled0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

### 11.9 PORTE Registers

### 11.9.1 DATA REGISTER (RE<2:0> PIC16(L)F1717/9 ONLY)

PORTE is a 4-bit wide input port and 3-bit wide output port. The corresponding data direction register is TRISE (Register 11-34). Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTE register (Register 11-33) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATE).

# 11.9.2 DIRECTION CONTROL (TRISE<2:0> PIC16(L)F1717/9 ONLY)

The TRISE register (Register 11-34) controls the PORTE pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISE register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

# 11.9.3 INPUT THRESHOLD CONTROL (PIC16(L)F1717/9 ONLY)

The INLVLE register (Register 11-40) controls the input voltage threshold for each of the available PORTE input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTE register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

Note: Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 11.9.4 OPEN-DRAIN CONTROL (PIC16(L)F1717/9 ONLY)

The ODCONE register (Register 11-38) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONE bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONE bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

### 11.9.5 SLEW RATE CONTROL (PIC16(L)F1717/9 ONLY)

The SLRCONE register (Register 11-39) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONE bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONE bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

### 11.9.6 ANALOG CONTROL (PIC16(L)F1717/9 ONLY)

The ANSELE register (Register 11-36) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELE bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELE bits has no effect on digital output functions. A pin with TRIS clear and ANSELE set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELE bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

# 11.9.7 PORTE FUNCTIONS AND OUTPUT PRIORITIES (PIC16(L)F1717/9 ONLY)

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELE register. Digital output functions may continue to control the pin when it is in Analog mode.

TABLE 11-7: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Register on Page |

|------------------------|-------|-------|-------|-------|---------|------------------------|------------------------|------------------------|------------------|

| ANSELE <sup>(1)</sup>  |       |       | _     | _     | _       | ANSE2                  | ANSE1                  | ANSE0                  | 146              |

| INLVLE                 |       |       |       | _     | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> | 148              |

| LATE <sup>(1)</sup>    | _     | _     | _     | _     | _       | LATE2                  | LATE1                  | LATE0                  | 146              |

| ODCONE <sup>(1)</sup>  | _     | _     | _     | _     | _       | ODE2                   | ODE1                   | ODE0                   | 147              |

| PORTE                  | _     | _     | _     | _     | RE3     | RE2 <sup>(1)</sup>     | RE1 <sup>(1)</sup>     | RE0 <sup>(1)</sup>     | 145              |

| SLRCONE <sup>(1)</sup> | _     | _     | _     | _     | _       | SLRE2                  | SLRE1                  | SLRE0                  | 148              |

| TRISE                  | _     | _     | _     | _     | TRISE3  | TRISE2 <sup>(1)</sup>  | TRISE1 <sup>(1)</sup>  | TRISE0 <sup>(1)</sup>  | 145              |

| WPUE                   |       |       |       | 1     | WPUE3   | WPUE2 <sup>(1)</sup>   | WPUE1 <sup>(1)</sup>   | WPUE0 <sup>(1)</sup>   | 147              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: PIC16(L)F1717/9 only.

### 12.8 Register Definitions: PPS Input Selection

#### REGISTER 12-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION

| U-0   | U-0 | U-0 | R/W-q/u | R/W-q/u | R/W-q/u     | R/W-q/u | R/W-q/u |

|-------|-----|-----|---------|---------|-------------|---------|---------|

| _     | _   | _   |         |         | xxxPPS<4:0> |         |         |

| bit 7 |     |     |         |         |             |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = value depends on peripheral

bit 7-5 **Unimplemented:** Read as '0'

bit 4-3 xxxPPS<4:3>: Peripheral xxx Input PORTx Selection bits

See Table 12-1 for the list of available ports for each peripheral.

11 = Peripheral input is from PORTD (PIC16(L)F1717/9 only)

10 = Peripheral input is from PORTC

01 = Peripheral input is from PORTB

00 = Peripheral input is from PORTA

bit 2-0 xxxPPS<2:0>: Peripheral xxx Input PORTx Bit Selection bits

111 = Peripheral input is from PORTx Bit 7 (Rx7)

110 = Peripheral input is from PORTx Bit 6 (Rx6)

101 = Peripheral input is from PORTx Bit 5 (Rx5)

100 = Peripheral input is from PORTx Bit 4 (Rx4)

011 = Peripheral input is from PORTx Bit 3 (Rx3)

010 = Peripheral input is from PORTx Bit 2 (Rx2)

001 = Peripheral input is from PORTx Bit 1 (Rx1)

000 = Peripheral input is from PORTx Bit 0 (Rx0)

### TABLE 12-1: AVAILABLE PORTS FOR INPUT BY PERIPHERAL

| Danish and     | Dominton           | PIC16(L)       | F1717/8/9   | PIC16(L)F1718 | PIC16(L | )F1717/9 |

|----------------|--------------------|----------------|-------------|---------------|---------|----------|

| Peripheral     | Register           | PORTA          | PORTB       | PORTC         | PORTC   | PORTD    |

| PIN interrupt  | INTPPS             | •              | •           |               |         |          |

| Timer0 clock   | T0CKIPPS           | •              | •           |               |         |          |

| Timer1 clock   | T1CKIPPS           | •              |             | •             | •       |          |

| Timer1 gate    | T1GPPS             |                | •           | •             | •       |          |

| CCP1           | CCP1PPS            |                | •           | •             | •       |          |

| CCP2           | CCP2PPS            |                | •           | •             | •       |          |

| COG            | COGINPPS           |                | •           | •             |         | •        |

| MSSP           | SSPCLKPPS          |                | •           | •             | •       |          |

| MSSP           | SSPDATPPS          |                | •           | •             | •       |          |

| MSSP           | SSPSSPPS           | •              |             | •             |         | •        |

| EUSART         | RXPPS              |                | •           | •             | •       |          |

| EUSART         | CKPPS              |                | •           | •             | •       |          |

| All CLCs       | CLCIN0PPS          | •              |             | •             | •       |          |

| All CLCs       | CLCIN1PPS          | •              |             | •             | •       |          |

| All CLCs       | CLCIN2PPS          |                | •           | •             |         | •        |

| All CLCs       | CLCIN3PPS          |                | •           | •             |         | •        |

| Example: CCP1F | PPS = 0x0B selects | RB3 as the inp | ut to CCP1. |               |         |          |

**Note:** Inputs are not available on all ports. A check in a port column of a peripheral row indicates that the port selection is valid for that peripheral. Unsupported ports will input a '0'.

TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3       | Bit 2   | Bit 1 | Bit 0 | Register on page |  |

|-----------------------|-------|-------|-------|-------------|-------------|---------|-------|-------|------------------|--|

| RB0PPS                | _     | _     | _     | RB0PPS<4:0> |             |         |       |       | 153              |  |

| RB1PPS                | _     | _     | _     |             |             | RB1PPS< | 4:0>  |       | 153              |  |

| RB2PPS                | _     | _     | _     |             |             | RB2PPS< | 4:0>  |       | 153              |  |

| RB3PPS                | _     | _     | _     |             |             | RB3PPS< | 4:0>  |       | 153              |  |

| RB4PPS                | _     | _     | _     |             |             | RB4PPS< | 4:0>  |       | 153              |  |

| RB5PPS                | _     | _     | _     |             |             | RB5PPS< | 4:0>  |       | 153              |  |

| RB6PPS                | _     | _     | _     |             |             | RB6PPS< | 4:0>  |       | 153              |  |

| RB7PPS                | _     | _     | _     |             |             | RB7PPS< | 4:0>  |       | 153              |  |

| RC0PPS                | _     | _     | _     |             |             | RC0PPS< | 4:0>  |       | 153              |  |

| RC1PPS                | _     | _     | _     |             |             | RC1PPS< | 4:0>  |       | 153              |  |

| RC2PPS                | _     | _     | _     |             |             | RC2PPS< | 4:0>  |       | 153              |  |

| RC3PPS                | _     | _     | _     |             |             | RC3PPS< | 4:0>  |       | 153              |  |

| RC4PPS                | _     | _     | _     |             | RC4PPS<4:0> |         |       |       |                  |  |

| RC5PPS                | _     | _     | _     |             | RC5PPS<4:0> |         |       |       |                  |  |

| RC6PPS                | _     | _     | _     |             | 153         |         |       |       |                  |  |

| RC7PPS                | _     | _     | _     |             | RC7PPS<4:0> |         |       |       |                  |  |

| RD0PPS <sup>(1)</sup> | _     | _     | _     |             | RD0PPS<4:0> |         |       |       |                  |  |

| RD1PPS <sup>(1)</sup> | _     | _     | _     |             | RD1PPS<4:0> |         |       |       |                  |  |

| RD2PPS <sup>(1)</sup> | _     | _     | _     |             | 153         |         |       |       |                  |  |

| RD3PPS <sup>(1)</sup> | _     | _     | _     |             | 153         |         |       |       |                  |  |

| RD4PPS <sup>(1)</sup> | _     | _     | _     |             | 153         |         |       |       |                  |  |

| RD5PPS <sup>(1)</sup> | _     | _     | _     |             | 153         |         |       |       |                  |  |

| RD6PPS <sup>(1)</sup> | _     | _     | _     | RD6PPS<4:0> |             |         |       |       | 153              |  |

| RD7PPS <sup>(1)</sup> | _     | _     | _     | RD7PPS<4:0> |             |         |       |       | 153              |  |

| RE0PPS <sup>(1)</sup> | _     | _     | _     |             | 153         |         |       |       |                  |  |

| RE1PPS <sup>(1)</sup> | _     | _     | _     | RE1PPS<4:0> |             |         |       |       |                  |  |

| RE2PPS <sup>(1)</sup> | _     | _     | _     |             | 153         |         |       |       |                  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

Note 1: PIC16(L)F1717/9 only.

#### 19.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 19-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

TABLE 19-2: DATA GATING LOGIC

| CLCxGLS0 | LCxG1POL | Gate Logic |  |  |

|----------|----------|------------|--|--|

| 0x55     | 1        | AND        |  |  |

| 0x55     | 0        | NAND       |  |  |

| 0xAA     | 1        | NOR        |  |  |

| 0xAA     | 0        | OR         |  |  |

| 0x00     | 0        | Logic 0    |  |  |

| 0x00     | 1        | Logic 1    |  |  |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 19-7)

- Gate 2: CLCxGLS1 (Register 19-8)

- · Gate 3: CLCxGLS2 (Register 19-9)

- Gate 4: CLCxGLS3 (Register 19-10)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register.

Data gating is indicated in the right side of Figure 19-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 19.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- · S-R Latch

- · D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- Transparent Latch with Set and Reset

Logic functions are shown in Figure 19-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 19.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx (CONTINUED)

| Name                 | Bit7     | Bit6     | Bit5     | Bit4         | Blt3     | Bit2        | Bit1     | Bit0     | Register on Page |

|----------------------|----------|----------|----------|--------------|----------|-------------|----------|----------|------------------|

| CLC2SEL3             | _        | _        | _        | LC2D4S<4:0>  |          |             |          | 226      |                  |

| CLC3GLS0             | LC3G1D4T | LC3G1D4N | LC3G1D3T | LC3G1D3N     | LC3G1D2T | LC3G1D2N    | LC3G1D1T | LC3G1D1N | 227              |

| CLC3GLS1             | LC3G2D4T | LC3G2D4N | LC3G2D3T | LC3G2D3N     | LC3G2D2T | LC3G2D2N    | LC3G2D1T | LC3G2D1N | 228              |

| CLC3GLS2             | LC3G3D4T | LC3G3D4N | LC3G3D3T | LC3G3D3N     | LC3G3D2T | LC3G3D2N    | LC3G3D1T | LC3G3D1N | 229              |

| CLC3GLS3             | LC3G4D4T | LC3G4D4N | LC3G4D3T | LC3G4D3N     | LC3G4D2T | LC3G4D2N    | LC3G4D1T | LC3G4D1N | 230              |

| CLC3POL              | LC3POL   | _        | -        | -            | LC3G4POL | LC3G3POL    | LC3G2POL | LC3G1POL | 225              |

| CLC3SEL0             |          | 1        | 1        |              |          | LC3D1S<4:0> | 1        |          | 225              |

| CLC3SEL1             |          | 1        | 1        |              | ı        | LC3D2S<4:0> | •        |          | 226              |

| CLC3SEL2             | _        | _        | _        |              | ı        | LC3D3S<4:0> | •        |          | 226              |

| CLC3SEL3             |          | 1        | 1        |              | ı        | LC3D4S<4:0> | 1        |          | 226              |

| CLC4GLS0             | LC4G1D4T | LC4G1D4N | LC4G1D3T | LC4G1D3N     | LC4G1D2T | LC4G1D2N    | LC4G1D1T | LC4G1D1N | 227              |

| CLC4GLS1             | LC4G2D4T | LC4G2D4N | LC4G2D3T | LC4G2D3N     | LC4G2D2T | LC4G2D2N    | LC4G2D1T | LC4G2D1N | 228              |

| CLC4GLS2             | LC4G3D4T | LC4G3D4N | LC4G3D3T | LC4G3D3N     | LC4G3D2T | LC4G3D2N    | LC4G3D1T | LC4G3D1N | 229              |

| CLC4GLS3             | LC4G4D4T | LC4G4D4N | LC4G4D3T | LC4G4D3N     | LC4G4D2T | LC4G4D2N    | LC4G4D1T | LC4G4D1N | 230              |

| CLC4POL              | LC4POL   | -        | -        | -            | LC4G4POL | LC4G3POL    | LC4G2POL | LC4G1POL | 225              |

| CLC4SEL0             | _        | 1        | 1        | LC4D1S<4:0>  |          |             |          |          | 225              |

| CLC4SEL1             | _        | -        | 1        | LC4D2S<4:0>  |          |             |          |          | 226              |

| CLC4SEL2             | _        | -        | -        | LC4D3S<4:0>  |          |             |          |          |                  |

| CLC4SEL3             | _        | _        | -        | LC4D4S<4:0>  |          |             |          |          |                  |

| CLCxPPS              | _        | 1        | 1        | CLCxPPS<4:0> |          |             |          |          | 152              |

| INTCON               | GIE      | PEIE     | TMR0IE   | INTE         | IOCIE    | TMR0IF      | INTF     | IOCIF    | 90               |

| PIE3                 |          | NCOIE    | COGIE    | ZCDIE        | CLC4IE   | CLC3IE      | CLC2IE   | CLC1IE   | 93               |

| PIR3                 | -        | NCOIF    | COGIF    | ZCDIF        | CLC4IF   | CLC3IF      | CLC2IF   | CLC1IF   | 96               |

| RxyPPS               | _        | 1        | 1        | RxyPPS<4:0>  |          |             |          | 153      |                  |

| TRISA                | TRISA7   | TRISA6   | TRISA5   | TRISA4       | TRISA3   | TRISA2      | TRISA1   | TRISA0   | 124              |

| TRISB                | TRISB7   | TRISB6   | TRISB5   | TRISB4       | TRISB3   | TRISB2      | TRISB1   | TRISB0   | 130              |

| TRISC                | TRISC7   | TRISC6   | TRISC5   | TRISC4       | TRISC3   | TRISC2      | TRISC1   | TRISC0   | 135              |

| TRISD <sup>(1)</sup> | TRISD7   | TRISD6   | TRISD5   | TRISD4       | TRISD3   | TRISD2      | TRISD1   | TRISD0   | 140              |

**Legend:** — = unimplemented read as '0'. Shaded cells are not used for CLC module.

Note 1: PIC16(L)F1717/9 only.

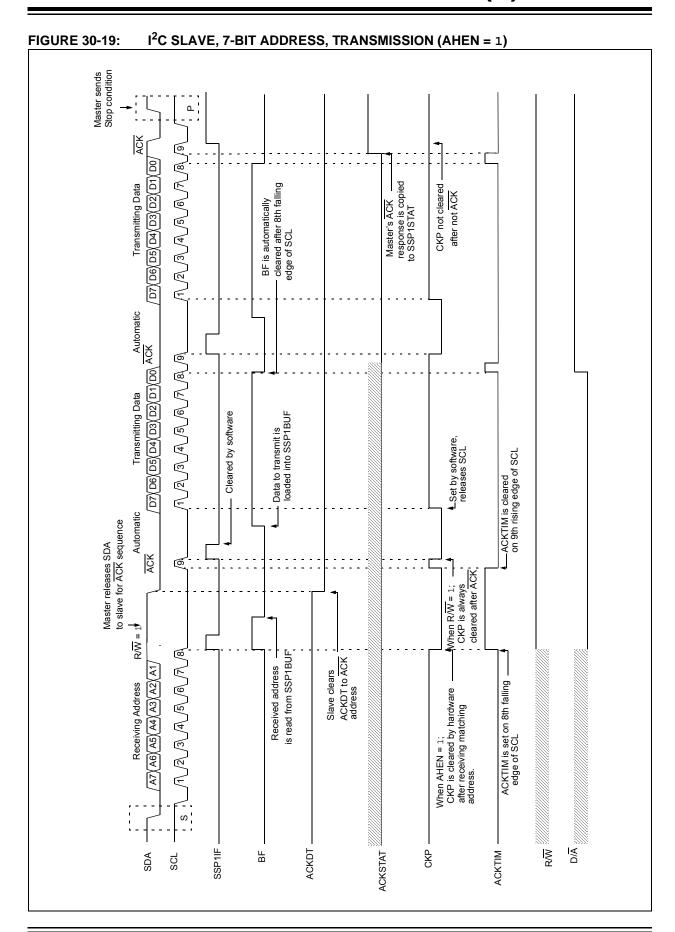

#### 30.5.3.2 7-Bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 30-18 can be used as a reference to this list.

- Master sends a Start condition on SDA and SCL.

- 2. S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the Slave setting SSP1IF bit.

- Slave hardware generates an ACK and sets SSP1IF.

- 5. SSP1IF bit is cleared by user.

- 6. Software reads the received address from SSP1BUF, clearing BF.

- 7. R/W is set so CKP was automatically cleared after the ACK.

- The slave software loads the transmit data into SSP1BUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSP1IF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSP1IF bit is cleared.

- The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master  $\overline{\mathsf{ACK}}$ s the clock will be stretched.

- **2:** ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not  $\overline{ACK}$ ; the clock is not held, but SSP1IF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

### 31.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 31-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RC1REG register.

#### 31.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RC1STA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TX1STA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RC1STA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

Note:

If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

#### 31.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 31.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RC1REG register.

Note:

If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See **Section 31.1.2.5** "**Receive Overrun Error**" for more information on overrun errors.

#### 31.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 34.2 **Standard Operating Conditions**

The standard operating conditions for any device are defined as:

Operating Voltage:  $V \mathsf{DDMIN} \leq V \mathsf{DD} \leq V \mathsf{DDMAX}$ Operating Temperature:  $TA\_MIN \le TA \le TA\_MAX$

VDD — OI

| +1.8V |

|-------|

| +2.5V |

| +3.6V |

|       |

| +2.3V |

| +2.5V |

| +5.5V |

|       |

|       |

| 40°C  |

| +85°C |

|       |

|       |

Ta\_Min -40°C

Note 1: See Parameter D001, DS Characteristics: Supply Voltage.

TABLE 34-4: I/O PORTS

### Standard Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym. | Characteristic                       | Min.           | Тур.† | Max.     | Units    | Conditions                                           |  |  |  |

|---------------|------|--------------------------------------|----------------|-------|----------|----------|------------------------------------------------------|--|--|--|

|               | VIL  | Input Low Voltage                    |                |       |          |          |                                                      |  |  |  |

|               |      | I/O PORT:                            |                |       |          |          |                                                      |  |  |  |

| D034          |      | with TTL buffer                      | _              | _     | 0.8      | V        | $4.5V \leq V \text{DD} \leq 5.5V$                    |  |  |  |

| D034A         |      |                                      | _              |       | 0.15 VDD | <b>V</b> | $1.8V \leq V \text{DD} \leq 4.5V$                    |  |  |  |

| D035          |      | with Schmitt Trigger buffer          | _              | -     | 0.2 VDD  | V        | $2.0V \leq V \text{DD} \leq 5.5V$                    |  |  |  |

|               |      | with I <sup>2</sup> C levels         | _              | _     | 0.3 VDD  | V        |                                                      |  |  |  |

|               |      | with SMBus levels                    | _              | _     | 0.8      | V        | $2.7 \text{V} \leq \text{VDD} \leq 5.5 \text{V}$     |  |  |  |

| D036          |      | MCLR, OSC1 (EXTRC mode)              | _              | _     | 0.2 VDD  | V        | (Note 1)                                             |  |  |  |

| D036A         |      | OSC1 (HS mode)                       | _              | _     | 0.3 VDD  | V        |                                                      |  |  |  |

|               | VIH  | Input High Voltage                   |                |       |          |          |                                                      |  |  |  |

|               |      | I/O ports:                           |                |       |          |          |                                                      |  |  |  |

| D040          |      | with TTL buffer                      | 2.0            | _     | _        | V        | $4.5V \leq V \text{DD} \leq 5.5V$                    |  |  |  |

| D040A         |      |                                      | 0.25 VDD + 0.8 |       | _        | <b>V</b> | $1.8V \leq V \text{DD} \leq 4.5V$                    |  |  |  |

| D041          |      | with Schmitt Trigger buffer          | 0.8 VDD        | I     | _        | <b>V</b> | $2.0V \leq V \text{DD} \leq 5.5V$                    |  |  |  |

|               |      | with I <sup>2</sup> C levels         | 0.7 VDD        | I     | _        | >        |                                                      |  |  |  |

|               |      | with SMBus levels                    | 2.1            |       | _        | <b>V</b> | $2.7V \leq V \text{DD} \leq 5.5V$                    |  |  |  |

| D042          |      | MCLR                                 | 0.8 VDD        | I     | _        | <b>V</b> |                                                      |  |  |  |

| D043A         |      | OSC1 (HS mode)                       | 0.7 Vdd        | _     | _        | V        |                                                      |  |  |  |

| D043B         |      | OSC1 (EXTRC oscillator)              | 0.9 Vdd        | _     | _        | V        | VDD > 2.0V(Note 1)                                   |  |  |  |

|               | lıL  | Input Leakage Current <sup>(2)</sup> |                |       |          |          |                                                      |  |  |  |

| D060          |      | I/O Ports                            | _              | ± 5   | ± 125    | nA       | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance,<br>85°C  |  |  |  |

|               |      |                                      | _              | ± 5   | ± 1000   | nA       | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance,<br>125°C |  |  |  |

| D061          |      | MCLR <sup>(3)</sup>                  | _              | ± 5   | ± 200    | nA       | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance,<br>85°C  |  |  |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in EXTRC mode.

- 2: Negative current is defined as current sourced by the pin.

- 3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 4: Including OSC2 in CLKOUT mode.

**Note:** Unless otherwise noted, VIN = 5V, FOSC = 500 kHz, CIN = 0.1  $\mu F$ , TA = 25°C.

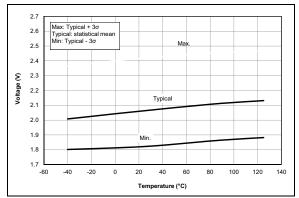

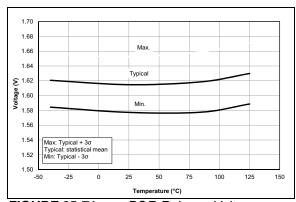

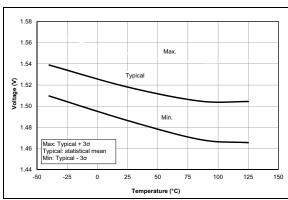

FIGURE 35-67: LPBOR Reset Voltage.

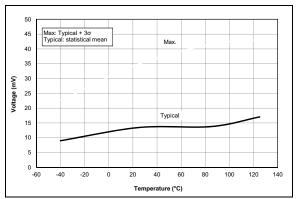

FIGURE 35-68: LPBOR Reset Hysteresis.

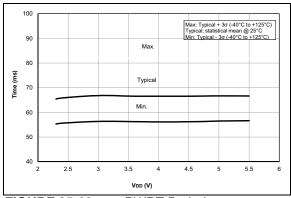

FIGURE 35-69: PWRT Period, PIC16F1717/8/9 Only.

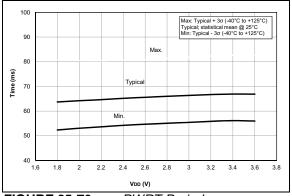

**FIGURE 35-70:** PWRT Period, PIC16LF1717/8/9 Only.

FIGURE 35-71: POR Release Voltage.

**FIGURE 35-72:** POR Rearm Voltage, NP Mode (VREGPM1 = 0), PIC16F1717/8/9 Only.

### Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office** 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address:

www.microchip.com Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323

Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Hangzhou Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355

Fax: 86-532-8502-7205 China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai Tel: 86-756-3210040

Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631

Fax: 91-11-4160-8632 India - Pune

Tel: 91-20-3019-1500 Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828 Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Dusseldorf** Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

Germany - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611

Fax: 39-0331-466781 Italy - Venice

Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15