#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1718t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

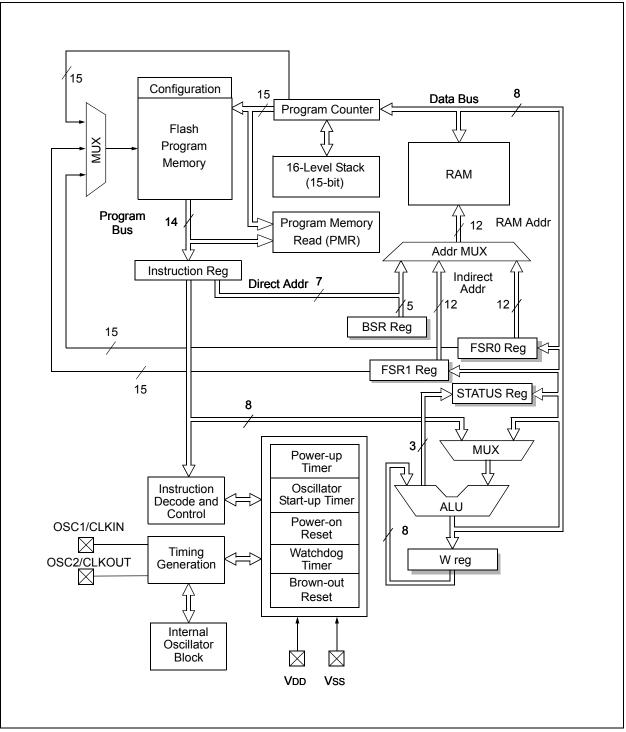

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contains an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

### FIGURE 2-1: CORE BLOCK DIAGRAM

| IABL     | ABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |               |                                              |              |         |         |                        |                        |                        |                      |                              |

|----------|----------------------------------------------------------|---------------|----------------------------------------------|--------------|---------|---------|------------------------|------------------------|------------------------|----------------------|------------------------------|

| Addr.    | Name                                                     | Bit 7         | Bit 6                                        | Bit 5        | Bit 4   | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Value on<br>POR, BOR | Value on all<br>other Resets |

| Bank     | ¢7                                                       |               |                                              |              |         |         |                        |                        |                        |                      |                              |

| 38Ch     | INLVLA                                                   | INLVLA7       | INLVLA6                                      | INLVLA5      | INLVLA4 | INLVLA3 | INLVLA2                | INLVLA1                | INLVLA0                | 1111 1111            | 1111 1111                    |

| 38Dh     | INLVLB                                                   | INLVLB7       | INLVLB6                                      | INLVLB5      | INLVLB4 | INLVLB3 | INLVLB2                | INLVLB1                | INLVLB0                | 1111 1111            | 1111 1111                    |

| 38Eh     | INLVLC                                                   | INLVLC7       | INLVLC6                                      | INLVLC5      | INLVLC4 | INLVLC3 | INLVLC2                | INLVLC1                | INLVLC0                | 1111 1111            | 1111 1111                    |

| 38Fh     | INLVLD <sup>(1)</sup>                                    | INLVLD7       | INLVLD6                                      | INLVLD5      | INLVLD4 | INLVLD3 | INLVLD2                | INLVLD1                | INLVLD0                | 1111 1111            | 1111 1111                    |

| 390h     | INLVLE                                                   |               |                                              |              |         | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> | 1111                 | 1111                         |

| 391h     | IOCAP                                                    | IOCAP7        | IOCAP6                                       | IOCAP5       | IOCAP4  | IOCAP3  | IOCAP2                 | IOCAP1                 | IOCAP0                 | 0000 0000            | 00 0000                      |

| 392h     | IOCAN                                                    | IOCAN7        | IOCAN6                                       | IOCAN5       | IOCAN4  | IOCAN3  | IOCAN2                 | IOCAN1                 | IOCAN0                 | 0000 0000            | 00 0000                      |

| 393h     | IOCAF                                                    | IOCAF7        | IOCAF6                                       | IOCAF5       | IOCAF4  | IOCAF3  | IOCAF2                 | IOCAF1                 | IOCAF0                 | 0000 0000            | 00 0000                      |

| 394h     | IOCBP                                                    | IOCBP7        | IOCBP6                                       | IOCBP5       | IOCBP4  | IOCBP3  | IOCBP2                 | IOCBP1                 | IOCBP0                 | 0000 0000            | 0000                         |

| 395h     | IOCBN                                                    | IOCBN7        | IOCBN6                                       | IOCBN5       | IOCBN4  | IOCBN3  | IOCBN2                 | IOCBN1                 | IOCBN0                 | 0000 0000            | 0000                         |

| 396h     | IOCBF                                                    | IOCBF7        | IOCBF6                                       | IOCBF5       | IOCBF4  | IOCBF3  | IOCBF2                 | IOCBF1                 | IOCBF0                 | 0000 0000            | 0000                         |

| 397h     | IOCCP                                                    | IOCCP7        | IOCCP6                                       | IOCCP5       | IOCCP4  | IOCCP3  | IOCCP2                 | IOCCP1                 | IOCCP0                 | 0000 0000            | 0000 0000                    |

| 398h     | IOCCN                                                    | IOCCN7        | IOCCN6                                       | IOCCN5       | IOCCN4  | IOCCN3  | IOCCN2                 | IOCCN1                 | IOCCN0                 | 0000 0000            | 0000 0000                    |

| 399h     | IOCCF                                                    | IOCCF7        | IOCCF6                                       | IOCCF5       | IOCCF4  | IOCCF3  | IOCCF2                 | IOCCF1                 | IOCCF0                 | 0000 0000            | 0000 0000                    |

| 39Ah     | )Ah                                                      |               |                                              |              |         |         |                        |                        |                        |                      |                              |

| 39Ch     | —                                                        | Unimplemen    | ited                                         |              |         |         |                        |                        |                        | _                    | —                            |

| 39Dh     | IOCEP                                                    | _             | —                                            | _            | _       | IOCEP3  | _                      | _                      | _                      | 0                    | 0                            |

| 39Eh     | IOCEN                                                    | _             | _                                            | _            | _       | IOCEN3  | _                      | _                      | _                      | 0                    | 0                            |

| 39Fh     | IOCEF                                                    | _             | _                                            | _            | _       | IOCEF3  | _                      | _                      | _                      | 0                    | 0                            |

| Bank     | 8                                                        | •             | •                                            | •            |         |         |                        |                        |                        |                      | •                            |

| 40Ch     |                                                          |               | 1.1                                          |              |         |         |                        |                        |                        |                      |                              |

| 414h     | _                                                        | Unimplemen    | ited                                         |              |         |         |                        |                        |                        | _                    | —                            |

| 415h     | TMR4                                                     | Holding Reg   | ister for the 8-I                            | bit TMR4 Reg | ister   |         |                        |                        |                        | 0000 0000            | uuuu uuuu                    |

| 416h     | PR4                                                      | Timer4 Perio  | d Register                                   |              |         |         |                        |                        |                        | 1111 1111            | uuuu uuuu                    |

| 417h     | T4CON                                                    | _             |                                              | T4OUT        | PS<3:0> |         | TMR4ON                 | T4CK                   | PS<1:0>                | -000 0000            | -000 0000                    |

| 418h     |                                                          |               |                                              |              |         |         |                        |                        |                        |                      |                              |

| <br>41Bh | —                                                        | Unimplemen    | ited                                         |              |         |         |                        |                        |                        | —                    | —                            |

| 41Ch     | TMR6                                                     | Holding Reg   | lolding Register for the 8-bit TMR6 Register |              |         |         |                        |                        |                        | 0000 0000            | uuuu uuuu                    |

| 41Dh     | PR6                                                      |               | Fimerô Period Register                       |              |         |         |                        |                        |                        | 1111 1111            | uuuu uuuu                    |

| 41Eh     | T6CON                                                    | _             | - 3                                          | T6OUT        | PS<3:0> |         | TMR6ON                 | T6CK                   | PS<1:0>                | -000 0000            | -000 0000                    |

| 41Fh     | _                                                        | Unimplemen    | ited                                         |              |         |         |                        |                        | -                      | _                    | _                            |

| Bank     | (9                                                       |               |                                              |              |         |         |                        |                        |                        |                      | 1                            |

| 48Ch     |                                                          |               |                                              |              |         |         |                        |                        |                        |                      |                              |

| to       | _                                                        | Unimplemented |                                              |              |         |         |                        |                        |                        | _                    | -                            |

### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Unimplemented to 497h 498h NCO1ACCL NCO1ACC 0000 0000 0000 0000 499h NCO1ACCH NCO1ACC 0000 0000 0000 0000 49Ah NCO1ACCU NCO1ACC \_\_\_\_ 0000 ---- 0000 49Bh NCO1INCL NCO1INC 0000 0001 0000 0001 49Ch NCO1INCH NCO1INC 0000 0000 0000 0000 49Dh NCO1INCU NCO1INC \_\_\_\_ \_\_\_\_ 0000 0000 NCO1CON 49Eh N1EN N10UT N1POL N1PFM 0-00 0-00 ---0 ---0 49Fh NCO1CLK N1PWS<2:0> N1CKS<1:0> 000- --00 000- --00

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented on PIC16(L)F1718.

2: Unimplemented on PIC16LF1717/8/9

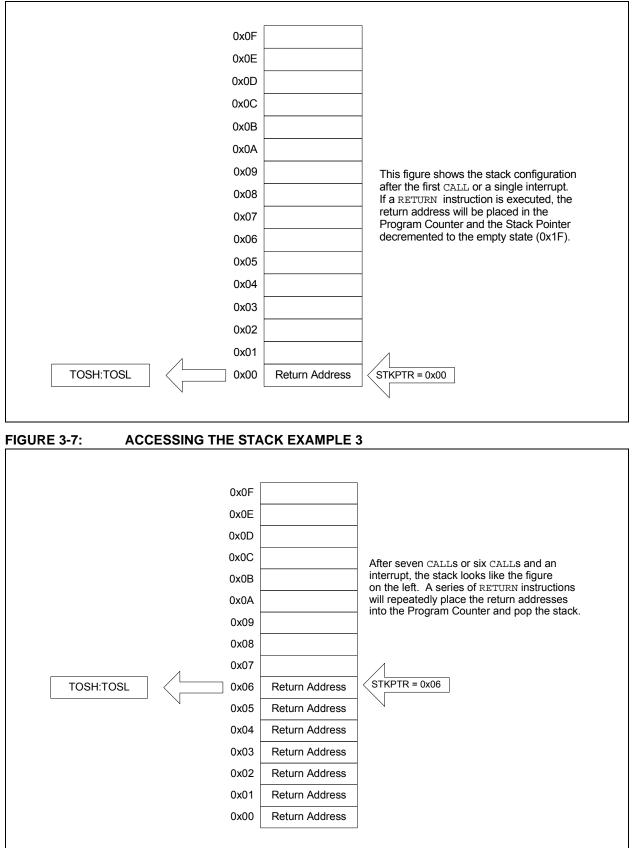

FIGURE 3-6: ACCESSING THE STACK EXAMPLE 2

#### 5.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 5.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

### 5.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 5-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 5-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 1.0        | 37     | Awake       | Active   | Waits for BOR ready (BORRDY = $1$ )                                 |

| 10         | Х      | Sleep       | Disabled | Waits for BOR feady (BORRD F - 1)                                   |

| 01         | 1      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)                     |

| 01         | 0      | X           | Disabled | Begins immediately (BORRDY = $x$ )                                  |

| 00         | Х      | Х           | Disabled | begins inimediately (BORRDT - X)                                    |

TABLE 5-1:BOR OPERATING MODES

**Note 1:** In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 5.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 5.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

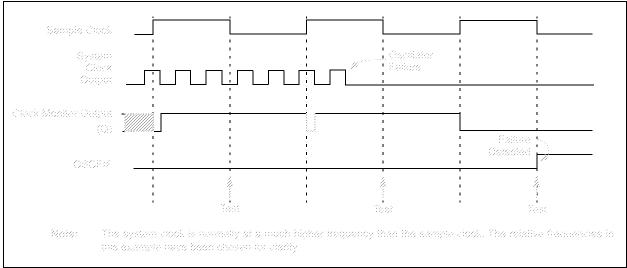

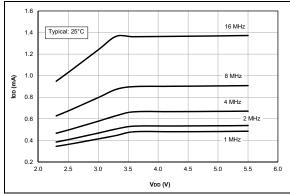

#### 6.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 6-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 6-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 6.2.2.7** "Internal Oscillator Clock Switch Timing" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

A fast start-up oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

#### 6.2.2.2 MFINTOSC

The Medium Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 6-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 6-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 6.2.2.7** "Internal Oscillator Clock Switch Timing" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

#### 6.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 6-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### 6.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 6-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See Section 6.2.2.7 "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

|         | - <b>LE</b> . <b>ODOO</b> |         |         |         |         |         |         |

|---------|---------------------------|---------|---------|---------|---------|---------|---------|

| R/W-0/0 | R/W-0/0                   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| ODC7    | ODC6                      | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    |

| bit 7   |                           |         |         |         |         |         | bit 0   |

|         |                           |         |         |         |         |         |         |

| Legend: |                           |         |         |         |         |         |         |

#### REGISTER 11-22: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ODC<7:0>:** PORTC Open-Drain Enable bits

For RC<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

### REGISTER 11-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits

For RC<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### REGISTER 11-24: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7   |         |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

INLVLC<7:0>: PORTC Input Level Select bits

For RC<7:0> pins, respectively

1 = Port pin digital input operates with ST thresholds

0 = Port pin digital input operates with TTL thresholds

## 12.8 Register Definitions: PPS Input Selection

REGISTER 12-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION

| U-0             | U-0                              | U-0                                                                                                                                                                                                                   | R/W-q/u | R/W-q/u        | R/W-q/u          | R/W-q/u           | R/W-q/u    |  |  |

|-----------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|------------------|-------------------|------------|--|--|

| _               | —                                | — xxxPPS<4:0>                                                                                                                                                                                                         |         |                |                  |                   |            |  |  |

| bit 7           |                                  |                                                                                                                                                                                                                       |         |                |                  |                   | bit        |  |  |

| Legend:         |                                  |                                                                                                                                                                                                                       |         |                |                  |                   |            |  |  |

| -               |                                  |                                                                                                                                                                                                                       |         |                | nented bit, read | as '0'            |            |  |  |

| u = Bit is un   | changed                          | x = Bit is unki                                                                                                                                                                                                       | nown    | -n/n = Value a | t POR and BOF    | R/Value at all ot | her Resets |  |  |

| '1' = Bit is se | et                               | '0' = Bit is cle                                                                                                                                                                                                      | ared    | q = value dep  | ends on periphe  | eral              |            |  |  |

|                 | 10 = Periphera<br>01 = Periphera | <ul> <li>11 = Peripheral input is from PORTD (PIC16(L)F1717/9 only)</li> <li>10 = Peripheral input is from PORTC</li> <li>01 = Peripheral input is from PORTB</li> <li>00 = Peripheral input is from PORTA</li> </ul> |         |                |                  |                   |            |  |  |

| bit 2-0         |                                  |                                                                                                                                                                                                                       |         |                |                  |                   |            |  |  |

000 = Peripheral input is from PORTx Bit 0 (Rx0)

| Derinherel    | Deviator           | PIC16(L)F1717/8/9 |              | PIC16(L)F1718 | PIC16(L | )F1717/9 |

|---------------|--------------------|-------------------|--------------|---------------|---------|----------|

| Peripheral    | Register           | PORTA             | PORTB        | PORTC         | PORTC   | PORTD    |

| PIN interrupt | INTPPS             | •                 | •            |               |         |          |

| Timer0 clock  | TOCKIPPS           | •                 | •            |               |         |          |

| Timer1 clock  | T1CKIPPS           | •                 |              | •             | •       |          |

| Timer1 gate   | T1GPPS             |                   | •            | •             | •       |          |

| CCP1          | CCP1PPS            |                   | •            | •             | •       |          |

| CCP2          | CCP2PPS            |                   | •            | •             | •       |          |

| COG           | COGINPPS           |                   | •            | •             |         | •        |

| MSSP          | SSPCLKPPS          |                   | •            | •             | •       |          |

| MSSP          | SSPDATPPS          |                   | •            | •             | •       |          |

| MSSP          | SSPSSPPS           | •                 |              | •             |         | •        |

| EUSART        | RXPPS              |                   | •            | •             | •       |          |

| EUSART        | CKPPS              |                   | •            | •             | •       |          |

| All CLCs      | CLCIN0PPS          | •                 |              | •             | •       |          |

| All CLCs      | CLCIN1PPS          | •                 |              | •             | •       |          |

| All CLCs      | CLCIN2PPS          |                   | •            | •             |         | •        |

| All CLCs      | CLCIN3PPS          |                   | •            | •             |         | •        |

| Example: CCP1 | PPS = 0x0B selects | RB3 as the inp    | out to CCP1. | · · ·         |         |          |

#### TABLE 12-1: AVAILABLE PORTS FOR INPUT BY PERIPHERAL

**Note:** Inputs are not available on all ports. A check in a port column of a peripheral row indicates that the port selection is valid for that peripheral. Unsupported ports will input a '0'.

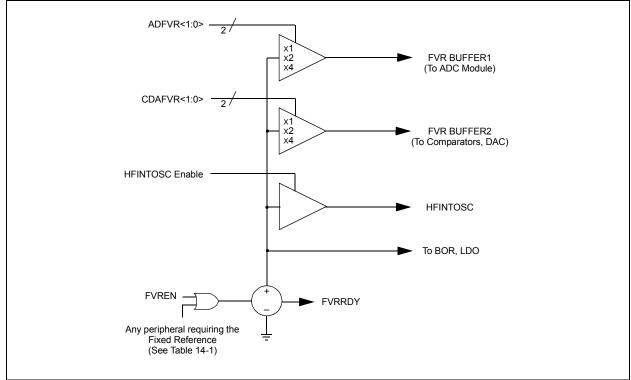

### TABLE 14-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

| Peripheral | Conditions                                                      | Description                                                 |

|------------|-----------------------------------------------------------------|-------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 100 and<br>IRCF<3:0> ≠ 000x                         | INTOSC is active and device is not in Sleep                 |

|            | BOREN<1:0> = 11                                                 | BOR always enabled                                          |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                   | BOR disabled in Sleep mode, BOR Fast Start enabled          |

|            | BOREN<1:0> = 01 and BORFS = 1                                   | BOR under software control, BOR Fast Start enabled          |

| LDO        | All PIC16F1717/8/9 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the ULP regulator when in Sleep mode |

## 15.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between  $-40^{\circ}$ C and  $+85^{\circ}$ C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

## 15.1 Circuit Operation

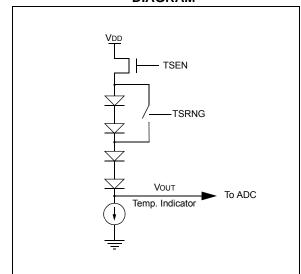

Figure 15-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 15-1 describes the output characteristics of the temperature indicator.

### EQUATION 15-1: VOUT RANGES

High Range:

$$V_{OUT} = V_{DD} - 4V_T$$

Low Range:  $V_{OUT} = V_{DD} - 2V_T$

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 15-1: TEMPERATURE CIRCUIT DIAGRAM

## 15.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 15-1 shows the recommended minimum  $\mathsf{V}\mathsf{D}\mathsf{D}$  vs. range setting.

### TABLE 15-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

## 15.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 21.0 "Analog-to-Digital Converter (ADC) Module"** for detailed information.

### REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

GxFSIM0: COGx Falling Event Input Source 0 Mode bit

GxFIS0 = 1:

bit 0

- 1 = Pin selected with COGxPPS control high-to-low transition will cause a falling event after falling event phase delay

- 0 = Pin selected with COGxPPS control low level will cause an immediate falling event

GxFIS0 = 0:

Pin selected with COGxPPS control has no effect on falling event

| R/W-0/0                 |                             |                  |                |                |                  |                  |              |

|-------------------------|-----------------------------|------------------|----------------|----------------|------------------|------------------|--------------|

|                         | R/W-0/0                     | R/W-0/0          | R/W-0/0        | U-0            | U-0              | U-0              | U-0          |

|                         | TRIGSEL<3:0> <sup>(1)</sup> |                  |                |                | —                | —                | —            |

| bit 7                   |                             |                  |                |                |                  |                  | bit (        |

| Logondu                 |                             |                  |                |                |                  |                  |              |

| Legend:<br>R = Readable | <b>b</b> :4                 |                  | L :4           |                |                  |                  |              |

|                         |                             | W = Writable     | DIC            | •              | nented bit, read |                  |              |

| u = Bit is unch         | anged                       | x = Bit is unkr  | nown           | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set        |                             | '0' = Bit is cle | ared           |                |                  |                  |              |

|                         | 0001 = CCF                  |                  | trigger select | eu             |                  |                  |              |

### REGISTER 21-3: ADCON2: ADC CONTROL REGISTER 2

- 1110 = Reserved

- 1111 = Reserved

- bit 3-0 Unimplemented: Read as '0'

- Note 1: This is a rising edge sensitive input for all sources.

- **2:** Signal also sets its corresponding interrupt flag.

#### **REGISTER 21-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u | R/W-x/u           | R/W-x/u                                   | R/W-x/u        | R/W-x/u                                                                                    | R/W-x/u                                                                                                                  | R/W-x/u                                                                                                                                   |

|---------|-------------------|-------------------------------------------|----------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|         |                   | ADRE                                      | S<9:2>         |                                                                                            |                                                                                                                          |                                                                                                                                           |

|         |                   |                                           |                |                                                                                            |                                                                                                                          | bit 0                                                                                                                                     |

|         |                   |                                           |                |                                                                                            |                                                                                                                          |                                                                                                                                           |

|         |                   |                                           |                |                                                                                            |                                                                                                                          |                                                                                                                                           |

| bit     | W = Writable I    | bit                                       | U = Unimpler   | nented bit, read                                                                           | d as '0'                                                                                                                 |                                                                                                                                           |

| anged   | x = Bit is unkn   | iown                                      | -n/n = Value a | at POR and BC                                                                              | R/Value at all o                                                                                                         | other Resets                                                                                                                              |

|         | '0' = Bit is clea | ared                                      |                |                                                                                            |                                                                                                                          |                                                                                                                                           |

|         | pit               | pit W = Writable<br>anged x = Bit is unkn | ADRE           | ADRES<9:2><br>Dit W = Writable bit U = Unimpler<br>anged x = Bit is unknown -n/n = Value a | ADRES < 9:2 ><br>Dit W = Writable bit U = Unimplemented bit, read<br>anged x = Bit is unknown -n/n = Value at POR and BC | ADRES < 9:2> Dit W = Writable bit U = Unimplemented bit, read as '0' anged x = Bit is unknown -n/n = Value at POR and BOR/Value at all of |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

|                  |            |                   |               | •              | •                |                  |              |

|------------------|------------|-------------------|---------------|----------------|------------------|------------------|--------------|

| R/W-x/u          | R/W-x/u    | R/W-x/u           | R/W-x/u       | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

| ADRES            | S<1:0>     | —                 | —             | —              |                  |                  | —            |

| bit 7            |            |                   |               |                |                  |                  | bit 0        |

|                  |            |                   |               |                |                  |                  |              |

| Legend:          |            |                   |               |                |                  |                  |              |

| R = Readable     | bit        | W = Writable      | bit           | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is unch  | anged      | x = Bit is unkr   | iown          | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |            | '0' = Bit is clea | ared          |                |                  |                  |              |

|                  |            |                   |               |                |                  |                  |              |

| bit 7-6          | ADRES<1:0> | . ADC Result F    | Register bits |                |                  |                  |              |

#### **REGISTER 21-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| bit 7-6 | ADRES<1:0>: ADC Result Register bits       |

|---------|--------------------------------------------|

|         | Lower two bits of 10-bit conversion result |

| bit 5-0 | Reserved: Do not use.                      |

#### REGISTER 21-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| —       | —       |         | —       | —       |         | ADRE    | S<9:8>  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-2 Reserved: Do not use.

bit 1-0 **ADRES<9:8>**: ADC Result Register bits Upper two bits of 10-bit conversion result

#### REGISTER 21-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|------------|---------|---------|---------|---------|---------|---------|

|         | ADRES<7:0> |         |         |         |         |         |         |

| bit 7   |            |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

#### 29.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 27.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 29.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 29.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 29-1 demonstrates the code to perform this function.

#### EXAMPLE 29-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | L CCPxCON   | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | S;Load the W reg with   |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

### 29.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by FOSC/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

## 33.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                              |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                         |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [0, 1]                                                             |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                                  |

| Status Affected: | None                                                                                             |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair.    |

|                  | FSRn is limited to the range<br>0000h-FFFFh. Moving beyond these<br>bounds will cause the FSR to |

| ANDLW            | AND literal with W                                                                                              |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                             |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |  |  |

| Status Affected: | Z                                                                                                               |  |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |

| ADDLW            | Add literal and W                                                                                             |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                             |  |  |

| Status Affected: | C, DC, Z                                                                                                      |  |  |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |  |  |

wrap-around.

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

AND W with f

ANDWF

| ADDWF            | Add W and f                                                                                                                                                                     |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                        |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |

| ADDWFC | ADD W and CARRY bit to f |

|--------|--------------------------|

|--------|--------------------------|

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                         |

| Status Affected: | C, DC, Z                                                                                                                                                                   |

| Description:     | Add W, the Carry flag and data<br>memory location 'f'. If 'd' is '0', the<br>result is placed in W. If 'd' is '1', the<br>result is placed in data memory<br>location 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                    |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ASRF f {,d}                                                                                              |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                         |  |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                   |  |

| Status Affected: | C, Z                                                                                                                      |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If |  |

one bit to the right through the Carry flag. The MSb remains unchanged. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'.

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                       |  |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                      |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                               |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                          |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] RETURN                                                                                                                                        |  |  |

| Operands:        | None                                                                                                                                                  |  |  |

| Operation:       | $TOS \to PC$                                                                                                                                          |  |  |

| Status Affected: | None                                                                                                                                                  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |  |  |

| RETLW            | Return with literal in W                                                                                                                                                      | RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                               |  |

| Operation:       | $k \rightarrow (W);$                                                                                                                                                          |                  | d ∈ [0,1]                                                                                                                                                                                                         |  |

|                  | $TOS \rightarrow PC$                                                                                                                                                          | Operation:       | See description below                                                                                                                                                                                             |  |

| Status Affected: | None                                                                                                                                                                          | Status Affected: | C                                                                                                                                                                                                                 |  |

| Description:     | The W register is loaded with the 8-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |

| Words:           | 1                                                                                                                                                                             |                  | C Register f                                                                                                                                                                                                      |  |

| Cycles:          | 2                                                                                                                                                                             |                  |                                                                                                                                                                                                                   |  |

| Example:         | CALL TABLE;W contains table                                                                                                                                                   | Words:           | 1                                                                                                                                                                                                                 |  |

|                  | ;offset value                                                                                                                                                                 | Cycles:          | 1                                                                                                                                                                                                                 |  |

|                  | <ul> <li>;W now has table value</li> </ul>                                                                                                                                    | Example:         | RLF REG1,0                                                                                                                                                                                                        |  |

| TABLE            | •                                                                                                                                                                             |                  | Before Instruction                                                                                                                                                                                                |  |

|                  | ADDWF PC $;W = offset$                                                                                                                                                        |                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |

|                  | RETLW k1 ;Begin table                                                                                                                                                         |                  | C = 0<br>After Instruction                                                                                                                                                                                        |  |

|                  | RETLW k2 ;                                                                                                                                                                    |                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |

|                  | •                                                                                                                                                                             |                  | $W = 1100 \ 1100$                                                                                                                                                                                                 |  |

|                  | •                                                                                                                                                                             |                  | C = 1                                                                                                                                                                                                             |  |

|                  | RETLW kn ; End of table                                                                                                                                                       |                  |                                                                                                                                                                                                                   |  |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                        |                  |                                                                                                                                                                                                                   |  |

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

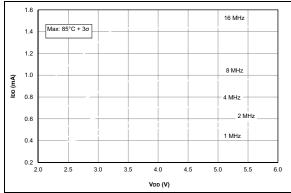

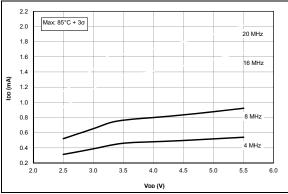

FIGURE 35-26: IDD Maximum, HFINTOSC Mode, PIC16F1717/8/9 Only.

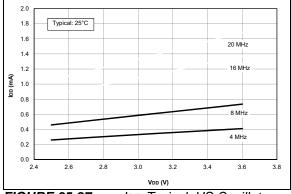

**FIGURE 35-27:** IDD Typical, HS Oscillator, 25°C, PIC16LF1717/8/9 Only.

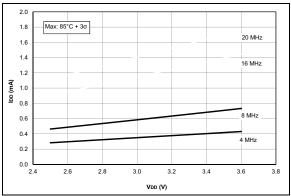

FIGURE 35-28: IDD Maximum, HS Oscillator, PIC16LF1717/8/9 Only.

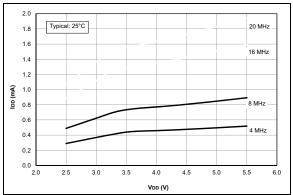

**FIGURE 35-29:** IDD Typical, HS Oscillator, 25°C, PIC16F1717/8/9 Only.

FIGURE 35-30: IDD Maximum, HS Oscillator, PIC16F1717/8/9 Only.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

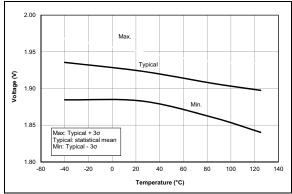

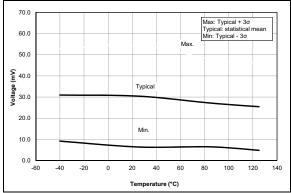

FIGURE 35-61: Brown-out Reset Voltage, Low Trip Point (BORV = 1), PIC16LF1717/8/9 Only.

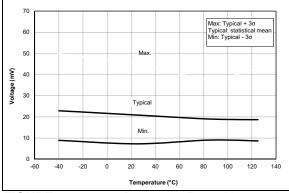

**FIGURE 35-62:** Brown-out Reset Hysteresis, Low Trip Point (BORV = 1), PIC16LF1717/8/9 Only.

FIGURE 35-63: Brown-out Reset Voltage, Low Trip Point (BORV = 1), PIC16F1717/8/9 Only.

FIGURE 35-64: Brown-out Reset Hysteresis, Low Trip Point (BORV = 1), PIC16F1717/8/9 Only.

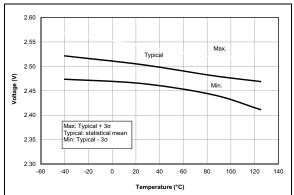

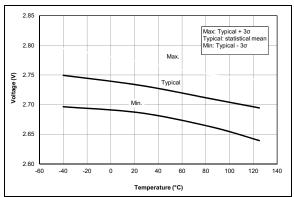

**FIGURE 35-65:** Brown-out Reset Voltage, High Trip Point (BORV = 0).

**FIGURE 35-66:** Brown-out Reset Hysteresis, High Trip Point (BORV = 0).

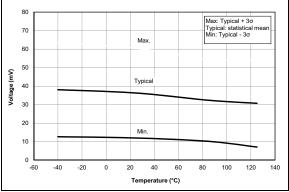

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

**FIGURE 35-109:** Comparator Output Filter Delay Time Over Temp., NP Mode (CxSP = 1), Typical Measured Values, PIC16F1717/8/9 Only.

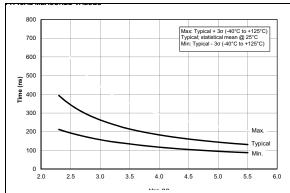

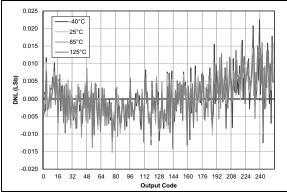

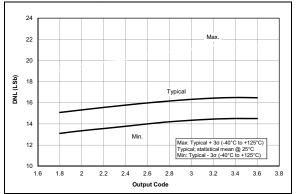

**FIGURE 35-110:** Typical DAC DNL Error, VDD = 3.0V, VREF = External 3V.

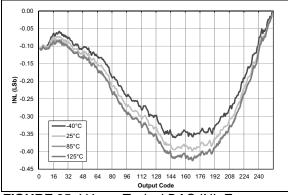

**FIGURE 35-111:** Typical DAC INL Error, VDD = 3.0V, VREF = External 3V.

FIGURE 35-112: Typical DAC INL Error, VDD = 5.0V, VREF = External 5V, PIC16F1717/8/9 Only.

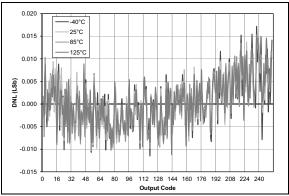

**FIGURE 35-113:** Typical DAC INL Error, VDD = 5.0V, VREF = External 5V, PIC16F1717/8/9 Only.

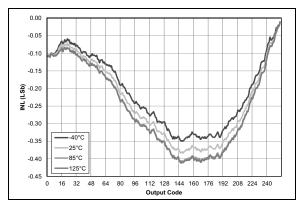

FIGURE 35-114: DAC INL Error, VDD = 3.0V, PIC16LF1717/8/9 Only.

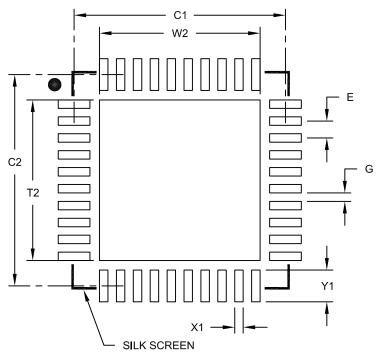

## 40-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 5x5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.40 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 3.80 |

| Optional Center Pad Length | T2 |             |      | 3.80 |

| Contact Pad Spacing        | C1 |             | 5.00 |      |

| Contact Pad Spacing        | C2 |             | 5.00 |      |

| Contact Pad Width (X40)    | X1 |             |      | 0.20 |

| Contact Pad Length (X40)   | Y1 |             |      | 0.75 |

| Distance Between Pads      | G  | 0.20        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2156B