Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | ·                                                                         |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 28x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1719-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                            | Function | Input<br>Type | Output<br>Type | Description                                  |  |  |

|-------------------------------------------------|----------|---------------|----------------|----------------------------------------------|--|--|

| RB1/AN10/C1IN3-/C2IN3-/                         | RB1      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

| OPA2OUT                                         | AN10     | AN            | _              | ADC Channel 10 input.                        |  |  |

|                                                 | C1IN3-   | AN            | —              | Comparator C1 negative input.                |  |  |

|                                                 | C2IN3-   | AN            | —              | Comparator C2 negative input.                |  |  |

|                                                 | OPA2OUT  |               | AN             | Operational Amplifier 2 output.              |  |  |

| RB2/AN8/OPA2IN-                                 | RB2      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                                 | AN8      | AN            | _              | ADC Channel 8 input.                         |  |  |

|                                                 | OPA2IN-  | AN            | —              | Operational Amplifier 2 inverting input.     |  |  |

| RB3/AN9/C1IN2-/C2IN2-/                          | RB3      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

| OPA2IN+                                         | AN9      | AN            | _              | ADC Channel 9 input.                         |  |  |

|                                                 | C1IN2-   | AN            | _              | Comparator C1 negative input.                |  |  |

|                                                 | C2IN2-   | AN            | _              | Comparator C2 negative input.                |  |  |

|                                                 | OPA2IN+  | AN            | _              | Operational Amplifier 2 non-inverting input. |  |  |

| RB4/AN11                                        | RB4      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                                 | AN11     | AN            | _              | ADC Channel 11 input.                        |  |  |

| RB5/AN13/T1G <sup>(1)</sup>                     | RB5      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                                 | AN13     | AN            |                | ADC Channel 13 input.                        |  |  |

|                                                 | T1G      | TTL/ST        |                | Timer1 gate input.                           |  |  |

| RB6/CLCIN2 <sup>(1)</sup> /ICSPCLK              | RB6      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                                 | CLCIN2   | TTL/ST        |                | Configurable Logic Cell source input.        |  |  |

|                                                 | ICSPCLK  | ST            |                | Serial Programming Clock.                    |  |  |

| RB7/DAC1OUT2/DAC2OUT2/                          | RB7      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

| CLCIN3 <sup>(1)</sup> /ICSPDAT                  | DAC1OUT2 | _             | AN             | Digital-to-Analog Converter output.          |  |  |

|                                                 | DAC2OUT2 | _             | AN             | Digital-to-Analog Converter output.          |  |  |

|                                                 | CLCIN3   | TTL/ST        |                | Configurable Logic Cell source input.        |  |  |

|                                                 | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                              |  |  |

| RC0/T1CKI <sup>(1)</sup> /SOSCO                 | RC0      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                                 | T1CKI    | ST            |                | Timer1 clock input.                          |  |  |

|                                                 | SOSCO    | XTAL          | XTAL           | Secondary Oscillator Connection.             |  |  |

| RC1/SOSCI/CCP2 <sup>(1)</sup>                   | RC1      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                                 | SOSCI    | XTAL          | XTAL           | Secondary Oscillator Connection.             |  |  |

|                                                 | CCP2     | TTL/ST        |                | Capture input.                               |  |  |

| RC2/AN14/CCP1 <sup>(1)</sup>                    | RC2      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                                 | AN14     | AN            | _              | ADC Channel 14 input.                        |  |  |

|                                                 | CCP1     | TTL/ST        | _              | Capture input.                               |  |  |

| RC3/AN15/SCK <sup>(1)</sup> /SCL <sup>(1)</sup> | RC3      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                                 | AN15     | AN            |                | ADC Channel 15 input.                        |  |  |

|                                                 | SCK      | TTL/ST        | —              | SPI clock input.                             |  |  |

|                                                 | 0.01     | 120           |                |                                              |  |  |

OD **Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ TTL = TTL compatible input ST

l<sup>2</sup>C

SCL

HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers. 2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

I<sup>2</sup>C clock.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

## TABLE 3-9: PIC16(L)F1717/8/9 MEMORY MAP, BANK 28-30

|               | Bank 28   |              | Bank 29               |               | Bank 30              |

|---------------|-----------|--------------|-----------------------|---------------|----------------------|

| E0Ch          |           | E8Ch         |                       | F0Ch          |                      |

| E0Dh          | _         | E8Dh         | _                     | F0Dh          | _                    |

| E0Eh          | _         | E8Eh         | _                     | F0Eh          | _                    |

| E0Fh          | PPSLOCK   | E8Fh         | _                     | F0Fh          | CLCDATA              |

| E10h          | INTPPS    | E90h         | RA0PPS                | F10h          | CLC1CON              |

| E11h          | TOCKIPPS  | E91h         | RA1PPS                | F11h          | CLC1POL              |

| E12h          | T1CKIPPS  | E92h         | RA2PPS                | F12h          | CLC1SEL0             |

| E13h          | T1GPPS    | E93h         | RA3PPS                | F13h          | CLC1SEL1             |

| E14h          | CCP1PPS   | E94h         | RA4PPS                | F14h          | CLC1SEL2             |

| E15h          | CCP2PPS   | E95h         | RA5PPS                | F15h          | CLC1SEL3             |

| E16h          | _         | E96h         | RA6PPS                | F16h          | CLC1GLS0             |

| E17h          | COGINPPS  | E97h         | RA7PPS                | F17h          | CLC1GLS1             |

| E18h          | _         | E98h         | RB0PPS                | F18h          | CLC1GLS2             |

| E19h          |           | E99h         | RB1PPS                | F19h          | CLC1GLS3             |

| E1Ah          |           | E9Ah         | RB2PPS                | F1Ah          | CLC2CON              |

| E1Bh          |           | E9Bh         | RB3PPS                | F1Bh          | CLC2POL              |

| E1Ch          |           | E9Ch         | RB4PPS <sup>(1)</sup> | F1Ch          | CLC2SEL0             |

|               |           |              | RB5PPS <sup>(1)</sup> |               |                      |

| E1Dh          | _         | E9Dh         |                       | F1Dh          | CLC2SEL1             |

| E1Eh          | —         | E9Eh         | RB6PPS <sup>(1)</sup> | F1Eh          | CLC2SEL2             |

| E1Fh          | —         | E9Fh         | RB7PPS <sup>(1)</sup> | F1Fh          | CLC2SEL3             |

| E20h          | SSPCLKPPS | EA0h         | RC0PPS                | F20h          | CLC2GLS0             |

| E21h          | SSPDATPPS | EA1h         | RC1PPS                | F21h          | CLC2GLS1             |

| E22h          | SSPSSPPS  | EA2h         | RC2PPS                | F22h          | CLC2GLS2             |

| E23h          |           | EA3h         | RC3PPS                | F23h          | CLC2GLS3             |

| E24h          | RXPPS     | EA4h         | RC4PPS                | F24h          | CLC3CON              |

| E25h          | CKPPS     | EA5h         | RC5PPS                | F25h          | CLC3POL              |

| E26h          | —         | EA6h         | RC6PPS                | F26h          | CLC3SEL0             |

| E27h          | _         | EA7h         | RC7PPS                | F27h          | CLC3SEL1             |

| E28h          | CLCIN0PPS | EA8h         | RD0PPS <sup>(1)</sup> | F28h          | CLC3SEL2             |

| E29h          | CLCIN1PPS | EA9h         | RD1PPS <sup>(1)</sup> | F29h          | CLC3SEL3             |

| E2911<br>E2Ah |           | EASI         | RD2PPS <sup>(1)</sup> | F2911<br>F2Ah |                      |

|               | CLCIN2PPS |              |                       | 1             | CLC3GLS0             |

| E2Bh          | CLCIN3PPS | EABh         | RD3PPS <sup>(1)</sup> | F2Bh          | CLC3GLS1             |

| E2Ch          | —         | EACh         | RD4PPS <sup>(1)</sup> | F2Ch          | CLC3GLS2             |

| E2Dh          | —         | EADh         | RD5PPS <sup>(1)</sup> | F2Dh          | CLC3GLS3             |

| E2Eh          | —         | EAEh         | RD6PPS <sup>(1)</sup> | F2Eh          | CLC4CON              |

| E2Fh          | _         | EAFh         | RD7PPS <sup>(1)</sup> | F2Fh          | CLC4POL              |

| E30h          |           | EB0h         | RE0PPS <sup>(1)</sup> | F30h          | CLC4SEL0             |

| E31h          |           | EB1h         | RE1PPS <sup>(1)</sup> | F31h          | CLC4SEL1             |

| E32h          |           | EB2h         | RE2PPS <sup>(1)</sup> | F32h          | CLC4SEL2             |

|               |           |              | NEZPES'               | •             | CLC4SEL2<br>CLC4SEL3 |

| E33h<br>E34h  |           | EB3h         |                       | F33h          | CLC4SEL3<br>CLC4GLS0 |

|               |           | EB4h<br>EB5h |                       | F34h          |                      |

| E35h<br>E36h  | _         |              | _                     | F35h          | CLC4GLS1             |

| E37h          |           | EB6h         |                       | F36h          | CLC4GLS2<br>CLC4GLS3 |

| E38h          |           | EB7h<br>EB8h |                       | F37h<br>F38h  | 01040133             |

| E39h          |           | EB9h         |                       | F39h          |                      |

| E390<br>E3Ah  |           | EBAh         |                       | F3Ah          |                      |

| E3An<br>E3Bh  |           | EBBh         |                       | F3Bh          |                      |

| E3Ch          |           | EBCh         |                       | F3Ch          |                      |

| E3Dh          |           | EBDh         |                       | F3Dh          |                      |

| E3Eh          |           | EBEh         |                       | F3Eh          |                      |

| E3Fh          |           | EBFh         |                       | F3En          |                      |

| E3FN<br>E40h  |           | EBFn<br>EC0h |                       | F40h          |                      |

|               |           |              |                       |               |                      |

|               | —         |              | —                     |               | —                    |

| E6Fh          |           | EEFh         |                       | F6Fh          |                      |

|               |           |              |                       |               |                      |

## 4.7 Register Definitions: Device and Revision

| R      | Р   | -     | _      |         |                     |

|--------|-----|-------|--------|---------|---------------------|

|        | R   | R     | R      | R       | R                   |

|        |     | DEV<  | <13:8> |         |                     |

| bit 13 |     |       |        |         | bit 8               |

| R      | R   | R     | R      | R       | R                   |

|        | DEV | <7:0> |        |         |                     |

|        |     |       |        |         | bit 0               |

|        |     | R R   | bit 13 | R R R R | bit 13<br>R R R R R |

#### **REGISTER 4-3: DEVID: DEVICE ID REGISTER**

#### Legend:

R = Readable bit

'1' = Bit is set '0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device      | DEVID<13:0> Values                 |  |  |  |  |  |  |  |

|-------------|------------------------------------|--|--|--|--|--|--|--|

| PIC16F1717  | 11 0000 0101 1100 ( <b>305Ch</b> ) |  |  |  |  |  |  |  |

| PIC16LF1717 | 11 0000 0101 1111 ( <b>305Fh</b> ) |  |  |  |  |  |  |  |

| PIC16F1718  | 11 0000 0101 1011 ( <b>305Bh</b> ) |  |  |  |  |  |  |  |

| PIC16LF1718 | 11 0000 0101 1110 ( <b>305Eh</b> ) |  |  |  |  |  |  |  |

| PIC16F1719  | 11 0000 0101 1010 ( <b>305Ah</b> ) |  |  |  |  |  |  |  |

| PIC16LF1719 | 11 0000 0101 1101 ( <b>305Dh</b> ) |  |  |  |  |  |  |  |

## REGISTER 4-4: REVID: REVISION ID REGISTER

| R            | R | R | R | R | R |  |  |  |  |

|--------------|---|---|---|---|---|--|--|--|--|

| REV<13:8>    |   |   |   |   |   |  |  |  |  |

| bit 13 bit 8 |   |   |   |   |   |  |  |  |  |

| R        | R | R | R | R | R | R | R |  |  |

|----------|---|---|---|---|---|---|---|--|--|

| REV<7:0> |   |   |   |   |   |   |   |  |  |

| bit 7    |   |   |   |   |   |   |   |  |  |

| Legend:          |                      |

|------------------|----------------------|

| R = Readable bit |                      |

| '1' = Bit is set | '0' = Bit is cleared |

#### bit 13-0 **REV<13:0>:** Revision ID bits

## 6.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaled output of the 16 MHz HFINTOSC, 500 kHz MFINTOSC, and 31 kHz LFINTOSC connect to a multiplexer (see Figure 6-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4 x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

### 6.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

| Note: | When                                   | using   | the  | PLLEN     | bit | of   | the  |  |  |

|-------|----------------------------------------|---------|------|-----------|-----|------|------|--|--|

|       | Config                                 | uration | Word | s, the 4x | PLL | . ca | nnot |  |  |

|       | be disabled by software and the SPLLEN |         |      |           |     |      |      |  |  |

|       |                                        |         |      | ailable.  |     |      |      |  |  |

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 or PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

| Note 1: | Individual  | inte | rrupt | flag  | bits | s are | e set, |

|---------|-------------|------|-------|-------|------|-------|--------|

|         | regardless  | of   | the   | state | of   | any   | other  |

|         | enable bits |      |       |       |      |       |        |

2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

## 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

## 11.4 Register Definitions: PORTB

#### REGISTER 11-9: PORTB: PORTB REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u                                               | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|---------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| RB7                                     | RB6     | RB5               | RB4                                                   | RB3                                | RB2     | RB1     | RB0     |  |

| bit 7                                   |         |                   |                                                       |                                    |         |         | bit 0   |  |

|                                         |         |                   |                                                       |                                    |         |         |         |  |

| Legend:                                 |         |                   |                                                       |                                    |         |         |         |  |

| R = Readable bit W = Writable bit       |         |                   | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         | iown              | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

## REGISTER 11-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 11-11: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

| TABLE 11-7: SUMMARY OF REGISTE | RS ASSOCIATED WITH PORTE |

|--------------------------------|--------------------------|

|--------------------------------|--------------------------|

| Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2                  | Bit 1                  | Bit 0                  | Register<br>on Page |

|------------------------|-------|-------|-------|-------|---------|------------------------|------------------------|------------------------|---------------------|

| ANSELE <sup>(1)</sup>  | _     | _     | _     |       | -       | ANSE2                  | ANSE1                  | ANSE0                  | 146                 |

| INLVLE                 | _     | _     | _     | _     | INLVLE3 | INLVLE2 <sup>(1)</sup> | INLVLE1 <sup>(1)</sup> | INLVLE0 <sup>(1)</sup> | 148                 |

| LATE <sup>(1)</sup>    | —     | —     | _     | _     | _       | LATE2                  | LATE1                  | LATE0                  | 146                 |

| ODCONE <sup>(1)</sup>  | —     | —     | _     | _     | _       | ODE2                   | ODE1                   | ODE0                   | 147                 |

| PORTE                  | —     | —     | _     | _     | RE3     | RE2 <sup>(1)</sup>     | RE1 <sup>(1)</sup>     | RE0 <sup>(1)</sup>     | 145                 |

| SLRCONE <sup>(1)</sup> | —     | —     | _     | _     | _       | SLRE2                  | SLRE1                  | SLRE0                  | 148                 |

| TRISE                  |       |       |       | _     | TRISE3  | TRISE2 <sup>(1)</sup>  | TRISE1 <sup>(1)</sup>  | TRISE0 <sup>(1)</sup>  | 145                 |

| WPUE                   |       |       |       | _     | WPUE3   | WPUE2 <sup>(1)</sup>   | WPUE1 <sup>(1)</sup>   | WPUE0 <sup>(1)</sup>   | 147                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: PIC16(L)F1717/9 only.

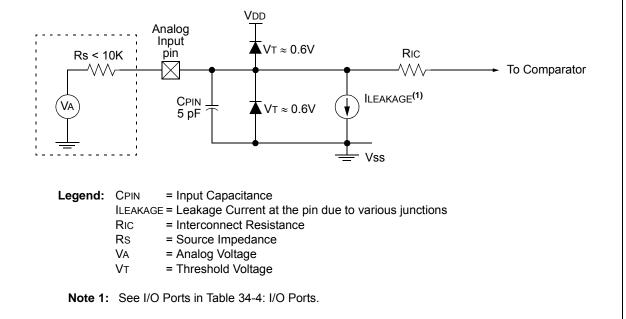

## 16.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 16-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### 17.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- 7. Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the desired pin PPS control bits.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- **2:** For operation with other peripherals only, disable PWMx pin outputs.

## 17.1.10 SETUP FOR PWM OPERATION TO OTHER DEVICE PERIPHERALS

The following steps should be taken when configuring the module for PWM operation to be used by other device peripherals:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- 7. Configure the PWM module by loading the PWMxCON register with the appropriate values.

**Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

| Name                 | Bit 7  | Bit 6    | Bit 5  | Bit 4  | Bit 3   | Bit 2      | Bit 1    | Bit 0  | Register<br>on Page |

|----------------------|--------|----------|--------|--------|---------|------------|----------|--------|---------------------|

| INTCON               | GIE    | PEIE     | TMR0IE | INTE   | IOCIE   | TMR0IF     | INTF     | IOCIF  | 90                  |

| NCO1ACCU             |        | _        | _      |        |         | NCO1AC     | C<19:16> |        | 239                 |

| NCO1ACCH             |        |          |        | NCO1AC | C<15:8> |            |          |        | 239                 |

| NCO1ACCL             |        |          |        | NCO1A  | CC<7:0> |            |          |        | 238                 |

| NCO1CLK              | N      | 1PWS<2:0 | >      | _      | _       | _          | N1CK     | S<1:0> | 238                 |

| NCO1CON              | N1EN   | _        | N1OUT  | N1POL  | —       | —          | —        | N1PFM  | 237                 |

| NCO1INCU             |        |          | _      |        |         | NCO1IN     | C<19:16> |        | 240                 |

| NCO1INCH             |        |          |        | NCO1IN | C<15:8> |            |          |        | 240                 |

| NCO1INCL             |        |          |        | NCO1IN | NC<7:0> |            |          |        | 239                 |

| PIE3                 | _      | NCOIE    | COGIE  | ZCDIE  | CLC4IE  | CLC3IE     | CLC2IE   | CLC1IE | 93                  |

| PIR3                 | _      | NCOIF    | COGIF  | ZCDIF  | CLC4IF  | CLC3IF     | CLC2IF   | CLC1IF | 96                  |

| TRISA                | TRISA7 | TRISA6   | TRISA5 | TRISA4 | TRISA3  | TRISA2     | TRISA1   | TRISA0 | 124                 |

| TRISC                | TRISC7 | TRISC6   | TRISC5 | TRISC4 | TRISC3  | TRISC2     | TRISC1   | TRISC0 | 135                 |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6   | TRISD5 | TRISD4 | TRISD3  | TRISD2     | TRISD1   | TRISD0 | 140                 |

| RxyPPS               |        |          | _      |        | F       | RxyPPS<4:0 | >        |        | 153                 |

TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH NCOX

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for NCOx module.

Note 1: PIC16(L)F1717/9 only.

| R/W-0/0                                                      |             |                  |                |                |               |                  |              |

|--------------------------------------------------------------|-------------|------------------|----------------|----------------|---------------|------------------|--------------|

|                                                              | R/W-0/0     | R/W-0/0          | R/W-0/0        | U-0            | U-0           | U-0              | U-0          |

|                                                              | TRIGSE      | L<3:0>(1)        |                | —              | —             | —                | —            |

| bit 7                                                        |             |                  |                |                |               |                  | bit (        |

| Logondu                                                      |             |                  |                |                |               |                  |              |

| Legend:                                                      | <b>b</b> :4 |                  | L :4           |                |               |                  |              |

| R = Readable bit W = Writable bit U = Unimplemented bit, rea |             |                  |                |                |               |                  |              |

| u = Bit is unch                                              | anged       | x = Bit is unkr  | nown           | -n/n = Value a | at POR and BO | R/Value at all c | other Resets |

| '1' = Bit is set                                             |             | '0' = Bit is cle | ared           |                |               |                  |              |

|                                                              | 0001 = CCF  |                  | trigger select | eu             |               |                  |              |

### REGISTER 21-3: ADCON2: ADC CONTROL REGISTER 2

- 1110 = Reserved

- 1111 = Reserved

- bit 3-0 Unimplemented: Read as '0'

- Note 1: This is a rising edge sensitive input for all sources.

- **2:** Signal also sets its corresponding interrupt flag.

#### **REGISTER 21-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u | R/W-x/u           | R/W-x/u                                   | R/W-x/u        | R/W-x/u                                                                                    | R/W-x/u                                                                                                                  | R/W-x/u                                                                                                                                   |

|---------|-------------------|-------------------------------------------|----------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|         |                   | ADRE                                      | S<9:2>         |                                                                                            |                                                                                                                          |                                                                                                                                           |

|         |                   |                                           |                |                                                                                            |                                                                                                                          | bit 0                                                                                                                                     |

|         |                   |                                           |                |                                                                                            |                                                                                                                          |                                                                                                                                           |

|         |                   |                                           |                |                                                                                            |                                                                                                                          |                                                                                                                                           |

| bit     | W = Writable I    | bit                                       | U = Unimpler   | nented bit, read                                                                           | d as '0'                                                                                                                 |                                                                                                                                           |

| anged   | x = Bit is unkn   | iown                                      | -n/n = Value a | at POR and BC                                                                              | R/Value at all o                                                                                                         | other Resets                                                                                                                              |

|         | '0' = Bit is clea | ared                                      |                |                                                                                            |                                                                                                                          |                                                                                                                                           |

|         | pit               | pit W = Writable<br>anged x = Bit is unkn | ADRE           | ADRES<9:2><br>Dit W = Writable bit U = Unimpler<br>anged x = Bit is unknown -n/n = Value a | ADRES < 9:2 ><br>Dit W = Writable bit U = Unimplemented bit, read<br>anged x = Bit is unknown -n/n = Value at POR and BC | ADRES < 9:2> Dit W = Writable bit U = Unimplemented bit, read as '0' anged x = Bit is unknown -n/n = Value at POR and BOR/Value at all of |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

|                  |            |                   |               | •                                                     | •                |          |         |  |  |

|------------------|------------|-------------------|---------------|-------------------------------------------------------|------------------|----------|---------|--|--|

| R/W-x/u          | R/W-x/u    | R/W-x/u           | R/W-x/u       | R/W-x/u                                               | R/W-x/u          | R/W-x/u  | R/W-x/u |  |  |

| ADRES            | S<1:0>     | —                 | —             | —                                                     |                  |          | —       |  |  |

| bit 7            |            |                   |               |                                                       |                  |          | bit 0   |  |  |

|                  |            |                   |               |                                                       |                  |          |         |  |  |

| Legend:          |            |                   |               |                                                       |                  |          |         |  |  |

| R = Readable     | bit        | W = Writable      | bit           | U = Unimplen                                          | nented bit, read | l as '0' |         |  |  |

| u = Bit is unch  | anged      | x = Bit is unkr   | iown          | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |  |

| '1' = Bit is set |            | '0' = Bit is clea | ared          |                                                       |                  |          |         |  |  |

|                  |            |                   |               |                                                       |                  |          |         |  |  |

| bit 7-6          | ADRES<1:0> | . ADC Result F    | Register bits |                                                       |                  |          |         |  |  |

#### **REGISTER 21-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| bit 7-6 | ADRES<1:0>: ADC Result Register bits       |

|---------|--------------------------------------------|

|         | Lower two bits of 10-bit conversion result |

| bit 5-0 | Reserved: Do not use.                      |

#### REGISTER 21-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| —       | —       |         | —       | —       |         | ADRE    | S<9:8>  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-2 Reserved: Do not use.

bit 1-0 **ADRES<9:8>**: ADC Result Register bits Upper two bits of 10-bit conversion result

#### REGISTER 21-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| ADRES<7:0> |         |         |         |         |         |         |         |  |

| bit 7      |         |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

|                                                                                               | U-0                                                                                                               | R-x/x                                                                      | R/W-0/0                                                                    | U-0                               | U-0                               | R/W-0/0      | R/W-0/0  |  |  |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------|-----------------------------------|--------------|----------|--|--|

| ZCDxEN                                                                                        | —                                                                                                                 | ZCDxOUT                                                                    | ZCDxPOL                                                                    | —                                 | _                                 | ZCDxINTP     | ZCDxINTN |  |  |

| bit 7                                                                                         |                                                                                                                   |                                                                            |                                                                            |                                   |                                   |              | bit 0    |  |  |

| Lonondi                                                                                       |                                                                                                                   |                                                                            |                                                                            |                                   |                                   |              |          |  |  |

| Legend:<br>R = Readable I                                                                     | h:+                                                                                                               | M = Mritable                                                               | -:+                                                                        |                                   | nanted bit read                   | aa 'O'       |          |  |  |

|                                                                                               |                                                                                                                   | W = Writable                                                               |                                                                            |                                   | nented bit, read                  |              |          |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                                                                                                                   |                                                                            |                                                                            |                                   |                                   |              |          |  |  |

| '1' = Bit is set                                                                              |                                                                                                                   | '0' = Bit is clea                                                          | ared                                                                       | q = value dep                     | ends on configu                   | iration bits |          |  |  |

| bit 7                                                                                         | 1 = Zero-cros<br>0 = Zero-cros                                                                                    | s detect is disa                                                           | bled. ZCD pir<br>abled. ZCD pir                                            | n is forced to o                  | utput to source a ording to PPS a |              |          |  |  |

| bit 6                                                                                         | Unimplemen                                                                                                        | ted: Read as '                                                             | )'                                                                         |                                   |                                   |              |          |  |  |

| bit 5                                                                                         | ZCDxPOL bit<br>1 = ZCD pin i<br>0 = ZCD pin i<br>ZCDxPOL bit<br>1 = ZCD pin i                                     | s sinking curre<br>s sourcing curr<br><u>= 1</u> :<br>s sourcing curr      | nt<br>rent                                                                 |                                   |                                   |              |          |  |  |

|                                                                                               | 0 = 200  pm                                                                                                       | s sinking curre                                                            | nt                                                                         |                                   |                                   |              |          |  |  |

| bit 4                                                                                         | <b>ZCDxPOL:</b> Ze 1 = ZCD logic                                                                                  | s sinking curre<br>ero-Cross Dete<br>c output is inve<br>c output is not i | ction Logic O<br>rted                                                      | utput Polarity b                  | bit                               |              |          |  |  |

| bit 4<br>bit 3-2                                                                              | <b>ZCDxPOL:</b> Zet<br>1 = ZCD logic<br>0 = ZCD logic                                                             | ero-Cross Dete<br>c output is inve                                         | ction Logic O<br>rted<br>nverted                                           | utput Polarity b                  | bit                               |              |          |  |  |

|                                                                                               | <b>ZCDxPOL:</b> Ze<br>1 = ZCD logic<br>0 = ZCD logic<br><b>Unimplement</b><br><b>ZCDxINTP:</b> Z<br>1 = ZCDIF bit | ero-Cross Dete<br>c output is inve<br>c output is not i                    | ction Logic Or<br>rted<br>nverted<br>o'<br>itive Edge Inte<br>o-high ZCDxC | errupt Enable b<br>DUT transition | it                                |              |          |  |  |

#### TABLE 25-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

| Name    | Bit 7  | Bit 6 | Bit 5   | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 |        | Bit 1  | Bit 0    | Register<br>on page |     |

|---------|--------|-------|---------|-------------------------------|--------|--------|----------|---------------------|-----|

| PIE3    | —      | NCOIE | COGIE   | ZCDIE                         | CLC4IE | CLC3IE | CLC2IE   | CLC1IE              | 93  |

| PIR3    | —      | NCOIF | COGIF   | ZCDIF                         | CLC4IF | CLC3IF | CLC2IF   | CLC1IF              | 96  |

| ZCD1CON | ZCD1EN |       | ZCD10UT | ZCD1POL                       |        |        | ZCD1INTP | ZCD1INTN            | 267 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 25-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         | _       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 57                  |

|         | 7:0  | ZCDDIS  |         | _        | _        |          | PPS1WAY  | WRT     | <1:0>   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

25.9

Register Definitions: 7CD Control

| FIGURE 27-5:           | TIMER1 GATE SINGLE-PULSE MODE                         |                                          |

|------------------------|-------------------------------------------------------|------------------------------------------|

|                        |                                                       |                                          |

| TMR1GE                 |                                                       |                                          |

| T1GPOL                 |                                                       |                                          |

| T1GSPM                 |                                                       |                                          |

| T1GG <u>O/</u><br>DONE | Cleared by falling edge                               | hardware on<br>of T1GVAL                 |

| t1g_in                 | rising edge of T1G                                    |                                          |

| T1CKI                  |                                                       |                                          |

| T1GVAL                 |                                                       |                                          |

| Timer1                 | N N + 1 N + 2                                         |                                          |

| TMR1GIF                | Cleared by software     Set by hard-     falling edge | ware on Cleared by<br>of T1GVAL software |

|        |                   |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRG     | <b>616 =</b> 0 |                             |                    |            |                             |

|--------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz |            | Fosc = 20.000 MHz           |                |            | Fosc                        | ; = 18.43      | 2 MHz          | Fosc                        | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                 |            | _                           | _              |            | _                           | _              |                | _                           | _                  |            | _                           |

| 1200   | —                 | —          | —                           | 1221           | 1.73       | 255                         | 1200           | 0.00           | 239                         | 1200               | 0.00       | 143                         |

| 2400   | 2404              | 0.16       | 207                         | 2404           | 0.16       | 129                         | 2400           | 0.00           | 119                         | 2400               | 0.00       | 71                          |

| 9600   | 9615              | 0.16       | 51                          | 9470           | -1.36      | 32                          | 9600           | 0.00           | 29                          | 9600               | 0.00       | 17                          |

| 10417  | 10417             | 0.00       | 47                          | 10417          | 0.00       | 29                          | 10286          | -1.26          | 27                          | 10165              | -2.42      | 16                          |

| 19.2k  | 19.23k            | 0.16       | 25                          | 19.53k         | 1.73       | 15                          | 19.20k         | 0.00           | 14                          | 19.20k             | 0.00       | 8                           |

| 57.6k  | 55.55k            | -3.55      | 3                           | —              |            | _                           | 57.60k         | 0.00           | 7                           | 57.60k             | 0.00       | 2                           |

| 115.2k | —                 | —          | —                           | —              | _          | —                           | —              | —              | —                           | —                  | —          | —                           |

#### TABLE 31-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  |            |                             |                | SYNC              | <b>C =</b> 0, <b>BRG</b>    | l = 0, BRG     | <b>616 =</b> 0 |                             |                |            |                             |

|--------|------------------|------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            | Fosc = 4.000 MHz            |                | Fosc = 3.6864 MHz |                             |                | Fos            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                | _          | _                           | 300            | 0.16              | 207                         | 300            | 0.00           | 191                         | 300            | 0.16       | 51                          |

| 1200   | 1202             | 0.16       | 103                         | 1202           | 0.16              | 51                          | 1200           | 0.00           | 47                          | 1202           | 0.16       | 12                          |

| 2400   | 2404             | 0.16       | 51                          | 2404           | 0.16              | 25                          | 2400           | 0.00           | 23                          | —              | _          | —                           |

| 9600   | 9615             | 0.16       | 12                          | _              | _                 | _                           | 9600           | 0.00           | 5                           | —              | _          | —                           |

| 10417  | 10417            | 0.00       | 11                          | 10417          | 0.00              | 5                           | _              | _              | _                           | —              | _          | _                           |

| 19.2k  | _                | _          | _                           | _              | _                 | _                           | 19.20k         | 0.00           | 2                           | _              | _          | _                           |

| 57.6k  | —                | _          | _                           | —              | _                 | —                           | 57.60k         | 0.00           | 0                           | —              | —          | —                           |

| 115.2k | —                | _          | _                           | —              | _                 | —                           | —              | _              | —                           | —              | —          | —                           |

|        |                   |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>G16 =</b> 0 |                             |                |                    |                             |  |

|--------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz |            | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc           | : = 18.43      | 2 MHz                       | Fosc           | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | —                 | _          | —                           |                   |            | _                           |                |                | —                           |                | —                  | —                           |  |

| 1200   | _                 | _          | —                           | _                 | _          | —                           | _              | _              | —                           | —              | _                  | —                           |  |

| 2400   |                   | _          | _                           | _                 | _          | _                           | _              | _              | _                           | _              | _                  | _                           |  |

| 9600   | 9615              | 0.16       | 207                         | 9615              | 0.16       | 129                         | 9600           | 0.00           | 119                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417             | 0.00       | 191                         | 10417             | 0.00       | 119                         | 10378          | -0.37          | 110                         | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k            | 0.16       | 103                         | 19.23k            | 0.16       | 64                          | 19.20k         | 0.00           | 59                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 57.14k            | -0.79      | 34                          | 56.82k            | -1.36      | 21                          | 57.60k         | 0.00           | 19                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 117.64k           | 2.12       | 16                          | 113.64k           | -1.36      | 10                          | 115.2k         | 0.00           | 9                           | 115.2k         | 0.00               | 5                           |  |

## 31.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 31.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TX1STA register configures the device for synchronous operation. Setting the CSRC bit of the TX1STA register configures the device as a master. Clearing the SREN and CREN bits of the RC1STA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RC1STA register enables the EUSART.

#### 31.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

### 31.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUD1CON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

31.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TX1REG register. If the TSR still contains all or part of a previous character the new character data is held in the TX1REG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TX1REG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TX1REG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

## 31.5.1.4 Synchronous Master Transmission Setup

- Initialize the SP1BRGH, SP1BRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 31.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TX1REG register.

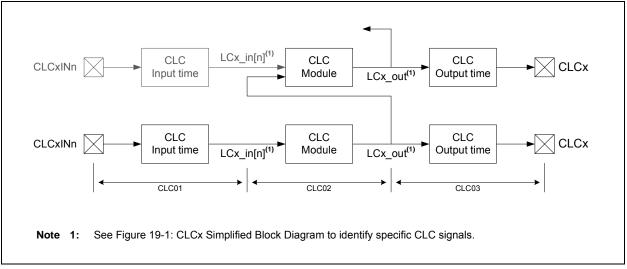

### FIGURE 34-12: CLC PROPAGATION TIMING

### TABLE 34-14: CONFIGURATION LOGIC CELL (CLC) CHARACTERISTICS

|               | Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                    |            |      |          |       |            |                          |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------|------|----------|-------|------------|--------------------------|--|--|--|--|

| Param.<br>No. | Sym.                                                                                                                          | Characteristic                     | Min.       | Тур† | Max.     | Units | Conditions |                          |  |  |  |  |

| CLC01*        | TCLCIN                                                                                                                        | CLC input time                     |            |      | 7        | OS17  | ns         | (Note 1)                 |  |  |  |  |

| CLC02*        | TCLC                                                                                                                          | CLC module input to output progaga | ation time | _    | 24<br>12 |       | ns<br>ns   | VDD = 1.8V<br>VDD > 3.6V |  |  |  |  |

| CLC03*        | TCLCOUT                                                                                                                       | CLC output time Ris                | e Time     | _    | OS18     | _     | _          | (Note 1)                 |  |  |  |  |

|               |                                                                                                                               | Fal                                | l Time     | —    | OS19     | _     | _          | (Note 1)                 |  |  |  |  |

| CLC04*        | FCLCMAX                                                                                                                       | CLC maximum switching frequency    |            | —    | 45       | _     | MHz        |                          |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: See Table 34-10 for OS17, OS18 and OS19 rise and fall times.

## 36.0 DEVELOPMENT SUPPORT

The PIC microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPASM™ Assembler - MPLINK™ Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 36.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- Local file history feature